D触发器的设计和仿真讲解

毕业设计(论文)-PWM清零D触发器的电路仿真设计

毕业论文题目:PWM清零D触发器的电路仿真设计摘要PWM (Pulse Width Modulation),脉冲宽度调制,是利用微处理器的数字输出来对模拟电路进行控制的一种非常有效的技术,广泛应用在测量、通信、功率控制与变换的许多领域中。

PWM的应用研究一直受到关注,首要的是PWM的数字化实现技术。

D触发器是一种常用的数字集成电路,它在数字PWM技术中有着广泛而重要的应用。

本论文首先对PWM技术进行了系统的介绍,基于对PWM原理的理解,对PWM中的D触发器电路进行研究,通过参数设计,对具有清零作用的D触发器电路结构进行了设计,结合集成电路EDA设计软件进行了电路仿真设计,并对结果进行了分析,实现了电路功能;同时,基于CMOS工艺,绘制了整体电路的版图。

关键词PWM;D触发器;CMOS工艺;版图AbstractPWM (Pulse Width Modulation),Pulse width modulation, is using the width of the microprocessor for analog to digital output control of a kind of very effective technology, widely used in measuring, communication and power control and transform in many areas. The application research has been a PWM, primary concern is the realization of digital technology, PWM. With microelectronics technology and power electronic technology development, the digital realization method also PWM has become the main form of PWM.D flip-flop is a kind of common digital integrated circuit, it in the digital technology has been widely PWM and important application. This paper first PWM technology is introduced, the system based on the principle of PWM, the D flip-flop PWM circuit design, research, and through the parameters of the function has cleared the trigger circuit structure D design and simulation design, and the results of the analysis and territory.KeywordsPWM; D flip-flop; CMOS technology; Layout目录摘要 (I)Abstract (II)第一章前言 (1)引言 (1)PWM技术 (1)模拟PWM技术 (1)1.2.2 数字PWM技术 (4)1.3 PWM的发展现状及应用 (6)论文的主要内容 (7)第二章 PWM触发器 (9)2.1 触发器分类 (9)2.1.1 RS触发器 (9)2.1.2 单稳态触发器 (10)施密特触发器 (11)2.2 D触发器的不同结构和不同工作方式 (13)第三章PWM清零D触发器的电路设计及仿真分析 (16)3.1 清零D触发器设计思想 (16)3.2 PWM的电路实现 (16)3.2.1 PWM清零D触发器工作原理 (16)3.2.2 PWM清零D触发器电路设计 (17)3.3 PWM清零D触发器的电路仿真 (18)第四章版图绘制 (19)4.1 版图设计规则 (19)4.1.1 DRC规则 (19)版图绘制规则 (20)4.2 电路整体版图 (21)结论 (22)参考文献 (23)附录 (24)致谢 (26)第一章前言1.1 引言脉冲宽度调制(PWM),是英文“Pulse Width Modulation”的缩写,简称脉宽调制,是利用微处理器的数字输出来对模拟电路进行控制的一种非常有效的技术,广泛应用在从测量、通信到功率控制与变换的许多领域中。

D触发器及其应用说课讲解

D触发器及其应用实验八D触发器及其应用一、实验目的1.熟悉基本D触发器的功能测试;2.了解触发器的两种触发方式(脉冲电平触发和脉冲边沿触发)及触发特点;3.熟悉触发器的实际应用;4.了解并掌握Multisim仿真软件的使用。

二、实验设备数字实验电路箱,74LS74,导线若干,Multisim数电仿真软件。

74LS74引脚图 74LS74逻辑图三、实验原理U1A74LS74D 1D21Q5~1Q6~1CLR11CLK3~1PR4D 触发器在时钟脉冲CP 的前沿(正跳变0到1)发生翻转,触发器的次态n Q +取决于脉冲上升沿到来之前D 端的状态,即n Q +=D 。

因此,它具有置0、置1两种功能。

由于CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D 端的数据状态变化,不会影响触发器的输出状态。

R 和S 分别是决定触发器初始状态Q 的直接置0、置1端。

当不需要强迫置0、置1时,R 和S端都应置高电平(如接+5V 电源)。

74LS74、74LS175等均为上升沿触发的边沿触发器。

触发器的应用很广,可用作数字信号的寄存,移位寄存,分频和波形发生器等。

四、实验内容1.测试D 触发器的逻辑功能;2.构成异步分频器,构成2分频和4分频;3.构成同步分频器,构成2分频和4分频。

五、实验设计及实验仿真1.测试D 触发器的逻辑功能:(1)将74LS74的D S D R 端分别加低电平,观察并记录Q 端的状态;(2)令D S D R 端为高电平,D 端分别接高、低电平,用单脉冲做CP ,观察记录当CP 为0,上升,1,下降时Q 段状态的变化;(3)当D S D R 为高电平,CP=0(或CP=1),改变D 端状态,观察Q 端的状态是否变化;(4)得到74LS74D 触发器的功能测试表:D SD RCP D N Q1 N Q 0 1 * * 0 1 1 1 1 0 * * 0 0 1 0 1 1 上升 0 0 0 1 0 1 1 上升 1 0 1 1 1 1 1 0 * 0 0 1 1 111*0 0 112.构成计时分频器,构成2分频和4分频:仿真如图所示:得到实验结果图如图所示:3.构成同步分频器,构成2分频和4分频:仿真如图所示:得到实验结果图如图所示:六、实验思考实验结束后,我们对下述电路进行了验证:完成两位竞赛抢答电路,观察抢答电路的工作情况,分析工作原理。

D触发器的设计和仿真

D触发器的设计和仿真

D触发器是数字电路中常见的一种触发器,它可以用于存储一位二进

制数据。

设计和仿真一个D触发器需要以下步骤:

1.确定D触发器的功能需求:D触发器具有一个输入端D、一个时钟

端CLK和一个输出端Q。

当CLK上升沿到来时,D触发器会将输入D的值

存储到输出Q中。

2.设计D触发器的逻辑电路:根据D触发器的功能需求,我们可以设

计逻辑电路来实现。

一种常用的实现方式是使用两个锁存器构成的锁存器

电路。

3.实现逻辑电路的布局和布线:根据设计的逻辑电路,将电路图转化

为电路布局和布线图。

这一步需要考虑电路的物理尺寸和电连接的布局。

4.进行仿真:使用电路设计软件,如TINA等,将设计的电路进行仿真。

仿真可以验证电路的功能是否符合设计需求,并找出可能存在的问题。

5.优化电路设计:根据仿真结果,对电路进行优化。

可能需要对电路

的逻辑设计进行调整,或者改进布局和布线方式,以提高电路的性能。

6.进行电路验证:在优化后,再次进行仿真验证,确保电路的功能和

性能满足设计需求。

7.进行实际制作和测试:最后,将电路进行实际制作,并进行测试。

测试可以包括输入输出波形的测量、电路的稳定性测试等等。

总结:设计和仿真一个D触发器是一个大致的流程,通过逐步优化和

测试,可以得到一个满足设计需求的D触发器电路。

在设计和仿真的过程中,需要运用逻辑电路设计原理、电路布局和布线技术,以及仿真工具等。

通过不断的实验和验证,可以不断改进和优化电路设计,以获得更好的设计结果。

数字逻辑实验— 触发器的仿真

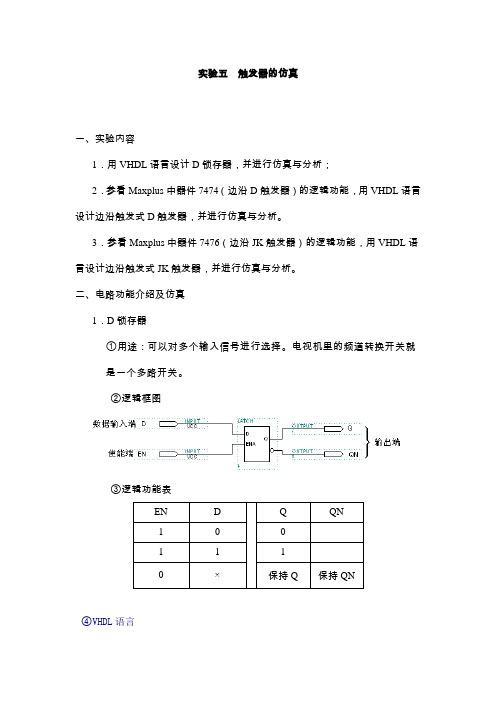

实验五触发器的仿真一、实验内容1.用VHDL语言设计D锁存器,并进行仿真与分析;2.参看Maxplus中器件7474(边沿D触发器)的逻辑功能,用VHDL语言设计边沿触发式D触发器,并进行仿真与分析。

3.参看Maxplus中器件7476(边沿JK触发器)的逻辑功能,用VHDL语言设计边沿触发式JK触发器,并进行仿真与分析。

二、电路功能介绍及仿真1.D锁存器①用途:可以对多个输入信号进行选择。

电视机里的频道转换开关就是一个多路开关。

②逻辑框图③逻辑功能表④VHDL语言library IEEE;use IEEE.std_logic_1164.all;entity D_latch isport(EN:in STD_LOGIC;d:in STD_LOGIC;nq,q:out STD_LOGIC-- qn:out STD_LOGIC);end D_latch;architecture bvh of D_latch is signal q_s,nq_s:STD_LOGIC; beginprocess(EN,d)beginif EN='1' thenq_s<=d;elsif EN='0' thenq_s<=q_s;nq_s<=nq_s;end if;q<=q_s;nq<=nq_s;end process;end bvh;⑤仿真波形图2.边沿式D触发器(Positive-Edge-Triggered D Flip-Flops with Preset , Clear and Complementary Outputs)①逻辑框图②逻辑功能表注:↑= Positive-going Transition③VHDL语言library IEEE;use IEEE.STD_LOGIC_1164.all;entity bianyan isport(prn,d,clk,clrn:in STD_LOGIC;q,qn:out STD_LOGIC);end bianyan;architecture bhv of bianyan issignal q_s,qn_s:STD_LOGIC;beginprocess(prn,d,clk,clrn)beginif (prn='0') and (clrn='1') thenq_s<='1';qn_s<='0';elsif (prn='1') and (clrn='0') thenq_s<='0';qn_s<='1';elsif (prn='0') and (clrn='0') thenq_s<='1';qn_s<='1';elsif (clk='1' and clk'event) thenif (d='1') thenq_s<='1';qn_s<='0';elsif (d='0') thenq_s<='0';qn_s<='1';end if;elsif (prn='1') and (clrn='1') and (clk='0') thenq_s<=q_s;qn_s<=qn_s;end if;q<=q_s;qn<=qn_s;end process;end bhv;④仿真波形图2.边沿式JK触发器①逻辑框图②逻辑功能表注:↓= Transition from high to low level③VHDL语言library IEEE;use IEEE.STD_LOGIC_1164.all;entity bianyanJK isport(prn,clk,clrn,J,K:in STD_LOGIC;q,qn:out STD_LOGIC);end bianyanJK;architecture bhv of bianyanJK issignal q_s,qn_s:STD_LOGIC;beginprocess(prn,clk,clrn,J,K)beginif (prn='0') and (clrn='1') thenq_s<='1';qn_s<='0';elsif (prn='1') and (clrn='0') thenq_s<='0';qn_s<='1';elsif (prn='0') and (clrn='0') thenq_s<='1';qn_s<='1';elsif(prn='1') and (clrn='1') thenif(clk='0' and clk'event) thenif(J='0') and (K='0') thenq_s<=q_s;qn_s<=qn_s;elsif(J='0') and (K='1') thenq_s<='0';qn_s<='1';elsif(J='1') and (K='0') thenq_s<='1';qn_s<='0';elsif(J='1') and (K='1') thenq_s<=not q_s;qn_s<=not qn_s;end if;elsif clk='1' thenq_s<=q_s;qn_s<=qn_s;end if;end if;q<=q_s;qn<=qn_s;end process;end bhv;④仿真波形图。

实验二D触发器的设计和仿真

告报验实哈尔滨工程大学教务处制实验二D触发器的设计和仿真一、实验目的1、学习模拟数字电路单元的基本设计方法。

2、学习Cadence工具下电路设计的基本操作和方法。

3、学习Sprectre工具的仿真操作方法。

二、实验内容. . . .本实验通过设计一个异步清零的D触发器电路学习Cadence工具下电路的设计和仿真方法。

实验内容包括:完成反相器、与非门、传输门电路的设计和仿真验证;完成各个单元电路symbol的建立;利用建立的单元电路symbol完成D触发器电路的设计和仿真;分析仿真结果。

该电路设计采用上华CSMC0.5umCMOS工艺设计,工作电压5V。

三、实验步骤、登陆到UNIX系统。

1在登陆界面,输入用户名和密码,用户名和密码都为学生学号。

2、Cadence的启动。

启动Cadence软件的命令有很多,不同的启动命令可以启动不同的工具集,常用的启动命令有icfb,icca等,也可以单独启动单个工具。

3、原理图的输入。

(1)Composer的启动。

在CIW窗口新建一个单元的Schematic视图。

(2)添加器件。

在comparator schematic窗口点击Add-Instance 或者直接点i,就可以选择所需的器件。

(3)添加连线。

执行Add-Wire,将需要连接的部分用线连接起来。

(4)添加管脚。

执行Add-Pin和直接点p,弹出添加管脚界面。

(5)添加线名。

为设计中某些连线添加有意义的名称有助于在 . . . . 波形显示窗口中显出该条线的信号名称,也可以帮助检查电路错误。

点击Add-Wire Name,弹出新窗口,为输入输出线添加名称。

为四端的MOS器件的衬底添加名称vdd!或gnd!,其中!表示全局变量。

(6)添加电源信号。

选择Vdd和Gnd的symbol各一个,在两个symbol 之间连接一个vdc,设置直流电压5V。

(6)保存并检查。

点击schematic窗口上的Check and Save按钮,察看是否有警告或者错误。

实验3-触发器的结构与仿真

2021

实验3 触发器电路结构与仿真

D触发器(不带复位端)

基于传输门的D锁存器

clk高电平期间,上面的TG导通,下面的TG断开,输入 信号D被传送到输出端;

clk低电平期间,上面的TG端口,下面的TG导通,双稳 态电路保持电路状态。

D触发器(不带复位端)

主从结构的D触发器:避免“空翻”问题

一对D锁存器可以构成一个正边沿触发式D触发器,这种电路只在控制时钟上 升沿到来的时刻采样D输入信号,并且据此改变Q和QN的输出。

D.CDL文件的编写

.SUBCKT DFF CK D Q QN//子电路定义开始语句,DFF为子电路参考名,后面四个 为子电路外部电路参考节点,不能为0,为局部变量。

XI0 CKB CK D net0 TG1G NL=0.28U NW=1.0U PL=0.28U PW=1.0U

XI1 net0 net1

IVG PL=0.28U PW=1.6U NL=0.28U NW=1.0U

XI2 net1 net2

IVG PL=0.28U PW=1.6U NL=0.28U NW=1.0U

XI3 CK CKB net2 net0 TG1G NL=0.28U NW=1.0U PL=0.28U PW=1.0U

XI4 CK CKB net1 net3 TG1G NL=0.28U NW=1.0U PL=0.28U PW=1.0U

MP0 D CKB Q VDD PCH W=PW L=PL//pmos器件 MN0 D CK Q GND NCH W=NW L=NL//nmos器件 .ENDS//子电路结束语句

.SUBCKT IVG A Z//子电路定义开始语句,IVG为子电路参考名,CMOS 反相器

数字逻辑设计-用5种不同方法说明D锁存器与D触发器的功能作用(纯原创)

1)用五种不同的方法描述D锁存器和D触发器的功能;2)锁存器和触发器进入无法预期状态(亚稳态)的原因分析;3)下载D触发器和D锁存器的规格说明PDF,理解动态参数的含义,分析这些定时参数与无法预期状态(亚稳态)的联系;4)对D锁存器和D触发器的功能进行波形仿真分工:1.1此处我们发现了6种方法,分别是功能的文字叙述、功能表、状态转移真值表、特征方程、状态图、时序图,下面进行详细介绍。

方法一:功能的文字叙述●D锁存器:功能分析文字描述:C = 0时,输出状态保持不变;C = 1时,输出随输入状态而改变。

●D触发器:功能分析文字描述:CLK=0时,主锁存器工作,接收输入信号Qm = D;从锁存器不工作,输出Q 保持不变。

CLK=1时,主锁存器不工作,Qm 保持不变;从锁存器工作,将Qm 传送到输方法二:功能表●D锁存器功能表D触发器功能表方法三:状态转移真值表●D锁存器状态转移真值表D触发器状态转移真值表方法四:特征方程●D锁存器特征方程:Q n+1 = D(C=1)●D触发器特征方程:Q n+1 = D方法五:状态图●D锁存器状态图●D锁存器状态图方法六:时序图●D锁存器时序图●D触发器时序图1.2什么是亚稳态:亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。

当一个触发器进入亚稳态引时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。

在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

●锁存器进入亚稳态的原因:⏹对于S-R锁存器:1.当S=R=1,然后同时取消时;2.当S和R端输入信号脉冲宽度过窄时;3.当S和R端输入信号同时取反时;均会出现亚稳态。

⏹对于D触发器:当输入信号脉冲宽度过窄时,会进入亚稳态。

●触发器进入亚稳态的原因:在同步系统中,如果触发器的建立时间(setup time)/保持时间(hold time)不满足要求,就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端毛刺、振荡、固定的某一电压值,而不是等于数据输入端D的值。

D触发器教程PPT课件

一、边沿触发器功能分类

1. JK 型触发器

定义 在CP作用下,J、K取值不同时, 具有保持、置0、

置1、翻转功能的电路,都叫做JK型时钟触发器。

符号

特性表

特性方程

Q

Q

1J C1 IK

J K Q n+1 功能 0 0 Q n 保持

0 1 0 置0

Qn1JQnKQn

CP下降沿 时刻有效

J CP K

1 0 1 置1

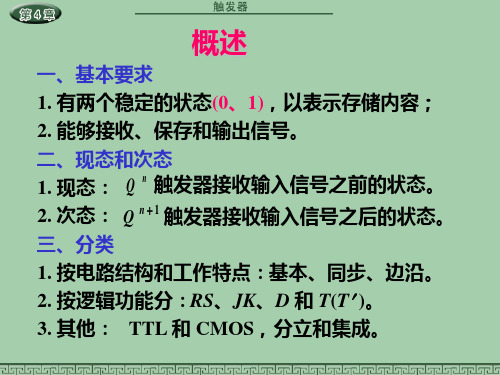

概述

一、基本要求 1. 有两个稳定的状态(0、1),以表示存储内容; 2. 能够接收、保存和输出信号。 二、现态和次态

1. 现态: Q n 触发器接收输入信号之前的状态。 2. 次态: Q n 1 触发器接收输入信号之后的状态。

三、分类 1. 按电路结构和工作特点:基本、同步、边沿。

2. 按逻辑功能分:RS、JK、D 和 T(T )。

若高电平同时撤消,则状态不定。

Q

G1 >1

Q 波S

>1 G2

形 图

R

Q

R

S

Q

三、特性表和特性方程

四、基本 RS 触发器主

R S Q n+1

要特点

0 0 Q n 保持 1. 优点:结构简单,

0 1 1 置 1 具有置 0、置 1、保持功能。

1 0 0 置0 1 1 不用 不许 Q n+1= S + RQ n

1 1 Q n 翻转

2. D 型触发器

定义 在CP作用下,D 取值不同时, 具有置0、置1 功能的电路,都叫做 D 型时钟触发器。

符号

Q

Q

1D C1

D CP

特性表

D Q n+1 功能

d触发器的建模方法

d触发器的建模方法d触发器是数字电路中常用的一种触发器类型,用于存储和控制数字信号。

在数字电路的设计和建模中,d触发器的建模方法是十分重要的。

本文将介绍d触发器的建模方法,并讨论其应用和优势。

我们来了解一下d触发器的基本原理。

d触发器是一种时序电路,它包含一个存储器单元和一个时钟信号。

d触发器的输出取决于其输入和时钟信号的状态。

当时钟信号发生变化时,d触发器会根据输入信号的状态决定输出信号的状态。

d触发器可以用于存储单个比特的数据,并在时钟信号的边沿进行更新。

在建模d触发器时,我们可以使用逻辑门来实现其功能。

最常见的方法是使用两个与门和一个非门来构建d触发器。

其中,一个与门用于存储输入信号,另一个与门用于存储时钟信号。

非门则用于反转输出信号,以实现数据的存储和更新。

在建模d触发器时,我们需要确定输入和输出的逻辑关系。

一般来说,d触发器的输出取决于当前时钟信号的状态和前一个时钟信号的状态。

具体而言,当时钟信号从低电平变为高电平时,d触发器会根据当前输入信号的状态更新输出信号的状态。

当时钟信号从高电平变为低电平时,d触发器会保持输出信号的状态不变。

这种建模方法可以确保d触发器在时钟信号的边沿进行数据的存储和更新。

除了基本的d触发器模型外,还有其他一些扩展模型可以实现更复杂的功能。

例如,带有使能信号的d触发器可以控制数据的存储和更新,使其在特定条件下才进行操作。

另外,带有预置和清零功能的d触发器可以在特定的输入信号下进行数据的预置和清零操作。

在数字电路设计和建模中,d触发器有着广泛的应用。

它可以用于存储和控制数据,实现时序逻辑功能。

例如,在计数器和状态机的设计中,d触发器可以用于存储和更新状态信息。

此外,d触发器还可以用于时钟信号的同步和分频,实现精确的时序控制。

相比其他触发器类型,d触发器具有一些优势。

首先,d触发器的建模和设计比较简单,易于理解和实现。

其次,d触发器的时序特性使其适用于各种时序逻辑应用,具有较高的灵活性和可靠性。

D触发器的设计和仿真

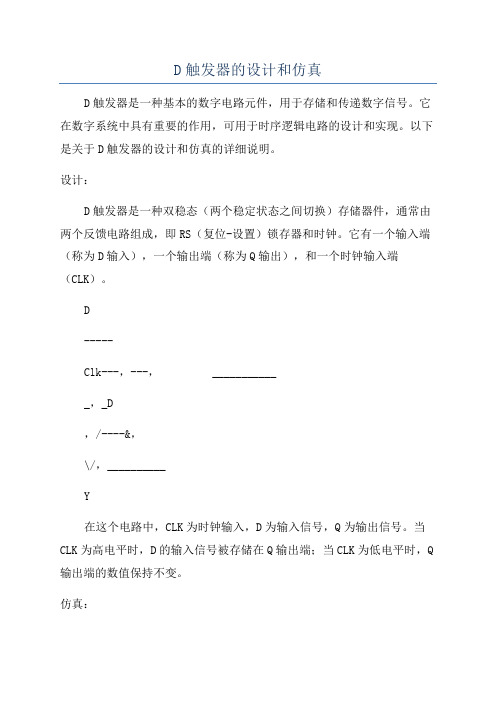

D触发器的设计和仿真D触发器是一种基本的数字电路元件,用于存储和传递数字信号。

它在数字系统中具有重要的作用,可用于时序逻辑电路的设计和实现。

以下是关于D触发器的设计和仿真的详细说明。

设计:D触发器是一种双稳态(两个稳定状态之间切换)存储器件,通常由两个反馈电路组成,即RS(复位-设置)锁存器和时钟。

它有一个输入端(称为D输入),一个输出端(称为Q输出),和一个时钟输入端(CLK)。

D-----Clk---,---, ____________,_D,/----&,\/,__________Y在这个电路中,CLK为时钟输入,D为输入信号,Q为输出信号。

当CLK为高电平时,D的输入信号被存储在Q输出端;当CLK为低电平时,Q 输出端的数值保持不变。

仿真:可以使用电路仿真工具来验证和验证D触发器的设计。

其中最常用和广泛使用的电路仿真工具是Spice(Simulation Program with Integrated Circuit Emphasis)。

在Spice中,可以使用硬件描述语言(HDL)来描述电路的连接和元件属性。

以下是一个基于Spice的D触发器仿真的示例代码:```*D触发器M1QCLKVDD0CMOSPL=1uW=0.5uM2QD0VDDCMOSPL=1uW=0.5uM3DCLKGNDGNDCMOSNL=1uW=0.5uR1QOUT1kV1CLK0DC5VV2 D 0 PULSE 0 5 0 50ns 50ns 20us 40us.tran 0.1ns 100us.end```在这个示例中,M1、M2和M3分别代表CMOSP(pMOS)和CMOSN (nMOS)开关,并使用L和W定义它们的尺寸。

R1是输出端电阻,V1和V2分别是时钟输入端和D输入端的电压源。

通过运行这个Spice仿真文件,可以获得D触发器的输入和输出波形,以验证其功能和性能。

总结:。

D触发器的设计和仿真报告

D触发器的设计和仿真报告D触发器是数字逻辑电路中常用的元件,用于存储和传输二进制数据。

本文介绍了D触发器的设计和仿真报告。

首先,我们需要了解D触发器的功能和原理。

D触发器有一个数据输入端D,一个时钟输入端CLK和两个输出端Q和/Q。

当时钟输入端出现上升沿时,D触发器会将输入端的数据D存储到输出端Q中。

即当CLK=1时,Q的值等于D的值。

当CLK=0时,D触发器保持原来的状态,不进行任何操作。

接下来,我们将进行D触发器的设计。

设计D触发器的方法有很多种,其中比较常用的是使用逻辑门和锁存器。

以D触发器的JK触发器为例,我们可以使用逻辑门和多路选择器来实现。

首先,我们可以使用与非门和与门来实现JK触发器的两个与门和一个与非门。

然后,我们可以使用多路选择器将两个与门和一个与非门的输出进行选择,从而实现JK触发器。

在实际设计中,我们需要根据要求确定输入输出的位宽,以及时钟的频率。

根据设计的要求,我们可以选择适合的逻辑门和多路选择器。

接下来,我们进行D触发器的仿真。

仿真可以帮助我们验证设计的正确性和性能。

可以使用仿真软件来进行仿真。

在仿真过程中,我们可以设置不同的输入来检查D触发器的输出是否符合我们的预期。

如果输出和预期不一致,我们可以根据仿真结果进行调试和优化。

在D触发器的仿真过程中,我们可以检查以下几个方面:1.输入的变化:可以检查D触发器对不同输入的响应情况,包括输入的变化速度和输入信号的稳定性。

2.时钟的频率:可以检查D触发器在不同时钟频率下的性能,包括是否出现时钟滞后和时钟失真等问题。

3.输出的变化:可以检查D触发器的输出是否符合设计要求,包括输出的稳定性和电平的准确性。

4.延迟和功耗:可以评估D触发器的延迟和功耗,并与设计要求进行比较。

通过仿真,我们可以评估D触发器的性能并做出相应的调整和优化。

可以根据仿真结果进行电路的修改和重新设计,以达到预期的功能和性能要求。

总结起来,D触发器的设计和仿真是数字电路设计过程中的重要环节。

d触发器与非门设计模10

d触发器与非门设计模拟1. 引言在数字电子技术中,触发器是一种重要的电子元件,用于存储和处理信息。

d触发器作为最简单且常用的一种触发器,具有广泛的应用。

本文将介绍d触发器的原理和设计模拟,并讨论非门的实现方法。

2. d触发器的原理d触发器是一种存储器件,用于存储和传输数字信息。

它具有一个输入端d和两个输出端q和q’。

d触发器的状态取决于输入信号d和时钟信号的变化。

在上升沿或下降沿时,输入端d的值被传递到输出端q,使得q的值与d相等。

d触发器可以分为边沿触发器和级沿触发器。

2.1 边沿触发器边沿触发器在时钟信号的上升沿或下降沿时更新其状态。

常见的边沿触发器包括d 触发器、JK触发器和T触发器。

根据时钟信号的上升沿或下降沿更新状态的性质,d触发器可以进一步分为正边沿触发器和负边沿触发器。

在正边沿触发器中,输入信号d在上升沿时被传递到输出端q;在负边沿触发器中,输入信号d在下降沿时被传递到输出端q。

2.2 级沿触发器级沿触发器根据时钟信号的边沿更新其状态。

常见的级沿触发器包括D触发器、JK 触发器和T触发器。

d触发器是最简单且常用的级沿触发器。

它通过给定的时钟信号来将输入信号d传输到输出端q。

d触发器有两个稳定状态,它的输出保持不变,直到时钟信号发生变化。

3. d触发器的设计模拟为了实现d触发器的功能,我们可以使用基本逻辑门来构建它。

常用的逻辑门包括与门、或门、非门和异或门。

3.1 与门与门是基本的逻辑门之一。

它有两个输入端和一个输出端。

当且仅当所有输入端都为高电平时,输出端才为高电平。

我们可以使用与门来实现d触发器的布尔表达式。

d触发器的布尔表达式为:q(t+1) = d可以使用与门来实现该布尔表达式。

将输入端d和时钟信号连接到与门的输入端,并将与门的输出端连接到输出端q。

这样,在时钟信号的边沿触发下,输入信号d的值将被传输到输出端q。

3.2 非门非门是基本的逻辑门之一。

它有一个输入端和一个输出端。

D触发器的设计和仿真

D触发器的设计和仿真

D触发器是一种常用的数字逻辑电路元件,用于存储和传输二进制数据。

它由两个非门和两个与非门组成,有时也称为双稳态门。

首先,确定逻辑功能和时序要求是设计D触发器的基础。

D触发器的

逻辑功能是将输入数据按时钟脉冲传输到输出端,因此需要确定输入和输

出的逻辑关系。

时序要求包括时钟频率、输入数据的稳定时间和输出数据

的保持时间等参数。

接下来,进行电路结构设计。

D触发器的电路结构可以采用多种形式,如RS触发器、JK触发器和D触发器等。

其中D触发器是最常用的一种,

它由两个非门和两个与非门组成。

根据逻辑功能和时序要求,可以选择合

适的D触发器结构。

然后,进行电路仿真和验证。

仿真可以使用电路仿真工具,如Verilog、VHDL等进行。

通过设置输入数据、时钟频率等参数,可以模拟

D触发器的工作过程,并得到输出数据。

仿真结果可以与设计要求进行比较,以验证电路的正确性和性能。

在进行电路仿真和验证时,还需要考虑各种因素对电路性能的影响。

例如,输入信号的时序关系、电路的时钟延迟和噪声等。

这些因素可能导

致D触发器的工作不稳定或出现误差,因此需要进行充分的分析和测试。

总之,设计和仿真D触发器是数字逻辑电路设计的一个重要环节。

通

过合理的设计和充分的仿真验证,可以确保D触发器的正确性和性能。

D触发器电路设计

D触发器电路设计D触发器是数字电路中常用的一种触发器。

它采用两个互补反相的输入信号,根据输入信号的状态变化来改变输出信号的状态。

本文将详细介绍D触发器电路的设计过程。

首先,我们需要确定D触发器的功能需求和工作频率。

D触发器的功能是根据D输入信号的状态(高电平或低电平)来决定输出信号的状态(保持或反转)。

工作频率是指触发器每秒处理的信号个数,通常以赫兹(Hz)表示。

接下来,我们需要选择合适的逻辑门作为D触发器的基本构建模块。

常见的逻辑门有与门(AND)、或门(OR)、非门(NOT)和异或门(XOR)等。

根据功能需求,我们可以选择不同的逻辑门来实现D触发器。

以D触发器的最简单形式,RS触发器为例,其实现方式如下:1.使用两个非门构成RS触发器的RS(重置和置位)输入端。

2.将D输入信号连接到RS触发器的S(置位)输入端。

3.将D输入信号取反连接到RS触发器的R(重置)输入端。

RS触发器的真值表如下:```D,R,S,Q(t),Q(t+1)---------------------------------0,0,1,0,00,1,0,0,11,0,0,1,01,1,1,x,x```其中,Q(t)表示触发器当前状态,Q(t+1)表示触发器下一个状态。

x 表示无效状态。

接下来,我们需要根据RS触发器的实现方式进行电路设计。

设计过程包括电路连接方式、逻辑门选择和信号线路布局等。

1.连接方式:根据RS触发器的实现方式,将D输入信号连接到RS触发器的S(置位)输入端,并将D输入信号取反连接到RS触发器的R(重置)输入端。

2.逻辑门选择:根据RS触发器的实现方式,使用两个非门作为RS触发器的RS输入端。

非门的输入端分别连接到D输入信号和D输入信号的反相信号。

3.信号线路布局:根据电路图设计合理的信号线路布局,保证信号传输的稳定性和可靠性。

可以使用导线或者线缆来连接逻辑门和触发器。

最后,我们需要进行电路测试和优化。

(Multisim数电仿真)D触发器及应用

实验3.9 D 触发器及应用一、实验目的:1.了解边沿D 触发器的逻辑功能和特点。

2.掌握D 触发器的异步置0和异步置1端的作用。

3.了解用D 触发器组成智力抢答器的工作原理。

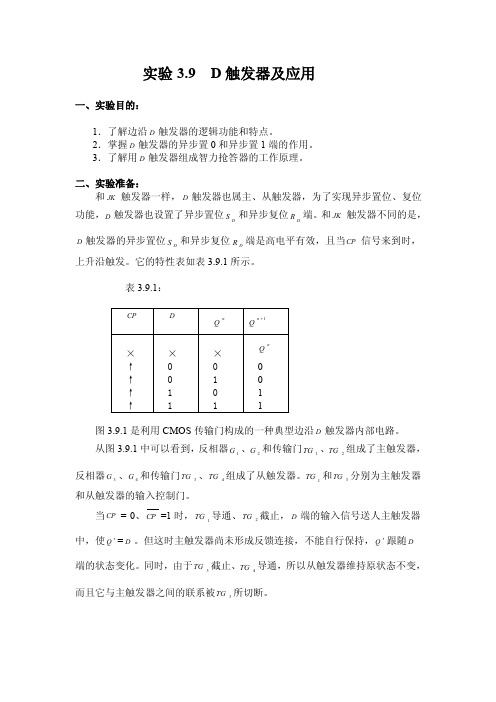

二、实验准备:和JK 触发器一样,D 触发器也属主、从触发器,为了实现异步置位、复位功能,D 触发器也设置了异步置位D S 和异步复位D R 端。

和JK 触发器不同的是,D触发器的异步置位D S 和异步复位D R 端是高电平有效,且当CP 信号来到时,上升沿触发。

它的特性表如表3.9.1所示。

表3.9.1:图3.9.1是利用CMOS 传输门构成的一种典型边沿D 触发器内部电路。

从图3.9.1中可以看到,反相器1G 、2G 和传输门1TG 、2TG 组成了主触发器,反相器3G 、4G 和传输门3TG 、4TG 组成了从触发器。

1TG 和3TG 分别为主触发器和从触发器的输入控制门。

当CP = 0、CP =1时,1TG 导通、2TG 截止,D 端的输入信号送人主触发器中,使Q '=D 。

但这时主触发器尚未形成反馈连接,不能自行保持,Q '跟随D 端的状态变化。

同时,由于3TG 截止、4TG 导通,所以从触发器维持原状态不变,而且它与主触发器之间的联系被3TG 所切断。

图3.9.1当CP 的上升沿到达时(即CP 跳变为1、CP 跳变为0),1TG 截止、2TG 导通。

由于门1G 的输入电容存储效应,1G 输入端的电压不会立刻消失,于是Q '在1TG 切断前的状态被保存下来。

同时,由于3TG 导通、4TG 截止,主触发器的状态通过3TG和3G 送到了输出端,使=QQ '=D (CP 上升沿到达时D 的状态)。

可见,这种触发器的动作特点是输出端状态的转换发生在CP 的上升沿,而且触发器所保存下来的状态仅仅取决于CP 上升沿到达时的输入状态。

因为触发器输出端状态的转换发生在CP 的上升沿,所以这是一个上升沿触发边沿触发器。

D触发器及其应用

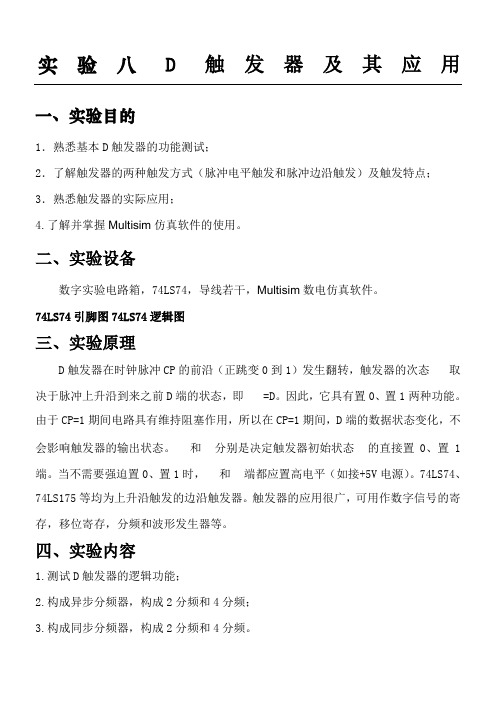

实验八D触发器及其应用一、实验目的1.熟悉基本D触发器的功能测试;2.了解触发器的两种触发方式(脉冲电平触发和脉冲边沿触发)及触发特点;3.熟悉触发器的实际应用;4.了解并掌握Multisim仿真软件的使用。

二、实验设备数字实验电路箱,74LS74,导线若干,Multisim数电仿真软件。

74LS74引脚图74LS74逻辑图三、实验原理D触发器在时钟脉冲CP的前沿(正跳变0到1)发生翻转,触发器的次态取决于脉冲上升沿到来之前D端的状态,即=D。

因此,它具有置0、置1两种功能。

由于CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D端的数据状态变化,不会影响触发器的输出状态。

和分别是决定触发器初始状态的直接置0、置1端。

当不需要强迫置0、置1时,和端都应置高电平(如接+5V电源)。

74LS74、74LS175等均为上升沿触发的边沿触发器。

触发器的应用很广,可用作数字信号的寄存,移位寄存,分频和波形发生器等。

四、实验内容1.测试D触发器的逻辑功能;2.构成异步分频器,构成2分频和4分频;3.构成同步分频器,构成2分频和4分频。

五、实验设计及实验仿真1.测试D 触发器的逻辑功能:(1)将74LS74的D S D R 端分别加低电平,观察并记录Q 端的状态;(2)令D S D R 端为高电平,D 端分别接高、低电平,用单脉冲做CP ,观察记录当CP 为0,上升,1,下降时Q 段状态的变化;(3)当D S D R 为高电平,CP=0(或CP=1),改变D 端状态,观察Q 端的状态是否变化;(4)得到74LS74D 触发器的功能测试表:2.构成计时分频器,构成2分频和4分频:仿真如图所示: 得到实验结果图如图所示:3.构成同步分频器,构成2分频和4分频:仿真如图所示:得到实验结果图如图所示:六、实验思考实验结束后,我们对下述电路进行了验证:完成两位竞赛抢答电路,观察抢答电路的工作情况,分析工作原理。

经过试验可得以下真值表:当主控1Rd=2Rd=0时,1D和2D置1置0都不会亮。

d触发器实验报告

d触发器实验报告D 触发器实验报告一、实验目的本次实验的主要目的是深入理解 D 触发器的工作原理,掌握其逻辑功能和特性,并通过实际操作和测试,学会使用相关仪器设备进行电路搭建和性能分析。

二、实验原理1、 D 触发器的定义与逻辑符号D 触发器是一种具有存储功能的数字电路元件,它能够在时钟脉冲的上升沿或下降沿将输入的数据(D 端)锁存到输出端(Q 端)。

其逻辑符号通常包括数据输入端(D)、时钟输入端(CLK)、输出端(Q 和\(\overline{Q}\))以及置位端(SET)和复位端(RESET)。

2、工作原理当时钟脉冲为低电平时,D 触发器保持原来的状态不变。

当时钟脉冲上升沿到来时,如果 D 端为高电平,则 Q 端输出高电平;如果 D 端为低电平,则 Q 端输出低电平。

3、特性方程\(Q^{n + 1} = D\)(在时钟上升沿时)三、实验仪器与设备1、数字电路实验箱提供电源、逻辑电平输入和输出接口,以及各种数字芯片的插槽。

2、示波器用于观察时钟脉冲和输出信号的波形,以分析电路的工作情况。

3、数字万用表用于测量电路中的电压、电流等参数,检查电路的连接是否正常。

4、 74LS74 双 D 触发器芯片本次实验所使用的核心芯片,具有两个独立的 D 触发器。

四、实验内容及步骤1、电路搭建按照实验原理图,在数字电路实验箱上插入 74LS74 芯片,并使用导线将其与电源、地、时钟脉冲源以及逻辑电平输入和输出端连接起来。

确保电路连接正确无误,避免短路和断路现象。

2、功能测试(1)将 D 端分别接高电平和低电平,观察在时钟脉冲上升沿作用下,Q 端输出的变化情况。

(2)使用示波器同时观察时钟脉冲和 Q 端输出的波形,验证 D 触发器的工作特性。

3、置位和复位功能测试(1)通过置位端(SET)和复位端(RESET)将 D 触发器强制置为高电平或低电平,观察 Q 端的输出状态。

(2)在置位或复位操作后,再次改变 D 端的输入电平,观察在时钟脉冲作用下 Q 端的输出是否受到影响。

D触发器

基于 CMOS 的 D 触发器的设计一、设计目的:1、进一步熟悉cadence软件的使用;2、掌握cadence的原理图编辑及修改方法;3、掌握cadence前仿的参数设置和方法;4、掌握D触发器的功耗、截止频率和瞬态仿真。

二、设计和原理:触发器是一个具有记忆功能的二进制信息存储器件,是构成多种时序电路的最基本逻辑单元。

D触发器在CLK 有效电平期间将D的状态输出。

用CMOS 做器件是集成电路的发展方向。

本次实验设计是用MOS 器件设计一个D触发器。

通过D触发器的功能设计电路图,再转换为MOS 器件的电路。

设计主要是根据D触发器的特性来设计的。

根据它的特性表画原理图D触发器的功能表如下;当CLK = 1 时触发器的Q*=D;当CLK = 0,触发器将保持不变,即Q*=Q。

D触发器的原理图:和主要参数:三、设计仿真:1、瞬态仿真①放参数设置②仿真结果2、功耗仿真①电流波形②平均电流值③功耗 P=U*I=1.8V*1.2094E-4=0.217692mW. 3.最高截止频率仿真Fmax=1/340p=2.94E8hz通过仿真验证,电路设计符合逻辑关系,完全正确的四、版图设计:五、实验总结;通过本次设计训练,使我对集成设计的基本流程有了进一步的了解,操作、动手能力方面也得到了很大的提高,熟悉并掌握了cadence的基本操作;但是在布线的时候出了问题,没能做出后面的工序,很是遗憾啊!希望在以后的学习中我能做到更好!由于MOS 器件内部有电容存在,所以信号的传输会有延时,而且各个器件的延时会进行叠加,这对输出的特性有很大的影响,有时会造成致命的错误,这对器件的使用范围会有制约,这是所不允许的。

通过电路原理图的调整可以解决一定的问题。

这个问题没有办法完全的解决。

这是因为器件的制造工艺的约束。

MOS 管的宽长比对MOS 电路的性能起着非常重要的作用。

因此在每个管子的选择都需要慎重。

对于怎样选择各个管子的参数目前还不知道有什么有效的简便的方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一、D触发器的设计和仿真

一、实验目的

1、学习模拟数字电路单元的基本设计方法。

2、学习Cadence工具下电路设计的基本操作和方法。

3、学习Sprectre工具的仿真操作方法。

二、实验内容

本实验通过设计一个异步清零的D触发器电路学习Cadence工具下电路的设计和仿真方法。

实验内容包括:完成反相器、与非门、传输门电路的设计和仿真验证;完成各个单元电路symbol的建立;利用建立的单元电路symbol完成D 触发器电路的设计和仿真;分析仿真结果。

该电路设计采用上华CSMC0.5umCMOS 工艺设计,工作电压5V。

三、实验步骤

1、登陆到UNIX系统。

在登陆界面,输入用户名和密码,用户名和密码都为学生学号。

2、Cadence的启动。

启动Cadence软件的命令有很多,不同的启动命令可以启动不同的工具集,常用的启动命令有icfb,icca等,也可以单独启动单个工具。

3、原理图的输入。

(1)Composer的启动。

在CIW窗口新建一个单元的Schematic视图。

(2)添加器件。

在comparator schematic窗口点击Add-Instance或者直接点i,就可以选择所需的器件。

(3)添加连线。

执行Add-Wire,将需要连接的部分用线连接起来。

(4)添加管脚。

执行Add-Pin和直接点p,弹出添加管脚界面。

(5)添加线名。

为设计中某些连线添加有意义的名称有助于在波形显示窗口中显出该条线的信号名称,也可以帮助检查电路错误。

点击Add-Wire Name,弹出新窗口,为输入输出线添加名称。

为四端的MOS器件的衬底添加名称vdd!或gnd!,其中!表示全局变量。

(6)添加电源信号。

选择Vdd和Gnd的symbol各一个,在两个symbol之间连接一个vdc,设置直流电压5V。

(6)保存并检查。

点击schematic窗口上的Check and Save按钮,察看是否有警告或者错误。

如果有,察看CIW窗口的提示。

4、电路仿真。

(1)启动模拟仿真环境。

在comparator schematic窗口,选择Tools-Analog Environment,弹出模拟仿真环境界面。

(2)选择仿真器。

在仿真窗口,选择Setup-Simulator/Directory/Host,设置仿真器为spectre,然后点击OK。

(3)设置模型库。

(4)设置分析类型。

在仿真窗口,点击Choose Analyses按钮,弹出Choose Analyses窗口,该窗口中列出了各种仿真类型,在本实验中只需进行瞬态仿真,所以选择tran,时间设为3um。

(5)设置设计变量,在仿真窗口中,点击Edit Variables 按钮,弹出变量设置窗口,点击Copy From按钮,整个设计本扫描一遍,设计中的各个变量被列出来。

(6)创建网表。

选择Simulation-Netlist-Create,产生了该设计的网表。

(7)设置波形显示工具。

Cadence中有两种波形显示工具:AWD和wavescane,在仿真窗口选择Session-assign,在弹出的窗口中可以选择波形显示工具为AWD或wavescane。

(8)选择输出结果显示信号。

(9)进行仿真。

选择Simulation-Run,或者直接点击仿真窗口右下角的Run 按钮来启动仿真,仿真开始过程中,在CIW窗口会出现一系列仿真信息,另外会弹出一个Spectre输出窗口。

仿真结束会自动弹出波形显示窗口。

(10)观察波形,看是否满足设计要求。

重复以上步骤完成反相器、传输门、与非门和D触发器电路的设计和仿真。

四实验结果

反相器二输入与非门

传输门

DFF

五.实验结果分析

通过本实验,我学习了利用半导体器件设计电路的方法和软件构图的一些技巧。

并学会了如何将已经绘制成功的电路图进行仿真,通过查看波形来检测电路是否达到设计要求。

实践了书本中学习的知识,加深了对已有知识的理解。

实验二、带异步清零的边沿触发D触发器版图设计

一、实验目的

1、学习Cadence工具下电路设计的基本操作和方法。

2、学习Layout Editor工具下版图设计的基本操作和方法。

3、学习Dracula工具的版图验证方法。

二、实验内容

本实验通过反相器、与非门和D触发器的版图设计学习使用Cadence Layout Editor工具进行版图设计验证的操作和方法。

实验内容包括:使用Cadence Layout Editor完成反相器和与非门版图的绘制;完成D触发器版图绘制,使用Dracula工具完成版图验证。

本实验采用CSMC0.5um CMOS工艺设计。

三、实验步骤

(1)工艺库的生成。

点击CIW中的File菜单选择其中的New项中的Library项,在弹出窗口的Name项中输入所需的名字,点击ok,在弹出的对话框中输入编好的技术文件名my.tf,点击ok。

(2)连接设计库到工艺库。

(3)启动版图设计工具Vituoso Layout Editor。

有很多种方法自动版图大师,最简单的办法是通过CIW打开或者新建一个单元的版图视图,这样就会自动启动版图大师。

(4)从LSW窗口中选择所需的层,在显示部分完成反相器和与非门版图绘制。

低压管画法见下图:

SN

SP

低压P 管

低压N 管

3、版图验证

(1)导出版图:在CIW 窗口中,File->export->stream, library browser 找到要检查的Layout ,Run direction: ./dracula.(dracula 文件夹要放在当前工作库下),output :文件名.gds ;options: case sensitivity->preserve ;user defined data: geometry ,Layer Map Table ,输入map 文件的路径。

(2)修改drc 文件:在终端里运行,cd dracula ;vi drc.rul 修改dracula 文件夹里

TB TO

A1

LVTO_M1

GT

SP

SN

TO

GT

A1 LVTO_M1

的drc.rul文件,indisk=文件名.gds,primary=文件名, program-dir前加分号;(3)运行drc:输入PDRACULA); :/get drc.rul; :/finish; : ./(./表示运行本路径下的该执行文件)。

(4)查找错误:回到版图文件,Tools->Dracula Interactive, DRC->setup, 路径输入./dracula。

出现错误后,点中错误,然后Fix current error,可看到错误的具体位置。

DRC里quit后,根据错误对版图进行修改,然后再导出gds文件,最后到终端再运行P(或PDRACULA); :/g drc.rul;:/fi;: (或/)。

四、实验结果

给出绘制的反相器,与非门,传输门,D触发器版图

反相器

二输入与非门

传输门DFF

五、实验总结

通过这次实验,我学会了软件来绘制版图,加深了对工艺的理解,也更加深入学习了电路,管子结构,电路及版图连接,增加了对集成电路设计这门课程的兴趣,更学到了很多相关知识技能。