几个常用的Verilog小程序

6款宝藏微信小程序推荐,一个比一个好用,听歌,文字识别全都一网打尽!

6款宝藏微信小程序推荐,一个比一个好用,听歌,文字识别全都一网打尽!吐司工具箱这是一款聚合类的工具箱,简单来说,就是一个软件囊括了很多实用工具。

具体来说里面有图片工具、休闲工具、学习工作、IT工具等四大类,30多个小工具,基本能满足日常大多数场景的使用需求。

所有的工具都可以免费使用,但是如果是带红点的工具箱,则需要先看一次广告,以后再使用就可以直接进入了。

像是里面的表情制作,就有丰富的表情包,喜欢斗图的小伙伴有福了~另外还有文字转语音,抖音去水印,虚拟来电,二维码生成,在线翻译,网络测速等功能,说是百宝箱也不为过~付费音乐这是一款强大的小程序,可以免费下载各种类型的付费音乐。

像是陈奕迅的孤勇者,提供了超多的版本,我们随机点击一个进去,即可进入下载界面。

点击下载文件,会自动复制一个链接,我们点击浏览器打开链接,会出现下载界面,点击立即下载即可。

另外如果想听某个歌手的歌曲,只要输入歌手名字,就会出现相应的歌曲,比如我们的杰伦哥,随便一搜,就有接近2000个结果~ 迅捷PDF转换器这是一款功能丰富的免费PDF转换工具,它的功能丰富。

像是PDF转Word,PDF转PPT等都可以完美解决。

另外像是PDF加密压缩合并等文档处理,它也可以轻松解决。

如果想要更加专业化的功能,这里建议大家下载它的专业APP,功能更加全面,支持大文件的转换和语音识别等特色功能。

历史价格查询这个小程序实在是买买党的必备神器,它可以查看京东和淘宝某个链接的历史价格。

对于一些像618、双十一的活动还是非常实用的,毕竟某些商家可喜欢一些“明降暗升”的猫腻,我们只需把链接复制黏贴在里面查查就知道,到底是不是真的实惠~猜画小歌这是谷歌出品的一款融合了计算机视觉技术的人工智能微信小程序。

在这个小程序中,你可以和小程序中的 AI 组队,在有限的时间内进行速写。

在规定的时间内,根据名词勾勒出对应的图画,AI 则需要在时间结束前猜出图画中的物体。

作为闲暇时的放松还是非常不错的。

十个常用的verilong小程序

十个常用的verilong小程序三角波信号发生器代码module triangle(clk,rst,out);input clk,rst;output[5:0] out;reg[5:0] out;reg[5:0] num;reg temp;always@(posedge clk,posedge rst) beginif(rst) num<=6'd0;else if(temp==1'b0)beginif(num==6'b111111) temp<=1'b1; else num<=num+6'd1;endelse if(num==6'd0) temp<=1'b0; else num<=num-6'd1;endalways@(num)out<=num;endmodule并串转换代码module ps(ina,inb,inc,ind,rst,clk,out); input ina,inb,inc,ind;input clk,rst;output out;reg[1:0] count;reg out;always@(posedge clk)beginif(rst)begincase(count)2'b00: out<=ind;2'b01: out<=inc;2'b10: out<=inb;2'b11: out<=ina;endcasecount=count+2'd1;endelse count=2'd0;endendmodule串并转换代码module sp(a,rst,va,vb,vc,vd,clk); input clk,rst;input[3:0] a;output va,vb,vc,vd;reg va,vb,vc,vd;always@(posedge clk)if(!rst)beginva<=0;vb<=0;vc<=0;vd<=0;endelse beginva<=a;vb<=va;vc<=vb;vd<=vc;endendmodule选通器代码module sample(q,a,b,sel,clk,resetn); input a,b,clk,sel,resetn;output q;wire c;reg q;always@(clk or resetn)beginif (resetn==1)q=0;else q=c;endassign c=(sel)?a:b;endmodule二选一选择器代码module muxtwo(a,b,sl,out);input a,b,sl;output out;reg out;always@(a,b,sl)if(!sl)out=a;else out=b;endmodule加法器代码module adder(court,sum,a,b,cin); input[2:0] a,b;input cin;output[2:0] sum;output court;assign{court,sum}=a+b+cin; endmodule比较器代码module compare(a,b,out);input a,b;output out;reg out;always@(a or b)out=(a==b)?1:0;endmoduleSR锁存器module SR_FF (Q, Q_n,S,R); output Q, Q_n; //端口声明input S,R;nand n1(Q, S,Q_n);nand n2(Q_n,R,Q); endmodule三态门设计电路module trist(in,ena,out);input in,ena;output out;assign out=ena?in:'bz; endmoduleJK触发器代码module JK(j,k,clear,clk,Q);input j,k,clear,clk;output Q;reg Q;always@(posedge clk )if(clear)Q=0;else beginif({j,k}==2'b11) ;else if({j,k}==2'b10) Q<=1'b1; else if({j,k}==2'b01) Q<=1'b0; else ;endendmodule。

(完整版)C50个经典小程序(新手必备)

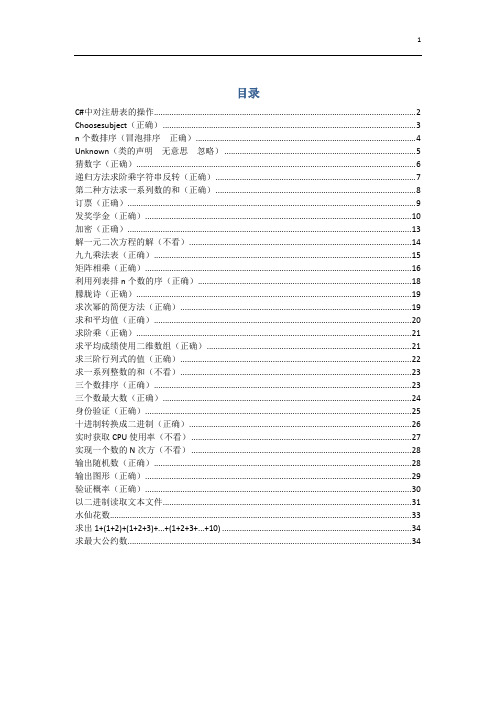

目录C#中对注册表的操作 (2)Choosesubject(正确) (3)n个数排序(冒泡排序正确) (4)Unknown(类的声明无意思忽略) (5)猜数字(正确) (6)递归方法求阶乘字符串反转(正确) (7)第二种方法求一系列数的和(正确) (8)订票(正确) (9)发奖学金(正确) (10)加密(正确) (13)解一元二次方程的解(不看) (14)九九乘法表(正确) (15)矩阵相乘(正确) (16)利用列表排n个数的序(正确) (18)朦胧诗(正确) (19)求次幂的简便方法(正确) (19)求和平均值(正确) (20)求阶乘(正确) (21)求平均成绩使用二维数组(正确) (21)求三阶行列式的值(正确) (22)求一系列整数的和(不看) (23)三个数排序(正确) (23)三个数最大数(正确) (24)身份验证(正确) (25)十进制转换成二进制(正确) (26)实时获取CPU使用率(不看) (27)实现一个数的N次方(不看) (28)输出随机数(正确) (28)输出图形(正确) (29)验证概率(正确) (30)以二进制读取文本文件 (31)水仙花数 (33)求出1+(1+2)+(1+2+3)+...+(1+2+3+...+10) .. (34)求最大公约数 (34)C#中对注册表的操作Windows 操作系统的注册表包含了很多有关计算机运行的配置方式,打开注册表我们可以看到注册表是按类似于目录的树结构组织的,其中第二级目录包含了五个预定义主键分别是:HKEY_CLASSES_ROOT,HKEY_CURRENT_USER,HKEY_LOCAL_MACHINE,HKEY_USERS,HKEY_CURRENT_CONFIG。

下面我们来分别解释这5个类的作用HKEY_CLASSES_ROOT该主键包含了文件的扩展名和应用程序的关联信息以及Window Shell和OLE用于储存注册表的信息。

verilog代码乘法除法编写

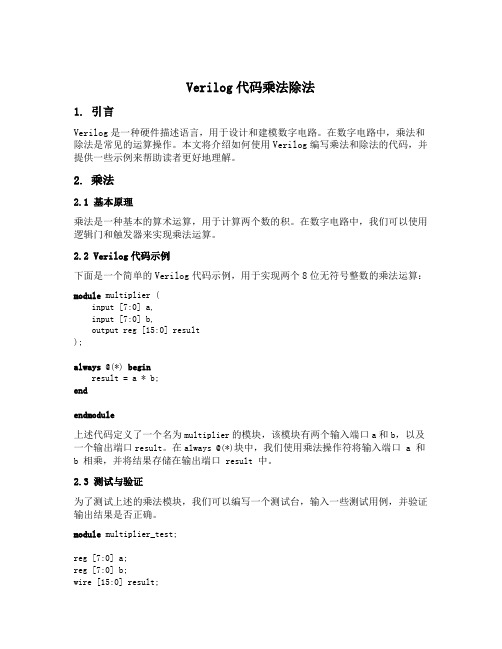

Verilog代码乘法除法1. 引言Verilog是一种硬件描述语言,用于设计和建模数字电路。

在数字电路中,乘法和除法是常见的运算操作。

本文将介绍如何使用Verilog编写乘法和除法的代码,并提供一些示例来帮助读者更好地理解。

2. 乘法2.1 基本原理乘法是一种基本的算术运算,用于计算两个数的积。

在数字电路中,我们可以使用逻辑门和触发器来实现乘法运算。

2.2 Verilog代码示例下面是一个简单的Verilog代码示例,用于实现两个8位无符号整数的乘法运算:module multiplier (input [7:0] a,input [7:0] b,output reg [15:0] result);always @(*) beginresult = a * b;endendmodule上述代码定义了一个名为multiplier的模块,该模块有两个输入端口a和b,以及一个输出端口result。

在always @(*)块中,我们使用乘法操作符将输入端口a和b相乘,并将结果存储在输出端口result中。

2.3 测试与验证为了测试上述的乘法模块,我们可以编写一个测试台,输入一些测试用例,并验证输出结果是否正确。

module multiplier_test;reg [7:0] a;reg [7:0] b;wire [15:0] result;multiplier dut(.a(a),.b(b),.result(result));initial begin// Test case 1: a = 5, b = 3a = 5;b = 3;#10; // Wait for 10 time unitsif (result !== 15)$display("Test case 1 failed");// Test case 2: a = 10, b = 0a = 10;b = 0;#10; // Wait for 10 time unitsif (result !== 0)$display("Test case 2 failed");// Add more test cases here...endendmodule上述代码定义了一个名为multiplier_test的测试台模块。

太空大战用Verilog编写的太空战斗小游戏

太空大战用Verilog编写的太空战斗小游戏太空战斗小游戏是一种经典的街机游戏,可以让玩家亲身体验太空战斗的刺激与挑战。

本文将介绍一种使用Verilog编写的太空战斗小游戏的方法,该方法可以使游戏在硬件环境下运行。

I. 游戏介绍太空战斗小游戏主要由玩家控制一艘飞船,与敌方的太空飞船进行激烈的战斗。

玩家可以通过操控飞船的移动和射击来击败敌人,躲避敌方飞船的攻击。

II. 游戏设计1. 硬件平台本游戏使用Verilog语言编写,并在FPGA(现场可编程门阵列)平台上运行。

FPGA提供了灵活的硬件编程环境,可以快速实现游戏的逻辑功能。

2. 游戏框架太空战斗小游戏可以分为游戏初始化、游戏进行和游戏结束三个阶段。

在游戏初始化阶段,需要对游戏进行各项参数的初始化设置,如飞船的初始位置、敌人的生成位置等。

在游戏进行阶段,玩家可以通过操控飞船进行移动和射击,同时需要监测敌人的位置和状态来进行相应的反应。

在游戏结束阶段,将根据游戏胜负的判定来展示相应的结果。

III. 游戏逻辑1. 飞船控制玩家可以通过键盘或者手柄操控飞船的移动。

根据按键或者手柄输入的信号,可以控制飞船在游戏界面上上下左右进行移动。

同时,玩家还可以通过按下射击键来发射子弹。

2. 敌人生成游戏中的敌人应该在不同的位置上随机生成。

可以使用伪随机数生成器来确定敌人的生成位置,保证游戏的随机性。

3. 碰撞检测在游戏进行过程中,需要检测飞船与敌人、飞船的子弹与敌人的碰撞。

通过检测碰撞,可以判断是否击中敌人或者被敌人击中,从而计算得分或者判断游戏结束。

IV. 实现方法太空战斗小游戏的实现主要需要定义飞船、子弹和敌人的模型,并定义各种操作和逻辑来实现游戏的功能。

可以使用有限状态机(FSM)来描述游戏的各个状态,如游戏初始化、游戏进行和游戏结束。

1. 飞船模型飞船模型可以定义为一个有固定大小的方块,可以在游戏界面上上下左右移动。

可以使用寄存器来保存飞船的位置信息,根据输入信号来更新飞船的位置。

[FPGA][Verilog][SPI]简单的读写SPI接口EEPROM-93C46程序

![[FPGA][Verilog][SPI]简单的读写SPI接口EEPROM-93C46程序](https://img.taocdn.com/s3/m/1221e485ec3a87c24028c428.png)

Write19: begin mo <= 0; cs <= 0; end

Read0: cs <= 0; Read1://110+add(7bit) begin cs <= 1; mo <= 1; end Read2: mo <= 1; Read3: mo <= 0;//110 Read4: mo <= 0; Read5: mo <= 1; Read6: mo <= 1; Read7: mo <= 1; Read8: mo <= 1; Read9: mo <= 1; Read10: mo <= 1; Read11: begin mo <= 0; led[7] <= mi; end Read12: led[7] <= mi; Read13: led[6] <= mi; Read14: led[5] <= mi; Read15:

从开始读数据手册,到研究时序,到编写 Verilog 程序,到仿真调试时序,整整 花了有 3-4 天时间。 最后时序已经完全正确, 却读不出任何数据,经过一个晚上的排查才发现是开发 板上的 DI DO SK CS 标号标错了,泪奔~~ 本来我想写一个完整的 SPI 接口出来,想了几天都没有头绪,最后还是写了一个 最简单的写数据读数据的小程序,如果做成接口也勉强可以用。 程序的功能很简单,往地址 0111111 的位置写了 00001111 的数据,地址都还没 有做成接口,固定在程序里面的。 具体用了一个状态机共 53 个状态,每一个状态都是一个 SCK 信号的处理,当然 有分为三个大状态,分别为 ENWR、WRITE、READ 93C46 要首先写 ENWR 信号才能写入数据,具体还得研究数据手册 通过这次 93C46 和上次写 18B20 的经历, 我感觉到数据手册的确是相当的重要的, 需要仔细推敲,分析每一个时序图!下次要做 I2C 接口的 24C02,1、2、3 线就 都学过拉。 当然作为初学者程序是写的那是超级的烂,欢迎拍砖

verilog之四位全加器的编译及仿真(用开源免费的软件——iverilog+GTKWave)

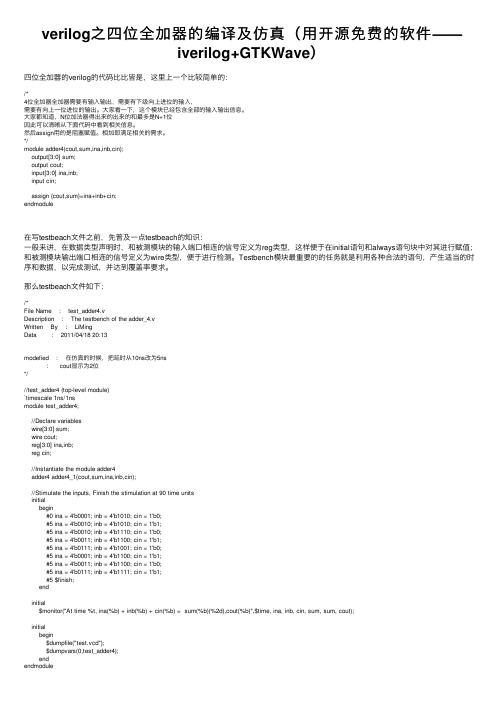

verilog之四位全加器的编译及仿真(⽤开源免费的软件——iverilog+GTKWave)四位全加器的verilog的代码⽐⽐皆是,这⾥上⼀个⽐较简单的:/*4位全加器全加器需要有输⼊输出,需要有下级向上进位的输⼊,需要有向上⼀位进位的输出。

⼤家看⼀下,这个模块已经包含全部的输⼊输出信息。

⼤家都知道,N位加法器得出来的出来的和最多是N+1位因此可以清晰从下⾯代码中看到相关信息。

然后assign⽤的是阻塞赋值。

相加即满⾜相关的需求。

*/module adder4(cout,sum,ina,inb,cin);output[3:0] sum;output cout;input[3:0] ina,inb;input cin;assign {cout,sum}=ina+inb+cin;endmodule在写testbeach⽂件之前,先普及⼀点testbeach的知识:⼀般来讲,在数据类型声明时,和被测模块的输⼊端⼝相连的信号定义为reg类型,这样便于在initial语句和always语句块中对其进⾏赋值;和被测模块输出端⼝相连的信号定义为wire类型,便于进⾏检测。

Testbench模块最重要的的任务就是利⽤各种合法的语句,产⽣适当的时序和数据,以完成测试,并达到覆盖率要求。

那么testbeach⽂件如下:/*File Name : test_adder4.vDescription : The testbench of the adder_4.vWritten By : LiMingData : 2011/04/18 20:13modefied : 在仿真的时候,把延时从10ns改为5ns: cout显⽰为2位*///test_adder4 (top-level module)`timescale 1ns/1nsmodule test_adder4;//Declare variableswire[3:0] sum;wire cout;reg[3:0] ina,inb;reg cin;//Instantiate the module adder4adder4 adder4_1(cout,sum,ina,inb,cin);//Stimulate the inputs, Finish the stimulation at 90 time unitsinitialbegin#0 ina = 4'b0001; inb = 4'b1010; cin = 1'b0;#5 ina = 4'b0010; inb = 4'b1010; cin = 1'b1;#5 ina = 4'b0010; inb = 4'b1110; cin = 1'b0;#5 ina = 4'b0011; inb = 4'b1100; cin = 1'b1;#5 ina = 4'b0111; inb = 4'b1001; cin = 1'b0;#5 ina = 4'b0001; inb = 4'b1100; cin = 1'b1;#5 ina = 4'b0011; inb = 4'b1100; cin = 1'b0;#5 ina = 4'b0111; inb = 4'b1111; cin = 1'b1;#5 $finish;endinitial$monitor("At time %t, ina(%b) + inb(%b) + cin(%b) = sum(%b)(%2d),cout(%b)",$time, ina, inb, cin, sum, sum, cout);initialbegin$dumpfile("test.vcd");$dumpvars(0,test_adder4);endendmodule由于是在windows的cmd下进⾏命令⾏的运⾏,所以有时候每次输⼊⼀个命令显得很费时间,所以我这⾥⼜写了⼀个(批处理⽂件)bat⽂件:go.batECHO OFFECHO *********************************ECHO * Batch fileECHO *********************************ECHO *ECHO ONiverilog -o test adder4.v test_adder4.vvvp -n test -lxt2cp test.vcd test.lxtgtkwave test.lxt(说明⼀下,我在windows下安装了gnuwin的软件,即能在windows下⽤gnu的⼀些⼩的实⽤的⼯具!)哈哈,这⾥就可以⼀键运⾏了,上⾯的⼀些命令的解释可以到我的“wndows下如何⽤Iverilog+GTKWave进⾏verilog的编译和查看仿真波形”的博⽂⾥去看看吧。

Verilog仿真软件 modelsim

下面是115网盘下载地址:/file/t7321e584f1 Modelsim安装步骤此处以Modelsim Se v6.0的安装为例说明具体的安装步骤以及应该注意的事项:Modelsim Se v6.0的安装:运行Modelsim Se v6.0目录中的的自解压缩安装文件,如下图1-1所示:图1-1 自解压缩安装文件等待解压缩完成之后,会出现Modelsim Se v6.0的安装选择画面,如图1-2所示,图1-2 选择安装模式选择FULL Product 安装模式,出现如图3所示的安装界面,如图1-3所示图1-3选择next,然受选择yes,出现如图1-4所示的安装路径选择对话框,图1-4 选择安装路径这里我选择默认安装路径c:\Modeltech_6.0。

连续两次next出现如图1-5所示的文件安装界面图1-5 安装文件复制完成后会弹出如图1-6所示的对话框图1-6 选择“是(Y)”出现图1-7图1-7 和图1-8图1-8 点击“确定”安装完成后,出现图1-9点击“是(Y)”后在桌面建立快捷方式。

紧接着出现图1-10图1-10 添加桌面快捷方式选择默认。

图1-11 完成安装完成安装,如图1-11所示。

2 配置Modelsim Se v6.0的的环境变量:先找到的安装文件夹的crack目录下的keygen.exe文件,然后运行。

如图2-1所示:点击“Generate”会出现图2-2。

图2-2这表示License文件生成成功。

将生成的License文件license.dat复制到Modelsim Se v6.0安装目录(我这里的安装目录是C:\Modeltech_6.0)。

然后打开计算机属性对话框的“高级”选项卡,找到用户环境变量LM_LICENSE_FILE,然后编辑,输入变量值C:\Modeltech_6.0\license.dat(也就是License文件的物理路径)如图2-3所示:图2-3 Modelsim v6.0 用户环境变量设置编辑完成之后,确定。

systemverilog_断言_快速教程

Bind: very useful in systemverilog.Assertion:1.## “a ##3 b”意思是a 之后3个周期b….2.“|->”表示如果先行算子匹配,后序算子在同一周期开始计算3.“|=>”表示如果先行算子匹配,后序算子在下一个周期开始计算4.重复操作符:* 连续重复“[*m]”: “a[*1:3]”表示a被连续重复1~3次** 跳转重复“[->]”: “a[->3]”表示a被跳转重复3次*** 非连续重复“[=m]”: “a[=3]”表示a被非连续重复3次芯片设计:verilog断言(SVA)语法断言assertion被放在verilog设计中,方便在仿真时查看异常情况。

当异常出现时,断言会报警。

一般在数字电路设计中都要加入断言,断言占整个设计的比例应不少于30%。

以下是断言的语法:1. SVA的插入位置:在一个.v文件中:module ABC ();rtl 代码SVA断言endmodule注意:不要将SVA写在enmodule外面。

2. 断言编写的一般格式是:【例】断言名称1:assert property(事件1) //没有分号$display("........",$time); //有分号else$display("........",$time); //有分号断言名称2:assert property(事件2)$display("........",$time);else$display("........",$time);断言的目的是:断定“事件1”和“事件2”会发生,如果发生了,就记录为pass,如果没发生,就记录为fail。

注意:上例中没有if,只有else,断言本身就充当if的作用。

上例中,事件1和事件2可以用两种方式来写:(1) 序列块: sequence name;。

几个常用的Verilog小程序

几个常用的Verilog小程序几个常用的Verilog小程序(1) 8位串并转换module haidaoqi(clk,rst,din,dout);input clk,rst,din;output [7:0] dout;reg[7:0] data,dout;reg[2:0] cnt;always@(posedge clk or posedge rst)if(rst) //复位高有效data <=8'b0;elsedata<= {data[7:0],din};//din是输入串行数据,假设输入数据高位在前//这是一个移位寄存器always@(posedge clk or posedge rst)if(rst)cnt <= 3'b0;elseif(cnt == 3'b111)cnt <= 3'b0;elsecnt <= cnt +1;//计数器,用来计算移位次数,移位8次在以后产生一个有效数据always@(posedge clk or posedge rst)if(rst)dout <= 8'b0;elseif(cnt == 3'b111)dout <= data;//如果计数器记到7,那么输出一个有效的8位数据elsedout <= 0;endmodule(2) 8 位数据寄存器module reg8(out_data,in_data,clk,clr);output[7:0] out_data;input[7:0] in_data;input clk,clr;reg[7:0] out_data;always @(posedge clk or posedge clr)beginif(clr) out_data <=0;else out_data <=in_data;endendmodule(3) 8位数据锁存器module haidaoqi(data_out,data_in,clk,rst); output[7:0] data_out;input[7:0] data_in;input clk,rst;reg[7:0] data_out;always @(rst or clk or data_in)beginif (rst) data_out<=8'b0;else if (clk) data_out<=data_in;else data_out<=8'b0;endendmodule(4) 8位并串转换module haidaoqi(rst,clk,tem,D1);input rst,clk;input [7:0] tem;output D1;reg D1;wire [7:0] tem;reg [2:0] counter;always @(posedge clk or posedge rst) begin if (rst)begincounter<=3'b0;D1<=0;endelse if(counter==7)begincounter<=3'b0;D1<=0;endelsebegincounter<=counter+1;D1=tem[counter];endendendmodule(5) clk一分四/八频module haidaoqi(clk1,clk2,clk,rst);output clk1,clk2;input clk,rst;reg clk1,clk2;reg[7:0] state;parameter S0=8'b00000000, S1=8'b00000001,S2=8'b00000010,S3=8'b00000100,S4=8'b00001000,S5=8'b00010000,S6=8'b00100000,S7=8'b01000000,S8=8'b10000000;always@(posedge clk)if(rst)beginclk1<=0;clk2<=0;state<=S0;endelsebegincase(state)S0:state<=S1;S1:state<=S2;S2:beginclk1<=~clk1;state<=S3;endS3:state<=S4;S4:clk1<=~clk1;clk2=~clk2;state<=S5;endS5:state<=S6;S6:beginclk1<=~clk1;state<=S7;endS7:state<=S8;S8:beginclk1<=~clk1;clk2=~clk2;state<=S0;enddefault:state<=S0; endcaseendendmodule(6) 8位比较器module haidaoqi(a,b,en,y); input[width-1:0] a,b; input en;output y;reg y;parameter width=8; always@(a or b)beginif(a==b)y<=1;elsey<=0;endelsey<=0;endmodule(7)带使能端的rammodule haidaoqi(dataout,datain,ena,read,write); output[7:0] dataout;input[7:0] datain;input ena,read,write;reg[7:0] ram[1:0];parameter addr=1'b0;assign dataout=(read && ena)?ram[addr]:8'hzz;always@(posedge write)beginram[addr]<=datain;endendmodule(8) 译码器module haidaoqi(ma,a,b,c,d,e);input[2:0] ma;output a,b,c,d,e;reg a,b,c,d,e;always@(ma)case(ma)3'b001:{a,b,c,d,e}<=5'b10000;3'b010:{a,b,c,d,e}<=5'b01000;3'b011:{a,b,c,d,e}<=5'b00100;3'b100:{a,b,c,d,e}<=5'b00010;3'b101:{a,b,c,d,e}<=5'b00001;default:{a,b,c,d,e}<=5'bzzzzz;endcaseendmodule(9) 带清0/置1端的T触发器module T-trigger(clk,T,R,S,Q,Q1);input clk,T,R,S;output Q,Q1;reg Q,Q1;always @(posedge clk or negedge R or negedge S) begin if(!R)beginQ <= 1'b0;Q1<=1'b1;endelse if(!S)beginQ <=1'b1;Q1<=1'b0;endelse if(T)beginQ<=~Q;Q1<=~Q1;endendendmodule(10)带起始位识别的串并转换(存8位有效数据)module SIM(din,clk,rst,dout,ok);input din,clk,rst;output ok;output[7:0] dout;reg[7:0] indata_buf,dout;reg[3:0] counter;reg[2:0] state;reg[1:0] cnt;reg tag,ok;integer bitpos=7;parameter s0=0,s1=1,s2=2,s3=3,s4=4;always@(posedge clk or posedge rst)if(rst)beginstate<=0;counter<=0;tag<=0;indata_buf<=8'bz;cnt<=0;bitpos=7;endelse case(state)s0:begintag=0;ok<=tag;if(din)begincnt<=cnt+1;state<=s0;if(cnt==3)beginstate<=s1;cnt<=0;endendelse begincounter<=0;state<=s0;endends1:beginif(counter==7) beginstate<=s2;counter<=0;endelsebegincounter<=counter+1; state<=s0;endends2:if(!din)state<=s3;elsestate<=s0;s3:beginif(bitpos==-1)beginbitpos=7;state<=s4;endelsebeginindata_buf[bitpos]<=din;bitpos<=bitpos-1;state<=s3;endends4:begintag=1'b1;ok<=tag;dout<=indata_buf;state<=s0;endendcaseendmodul(11)移位寄存器(9位有效数据输出)module ywjc(din,clk,rst,dout,ok);input din,clk,rst;output ok;output[8:0] dout;reg[8:0] indata_buf,dout;reg[3:0] counter;reg[2:0] state;reg[1:0] cnt;reg tag,ok;integer bitpos=8;parameter s0=0,s1=1,s2=2,s3=3,s4=4; always@(posedge clk or posedge rst) if(rst) beginstate<=0;counter<=0;tag<=0;indata_buf<=9'bz;cnt<=0;bitpos=8;endelse case(state)s0:begintag=0;ok<=tag;begincnt<=cnt+1;state<=s0;if(cnt==3)beginstate<=s1;cnt<=0;endendelse begincounter<=0;state<=s0;endends1:beginif(counter==8)beginstate<=s2;counter<=0;endelsecounter<=counter+1; state<=s0;endends2:if(!din)state<=s3;elsestate<=s0;s3:beginif(bitpos==-1)beginbitpos=8;state<=s4;endelsebeginindata_buf[bitpos]<=din; bitpos<=bitpos-1; state<=s3;endends4:begintag=1'b1;ok<=tag;dout<=indata_buf;state<=s0; end endcase endmodule。

verilog串口通信程序

verilog串⼝通信程序FPGA实现RS-232串⼝收发的仿真过程(Quartus+Synplify+ModelSim)(2007-09-11 12:17:37)⽹上关于RS-232的异步收发介绍得很多,最近没事学着摸索⽤ModelSim来做时序仿真,就结合⽹上的参考资料和⾃⼰的琢磨,做了这个东西。

针对我这个⼩程序结合FPGA的开发流程,主要⾛了以下⼏步:1. ⽂本程序输⼊(Verilog HDL)2. 功能仿真(ModelSim,查看逻辑功能是否正确,要写⼀个Test Bench)3. 综合(Synplify Pro,程序综合成⽹表)4. 布局布线(Quartus II,根据我选定的FPGA器件型号,将⽹表布到器件中,并估算出相应的时延)5. 时序仿真(ModelSim,根据时延做进⼀步仿真)这⾥贴出我的程序和各个详细步骤,能和各位正在学习的新⼿们⼀起分享。

0. 原理略⼀、⽂本程序输⼊(Verilog HDL)发送端:module trans(clk,rst,TxD_start,TxD_data,TxD,TxD_busy);input clk,rst,TxD_start;input[7:0] TxD_data; lk(clk),.rst(rst),.TxD_start(TxD_start),.TxD_busy(TxD_busy),.TxD_data(TxD_data),.TxD(TxD));rcv rcv(.clk(clk),.rst(rst),.RxD(TxD), xD_data(RxD_data),.RxD_data_ready(RxD_data_ready));initial beginTxD_start = 0;TxD_data = 0;clk = 0;rst = 1;#54 rst = 0;#70 rst = 1;#40 TxD_start = 1'b1;#10 TxD_data = 8'b;#100 TxD_start = 1'b0;endalways begin#30 clk = ~clk;#10 clk = ~clk;endendmodule⼆、综合三、FPGA与PC串⼝⾃收发通信串⼝通信其实简单实⽤,这⾥我就不多说,只把⾃⼰动⼿写的verilog代码共享下。

systemverilog_断言_快速教程

Bind: very useful in systemverilog.Assertion:1.## “a ##3 b”意思是a 之后3个周期b….2.“|->”表示如果先行算子匹配,后序算子在同一周期开始计算3.“|=>”表示如果先行算子匹配,后序算子在下一个周期开始计算4.重复操作符:* 连续重复“[*m]”: “a[*1:3]”表示a被连续重复1~3次** 跳转重复“[->]”: “a[->3]”表示a被跳转重复3次*** 非连续重复“[=m]”: “a[=3]”表示a被非连续重复3次芯片设计:verilog断言(SVA)语法断言assertion被放在verilog设计中,方便在仿真时查看异常情况。

当异常出现时,断言会报警。

一般在数字电路设计中都要加入断言,断言占整个设计的比例应不少于30%。

以下是断言的语法:1. SVA的插入位置:在一个.v文件中:module ABC ();rtl 代码SVA断言endmodule注意:不要将SVA写在enmodule外面。

2. 断言编写的一般格式是:【例】断言名称1:assert property(事件1) //没有分号$display("........",$time); //有分号else$display("........",$time); //有分号断言名称2:assert property(事件2)$display("........",$time);else$display("........",$time);断言的目的是:断定“事件1”和“事件2”会发生,如果发生了,就记录为pass,如果没发生,就记录为fail。

注意:上例中没有if,只有else,断言本身就充当if的作用。

上例中,事件1和事件2可以用两种方式来写:(1) 序列块: sequence name;。

MOSES系列经典结构小程序

MOSES 系列经典结构小程序本主题由 cqjt 于 2009-3-24 09:16 移动列兵∙ 发短消息 ∙ 加为好友 1#大 中 小 发表于 2008-8-9 12:06 只看该作者 MOSES 系列经典结构小程序今天,我决定把近几年写的几个小程序集中拿出来,跟大家共享,都是结合结构人常用的一些机械劳动而写。

这些程序主要是用VB 对AutoCAD 进行的二次开发,使用前最好先打开AutoCAD,且所有程序均支持AutoCAD 2004~2006版本。

首先把程序可能用到的两个字体传上来。

如果有朋友对编辑字体文件感兴趣,我后面跟贴详解怎么自己修改字体文件,如用(代替%%130作为钢筋符号等。

很多人用探索者的钢筋字体是因为自己不会编写钢筋字体。

其实我觉得探索者的钢筋字体确实非常难看,打印出来干巴巴的。

其实探索者里面的很多功能根本就用不着的,CAD 本身都有该功能,只是很多初学者不知道怎么用而已,比如关闭层和显示层命令,用CAD 本身的该命令比探索者的关层显层速度不知道快了多少倍。

[attach]3364680[/attac[ 本帖最后由 imoses 于 2008-8-20 21:10 编辑 ] 附件 字体.rar (599.7 KB) 2008-8-9 12:06, 下载次数: 232编辑 引用 报告 评分 回复TOP列兵∙ 发短消息 ∙ 加为好友2# 大 中 小 发表于 2008-8-9 12:19 只看该作者计算书整理(图纸归并)程序1、程序开发背景:使用过PKPM 出计算书的朋友都知道,如果要出漂亮的计算书(如文字重叠等问题),一般是把T 文件转换成dwg 文件,再进行处理,如删除构件编号、文字处理(对齐方式、高宽比),以及一张一张的dwg 文件打开再打印,非常麻烦,一般用ctr+c 和ctrl+v 把要打印的合并到一个文件,再处理。

程序就是简化这些操作而写。

2、程序使用方法:将需要打印的T 文件均转换成DWG 格式,并把这些DWG 格式文件拷贝到一个单独文件夹。

Verilog 数字系统设计90例

Verilog数字系统设计代码90例Contents1、二选一多路选择器 (1)2、多路器模块的编写测试平台 (1)3、三位加法器 (2)4、比较器 (2)5、实例调用—三态门选择器 (2)6、同步置位/清零的计数器 (3)7、异步清零 (3)8、case语句实现3-8译码器的部分代码 (3)9、for语句来实现8位数据中低4位左移到高4位 (4)10、for语句计算出13路脉冲信号为高电平的个数 (4)11、生成语句对两个N位的总线用门级原语进行按位异或 (5)12、用条件生成语句实现参数化乘法器 (5)13、使用case生成语句实现N位加法器 (6)14、四选一多路器 (7)15、四位计数器 (7)16、使用任务控制交通灯 (8)17、CPU总线控制的任务 (9)18、自动任务示例 (9)19、用函数实现乘累加器 (10)20、计算32位地址值的偶校验位 (11)21、左/右移位寄存器 (12)22、用函数的递归调用定义阶乘计算 (12)23、常量函数 (13)24、带符号函数 (13)25、显示任务 (14)26、文件写入操作的例子 (14)27、读取文件的示例1 (15)28、读取文件的示例2 (15)29、使用$random生成随机数 (16)30、宏定义语句`define (16)31、带有宏定义的8位加法器 (17)32、用`include语句设计的16位加法器 (17)33、结构化描述方式对四选一多路选择器 (18)34、结构化描述方式实现一位全加器 (18)35、结构化描述方式实例化四个一位全加器实现四位串行进位全加器 (18)36、用户定义原语 (19)37、四选一的多路选择器的自定义原语设计 (20)38、用户定义原语的方式设计电平敏感锁存器 (20)39、用户定义原语的方式设计D触发器(时钟下降沿触发) (20)40、采用实例化前面用定义原语设计的四选一多路选择器(MUX)的方法实现十六41、数据流建模描述方式:一位全加器 (22)42、行为建模方式设计一位加法器 (22)43、混合设计方式设计一位全加器 (22)44、数据流描述方式对四选一多路选择器建模 (23)45、行为建模方式设计四选一多路选择器 (23)46、用RTL级建模方式设计此电路 (24)47、四位全加器 (24)48、组合逻辑电路 (24)49、单向三态端口 (25)50、单向总线缓冲器 (25)51、双向三态端口 (25)52、双向总线缓冲器 (26)53、2选1多路选择器 (26)54、多路比较器 (27)55、带使能端的3-8译码器 (28)56、4位二进制到格雷码的转换器 (29)57、时序逻辑电路 (30)58、JK触发器 (31)59、D触发器 (32)60、带异步复位端D触发器 (32)61、带异步置位端D触发器 (32)62、带有异步置位和复位的D触发器 (33)63、带有同步复位的D触发器 (33)64、带同步置位端的上升沿触发器 (33)65、带异步复位端和输出使能端的上升沿触发器 (34)66、锁存器:电平触发的存储器单元,基本SR锁存器 (34)67、透明锁存器 (35)68、基本N位同步计数器 (35)69、带有异步复位、同步计数使能和可预置的十进制计数器 (35)70、格雷码计数器 (36)71、四位移位寄存器 (37)72、8位串入串出移位寄存器 (37)73、利用移位寄存器产生顺序脉冲 (38)74、可输出输入信号的2分频信号、4分频信号和8分频信号的分频器 (38)75、分频系数为12的分频器 (39)76、分频系数为6,占空比为1:5的偶数分频器 (39)77、3分频占空比为1:1的奇数分频器 (40)78、分频系数为5、占空比为1:1的奇数分频器 (41)79、分频系数为7、占空比为1:6的奇数分频器 (42)80、带使能端和复位端的时钟同步8位寄存器组逻辑 (42)81、自触发always块 (42)82、1001序列信号检测器 (43)83、米利型有限状态机 (47)85、并行数据流转换为一种特殊串行数据流模块的设计 (53)86、设计对数字采集芯片AD0809的控制接口电路的Verilog代码 (57)87、面积优化——设计乘法选择器 (61)88、串行化——描述一个乘法累加器,其位宽位16位对8个16位数据进行乘法和加法运算 (63)89、流水线设计——流水线计数使用实例:8位加法器 (64)90、流水线设计——设计一个为8位全加器(一个是直接实现,一个采用4级流水线实现) (65)1、二选一多路选择器行为描述:module muxtwo(out,a,b,sl);input a,b,sl;output out;reg out;always@(a or b or sl)if(!sl) out = a;else out = b; endmodule逻辑描述:module muxtwo(out,a,b,sl);input a,b,sl;output out;不用写寄存器wire nsl,sela,selb;assign nsl = ~sl;assign sela = a&nsl;assign selb = b&sl;assign out = sela|selb; endmodule门级描述:module muxtwo(out,a,b,sl);input a,b,sl;output out;不用写寄存器not u1(nsl,sl);and u2(sela,a,nsl);and u3(selb,b,sl);or u4(out,sela,selb); endmodule2、多路器模块的编写测试平台`include “muxtwo.v”module t;reg ain,bin,select;reg clock;wire outw;initialbeginain=0; bin=0;select=0; clock=0;endalways #50 clock =~clock;always@(posedge clock)begin#1 ain = {$random}%2;#3 bin = {$random}%2;endmuxtwo m(.out(outw),.a(ain),.b(bin),.sl(select));endmodule3、三位加法器module adder ( count,sum,a,b,cin );input [2:0] a,b;input cin;output count;output [2:0] sum;assign {count,sum}=a+b+cin;endmodule4、比较器:module compare ( equal,a,b );output equal; //声明输出信号equalinput [1:0] a,b; //声明输入信号a,bassign equal=(a==b)?1:0;//如果两个输入信号相等,输出为1。

芯片设计:verilog断言(SVA)语法

芯片设计:verilog断言(SVA)语法(2014-01-23 13:51:36)转载▼标签:verilogsvaassertion断言it作者:白栎旸断言assertion被放在verilog设计中,方便在仿真时查看异常情况。

当异常出现时,断言会报警。

一般在数字电路设计中都要加入断言,断言占整个设计的比例应不少于30%。

以下是断言的语法:1. SVA的插入位置:在一个.v文件中:module ABC ();rtl 代码SVA断言endmodule注意:不要将SVA写在enmodule外面。

2. 断言编写的一般格式是:【例】断言名称1:assert property(事件1) //没有分号$display("........",$time); //有分号else$display("........",$time); //有分号断言名称2:assert property(事件2)$display("........",$time);else$display("........",$time);断言的目的是:断定“事件1”和“事件2”会发生,如果发生了,就记录为pass,如果没发生,就记录为fail。

注意:上例中没有if,只有else,断言本身就充当if的作用。

上例中,事件1和事件2可以用两种方式来写:(1) 序列块: sequence name;。

;endsequence(2) 属性块:property name;。

;endsequence从定义来讲,sequence块用于定义一个事件(砖),而property块用于将事件组织起来,形成更复杂的一个过程(楼)。

sequence块的内容不能为空,你写乱字符都行,但不能什么都没有。

sequence也可以包含另一个sequence, 如:sequence s1;s2(a,b);endsequence //s1和s2都是sequence块sequence块和property块都有name,使用assert调用时都是:“assert property(name);”在SVA中,sequence块一般用来定义组合逻辑断言,而property一般用来定义一个有时间观念的断言,它会常常调用sequence,一些时序操作如“|->”只能用于property就是这个原因。

Verilog 实现任意占空比、任意分频的方法

分频程序虽然简单,但我觉得由简入难是学习的一个必然阶段,慢慢的我们自然会成长起来。

所以如果有时间的话,大家都可以将自己的这种“小程序”贴到论坛上来。

如果你的程序好,其他人也可以学习;如果你的程序有问题,大家可以一起帮你找问题,共同进步。

还有,我觉得在发贴的时候,最好能将原理说一下。

一来大家看你的贴能学到东西;二来也方便解答你的问题,不然还得解答者自己去找资料搞懂原理,然后再回答你,回答你问题的人自然也就不多了。

说了一些题外话,下面转入正文:在verilog程序设计中,我们往往要对一个频率进行任意分频,而且占空比也有一定的要求这样的话,对于程序有一定的要求,现在我在前人经验的基础上做一个简单的总结,实现对一个频率的任意占空比的任意分频。

比如:我们FPGA系统时钟是50M Hz,而我们要产生的频率是880Hz,那么,我们需要对系统时钟进行分频。

我们很容易想到用计数的方式来分频:50000000/880 = 56818这个数字不是2的整幂次方,那么怎么办呢?我们可以设定一个参数,让它到56818的时候重新计数不就完了吗?呵呵,程序如下:module div(clk, clk_div);input clk;output clk_div;reg [15:0] counter;always @(posedge clk)if(counter==56817) counter <= 0;else counter <= counter+1;assign clk_div = counter[15];endmodule下面我们来算一下它的占空比:我们清楚地知道,这个输出波形在counter 为0到32767的时候为低,在32767到56817的时候为高,占空比为40%多一些,如果我们需要占空比为50%,那么怎么办呢?不用急,慢慢来。

我们再设定一个参数,使它为56817的一半,使达到它的时候波形翻转,那不就完了吗?呵呵,再看看:module div(clk, clk_div);input clk;output clk_div;reg [14:0] counter;always @(posedge clk)if(counter==28408) counter <= 0;else counter <= counter+1;reg clk_div;always @(posedge clk)if(counter==28408) clk_div <= ~clk_div;endmodule占空比是不是神奇地变成50%了呢?呵呵。

VerilogHDL多个小程序教程(由易到难)

【例 3.3】4 位全加器的仿真程序

`timescale 1ns/1ns `include "adder4.v" module adder_tp; reg[3:0] a,b; reg cin; wire[3:0] sum; wire cout; integer i,j; //调用测试对象 //设定 cin 的取值 //测试输出信号定义为 wire 型 //测试模块的名字 //测试输入信号定义为 reg 型

-7 -

程序文本 endmodule

【例 5.13】用 casez 描述的数据选择器

王金明: 《 Verilog HDL 程序设计教程》

【例 3.1】4 位全加器

module adder4(cout,sum,ina,inb,cin); output[3:0] sum; output cout; input[3:0] ina,inb; input cin; assign {cout,sum}=ina+inb+cin; endmodule

【例 5.1】用 case 语句描述的 4 选 1 数据选择器

module mux4_1(out,in0,in1,in2,in3,sel); output out; input in0,in1,in2,in3; input[1:0] sel; reg out; always @(in0 or in1 or in2 or in3 or sel) case(sel) 2'b00: 2'b01: 2'b10: 2'b11: out=in0; out=in1; out=in2; out=in3; //敏感信号列表

count4 mycount(out,reset,clk);

芯片设计:verilog断言(SVA)语法

芯片设计:verilog断言(SVA)语法2014-01-23▼作者:白栎旸断言assertion被放在verilog设计中,方便在仿真时查看异常情况。

当异常出现时,断言会报警。

一般在数字电路设计中都要加入断言,断言占整个设计的比例应不少于30%。

以下是断言的语法:1. SVA的插入位置:在一个.v文件中:module ABC ();rtl代码SVA断言endmodule注意:不要将SVA写在enmodule外面。

2. 断言编写的一般格式是:【例】断言名称1:assert property(事件1) //没有分号$display("........",$time); //有分号else$display("........",$time); //有分号断言名称2:assert property(事件2)$display("........",$time);else$display("........",$time);断言的目的是:断定“事件1”和“事件2”会发生,如果发生了,就记录为pass,如果没发生,就记录为fail。

注意:上例中没有if,只有else,断言本身就充当if的作用。

上例中,事件1和事件2可以用两种方式来写:(1) 序列块: sequence name;。

;endsequence(2) 属性块:property name;。

;endsequence从定义来讲,sequence块用于定义一个事件(砖),而property块用于将事件组织起来,形成更复杂的一个过程(楼)。

sequence块的内容不能为空,你写乱字符都行,但不能什么都没有。

sequence也可以包含另一个sequence, 如:sequence s1;s2(a,b);endsequence //s1和s2都是sequence块sequence块和property块都有name,使用assert调用时都是:“assert property(name);”在SVA中,sequence块一般用来定义组合逻辑断言,而property一般用来定义一个有时间观念的断言,它会常常调用sequence,一些时序操作如“|->”只能用于property 就是这个原因。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

几个常用的Verilog小程序(1) 8位串并转换module haidaoqi(clk,rst,din,dout);input clk,rst,din;output [7:0] dout;reg[7:0] data,dout;reg[2:0] cnt;always@(posedge clk or posedge rst)if(rst) //复位高有效data <=8'b0;elsedata<= {data[7:0],din};//din是输入串行数据,假设输入数据高位在前//这是一个移位寄存器always@(posedge clk or posedge rst)if(rst)cnt <= 3'b0;elseif(cnt == 3'b111)cnt <= 3'b0;elsecnt <= cnt +1;//计数器,用来计算移位次数,移位8次在以后产生一个有效数据always@(posedge clk or posedge rst)if(rst)dout <= 8'b0;elseif(cnt == 3'b111)dout <= data;//如果计数器记到7,那么输出一个有效的8位数据elsedout <= 0;endmodule(2) 8 位数据寄存器module reg8(out_data,in_data,clk,clr);output[7:0] out_data;input[7:0] in_data;input clk,clr;reg[7:0] out_data;always @(posedge clk or posedge clr)beginif(clr) out_data <=0;else out_data <=in_data;endendmodule(3) 8位数据锁存器module haidaoqi(data_out,data_in,clk,rst); output[7:0] data_out;input[7:0] data_in;input clk,rst;reg[7:0] data_out;always @(rst or clk or data_in)beginif (rst) data_out<=8'b0;else if (clk) data_out<=data_in;else data_out<=8'b0;endendmodule(4) 8位并串转换module haidaoqi(rst,clk,tem,D1);input rst,clk;input [7:0] tem;output D1;reg D1;wire [7:0] tem;reg [2:0] counter;always @(posedge clk or posedge rst) beginif (rst)begincounter<=3'b0;D1<=0;endelse if(counter==7)begincounter<=3'b0;D1<=0;endelsebegincounter<=counter+1;D1=tem[counter];endendendmodule(5) clk一分四/八频module haidaoqi(clk1,clk2,clk,rst);output clk1,clk2;input clk,rst;reg clk1,clk2;reg[7:0] state;parameter S0=8'b00000000,S1=8'b00000001,S2=8'b00000010,S3=8'b00000100,S4=8'b00001000,S5=8'b00010000,S6=8'b00100000,S7=8'b01000000,S8=8'b10000000;always@(posedge clk)if(rst)beginclk1<=0;clk2<=0;state<=S0;endelsebegincase(state)S0:state<=S1;S1:state<=S2;S2:beginclk1<=~clk1;state<=S3;endS3:state<=S4;S4:beginclk1<=~clk1;clk2=~clk2;state<=S5;endS5:state<=S6;S6:beginclk1<=~clk1;state<=S7;endS7:state<=S8;S8:beginclk1<=~clk1;clk2=~clk2;state<=S0;enddefault:state<=S0;endcaseendendmodule(6) 8位比较器module haidaoqi(a,b,en,y);input[width-1:0] a,b;input en;output y;reg y;parameter width=8;always@(a or b)if(en)beginif(a==b)y<=1;elsey<=0;endelsey<=0;endmodule(7)带使能端的rammodule haidaoqi(dataout,datain,ena,read,write); output[7:0] dataout;input[7:0] datain;input ena,read,write;reg[7:0] ram[1:0];parameter addr=1'b0;assign dataout=(read && ena)?ram[addr]:8'hzz;always@(posedge write)beginram[addr]<=datain;endendmodule(8) 译码器module haidaoqi(ma,a,b,c,d,e);input[2:0] ma;output a,b,c,d,e;reg a,b,c,d,e;always@(ma)case(ma)3'b001:{a,b,c,d,e}<=5'b10000;3'b010:{a,b,c,d,e}<=5'b01000;3'b011:{a,b,c,d,e}<=5'b00100;3'b100:{a,b,c,d,e}<=5'b00010;3'b101:{a,b,c,d,e}<=5'b00001;default:{a,b,c,d,e}<=5'bzzzzz;endcaseendmodule(9) 带清0/置1端的T触发器module T-trigger(clk,T,R,S,Q,Q1);input clk,T,R,S;output Q,Q1;reg Q,Q1;always @(posedge clk or negedge R or negedge S) beginif(!R)beginQ <= 1'b0;Q1<=1'b1;endelse if(!S)beginQ <=1'b1;Q1<=1'b0;endelse if(T)beginQ<=~Q;Q1<=~Q1;endendendmodule(10)带起始位识别的串并转换(存8位有效数据)module SIM(din,clk,rst,dout,ok);input din,clk,rst;output ok;output[7:0] dout;reg[7:0] indata_buf,dout;reg[3:0] counter;reg[2:0] state;reg[1:0] cnt;reg tag,ok;integer bitpos=7;parameter s0=0,s1=1,s2=2,s3=3,s4=4;always@(posedge clk or posedge rst)if(rst)beginstate<=0;counter<=0;tag<=0;indata_buf<=8'bz;cnt<=0;bitpos=7;endelse case(state)s0:begintag=0;ok<=tag;if(din)begincnt<=cnt+1;state<=s0;if(cnt==3)beginstate<=s1;cnt<=0;endendelse begincounter<=0;state<=s0;endends1:beginif(counter==7)beginstate<=s2;counter<=0;endelsebegincounter<=counter+1;state<=s0;endends2:if(!din)state<=s3;elsestate<=s0;s3:beginif(bitpos==-1)beginbitpos=7;state<=s4;endelsebeginindata_buf[bitpos]<=din;bitpos<=bitpos-1;state<=s3;endends4:begintag=1'b1;ok<=tag;dout<=indata_buf;state<=s0;endendcaseendmodul(11)移位寄存器(9位有效数据输出)module ywjc(din,clk,rst,dout,ok);input din,clk,rst;output ok;output[8:0] dout;reg[8:0] indata_buf,dout;reg[3:0] counter;reg[2:0] state;reg[1:0] cnt;reg tag,ok;integer bitpos=8;parameter s0=0,s1=1,s2=2,s3=3,s4=4;always@(posedge clk or posedge rst) if(rst)beginstate<=0;counter<=0;tag<=0;indata_buf<=9'bz;cnt<=0;bitpos=8;endelse case(state)s0:begintag=0;ok<=tag;begincnt<=cnt+1;state<=s0;if(cnt==3)beginstate<=s1;cnt<=0;endendelse begincounter<=0;state<=s0;endends1:beginif(counter==8)beginstate<=s2;counter<=0;endelsecounter<=counter+1;state<=s0;endends2:if(!din)state<=s3;elsestate<=s0;s3:beginif(bitpos==-1)beginbitpos=8;state<=s4;endelsebeginindata_buf[bitpos]<=din;bitpos<=bitpos-1;state<=s3;endends4:begintag=1'b1;ok<=tag;dout<=indata_buf;state<=s0;endendcaseendmodule。