时序逻辑电路的Verilog_HDL实现实验报告

Verilog HDL实验报告

HDL实验报告专业电子科学与技术姓名学号指导老师1 实验一Modelsim仿真软件的使用1.1 实验目的(1)熟悉Modelsim 软件;(2)掌握Modelsim 软件的编译、仿真方法;(3)熟练运用Modelsim 软件进行HDL 程序设计开发。

1.2 实验步骤(1)学习使用Modelsim软件;(2)分析原理及功能;(3)用Verilog HDL编写程序;(4)编写测试程序进行仿真;(4)观察波形,分析仿真结果是否正确。

1.3 实验内容用Verilog HDL 程序实现一个异或门,Modelsim 仿真,观察效果。

1.4.1 程序module my_xor(ina,inb,out);input ina,inb;output out;assign out=ina^inb;endmodulemodule t_xor;reg ina,inb;wire out;initialbeginina=1'b0;forever #20 ina=~ina;endinitialbegininb=1'b0;forever #10 inb=~inb;endmy_xor tt(.ina(ina),.inb(inb),.out(out));endmodule2 实验二简单组合电路设计2.1 实验目的(1)掌握基于Modelsim 的数字电路设计方法;(2)熟练掌握HDL 程序的不同实现方法2.2 实验步骤(1)分析原理及功能;(2)根据原理用Verilog HDL编写程序;(3)编写测试程序进行仿真;(4)观察波形,分析仿真结果是否正确。

2.3 实验内容设计一个三人表决器(高电平表示通过) ,实验内容如下:(1)三个人,一个主裁判,两个副裁判;(2)规则:只要主裁判同意,输出结果为通过;否则,按少数服从多数原则决定是否通过。

使用Verilog HDL 程序实现上述实验内容,并使用modelsim 仿真(要求:至少使用两种方法实现上述实验内容和testbench)。

Verilog HDL 实验报告

Verilog实验报告班级:学号:姓名:实验1 :用 Verilog HDL 程序实现直通线1 实验要求:(1) 编写一位直通线的 Veirlog HDL 程序.(2) 编写配套的测试基准.(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.(4) 建议用模式 52 试验程序:module wl(in,out);input in;output out;wire out;assign out=in;endmodule3 测试基准:`include “wl.v”module wl_tb;reg in_tb;wire out_tb;initialbeginin_tb =0;#100 in_tb =1;#130 in_tb =0;endendmodule4 仿真图形:实验2 :用 Verilog HDL 程序实现一位四选一多路选择器1实验要求:(1) 编写一位四选一多路选择器的 Veirlog HDL 程序.(2) 编写配套的测试基准.(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.(4)建议用模式 52 试验程序:module mux4_to_1 (out,i0,i1,i2,i3,s1,s0);output out;input i0,i1,i2,i3;input s1, s0;reg out;always @ (s1 or s0 or i0 or i1 or i2 or i3)begincase ({s1, s0})2'b00: out=i0;2'b01: out=i1;2'b10: out=i2;2'b11: out=i3;default: out=1'bx;endcaseendendmodule3 测试基准:`include "mux4_to_1.v"module mux4_to_1_tb1;reg ain,bin,cin,din;reg[1:0] select;reg clock;wire outw;initialbeginain=0;bin=0;cin=0;din=0;select=2'b00;clock=0;endalways #50 clock=~clock;always @(posedge clock)begin#1 ain={$random} %2;#3 bin={$random} %2;#5 cin={$random} %2;#7 din={$random} %2;endalways #1000 select[0]=!select[0];always #2000 select[1]=!select[1];mux4_to_1 m(.out(outw),.i0(ain),.i1(bin),.i2(cin),.i3(din),.s1(select[1]),.s0(select[0])); endmodule4 仿真图形:实验3:用 Verilog HDL 程序实现十进制计数器1实验要求:(1) 编写十进制计数器的 Veirlog HDL 程序. 有清零端与进位端, 进位端出在输出为 9 时为高电平.(2) 编写配套的测试基准.(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.(4) 自行选择合适的模式2 实验程序:module counter_10c (Q, clock, clear, ov);output [3:0] Q;output ov;input clock, clear;reg [3:0] Q;reg ov;initial Q=4'b0000;always @ (posedge clear or negedge clock)beginif (clear)Q<=4'b0;else if (Q==8)beginQ<=Q+1;ov<=1'b1;endelse if (Q==9)beginQ<=4'b0000;ov<=1'b0;endelsebeginQ<=Q+1;ov<=1'b0;endendendmodule3 测试基准:`include"./counter_10c.v"module counter_10c_tb;wire[3:0] D_out;reg clk,clr;wire c_out;reg[3:0] temp;initialbeginclk=0;clr=0;#100 clr=1;#20 clr=0;endalways #20 clk=~clk;counter_10c m_1(.Q(D_out),.clear(clr),.clock(clk),.ov(c_out)); endmodule4 仿真波形:实验4 :用 Verilog HDL 程序实现序列检测器1 实验要求:、(1) 编写序列检测器的 Veirlog HDL 程序. 检测串行输入的数据序列中是否有目标序列5'b10010, 检测到指定序列后, 用一个端口输出高电平表示.(2) 编写配套的测试基准.(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.(4) 自行选择合适的模式2试验程序:module e15d1_seqdet( x, z, clk, rst);input x,clk, rst;output z;reg [2:0] state;wire z;parameter IDLE = 3 'd0,A = 3'd1,B = 3'd2,C = 3'd3,D = 3'd4,E = 3'd5,F = 3'd6,G = 3'd7;assign z =(state==D && x==0)?1:0;always @(posedge clk or negedge rst)if(!rst)beginstate<=IDLE;endelsecasex(state)IDLE: if(x==1)state<=A;else state<=IDLE;A: if (x==0)state<=B;else state<=A;B: if (x==0)state<=C;else state<=F;C: if(x==1)state<=D;else state<=G;D: if(x==0)state<=E;else state<=A;E: if(x==0)state<=C;else state<=A;F: if(x==1)state<=A;else state<=B;G: if(x==1)state<=F;else state <=G;default: state<=IDLE;endcaseendmodule3测试基准:`include"e15d1_seqdet.v"`timescale 1ns/1ns`define halfperiod 20module e15d1_seqdet_tb;reg clk, rst;reg [23:0] data;wire z;reg x;initialbeginclk =0;rst =1;#2 rst =0;#30 rst =1;data= 20 'b1100_1001_0000_1001_0100;#(`halfperiod*1000) $stop;endalways #(`halfperiod) clk=~clk;always @ (posedge clk)begin#2 data={data[22:0],data[23]};x=data[23];ende15d1_seqdet m(.x(x),.z(z),.clk(clk),.rst(rst)); endmodule4仿真波形:。

Verilog HDL 实验报告

实验一Modelsim仿真软件的使用一、实验目的(1)熟悉Modelsim 软件(2)掌握Modelsim 软件的编译、仿真方法(3)熟练运用Modelsim 软件进行HDL 程序设计开发二、实验内容1、实验要求用Verilog HDL 程序实现一个异或门,Modelism仿真,观察效果。

2、步骤1、建立工程2、添加文件到工程3、编译文件4、查看编译后的设计单元5、将信号加入波形窗口6、运行仿真3、方法moduleyihuo (a,b,c);inputa,b;output c;assign c=a^b;endmodule测试程序:module t_yihuo;reg a,b;wire c;initialbegina=0;forever #20 a=~a;endinitialbeginb=0;forever #30 b=~b;endyihuou1(a,b,c);endmodule二、实验结果波形图:三、分析和心得通过这次的实验,我基本熟悉Modelsim软件,掌握了Modelsim软件的编译、仿真方法。

同时在编写程序的过程中,加深了我对课上所讲的HDL的语法的认识。

实验二简单组合电路设计一、实验目的(1)掌握基于Modelsim的数字电路设计方法(2)熟练掌握HDL 程序的不同实现方法二、实验内容1、实验要求设计一个三人表决器(高电平表示通过),实验内容如下:(1)三个人,一个主裁判,两个副裁判;(2)规则:只要主裁判同意,输出结果为通过;否则,按少数服从多数原则决定是否通过。

使用 Verilog HDL 程序实现上述实验内容,并使用modelsim 仿真。

2、方法module test(a,b,c,s);inputa,b,c;output s;assign s=c|(b&a);endmodulemodulet_test;rega,b,c;wire s;initialbegina=0;forever#10 a=~a;endinitialbeginb=0;forever #20 b=~b;endinitialbeginc=0;forever#40 c=~c;endtest u1(a,b,c,s);endmodule三、实验结果四、分析和心得通过本次实验,我掌握基于Modelsim的简单数字电路设计方法,且尝试了用不同方法实现功能,三人表决器可以通过testbench测试程序实现,也可以利用always模块实现,可见程序的设计思想是很重要的。

Verilog-HDL实验报告

HDL实验报告专业电子科学与技术姓名学号指导老师1 实验一Modelsim仿真软件的使用1.1 实验目的(1)熟悉Modelsim 软件;(2)掌握Modelsim 软件的编译、仿真方法;(3)熟练运用Modelsim 软件进行HDL 程序设计开发。

1.2 实验步骤(1)学习使用Modelsim软件;(2)分析原理及功能;(3)用Verilog HDL编写程序;(4)编写测试程序进行仿真;(4)观察波形,分析仿真结果是否正确。

1.3 实验内容用Verilog HDL 程序实现一个异或门,Modelsim 仿真,观察效果。

1.4.1 程序module my_xor(ina,inb,out);input ina,inb;output out;assign out=ina^inb;endmodulemodule t_xor;reg ina,inb;wire out;initialbeginina=1'b0;forever #20 ina=~ina;endinitialbegininb=1'b0;forever #10 inb=~inb;endmy_xor tt(.ina(ina),.inb(inb),.out(out));endmodule2 实验二简单组合电路设计2.1 实验目的(1)掌握基于Modelsim 的数字电路设计方法;(2)熟练掌握HDL 程序的不同实现方法2.2 实验步骤(1)分析原理及功能;(2)根据原理用Verilog HDL编写程序;(3)编写测试程序进行仿真;(4)观察波形,分析仿真结果是否正确。

2.3 实验内容设计一个三人表决器(高电平表示通过) ,实验内容如下:(1)三个人,一个主裁判,两个副裁判;(2)规则:只要主裁判同意,输出结果为通过;否则,按少数服从多数原则决定是否通过。

使用Verilog HDL 程序实现上述实验内容,并使用modelsim 仿真(要求:至少使用两种方法实现上述实验内容和testbench)。

时序电路应用实验报告(3篇)

第1篇一、实验目的1. 理解时序电路的基本概念和组成,掌握时序电路的设计方法和分析方法。

2. 掌握计数器、寄存器、移位寄存器等时序电路的应用。

3. 熟悉FPGA开发环境,能够使用Quartus II设计工具进行时序电路的设计和仿真。

二、实验原理时序电路是数字电路中的一种重要电路,它能够根据输入信号的变化,产生一系列有序的输出信号。

时序电路主要由触发器、逻辑门和时钟信号组成。

1. 触发器:触发器是时序电路的基本单元,具有存储一个二进制信息的功能。

常见的触发器有D触发器、JK触发器、T触发器等。

2. 逻辑门:逻辑门用于实现基本的逻辑运算,如与、或、非、异或等。

3. 时钟信号:时钟信号是时序电路的同步信号,用于控制触发器的翻转。

三、实验内容1. 计数器设计(1)设计一个3位同步二进制加计数器。

(2)设计一个3位同步二进制减计数器。

2. 寄存器设计使用74LS74触发器设计一个双向移位寄存器。

3. 移位寄存器设计使用74LS74触发器设计一个单向移位寄存器。

4. 环形计数器设计使用74LS74触发器设计一个环形计数器。

5. 可控分频器设计使用Verilog HDL语言设计一个可控分频器,实现时钟信号的分频功能。

四、实验步骤1. 使用Quartus II设计工具创建工程,并添加所需的设计文件。

2. 根据实验原理,编写时序电路的Verilog HDL代码。

3. 编译代码,并生成测试平台。

4. 在测试平台上进行仿真,验证时序电路的功能。

5. 将设计下载到FPGA,进行硬件实验。

6. 记录实验结果,分析实验现象。

五、实验结果与分析1. 计数器实验结果(1)3位同步二进制加计数器:按照时钟信号的变化,计数器能够从000计数到111。

(2)3位同步二进制减计数器:按照时钟信号的变化,计数器能够从111减到000。

2. 寄存器实验结果使用74LS74触发器设计的双向移位寄存器,能够实现数据的左移和右移功能。

3. 移位寄存器实验结果使用74LS74触发器设计的单向移位寄存器,能够实现数据的左移功能。

时序逻辑电路的Verilog_HDL实现实验报告

时序逻辑电路的Verilog HDL 实现一.实验要求(1):编写JK 触发器、8位数据锁存器、数据寄存器的Verilog HDL 程序,并实现其仿真及其测试程序;(2):在实验箱上设计含异步清零和同步使能的计数器。

(3):进行波形仿真测试后;画出仿真波形。

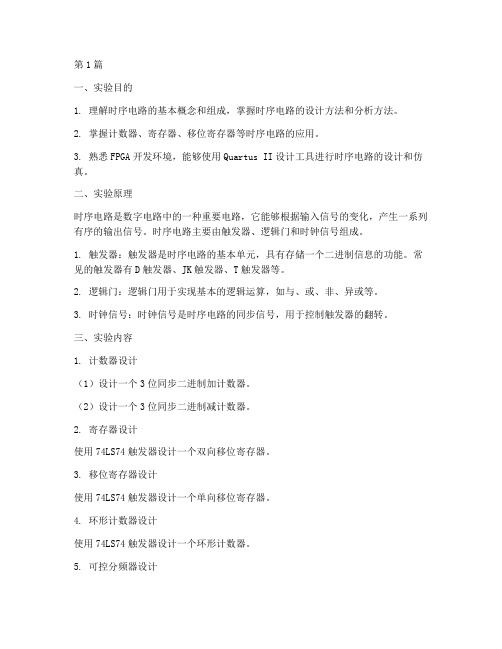

(4):写出实验心得二.实验内容:(1)1.JK 触发器的元件符号如图7.14所示,其中J 、K 是数据输入端,CLR 是复位控制输入端,当CLR=0时,触发器的状态被置为0态;CLK 是时钟输入端;Q 和QN 是触发器的两个互补输出端。

JK 触发器的状态方程为Q n+1 =J Q n +K Q nJK 触发器的verilog HDL 程序module jkff_rs(clk,j,k,q,rs,set); input clk,j,k,set,rs;output reg q;always@(posedge clk,negedge rs,negedge set)begin if(!rs) q<=1'b0;else if(!set) q<=1'b1;else case({j,k})2'b00:q<=q;2'b01:q<=1'b0;2'b10:q<=1'b1;2'b11:q<=~q;default:q<=1'bx;endcaseendendmoduleJK 触发器的功能:带异步清0,异步置1(低电平有效)JK 触发器的仿真结果JK 触发器的元件符号2.8位数据锁存器锁存器元件符号如图所示。

CLR是复位控制输入端,当CLR=0时,8位数据输出Q[7..0]=00000000。

ENA是使能控制输入端,当ENA=1时,锁存器处于工作状态,输出Q[7..0]=D[7..0];ENA=0时,锁存器的状态保持不变。

OE是三态输出控制端,当OE=1时,输出为高阻态;OE=0时,锁存器为正常输出状态。

verilog hdl实验报告

verilog hdl实验报告《Verilog HDL实验报告》Verilog HDL(硬件描述语言)是一种用于描述电子系统的硬件的语言,它被广泛应用于数字电路设计和硬件描述。

本实验报告将介绍Verilog HDL的基本概念和使用方法,并通过实验展示其在数字电路设计中的应用。

实验目的:1. 了解Verilog HDL的基本语法和结构2. 掌握Verilog HDL的模块化设计方法3. 熟悉Verilog HDL的仿真和综合工具的使用实验内容:1. Verilog HDL的基本语法和结构Verilog HDL是一种硬件描述语言,其语法和结构类似于C语言。

它包括模块定义、端口声明、信号赋值等基本元素。

在本实验中,我们将学习如何定义Verilog模块,并使用端口声明和信号赋值描述数字电路的行为。

2. Verilog HDL的模块化设计方法Verilog HDL支持模块化设计,可以将复杂的电路分解为多个模块,每个模块描述一个子电路的行为。

在本实验中,我们将学习如何设计和实现Verilog模块,并将多个模块组合成一个完整的数字电路。

3. Verilog HDL的仿真和综合工具的使用Verilog HDL可以通过仿真工具进行功能验证,也可以通过综合工具生成实际的硬件电路。

在本实验中,我们将使用Verilog仿真工具对设计的数字电路进行功能验证,并使用综合工具生成对应的硬件电路。

实验步骤:1. 学习Verilog HDL的基本语法和结构2. 设计一个简单的数字电路,并实现Verilog模块描述其行为3. 使用仿真工具对设计的数字电路进行功能验证4. 使用综合工具生成对应的硬件电路实验结果:通过本实验,我们学习了Verilog HDL的基本概念和使用方法,并成功设计和实现了一个简单的数字电路。

我们使用仿真工具对设计的数字电路进行了功能验证,并使用综合工具生成了对应的硬件电路。

实验结果表明,Verilog HDL在数字电路设计中具有重要的应用价值。

《FPGA系统设计》实验报告》时序逻辑电路的设计

《FPGA系统设计》实验报告》时序逻辑电路的设计

一、设计任务

分别设计并实现锁存器、触发器的VHDL模型。

二、设计过程

1、同步锁存器:

同步锁存器是指复位和加载功能全部与时钟同步,复位端的优先级较高。

下图为同步锁存器的VHDL程序及模型:

2、异步锁存器:

异步锁存器,是指复位与时钟不同步的锁存器。

下图为同步锁存器的VHDL程序及模型:

3、D触发器:

D触发器是最常用的触发器。

下图为简单D触发器的VHDL 模型:

4、T触发器:

T触发器的特点是在时钟沿处输出信号发生翻转。

按

照有无复位、置位信号以及使能信号等,T触发器也有多种类型。

下图为带异步复位T触发器的VHDL模型:

5、JK触发器:

JK触发器中,J、K信号分别扮演置位、复位信号的角色。

为了更清晰的表示出JK触发器的工作过程,以下给出JK触发器的真值表(如表1所示)。

表1 JK触发器真值表

按照有无复位、置位信号,常见的JK触发器也有多种类型,下图带异步复位(clr)、置位(prn)的JK触发器的VHDL模型:

三.总结

本次实验中较为顺利,在第一次课的时间内我就已经完成了必做实验与选作实验。

在实验的过程中,在防抖电路处有了较大的困难。

由于仿真中不存在此问题,在实际操作中参数选择时遇到了一定的困难。

在反复比对效果之后,我

确定了电路的参数,实现了防抖功能。

通过这次实验,我对时钟脉冲、计数器等有了更加深入的认识与理解。

数字系统设计与Verilog HDL实验报告(二)

《数字系统设计与Verilog HDL》实验报告(二)班级:自动1003班姓名:**学号:********实验二、四位并串转换电路一、实验目的1、了解及掌握时序电路的基本结构常用数字电路;2、通过ModelSim软件编写时序电路的程序进行仿真和调试。

二、实验内容1、熟悉时序电路中时钟的同步与异步用法;2、编写一个四位并串转换设计程序以及测试该模块的测试程序,要求如下:(1)输入一个四位二进制数pin;(2)每个时钟周期按从左往右的顺序输出一位pin的二进制位的数。

三、实验步骤及源程序新建工程及文件,分别添加设计程序及测试程序,进行编译及纠错,编译通过后运行程序仿真进行调试得出结果。

设计模块:module para_to_serial4(pin,clk,reset,sout);input [3:0] pin;input clk,reset;output sout;reg sout;reg [3:0] data;always @(posedge clk or negedge reset)beginif(~reset)beginsout<=1'b0;data<=pin;endelsebegindata<={data[2:0],data[3]};sout<=data[3];endendendmodule测试模块:`timescale 1ns/1nsmodule test_para_to_ser;wire sout;reg [3:0] pin;reg clk,reset;para_to_serial4 test1(pin,clk,reset,sout);initialbeginclk=1'b0;reset=1'b0;#5 reset=1'b1;#300 $stop;endinitialpin=4'b1001;always#5 clk=~clk;endmodule四、实验结果五、实验心得体会这次试验相对于上次有了一定的难度,由于这门课程刚开始学习,我还不能很好地从宏观把握这门课程,对这门课程的认识和理解还不够深刻,所以做实验时遇到了一些困难,虽然找了一些参考资料,有一定的帮助,但最后还是有点纠结,最终在和同学的交流中才比较深刻的对实验有了了解。

verilog_hdl电子时钟实验报告

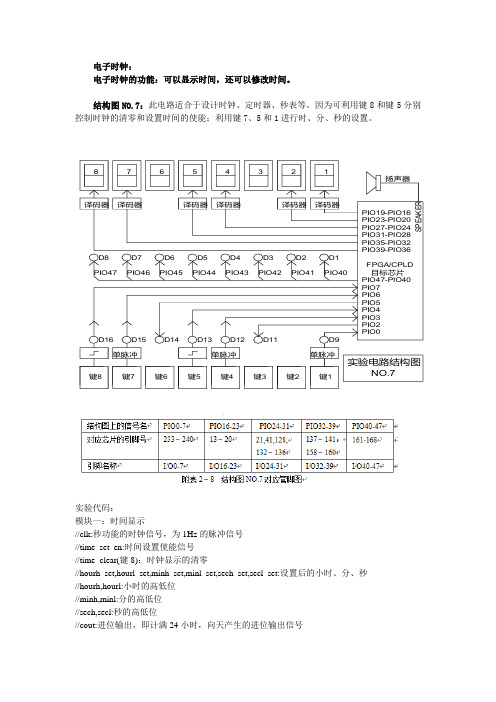

电子时钟:电子时钟的功能:可以显示时间,还可以修改时间。

结构图NO.7:此电路适合于设计时钟、定时器、秒表等。

因为可利用键8和键5分别控制时钟的清零和设置时间的使能;利用键7、5和1进行时、分、秒的设置。

D16D15D14D13D12D11D9D8PIO47D7PIO46D6PIO45D5PIO44D4PIO43D3PIO42D2PIO41PIO40D1NO.7实验电路结构图SPEAKER扬声器FPGA/CPLD目标芯片12345678PIO0PIO2PIO3PIO4PIO5PIO6PIO7单脉冲单脉冲单脉冲键1键2键3键4键5键6键7键8PIO47-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器实验代码:模块一:时间显示//clk:秒功能的时钟信号,为1Hz的脉冲信号//time_set_en:时间设置使能信号//time_clear(键8):时钟显示的清零//hourh_set,hourl_set,minh_set,minl_set,sech_set,secl_set:设置后的小时、分、秒//hourh,hourl:小时的高低位//minh,minl:分的高低位//sech,secl:秒的高低位//cout:进位输出,即计满24小时,向天产生的进位输出信号moduletime_count(clk,time_set_en,time_clear,hourh_set,hourl_set,minh_set,minl_set,sech_set,secl_set,h ourh,hourl,minh,minl,sech,secl);input clk;input time_set_en,time_clear;input[3:0]hourh_set,hourl_set,minh_set,minl_set,sech_set,secl_set;output[3:0]hourh,hourl,minh,minl,sech,secl;reg[3:0]hourh,hourl,minh,minl,sech,secl;reg c1,c2; //c1和c2分别为秒向分,分向时的进位always@(posedge time_set_en or posedge clk or posedge time_clear)beginif(time_set_en) //time_set_en:时间设置使能信号beginsech<=sech_set;secl<=secl_set;minh<=minh_set;minl<=minl_set;hourh<=hourh_set;hourl<=hourl_set;endelse if(time_clear) //time_clear(键8):时钟显示的清零beginhourh<=0;hourl<=0;minh<=0;minl<=0;sech<=0;secl<=0;endelsebeginif(secl==9) //sech,secl:秒的高低位设置beginsecl<=0;if(sech==5)beginsech<=0;c1<=1;if(minl==9) //minh,minl:分的高低位设置beginminl<=0;if(minh==5)beginminh<=0;c2<=1;if((hourh==2)&&(hourl==3))beginhourh<=0;hourl<=0;endif(hourl==9) //hourh,hourl:小时的高低位设置beginhourl<=0;if(hourh==2)hourh<=0;elsehourh<=hourh+1;endelsebeginhourl<=hourl+1;endendelsebeginminh<=minh+1;endendelsebeginminl<=minl+1;c2<=0;endendelsebeginsech<=sech+1;endendelsebeginsecl<=secl+1;c1<=0;endendendendmodule模块二:时间设置//key7:设置数码管8和7//key4:设置数码管5和4//key1:设置数码管2和1//time_set_en(键5):设置时间的使能端//hourh_set,hourl_set,minh_set,minl_set,sech_set,secl_set:设置后的小时、分、秒//hourh,hourl,minh,minl,sech,secl:当前的小时,分,秒moduletime_set(key7,key4,key1,time_set_en,hourh,hourl,minh,minl,sech,secl,hourh_set,hourl_set,minh_ set,minl_set,sech_set,secl_set);input key7,key4,key1;input time_set_en;input[3:0]hourh,hourl,minh,minl,sech,secl;output[3:0]hourh_set,hourl_set,minh_set,minl_set,sech_set,secl_set;reg[3:0]hourh_set,hourl_set,minh_set,minl_set,sech_set,secl_set;always@(posedge time_set_en)beginif(key7)beginif((hourh_set==2)&&(hourl_set==3))beginhourh_set<=0;hourl_set<=0;endelse if(hourl_set==9)beginhourl_set<=0;if(hourh_set==2)hourh_set<=0;elsehourh_set<=hourh_set+1;endelsebeginhourl_set<=hourl_set+1;endendelse if(key4)beginif(minl_set==9)beginminl_set<=0;if(minh_set==5)beginminh_set<=0;endelseminh_set<=minh_set+1;endelsebeginminl_set<=minl_set+1;endendelse if(key1)beginif(secl_set==9)beginsecl_set<=0;if(sech_set==5)beginsech_set<=0;endelsesech_set<=sech_set+1;endelsesecl_set<=secl_set+1;endelsebeginhourh_set<=hourh;hourl_set<=hourl;minh_set<=minh;minl_set<=minl;sech_set<=sech;secl_set<=secl;endendendmodule模块三:顶层模块//clk:时间计数的时钟信号//time_set_en:设置时间使能信号//time_clear:显示时间清零使能信号//hourh,hourl,minh,minl,sech,secl:当前或设置后的小时,分,秒//key7:设置数码管8和7//key4:设置数码管5和4//key1:设置数码管2和1moduletime_and_set(clk,time_set_en,time_clear,hourh,hourl,minh,minl,sech,secl,key7,key4,key1); input clk;input time_set_en,time_clear;input key7,key4,key1;output[3:0] hourh,hourl,minh,minl,sech,secl;wire[3:0]hh,hl,mh,ml,sh,sl;wire[3:0]hh_set,hl_set,mh_set,ml_set,sh_set,sl_set;time_countU1( .clk(clk),.time_set_en(time_set_en),.time_clear(time_clear),.hourh_set(hh_set),.hourl_set(hl_s et),.minh_set(mh_set),.minl_set(ml_set),.sech_set(sh_set),.secl_set(sl_set),.hourh(hourh),.hourl(ho url),.minh(minh),.minl(minl),.sech(sech),.secl(secl));time_setU2(.key7(key7),.key4(key4),.key1(key1),.time_set_en(time_set_en),.hourh_set(hh_set),.hourl_set (hl_set),.minh_set(mh_set),.minl_set(ml_set),.sech_set(sh_set),.secl_set(sl_set),.hourh(hourh),.hou rl(hourl),.minh(minh),.minl(minl),.sech(sech),.secl(secl));endmodule模块一的时序仿真图:RTL图:引脚图:实验体会:通过这次课程设计,对fpga有了很多的的认识,而且懂得了硬件的更多知识,课程设计过程中,总会遇到很多的问题,然后一起跟同学讨论,或者问老师,解决问题之后感觉收获很多,而且学会了自己独立思考,查询资料。

verilog hdl电子时钟实验报告

电子时钟:电子时钟的功能:可以显示时间,还可以修改时间。

结构图NO.7:此电路适合于设计时钟、定时器、秒表等。

因为可利用键8和键5分别控制时钟的清零和设置时间的使能;利用键7、5和1进行时、分、秒的设置。

D16D15D14D13D12D11D9D8PIO47D7PIO46D6PIO45D5PIO44D4PIO43D3PIO42D2PIO41PIO40D1NO.7实验电路结构图S P E A K E R扬声器FPGA/CPLD 目标芯片12345678PIO0PIO2PIO3PIO4PIO5PIO6PIO7单脉冲单脉冲单脉冲键1键2键3键4键5键6键7键8PIO47-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器实验代码:模块一:时间显示//clk:秒功能的时钟信号,为1Hz 的脉冲信号 //time_set_en:时间设置使能信号 //time_clear(键8):时钟显示的清零//hourh_set,hourl_set,minh_set,minl_set,sech_set,secl_set:设置后的小时、分、秒 //hourh,hourl:小时的高低位 //minh,minl:分的高低位 //sech,secl:秒的高低位//cout:进位输出,即计满24小时,向天产生的进位输出信号moduletime_count(clk,time_set_en,time_clear,hourh_set,hourl_set,minh_set,minl_set,sech_set,secl_set,h ourh,hourl,minh,minl,sech,secl);input clk;input time_set_en,time_clear;input[3:0]hourh_set,hourl_set,minh_set,minl_set,sech_set,secl_set;output[3:0]hourh,hourl,minh,minl,sech,secl;reg[3:0]hourh,hourl,minh,minl,sech,secl;reg c1,c2; //c1和c2分别为秒向分,分向时的进位always@(posedge time_set_en or posedge clk or posedge time_clear)beginif(time_set_en) //time_set_en:时间设置使能信号beginsech<=sech_set;secl<=secl_set;minh<=minh_set;minl<=minl_set;hourh<=hourh_set;hourl<=hourl_set;endelse if(time_clear) //time_clear(键8):时钟显示的清零beginhourh<=0;hourl<=0;minh<=0;minl<=0;sech<=0;secl<=0;endelsebeginif(secl==9) //sech,secl:秒的高低位设置beginsecl<=0;if(sech==5)beginsech<=0;c1<=1;if(minl==9) //minh,minl:分的高低位设置beginminl<=0;if(minh==5)beginminh<=0;c2<=1;if((hourh==2)&&(hourl==3))beginhourh<=0;hourl<=0;endif(hourl==9) //hourh,hourl:小时的高低位设置beginhourl<=0;if(hourh==2)hourh<=0;elsehourh<=hourh+1;endelsebeginhourl<=hourl+1;endendelsebeginminh<=minh+1;endendelsebeginminl<=minl+1;c2<=0;endendelsebeginsech<=sech+1;endendelsebeginsecl<=secl+1;c1<=0;endendendendmodule模块二:时间设置//key7:设置数码管8和7//key4:设置数码管5和4//key1:设置数码管2和1//time_set_en(键5):设置时间的使能端//hourh_set,hourl_set,minh_set,minl_set,sech_set,secl_set:设置后的小时、分、秒//hourh,hourl,minh,minl,sech,secl:当前的小时,分,秒moduletime_set(key7,key4,key1,time_set_en,hourh,hourl,minh,minl,sech,secl,hourh_set,hourl_set,minh_ set,minl_set,sech_set,secl_set);input key7,key4,key1;input time_set_en;input[3:0]hourh,hourl,minh,minl,sech,secl;output[3:0]hourh_set,hourl_set,minh_set,minl_set,sech_set,secl_set;reg[3:0]hourh_set,hourl_set,minh_set,minl_set,sech_set,secl_set;always@(posedge time_set_en)beginif(key7)beginif((hourh_set==2)&&(hourl_set==3))beginhourh_set<=0;hourl_set<=0;endelse if(hourl_set==9)beginhourl_set<=0;if(hourh_set==2)hourh_set<=0;elsehourh_set<=hourh_set+1;endelsebeginhourl_set<=hourl_set+1;endendelse if(key4)beginif(minl_set==9)beginminl_set<=0;if(minh_set==5)beginminh_set<=0;endelseminh_set<=minh_set+1;endelsebeginminl_set<=minl_set+1;endendelse if(key1)beginif(secl_set==9)beginsecl_set<=0;if(sech_set==5)beginsech_set<=0;endelsesech_set<=sech_set+1;endelsesecl_set<=secl_set+1;endelsebeginhourh_set<=hourh;hourl_set<=hourl;minh_set<=minh;minl_set<=minl;sech_set<=sech;secl_set<=secl;endendendmodule模块三:顶层模块//clk:时间计数的时钟信号//time_set_en:设置时间使能信号//time_clear:显示时间清零使能信号//hourh,hourl,minh,minl,sech,secl:当前或设置后的小时,分,秒//key7:设置数码管8和7//key4:设置数码管5和4//key1:设置数码管2和1moduletime_and_set(clk,time_set_en,time_clear,hourh,hourl,minh,minl,sech,secl,key7,key4,key1); input clk;input time_set_en,time_clear;input key7,key4,key1;output[3:0] hourh,hourl,minh,minl,sech,secl;wire[3:0]hh,hl,mh,ml,sh,sl;wire[3:0]hh_set,hl_set,mh_set,ml_set,sh_set,sl_set;time_countU1( .clk(clk),.time_set_en(time_set_en),.time_clear(time_clear),.hourh_set(hh_set),.hourl_set(hl_s et),.minh_set(mh_set),.minl_set(ml_set),.sech_set(sh_set),.secl_set(sl_set),.hourh(hourh),.hourl(ho url),.minh(minh),.minl(minl),.sech(sech),.secl(secl));time_setU2(.key7(key7),.key4(key4),.key1(key1),.time_set_en(time_set_en),.hourh_set(hh_set),.hourl_set (hl_set),.minh_set(mh_set),.minl_set(ml_set),.sech_set(sh_set),.secl_set(sl_set),.hourh(hourh),.hou rl(hourl),.minh(minh),.minl(minl),.sech(sech),.secl(secl));endmodule模块一的时序仿真图:RTL图:引脚图:实验体会:通过这次课程设计,对fpga有了很多的的认识,而且懂得了硬件的更多知识,课程设计过程中,总会遇到很多的问题,然后一起跟同学讨论,或者问老师,解决问题之后感觉收获很多,而且学会了自己独立思考,查询资料。

FPGA——Verilog时序电路实验报告

Verilog设计实验报告唐睿电子工程2011301200062武汉大学电工电子实验教学示范中心集成电路设计实验实验报告:学院:电子信息学院专业:电子信息工程2014 年 5 月7 日实验名称时序逻辑电路基础指导教师曹华伟姓名唐睿年级2011级学号2011301200062 成绩一、预习部分1.实验目的(预期成果)2.实验基本原理(概要)3.主要仪器设备(实验条件,含必要的元器件、工具)1).实验目的1.掌握时序逻辑电路的实现方法;2.了解时序电路的仿真与测试;3.熟悉并理解硬件描述语言;4.用硬件描述语言实现基本时序电路基础的电路;5.在DE2-115开发板中验证并测试其时序逻辑电路功能是否实现。

2).实验基本原理1. D触发器工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD=1且RD=0时(SD的非为0,RD的非为1,即在两个控制端口分别从外部输入的电平值,原因是低电平有效),不论输入端D为何种状态,都会使Q=1,Q非=0,即触发器置1;当SD=0且RD=1(SD的非为1,RD的非为0)时,Q=0,Q非=1,触发器置0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

2. 时序逻辑电路(Sequential Logic Circuit)输出不仅取决于当前输入信号,而且取决于电路之前所处的状态。

基本的时序电路单元有触发器(D、JK、T 等触发器)、锁存器、计数器等。

3. VHDL 中,主要程序分析,时序电路通过process(clk)和if clk’event and clk = ‘1’then 边沿检测语句实现触发器风格的电路;具有非完分支的if、case 语句形成锁存器电路。

例如:process(clk)begin ――D 触发器if (clk’event and clk = ‘1’) thenq <= d; end if;end process;process(g,d) begin ――锁存器if g=1 then q <= d; end if;end process;Verilog HDL 中,时序电路通过always 块语句和@(posedge clk)或@(negedge clk)边沿条件方式实现,例如:always @(posedge clk) //二分频器begin if (! Rst) clk_out = 0;else clk_out =~clk_out; end3. 实验设备与软件平台D E2-115实验板,Q u a r tu s I I v5.0,微型计算机,。

时序逻辑实验报告

一、实验目的1. 理解时序逻辑电路的基本概念和工作原理。

2. 掌握时序逻辑电路的设计方法和测试方法。

3. 熟悉常用中规模集成计数器和寄存器的逻辑功能和使用方法。

二、实验原理时序逻辑电路是指其输出不仅取决于当前输入信号,还取决于电路的过去状态。

本实验主要涉及计数器和寄存器两种时序逻辑电路。

计数器:计数器是一种能够对输入脉冲进行计数的时序逻辑电路。

常见的计数器有二进制计数器、十进制计数器和可编程计数器等。

寄存器:寄存器是一种用于存储二进制信息的时序逻辑电路。

常见的寄存器有D型寄存器、移位寄存器和计数寄存器等。

三、实验设备1. 数字电子技术实验箱2. 示波器3. 信号源4. 集成芯片:74LS163、74LS00、74LS20等四、实验内容1. 计数器设计(1)设计一个4位二进制加法计数器,实现0-15的循环计数。

(2)设计一个10进制计数器,实现0-9的循环计数。

2. 寄存器设计(1)设计一个D型寄存器,实现数据的存储和读取。

(2)设计一个移位寄存器,实现数据的右移和左移。

3. 时序逻辑电路测试(1)测试计数器的计数功能。

(2)测试寄存器的存储和读取功能。

五、实验步骤1. 计数器设计(1)根据计数器的功能要求,设计电路图。

(2)根据电路图,选择合适的集成芯片。

(3)搭建实验电路。

(4)测试计数器的计数功能。

2. 寄存器设计(1)根据寄存器的功能要求,设计电路图。

(2)根据电路图,选择合适的集成芯片。

(3)搭建实验电路。

(4)测试寄存器的存储和读取功能。

3. 时序逻辑电路测试(1)测试计数器的计数功能。

(2)测试寄存器的存储和读取功能。

六、实验结果与分析1. 计数器设计(1)4位二进制加法计数器能够实现0-15的循环计数。

(2)10进制计数器能够实现0-9的循环计数。

2. 寄存器设计(1)D型寄存器能够实现数据的存储和读取。

(2)移位寄存器能够实现数据的右移和左移。

3. 时序逻辑电路测试(1)计数器的计数功能正常。

数字逻辑实验报告-Verilog时序逻辑设计

电子科技大学实验报告学生姓名:任彦璟学号:2015040101018 指导教师:吉家成米源王华一、实验项目名称:Verilog时序逻辑设计二、实验目的:掌握边沿D触发器74x74、同步计数器74x163、4位通用移位寄存器74x194,的工作原理。

设计移位寄存器74x194设计3位最大序列长度线性反馈移位寄存器(LFSR:Linear Feedback Shift Register)计数器。

设计同步计数器74x163 。

三、实验内容:1.设计边沿D触发器74x74。

2.设计通用移位寄存器74x194。

3.采用1片74x194和其它小规模逻辑门设计3位LFSR计数器。

4.设计4位同步计数器74x163。

四、实验原理:74x74逻辑电路图CLK_D CLR_L_DS1_LS1_H S0_LS0_Hw1w2w3w4w5w6w7w8w9w10w11w12w13w14w15w16w17w18w19w20 74x194逻辑电路图3位LFSR逻辑电路图74x163逻辑电路图上图的设计可以采用门级描述,也可以采用教材《数字设计—原理与实践》(第4版)第525页的表8-20中的行为描述五、实验器材(设备、元器件):PC 机、Windows XP 、Anvyl 或Nexys3开发板、Xilinx ISE 14.7开发工具、Digilent Adept 下载工具。

六、实验步骤:实验步骤包括:建立新工程,设计代码与输入,设计测试文件,设置仿真,查看波形,约束与实现、生成流代码与下载调试。

七、关键源代码及波形图:1.D 触发器的Verilog 代码 源码如下module vr74x74(CLK, D, PR_L, CLR_L, Q, QN);input CLK, D, PR_L, CLR_L ;output Q, QN ;wire w1, w2, w3, w4 ;nand (w1, PR_L, w2, w4);nand (w2, CLR_L, w1, CLK) ; nand (w3, w2, CLK, w4) ;仿真结果如下图所示检查输入输出关系,设计无误。

用Verilog-HDL做CPLD设计(时序逻辑电路的实现)

用Verilog-HDL做CPLD设计(时序逻辑电路的实现)第8 讲用Verilog-HDL做CPLD设计时序逻辑电路的实现8.1 闪烁灯的实现8.2 流水灯的实现8.3 可编程单脉冲发生器在第七讲中,已经介绍了组合逻辑电路的实现。

组合逻辑电路的特点是:在任意时刻,电路产生的稳定输出仅与当前时刻的输入有关。

时序逻辑电路则不同于它,其特点是:在任意时刻电路产生的稳定输出不仅与当前时刻的输入有关,而且还与电路过去的输入有关。

本讲中将介绍时序逻辑电路的实现。

8.1 闪烁灯的实现在目标板上,设计有一个10MHz的时钟源。

假如直接把它输出到发光二级管LED,由于人眼的延迟性,我们将无法看到LED闪烁,认为它一直亮着。

如果我们期望看到闪烁灯,就需要将时钟源的频率降低后再输出。

因此,可以采用如图1所示的逻辑功能框图。

图1 闪烁灯的逻辑功能框图其中,CLK表示10MHz的时钟源,作为输入;LED0-LED7表示发光二极管,作为输出;6、44、43、38、37、36、35、40和42是上述变量对应芯片XC9536的引脚。

虚线框中的部分是CPLD设计,用于实现闪烁灯的功能。

如图1所示,在XC9536中,加入计数电路与判别电路。

计数电路可用计数器实现。

每来一个时钟脉冲CLK,计数器就加1。

而每当判断出计数器达到某个数值时,就使得灯LED0-LED7的亮灭反转一次,即:周期性地输出高电平"1"和低电平"0"。

这样设计也就相当于把10MHz的时钟源分频后再输出。

如果最终要使得灯1s闪烁一次,即:输出1Hz的时钟脉冲,就需要把10MHz的时钟经过107分频。

根据上述分析,可以得到下面的Verilog- HDL 描述。

/* 闪烁灯的Verilog-HDL描述*/module LIGHT ( CLK, LED ); // 模块名及端口参数,范围至endmoduleinput CLK; // 输入端口定义,对应第6脚output [7:0] LED;// 输出端口定义,LED[0]-LED[7]分别对应第44、43、38、37、36、35、40和42脚reg [7:0] LED; // 输出端口定义为寄存器型reg [22:0] buffer; // 中间变量buffer定义为寄存器型always @ ( posedge CLK )// always语句,表示每当CLK的上升沿到来时,完成begin-end之间语句的操作begin // 顺序语句,到end止buffer = buffer +1; // 缓冲器buffer按位加1if ( buffer == 23'b11111111111111111111111)// 判别buffer中的数值为(2^23-1)≈10^7时,做输出处理//"23"表示以位计的数值长度,"b"表示二进制,"11…1"表示二进制的数字序列beginLED=~LED; // LED[0]-LED[7]反转一次,即:由0变为1,或由1变为0endendendmodule把以上闪烁灯的描述,用WebPACK Project Navigator软件,生成目标文件,并通过下载电缆写入芯片XC9536中。

数字逻辑实验报告

数字逻辑实验报告实验介绍数字逻辑是计算机科学不可或缺的基础课程,本次实验我们将学习数字逻辑的基本概念,使用Verilog语言实现逻辑电路,并在数字仿真软件中模拟电路的运行过程。

实验目的•理解数字逻辑电路的基本概念和原理;•掌握Verilog语言的基本语法和编程技巧;•学会使用数字仿真软件模拟数字逻辑电路的运行过程。

实验过程实验一:组合逻辑电路的实现本实验中我们将使用Verilog语言实现一个简单的组合逻辑电路。

组合逻辑电路是由一些基本逻辑门连接而成的电路,这些逻辑门输出状态仅受输入状态影响,不受电路的历史状态影响,因此称为组合逻辑电路。

在本实验中,我们将使用Verilog语言实现一个简单的组合逻辑电路,具体如下:module combinational_logic(input a, b, c, output d, e);assign d = ~(a & b);assign e = ~(c | d);endmodule以上Verilog代码实现了一个简单的组合逻辑电路,在电路中有三个输入端口(a、b、c)和两个输出端口(d、e)。

其中d输出端口为(a & b)的反相值,e输出端口为(c | d)的反相值。

实验二:时序逻辑电路的实现时序逻辑电路是一种与历史状态相关的电路,因此称为时序逻辑电路。

与组合逻辑电路的不同之处,在于时序逻辑电路有一种状态元件,在时钟信号的驱动下更改其状态。

在本实验中,我们将使用Verilog语言实现一个简单的时序逻辑电路,具体如下:module sequential_logic(input clock, reset, input data, output reg q);always @(posedge clock or negedge reset) beginif(!reset) beginq <= 1'b0;endelse beginq <= data;endendendmodule以上Verilog代码实现了一个简单的时序逻辑电路,在电路中有两个输入端口(clock、reset)和一个输出端口(q)。

实验五时序逻辑电路实验报告

实验五时序逻辑电路实验报告一、实验目的1.了解时序逻辑电路的基本原理和设计方法。

2.掌握时序逻辑电路的设计方法。

3.运用Verilog语言进行时序逻辑电路的设计和仿真。

二、实验原理时序逻辑电路是指在电路中引入记忆元件(如触发器、计数器等),通过电路中的时钟信号和输入信号来控制电路的输出。

时序逻辑电路的输出不仅与当前输入有关,还与之前输入和输出的状态有关,因此对于时序逻辑电路的设计,需要考虑时钟信号的频率、输入信号的变化及当前状态之间的关系。

三、实验内容本次实验通过使用Verilog语言设计和仿真下列时序逻辑电路。

1.设计一个10进制累加器模块,实现对输入信号进行累加并输出,并在仿真中验证结果的正确性。

2.设计一个4位二进制计数器模块,实现对输入时钟信号的计数,并在仿真中验证结果的正确性。

3.设计一个4位带加载/清零控制功能的二进制计数器模块,实现对输入时钟信号的计数,并在仿真中验证结果的正确性。

四、实验步骤1.根据实验原理和要求,利用Verilog语言设计10进制累加器模块。

在设计中需要注意时钟的频率和输入信号的变化。

2.编译并运行仿真程序,验证设计的10进制累加器模块的正确性。

3.在设计时钟频率和输入信号变化的基础上,设计4位二进制计数器模块。

4.编译并运行仿真程序,验证设计的4位二进制计数器模块的正确性。

5.在设计4位二进制计数器模块的基础上,引入加载/清零控制功能,设计一个4位带加载/清零控制功能的二进制计数器模块。

6.编译并运行仿真程序,验证设计的带加载/清零控制功能的二进制计数器模块的正确性。

7.总结实验结果,撰写实验报告。

五、实验结果与分析1.经过验证实验,10进制累加器模块能够正确实现对输入信号的累加并输出正确的结果。

2.经过验证实验,4位二进制计数器模块能够正确实现对输入时钟信号的计数,并输出正确的计数结果。

3.经过验证实验,带加载/清零控制功能的二进制计数器模块能够正确实现对输入时钟信号的计数,并在加载或清零信号的控制下实现加载或清零操作。

VerilogHDL基础实验可编程实验报告

可编程逻辑器件设计实验报告实验名称:第二部分:VerilogHDL基础实验实验目的:掌握Quartus II 软件的基本使用方法,完成基本时序电路设计实验时间: 2014 年 06 月 19 日地点: 803实验室学生姓名:学号:实验名称:简单D触发器实验一简单D触发器1、实验步骤(1)创建工程启动New Project Wizard,创建一个工程。

(2)创建文件选择菜单File—>New—>Verilog HDL File,创建一个Verilog HDL文件,在Verilog HDL文件中编写能够完成实验功能的Verilog HDL代码。

(3)编译工程选择菜单Processing —>Start Compilation,或者单击按钮。

(4)观察RTL视图选择菜单Tools—>Netlist Viewers—>RTL Viewer即可生成RTL视图。

(5)仿真1).创建VWF文件选择菜单File—>New—>Vector Waveform File2). 设定“End Time”选择菜单Edit File—> End Time,在弹出的对话框中将Time设置为20us。

3).在VWF文件中输入信号节点选择菜单View—>Utility Windows—>Node Finder,在出现的对话框中将Filter框中设置为Pins:all,再单击List按钮,从端口列表中选择需要观察的并拖到波形编辑窗口中。

4).编辑输入信号波形5).观察仿真结果选择菜单Processing—>Start Simulation,或者单击按钮,观察输出波形。

2. VerilogHDL代码module _DFF (clk,d,q);input clk,d;output q;reg q;always@ (posedge clk)beginq<=d;endendmodule3. RTL 视图4.仿真波形实验二同步置数的D触发器1.实验步骤(1)创建工程启动New Project Wizard,创建一个工程。

时序逻辑电路设计实验-二进制加法计数器

<时序逻辑电路设计实验>实验报告学生姓名:文超周李旭班级学号:1138019 1138033指导老师:潘秀琴<实验报告内容>一、实验名称:时序逻辑电路设计实验二、实验学时:5学时三、实验目的:1、掌握Verilog HDL 时序电路的设计方法,重点练习条件语句、always模块、和寄存器型变量使用方法。

2、了解常用时序逻辑电路(计数器)中清零和使能控制的概念,以及同步清零、异步清零、同步置数、异步置数的区别。

四、实验内容1、用Verilog HDL设计同步二进制加法计数器,并对其进行功能仿真。

2、用Verilog HDL设计加减可控的二进制计数器,并对其进行功能仿真。

五、实验原理计数器是最常用的时序逻辑电路,从计算机的微处理器地址发生器到频率计都需要用到计数器。

常见计数器有加法计数器和减法计数器。

加法计数器时根据二进制加法原理,每来一个脉冲计数值加1;减法计数器根据二进制减法原理每来一个脉冲计数器值减1。

同一计数器兼具有加法和减法功能,成为加减可控计数器或可逆计数器。

六、实验步骤1、认真阅读实验目的、内容及要求,清楚实验的具体步骤。

2、根据实验要求查阅相关学习资料,整理完成本实验任务的基本思路并完成实验的代码编写。

3、逻辑功能代码编写:根据确定的实现方案,在软硬件实验环境下,用VerilogHDl语言进行可编程逻辑电路功能设计,完成程序代码编写。

4、逻辑功能检查:认真分析所编写代码是否能够实现实验任务所要求的功能,如果有不符合的地方,对代码逻辑电路功能描述进行修改,确认正确进入下一步。

5、编译并进行代码修改和完善:对编写完成的代码进行编译,并对编译过程中出现的错误进行语法修改,直至编译完全通过。

6、功能仿真:建立波形文件,对所涉及时序电路进行功能仿真,认真分析时序所描述的功能与所要求的功能是否符合,如果不符合重复本部分规定的内容或者程序中变量端口模块的定义应用是否正确等内容,直至功能仿真完全正确。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

时序逻辑电路的Verilog HDL 实现

一.实验要求

(1):编写JK 触发器、8位数据锁存器、数据寄存器的Verilog HDL 程序,并实现其仿真及其测试程序;

(2):在实验箱上设计含异步清零和同步使能的计数器。

(3):进行波形仿真测试后;画出仿真波形。

(4):写出实验心得

二.实验内容:

(1)1.JK 触发器的元件符号如图7.14所示,其中J 、K 是数据输入端,CLR 是复位控制输入端,当CLR=0时,触发器的状态被置为0态;CLK 是时钟输入端;Q 和QN 是触发器的两个互补输出端。

JK 触发器的状态方程为

Q n+1 =J Q n +K Q n

JK 触发器的verilog HDL 程序

module jkff_rs(clk,j,k,q,rs,set); input clk,j,k,set,rs;

output reg q;

always@(posedge clk,negedge rs,negedge set)

begin if(!rs) q<=1'b0;

else if(!set) q<=1'b1;

else case({j,k})

2'b00:q<=q;

2'b01:q<=1'b0;

2'b10:q<=1'b1;

2'b11:q<=~q;

default:q<=1'bx;

endcase

end

endmodule

JK 触发器的功能:带异步清0,异步置1(低电平有效)

JK 触发器的仿真结果

JK 触发器的元件符号

2.8位数据锁存器锁存器元件符号如图所示。

CLR是复位控制输入端,当CLR=0时,8位数据输出Q[7..0]=00000000。

ENA是使能控制输入端,当ENA=1时,锁存器处于工作状态,输出Q[7..0]=D[7..0];ENA=0时,锁存器的状态保持不变。

OE是三态输出控制端,当OE=1时,输出为高阻态;OE=0时,锁存器为正常输出状态。

8位数据锁存器元件符号

8位数据锁存器的verilog HDL程序

module tt1373(le,oe,q,d);

input le,oe;

input[7:0] d;

output reg[7:0] q;

always @(le,oe,d)

begin if((!oe)&&(le))q<=d;

else q<=8'bz;

end

endmodule

8位数据锁存器的功能:锁存器一次锁存8位数据,功能类似74LS373 8位数据锁存器的仿真结果

3.8位数据寄存器电路的元件符号如图7.18所示,其中CLR 是复位控制输入端;LOD 是预置控制输入端;S 是移位方向控制输入端,当S=1时,是右移移位寄存器,S=0时,是左移移位寄存器;DIR 是右移串入输入信号;DIL 是左移串入输入信号。

数据寄存器的verilog HDL 程序

module reg_w(dout,din,clk,clr);

parameter WIDTH=7;

input clk,clr;

input [WIDTH:0] din;

output reg[WIDTH:0] dout;

always@(posedge clk,posedge clr)

begin if(clr) dout<=0;

else dout<=din;

end

endmodule

数据寄存器的功能:该8位数据寄存器每次对8位并行输入的数据信号进行同步寄存,且具有异步清零端(clr )

数据寄存器的仿真结果

(2).8位二进制计数器的元件符号如图7.20所示,CLR 是复位控制输入端;ENA 是使能控制输入端;LOAD 是预置控制输入端;D[7..0]是8位并行数据输入端;UPDOWN 是加减控制输入端,当UPDOWN=0时,计数器作加法操作,UPDOWN=1时,计数器作减法操作;COUT 是进/借位输出端。

8位二进制计数器元件符号

含异步清零和同步使能的计数器的verilog程序

module CNT4B(CLK,RST,ENA,CLK_1,RST_1,ENA_1,OUTY,COUT); input CLK,RST,ENA;

output CLK_1,RST_1,ENA_1;

output[3:0] OUTY;

output COUT;

reg[3:0] OUTY;

reg COUT;

wire CLK_1;

wire RST_1;

wire ENA_1;

assign CLK_1 = CLK;

assign RST_1 = RST;

assign ENA_1 = ENA;

always@(posedge CLK or negedge RST)

begin if(!RST)

begin OUTY<=4'b0000;

COUT<=1'b0;

end

else if(ENA) begin OUTY<=OUTY+1'b1;

COUT<=OUTY[0] & OUTY[1] & OUTY[2] & OUTY[3];

end

end

endmodule

说明:

rst是异步清0信号,高电平有效;clk是锁存信号;D[3..0]是4位数据输入端;ENA是使能信号

4位计数器的功能:计数使能、异步复位和计数值并行预置

含异步清零和同步使能的计数器的仿真结果

二.实验心得:

很喜欢这种老师的教学方式和考核方式,虽然课时不多,授课不多,但是目的性和灵活性很强。

首先给了我们一些较为简洁的指导,然后分组确定了每个组的课题。

之所以说喜欢这堂课是因为享受到了把看是不可能变为可能进而到实现的过程。

起初很摸不着头脑,比较浮躁。

经过和小组的讨论后,平静了不少,也受益很多。

然后开始着手在网上寻找各种有用的资料,静下心去阅读和思考。

慢慢地有了一点点小成果,回寝室也多了一个目标。

合作,多途径解决方案,这就是我受益最大的。

这仅仅是一个开始,但绝不是结束。

最后挺感谢漆老师的,经过这堂课的启迪,我懂得了不少方法,我会继续努力!加油。