微电子技术新进展

微电子技术的创新与发展

微电子技术的创新与发展引言:微电子技术作为一门先进的技术领域,在近几十年来发展迅速。

它的创新和发展为全球电子行业带来了巨大的进步和变革。

本文将围绕微电子技术的创新与发展展开讨论,包括新材料、封装技术、集成电路设计以及应用领域的拓展等方面。

一、新材料的应用与创新微电子技术的创新离不开新材料的应用。

近年来,石墨烯等新材料的引入使得微电子器件的性能得到了极大的提升。

石墨烯具有优良的电子输运性质和热传导性能,它被广泛应用于高速、高频和低功耗的移动通信芯片中,推动了移动通信技术的快速发展。

此外,氮化镓等宽禁带半导体材料的应用也使得功耗更低、工作速度更高的集成电路成为可能。

二、封装技术的创新与推动封装技术是微电子产品中不可或缺的环节之一。

随着集成度的提高,芯片封装也在不断创新。

例如,三维封装技术使得芯片的堆叠更加紧密,减小了元件之间的距离,提高了互连效率。

此外,先进的热管理技术也为芯片的稳定运行提供了保障。

具有自修复功能的封装材料可以修复封装中出现的微裂纹和缺陷,延长了芯片的使用寿命。

三、集成电路设计的突破与创新集成电路设计是微电子领域的核心之一。

随着技术的进步,芯片的集成度不断提高,而设计的复杂性也在迅速增加。

在此背景下,创新的设计方法和工具应运而生。

通过引入先进的算法和优化方法,设计师可以在保证芯片性能的同时,减小功耗、缩短设计周期。

同时,人工智能的发展也为集成电路设计带来了新的机遇。

基于机器学习和神经网络的设计工具,能够提供更高效和准确的设计方案。

四、微电子技术的应用领域拓展微电子技术的创新与发展不仅仅局限于电子领域,它也在其他领域发挥着重要的作用。

例如,在医疗领域,微电子传感器可以实时监测患者的生命体征,用于诊断和治疗疾病。

在能源领域,微电子技术的创新使得太阳能电池、锂电池等能源设备的性能得到提升,并推动了新能源的发展。

在环保领域,微电子技术的应用使得智能监控系统可以实时感知环境信息,实现资源的高效利用。

微电子制造技术的新进展与发展趋势

微电子制造技术的新进展与发展趋势微电子制造技术是当今信息时代的重要支撑之一。

随着信息技术的高速发展,微电子制造技术也在不断进步和发展。

本文将从微电子制造技术的新进展和未来发展趋势两个方面进行探讨。

一、微电子制造技术的新进展随着国内外市场对高品质电子产品需求的日渐增加,微电子制造技术在整个电子产业链中的作用越来越明显。

与此同时,随着人工智能、物联网、云计算等新技术的不断涌现,微电子制造技术也在不断革新和升级。

1、新型晶体管的涌现在微电子制造技术中,晶体器件是非常重要的一环。

传统的CMOS(互补金属氧化物半导体)技术,在达到4nm左右时遇到了困境。

但随着新型晶体管的涌现,这一限制得到了很大程度的突破。

例如,半金属半绝缘体场效应晶体管(FinFET)和多峰形蜗牛晶体管(MBCFET)等,在提高晶体管性能的同时,降低了功耗和散热问题,有望成为未来计算机芯片制造的新选择。

2、3D打印技术的应用3D打印技术的出现,为微电子制造技术带来了全新的突破。

该技术可以用于制造传统的电子元器件,也可以用于制造微纳米制造模板,甚至可以用于直接打印出基于碳纳米管和石墨烯等材料的电子元件。

这些技术对于微电子制造的材料和器件研究,带来了更为广阔的空间。

3、高清晰度显示器的生产高清晰度(High-Definition,简称HD)显示器可以提供更加清晰明晰的显示效果,已经成为移动设备、电视机等电子产品市场的主流趋势。

为了满足市场需求,微电子制造技术也在不断加强高清晰度显示器的制造技术。

例如,在制造宽色域显示器时,采用了类似于“白色LED + 红绿蓝荧光粉”的方式,提高了显示器的亮度和色彩还原度。

二、微电子制造技术的发展趋势除了新型晶体管、3D打印和高清晰度显示器等技术的突破,微电子制造技术在未来的发展趋势中还有以下几个方面的重点发展:1、低功耗和高信噪比低功耗和高信噪比是微电子制造技术需要持续发展的一个方向。

随着物联网的兴起,各种传感器的应用日益广泛。

微电子技术微型电子器件与电路的研究与应用

微电子技术微型电子器件与电路的研究与应用微电子技术是近年来快速发展的一门前沿技术,它涉及微型电子器件和电路的设计、制造、测试和应用等多个领域。

本文将介绍微电子技术在微型电子器件与电路研究和应用方面的一些重要进展和应用案例。

一、微电子器件的研究与应用1. MOSFETMOSFET是微电子器件中的一种关键器件,它是现代集成电路的基础。

通过研究不同工艺参数对MOSFET性能的影响,可以实现器件的优化设计。

同时,MOSFET在数字电路、模拟电路和功率电子等领域都有广泛应用。

2. MEMSMEMS(Micro-Electro-Mechanical Systems)是一种将微机械系统与微电子技术相结合的新颖技术。

通过微纳加工工艺,制造出微小的机械结构,并借助电子技术对其进行控制和感知。

MEMS在加速度计、陀螺仪、微型传感器等领域有广泛应用。

3. NEMSNEMS(Nano-Electro-Mechanical Systems)是MEMS技术的延伸,主要研究纳米尺度的微型机械系统。

NEMS的特点是尺寸更小、力学性能更好,具有更高的灵敏度和更低的功耗。

NEMS在生物传感、纳米机器人等领域有重要应用前景。

二、微型电子电路的研究与应用1. 集成电路集成电路是将数百万甚至上亿个微型电子器件集成在一个芯片上的产物。

通过研究不同的集成电路设计与制造工艺,可以实现电路的小型化、高速化和低功耗化。

集成电路在计算机、通信、消费电子等领域的应用十分广泛。

2. 射频电路射频电路是指在无线通信系统中起中频、射频信号放大与处理的电路。

通过研究射频电路的设计和优化,可以实现无线通信设备的高性能和高可靠性。

射频电路在无线电通信、雷达、卫星通信等领域发挥重要作用。

3. 数模混合电路数模混合电路是指将数字电路和模拟电路相结合的电路。

它能够在数字信号处理的同时实现高精度的模拟信号处理,具有广泛的应用前景。

数模混合电路在音频处理、图像处理、模拟信号采集等领域有重要作用。

微电子技术的发展现状与未来趋势

微电子技术的发展现状与未来趋势随着科技的迅猛发展,微电子技术作为电子领域的重要组成部分,正以令人瞩目的速度不断发展。

在今天的社会中,微电子技术已经无处不在,从我们日常使用的手机、电脑到各种智能设备,都离不开微电子技术的应用。

本文将从多个角度来探讨微电子技术的发展现状和未来趋势。

首先,我们来看看微电子技术的现状。

目前,微电子技术在各个领域都发挥着重要作用。

在通信领域,微电子技术使得无线通信更加便捷和高效,推动了移动互联网的迅猛发展。

在医疗领域,微电子技术被广泛应用于生物传感器、医疗设备等方面,为医疗行业带来了巨大的进步。

另外,在能源领域,微电子技术也有重要作用,例如太阳能电池、高效节能的微处理器等。

总之,微电子技术的广泛应用使得我们的生活变得更加便利和高效。

然而,我们也应该认识到,微电子技术发展中存在一些挑战和问题。

首先,尽管微电子技术已经取得了巨大的进步,但是其制造成本仍然较高,这限制了其应用范围的扩大。

其次,由于微电子技术对环境的敏感性,电子废弃物的增加成为了一个难题。

此外,微电子技术的安全性问题也备受关注。

随着互联网的普及,网络安全问题对于微电子技术的发展具有重要影响。

因此,在微电子技术的发展过程中,我们需要找到解决这些问题的方法,以推动其向更高水平发展。

接下来,我们来探讨一下微电子技术的未来趋势。

可以预见的是,随着人工智能和物联网技术的不断发展,微电子技术将会在更多领域得到应用。

例如,在智能家居领域,微电子技术可以实现设备之间的互联互通,使得家居设备更加智能化和便捷。

此外,随着可穿戴设备的普及,微电子技术也将在健康监测、运动追踪等方面发挥作用。

更重要的是,微电子技术的应用将会渗透到更广泛的生活领域,从而改变我们的生活方式。

未来,微电子技术的发展还将面临新的挑战和机遇。

首先,研发更先进的微电子器件和材料将是发展的关键。

例如,研究新型半导体材料、设计更小尺寸的集成电路等将推动微电子技术向更高级别发展。

电子学的新进展和技术应用

电子学的新进展和技术应用电子学作为一门应用广泛的学科,在科技领域中发挥着重要的作用。

如今随着科技的进步,不断涌现出新的电子学技术和应用。

本文将探讨一些新的进展和技术应用,介绍它们在实际生活中的应用,以及其对未来科技发展的影响。

1. 微电子技术微电子技术是电子学中的一个分支,它涉及了电子学、材料学、物理学等多个领域。

随着集成电路的快速发展,现在已经进入了纳米时代,很多芯片尺寸已经缩小到了纳米级别。

这种技术的先进性与其成本效益非常佳,因此在很多领域得到了广泛应用。

微电子技术的应用范围非常广泛,比如在医疗领域,它可以用于制造病人监测器和移动医疗设备等。

另外,由于微电子技术具有高度可靠性和集成度高等优点,因此可以被应用到汽车和交通系统中。

2. 智能电子设备随着人们对生活质量要求的提高,传统家电产品已经不能满足人们的需要,智能电子设备因此应运而生。

智能电子设备的优点在于可以通过互联网技术进行远程控制,具有较高的便利性和安全性。

目前,智能电子设备已经广泛应用到家庭、商业和工业等方面。

智能家居系统是智能电子设备中的一个新兴领域,它可以实现家居环境的自动化控制,例如灯光、温度、安防等。

此外,智能家居系统还可以集成多种设备,如Wi-Fi、蓝牙和红外遥控等,实现智能家居的互联。

3. 可穿戴电子设备可穿戴电子设备是近年来广泛研究的一个领域,随着物联网技术的发展,可穿戴电子设备已经成为人们日常生活中不可缺少的一部分。

它们可以被用于运动监测、医疗检测、身体健康管理等领域,设计紧凑、便携且容易使用。

目前市场上已经有很多可穿戴电子设备,例如智能手表、智能眼镜和智能健身手环等。

这些设备具有多种功能,如计步器、心率检测器、血压计等。

4. 可再生能源技术可再生能源技术是全球能源转型的一个重要方向,其目的是通过利用自然资源,例如太阳能和风能,替代传统的化石能源,减少造成的环境问题。

这种技术的发展已经得到了政府和企业的广泛关注,成为一种热门研究方向。

微电子技术新进展

二、微电子技术的主要发展方向(2)

集成电路追求目标3G(G=109)---3T(T=1012) 存储量(GB—TByte) 速度(GHz—THz)、 数据传输率(Gbps- Tbps, bits per second)

Single die Wafer

Going up to 12” (300mm)

缩小器件的特征尺寸

所谓特征尺寸是指器件中最小线条宽度,常常作为技 术水平的标志。对MOS器件而言,通常指器件栅电极所决 定的沟道几何长度,是一条工艺线中能加工的最小尺寸, 也是设计采用的最小设计尺寸单位(设计规则)。

缩小特征尺寸从而提高集成度是提高产品性能/价格 比最有效手段之一。只有特征尺寸缩小了,在同等集成度 的条件下,芯片面积才可以做得更小,而且可以使产品的 速度、可靠性都得到提高,相应成本可以降低。

P6 (Pentium Pro) in 1996

150 to 200 MHz clock rate

196 mm**2 5500K transistors (external cache)

0.35 micron 4 layers metal 3.3volt VDD >20W typical power

反型层的 量子化效应

考虑量子化效应 的器件模型

电源电压1V时,栅介质层中电场 约为5MV/cm,硅中电场约1MV/cm

可靠性

➢诞生基于新原理的器件和电路

… ...

NANOELECTRONIC DEVICE OPTIONS

微电子封装技术的研究现状及其应用展望

微电子封装技术的研究现状及其应用展望近年来,随着电子产品的快速普及和电子化程度的不断提高,微电子封装技术越来越引起人们的重视。

微电子封装技术主要是将电子器件、芯片及其他微型电子元器件封装在合适的封装材料中以保护它们免受机械损伤和外部环境的影响。

本文将分析现有微电子封装技术的研究现状,并探讨其未来的应用前景。

一、微电子封装技术的研究现状随着电子元器件不断地微型化、多功能化、高集成化和高可靠化,微电子封装技术越来越得到广泛的应用和发展。

在微电子封装技术中,主要有以下几种常用的封装方式:1. 线路板封装技术线路板封装技术(PCB)是较为常见的一种微电子封装技术。

这种方式主要利用印刷板制成印刷电路板,并通过它与芯片之间实现联系,使其具有一定能力。

通常,PCB 封装技术可用于集成电路和大多数微型传感器中的有效信号接口。

2. QFP 封装技术QFP 封装技术指的是方形封装技术,它是一种常见的微电子封装技术,这种技术的特点在于其实现方式非常灵活,具有高密度、高可靠的特点。

这种技术可以用于各种芯片、集成电路、传感器和其他各种微型电子元器件的封装。

3. BGA 封装技术BGA 封装技术指的是球格阵列封装技术,这种技术主要利用钎接技术将芯片连接到小球上。

BGA 封装技术常用于高密度封装尺寸的芯片和集成电路中,并具有高可靠和高信号性能等特点。

它目前被广泛应用于计算机芯片、消费电子、汽车电子、无人机和航空电子等领域中。

4. CSP 封装技术CSP 封装技术指的是芯片级封装技术,该技术是近年来发展起来的一种新型微电子封装技术,主要是使用钎接工艺将芯片封装在封装材料上。

CSP 封装技术具有极小的尺寸和高密度、高可靠性、高信号性能和高互连和生产效率等优点,因此,它被广泛地应用于各种电子元器件和集成电路中。

二、微电子封装技术的应用展望微电子封装技术具有比传统封装技术更高的密度、高速度、高可靠性和多功能的优点,因此,它的应用前景是广阔的。

微电子器件封装技术的优化与创新

微电子器件封装技术的优化与创新微电子器件是现代电子技术的基础,它的封装技术也是电子制造业中不可或缺的一部分。

随着科技的发展和创新,微电子器件封装技术也在不断地进行优化和创新,以满足日益增长的市场需求。

本文将探讨微电子器件封装技术的优化与创新,以及未来的发展趋势。

一、微电子器件封装技术的发展历程微电子器件封装技术最初出现在20世纪50年代。

当时的封装方式主要是使用外框、连接线、引脚等元器件进行封装。

后来,随着集成电路技术的不断发展,微电子器件的封装技术也在不断地进行更新换代。

目前,微电子器件的封装方式主要分为裸芯片封装和模块化封装两种。

其中,裸芯片封装是指将芯片直接固定在印刷电路板上,并进行导线连接,免去其他部件的使用;而模块化封装则是将芯片、电源、传感器等元器件放置在一起,形成一个整体模块。

二、微电子器件封装技术的优化与创新1. 封装材料的多元化在传统的微电子器件封装技术中,使用的封装材料主要是塑料和陶瓷。

但随着人们对封装材料性能的要求不断提高,越来越多的新型封装材料也被引入使用。

例如,金属基板、硅胶、环氧树脂等材料的应用,可以提高封装材料的耐热性、耐腐蚀性以及抗震动性能,进一步提高了微电子器件的可靠性和性能稳定性。

2. 封装工艺的精细化封装工艺的精细化是微电子器件封装技术创新的另一个方向。

目前,很多公司都在研究和使用微纳米技术,将封装工艺做的更加细致化。

例如,采用微纳米技术可以实现微纳米级别的电子线路制作和微型结构制造,使得微电子器件封装更加精细化。

3. 三维封装技术三维封装技术是指将芯片垂直堆叠,以达到空间利用效率的最大化。

与传统封装技术相比,三维封装技术具有更小的体积、更高的集成度和更快的传输速度等优点。

这种技术的应用已经广泛进入到手机、电脑、平板等产品中,有望成为未来微电子器件封装技术的发展趋势。

三、未来的发展趋势1. 大规模集成未来的微电子器件封装技术将实现更高的功率密度、更多的信号处理功能、更快的运算速度和更低的功耗水平。

超导技术在微电子学中的应用进展

超导技术在微电子学中的应用进展引言近年来,随着科技的不断发展,超导技术在微电子学领域中的应用进展取得了显著的突破。

超导技术以其低电阻、高电流密度和零电阻的特性,为微电子学领域带来了许多新的机遇和挑战。

本文将探讨超导技术在微电子学中的应用进展,并分析其对微电子学领域的影响。

一、超导材料在微电子学中的应用1. 超导电路超导电路是超导技术在微电子学中的一项重要应用。

超导电路具有零电阻的特性,能够实现高速、低功耗的信号传输。

目前,超导电路已经广泛应用于微处理器、通信设备等领域。

例如,超导量子比特(Qubit)是实现量子计算的关键元件,其采用超导电路实现了量子态的存储和操作,为量子计算的发展提供了新的可能性。

2. 超导传感器超导传感器是超导技术在微电子学中的另一项重要应用。

由于超导材料具有极高的敏感度和低噪声特性,因此可以用于制造高灵敏度的传感器。

例如,超导量子干涉仪是一种基于超导材料的传感器,可以用于测量微小的位移、压力和磁场等物理量。

此外,超导传感器还可以应用于医学领域,用于检测人体内部的微小变化,如心电图、脑电图等。

二、超导技术对微电子学的影响1. 提高微电子器件的性能超导技术的应用可以显著提高微电子器件的性能。

由于超导材料具有零电阻的特性,可以大幅度降低器件的功耗和发热量,提高器件的工作效率和可靠性。

此外,超导材料的高电流密度特性可以实现更高的电流传输能力,从而提高微电子器件的工作速度和响应时间。

2. 促进微电子学的创新发展超导技术的应用为微电子学的创新发展提供了新的思路和方法。

例如,超导量子比特的出现为量子计算的实现带来了新的希望,超导传感器的应用为微电子学的传感技术提供了新的可能性。

此外,超导技术还可以与其他新兴技术相结合,如人工智能、物联网等,推动微电子学的跨学科研究和应用。

三、超导技术在微电子学中的挑战和未来发展方向1. 材料研究和制备技术超导技术在微电子学中的应用面临着材料研究和制备技术上的挑战。

2024年微电子封装市场发展现状

微电子封装市场发展现状引言微电子封装是电子行业的一个重要领域,涉及到电子元器件的封装和连接技术。

随着科技的不断进步和应用需求的增长,微电子封装市场正面临着巨大的发展机遇。

本文将对微电子封装市场的现状进行分析和评估,为读者提供市场发展的全面了解。

市场概述微电子封装市场广泛应用于电子设备、通信设备、汽车电子、医疗设备等行业。

随着智能手机、物联网、5G通信等新技术的兴起,对微电子封装的需求不断增长。

根据市场研究机构的数据显示,微电子封装市场规模在过去几年中保持稳定增长,并有望在未来几年内保持良好的发展趋势。

技术进展微电子封装市场的发展得益于技术的不断进步。

随着微电子封装技术的不断升级,封装密度和性能得到了显著提升,同时尺寸和功耗也得到了有效控制。

新的封装技术,例如薄型封装、多芯片封装和三维封装等,为微电子封装市场注入了新的活力。

市场挑战微电子封装市场面临着一些挑战。

首先,封装成本较高,这限制了一些应用领域的发展。

其次,封装技术的发展速度较慢,难以满足新兴应用对性能和功耗的需求。

此外,市场竞争激烈,技术壁垒较高,对企业的创新能力提出了更高的要求。

发展趋势微电子封装市场在未来几年中有望保持持续增长。

首先,5G通信的商用化将推动微电子封装市场的快速发展。

其次,人工智能、物联网等新兴技术的普及将提高对微电子封装的需求。

此外,节能环保、小型化等市场需求也将促进微电子封装技术的创新和升级。

市场竞争格局微电子封装市场竞争激烈,主要厂商包括英特尔、三星电子、台积电、中芯国际等。

这些企业在封装技术研发、生产能力和市场份额方面具有较强优势。

此外,新兴企业也在不断涌现,通过技术创新和市场定位寻求突破。

结论微电子封装市场是一个充满机遇与挑战并存的市场。

随着新技术的不断涌现和应用领域的不断扩展,微电子封装市场有望进一步发展壮大。

为保持竞争力,企业需加强技术创新、提高生产效率,并关注市场趋势的变化,及时调整发展战略。

2023年中国微电子技术政策及环境分析:产业将迎来发展新机遇

2023年中国微电子技术政策及环境分析:产业将迎来发展新机遇中国政府在推动微电子技术产业进展方面实行了多重政策。

其中,投资是最重要的一项。

政府通过设立基金、发放补贴等方式,向微电子技术企业供应融资支持。

除了资金方面的支持,政府还对企业的研发项目赐予了税收优待政策,使得企业能够更好地进行科技创新。

此外,政府还在人才引进和培育方面下了大力气。

政府设立了一系列人才方案,为企业引进了很多高端人才,同时也在高校设立了微电子技术相关专业,培育了更多的人才人才,为企业供应了人才基础。

1、投资政策是中国政府支持微电子技术进展的主要手段之一。

2022年,中国政府宣布投资1000亿元人民币用于支持集成电路产业的进展,这是中国政府历史上最大的一笔投资。

此外,中国政府还设立了很多基金,如中关村国家自主创新示范区重大科技专项基金、国家集成电路产业进展基金等,以吸引更多的投资者进入微电子领域。

除此之外,中国政府还为企业供应了一系列的政策支持,如减免税收、资金扶持等,为企业的进展供应了保障。

这些政策的实施为微电子产业的富强进展奠定了坚实的基础。

2、税收政策是支持微电子企业进展的重要手段之一。

中国政府为了鼓舞企业进行研发,出台了很多税收优待政策。

例如,企业进行研发时发生的费用可以享受税前扣除,享受研发费用加计扣除等政策。

此外,为鼓舞企业进行技术创新,中国政府还推出了一系列的税收减免政策。

这些措施有助于提高企业的创新意识和技术创新力量,促进微电子行业的进展。

3、人才培育政策是支持微电子技术产业进展的重要措施之一。

中国政府在人才培育方面也实行了一系列措施。

政府实施了各种方案,如“千人方案”、“万人方案”等,吸引和培育更多的高级人才,为企业的进展供应了强有力的支持。

此外,政府还鼓舞高校加强与企业的合作,开展校企合作项目,为微电子企业输送更多的人才。

政府的这些政策措施为微电子行业供应了强有力的人才支持,有助于提高企业的技术水平和竞争力。

微电子技术的最新研究进展

微电子技术的最新研究进展微电子技术是一门涉及电子学、物理学、材料学等多学科的交叉学科,其研究范围涉及到微型集成电路、微机电系统、光电子器件、传感器等领域。

这些研究领域的快速发展有助于我们构建更为高效、可靠和智能化的先进电子系统,为我们现代化社会的发展提供了必要的支撑。

近年来,国际上微电子技术领域的学者们不断推进该领域的研究和开发,尤其是在一些最新技术上,取得了相当显著的成就。

本文将介绍微电子技术领域的一些最新进展。

一、三维集成电路技术随着摩尔定律的逐渐失效,三维集成电路技术被认为是摩尔定律的替代方案,其基本原理为将多个微电子器件水平层叠并互相连接,从而在同等面积的基础上提高电子电路的密度、性能和功耗等方面的参数。

三维集成电路技术目前已经成为全球微电子技术研究的热点领域之一。

在三维集成电路技术的研究中,研究者们主要关注如何保证器件层叠时的互连可靠和散热等问题。

近年来,三维集成电路技术的应用逐渐向高端领域、如人工智能、工业4.0、智能汽车等方向发展,为微电子技术的快速发展提供了巨大的推动力。

二、柔性电子学技术柔性电子学技术是指将材料科学和电子学结合,开发制造柔性、弯曲等特殊形状的电子元器件或集成电路,比如可穿戴设备、智能手环、智能贴片、柔性显示器等等。

采用柔性电子学技术的产品,高度集成了多种传感器、微处理器、可穿戴设备等,可长时间稳定运行和持久工作,且使用方便。

柔性电子学技术的开发旨在为传统电子器件提供一个崭新的市场。

当前,柔性电子学技术领域正在快速发展,其主要的技术难点在于如何解决能源、物理和工厂制造等方面的技术瓶颈。

国内外研究者们正在不断突破技术难关,将柔性电子学技术应用在更多的领域中。

三、新型存储器件技术在数字化智能时代,数据存储已成为信息处理的主要方式之一。

新型存储器件技术的研究为提高数据存储的效率和安全性提供了更多的可能性。

其中,非易失性存储器件是当前新型存储器件技术开发中的一个重要方向。

微电子技术的研究进展与应用前景

微电子技术的研究进展与应用前景随着科技的不断发展,微电子技术已经成为当今世界快速发展的重要支撑。

微电子技术的研究和应用的不断扩大,给人们的生活和工作带来了丰富多样的变化,未来发展的前景也十分广阔。

微电子技术,顾名思义就是微小的电子器件。

它已经深入到我们日常生活中的方方面面。

从智能手机、平板电脑,到汽车、反恐监控,微电子技术的应用几乎涵盖了人们物质生活的各个领域。

而其最为核心的技术——集成电路,又是微电子技术的核心领域。

随着技术的不断革新,集成电路面临的挑战也越来越大,但是它的发展前景依然是十分广阔的。

近年来,由于人工智能、高性能计算等的广泛运用,造成了电路的设计布局更为复杂,同时也增加了功耗、温度变化等因素的影响。

这一影响要求高速、低功耗和温度鲁棒性方面的电路在设计上也必须做出相应的改进。

微电子技术研究所面临的挑战使得许多科研人员加倍努力,不断推陈出新,花费数年时间钻研一款先进的微电子器件。

幸运的是,近年来发展的微电子技术不仅在计算机工业领域取得了长足的进展,还被广泛应用在高速铁路系统、军事设施、交通运输行业等领域。

最近,由200多个研究组成的盟集团成功研发出16纳米制程电子器件。

同时,五常光电还针对飞行器前缘温度较高情况下风洞和实测环境严酷的实用要求,推出了一款180度宽视角广角图像传感器。

这些成果都是在微电子技术研究所所取得的突破。

随着这些微电子技术的进一步发展,在未来将有望应用于仓储物流、医疗设备、环境检测等更多领域,成为未来经济发展的战略制高点。

微电子技术未来的应用前景还十分广阔。

由于不断创新和技术进步,微电子技术成本会逐渐降低,产品会不断丰富,因此它将进一步推动国家经济和社会发展的成长。

同时,微电子技术是央视科学传媒工作室所关注和纪录片《钱学森》也有介绍到的,它成为了创意有限第三方分公司与复合材料领域合作开发出的新材料——图形砷化镓奠定了稳固基础,为国际产业发展带来创新的方向。

总之,微电子技术的研究和应用对于当今世界的经济和社会发展都是十分重要的。

电子行业微电子技术新进展

电子行业微电子技术新进展引言随着科技的不断进步和全球经济的发展,电子行业正迎来了微电子技术的全新进展。

微电子技术作为集成电路领域的前沿技术,不仅在计算机、通信等领域有广泛应用,也逐渐渗透到智能穿戴设备、物联网和等领域。

本文将介绍电子行业微电子技术的新进展,重点聚焦于芯片制造技术、封装技术和尺寸缩小等方面。

芯片制造技术的新进展近年来,随着电子行业对芯片性能要求的不断提高,芯片制造技术也在不断创新和发展。

以下是电子行业微电子技术芯片制造技术的新进展:1.先进制程技术:先进制程技术是芯片制造技术的核心,它可以实现芯片尺寸的减小和性能的提升。

随着微电子技术的发展,先进制程技术不断推进,从14nm、10nm到7nm和5nm制程,进一步增加了芯片的集成度和性能。

2.三维堆叠技术:三维堆叠技术是一种将多个芯片层次进行堆叠和封装的技术。

通过将不同功能的芯片进行堆叠,可以提高芯片的性能和功耗。

目前,三维堆叠技术已经广泛应用于存储器和处理器等领域,为微电子技术的发展创造了更多可能性。

3.自组装技术:自组装技术是一种新兴的芯片制造技术,通过利用化学、物理和生物学等方法使芯片元件自动组装起来。

相比传统的工艺制造方法,自组装技术可以实现更高的芯片密度和更好的性能。

目前,自组装技术已经在柔性显示器、传感器和太阳能电池等领域取得了一些进展。

封装技术的新进展除了芯片制造技术,封装技术也是微电子技术的重要组成部分。

封装技术可以将芯片与外部环境隔离,并提供保护和连接功能,为芯片的正常运行提供保障。

以下是电子行业微电子技术封装技术的新进展:1.高密度封装技术:高密度封装技术可以将更多的芯片元件集成到较小的封装体积中。

通过使用更小、更紧凑的封装设计,可以提高芯片的集成度和性能。

目前,高密度封装技术已经广泛应用于移动设备、智能穿戴设备和物联网等领域。

2.先进封装材料:先进封装材料是封装技术的关键因素之一。

通过选择适当的封装材料,可以提供更好的热传导、电磁屏蔽和机械强度等性能。

微电子技术发展现状及未来趋势分析的文章

微电子技术发展现状及未来趋势分析的文章微电子技术发展现状及未来趋势分析微电子技术是电子科学与技术中的一个重要分支,主要研究微小尺寸的电子器件及其集成电路。

在过去的几十年里,微电子技术快速发展,深刻改变了我们的生活和工作方式。

本文将对微电子技术的发展现状进行分析,并展望其未来的发展趋势。

首先,我们来看微电子技术的发展现状。

随着尺寸的缩小,微电子技术取得了令人瞩目的成就。

从1965年摩尔定律的提出以来,集成电路中晶体管的数量每隔18-24个月就会翻倍,性能也会提升。

当前,微电子技术已经进入了纳米级尺寸,晶体管的缩小程度达到了十几纳米,甚至更小,这为电子器件的功能集成、性能提升和能耗降低提供了广阔的空间。

其次,微电子技术在各个领域都发挥着重要作用。

在通信领域,微电子技术的应用促进了移动通信设备的普及,实现了信息时代的爆炸式增长。

在医疗领域,微电子器件的应用使得体内植入医疗器械成为可能,提高了医疗的精准度和效率。

在能源领域,微电子技术的进步促进了可再生能源的发展,推动了能源转型。

在智能手机、电子游戏等消费电子产品领域,微电子技术的发展使得产品更加小巧、功能更加强大。

然而,微电子技术的发展也面临一些挑战。

首先是制造工艺的难度增加。

随着尺寸的进一步缩小,微电子器件的制造变得更加复杂,制程步骤更加繁琐,对设备和工艺的要求也越来越高。

其次是能源问题。

微电子器件数量的增加和功耗的增大使得能源需求也相应增加,如何提高电子器件的能效成为亟待解决的问题。

此外,微电子技术的推动也会引发一些社会问题,例如信息安全、隐私保护等问题需要得到更好的解决。

然而,面对这些挑战,未来微电子技术的发展仍然充满希望。

首先,制造工艺的进一步突破将会推动微电子技术的发展。

随着新材料、新工艺的应用,器件制造的纳米级精度将会成为可能,从而提供更高性能和更低功耗的微电子产品。

其次,人工智能和机器学习技术的发展将会为微电子技术的应用带来新的机遇。

例如,在物联网和智能家居领域,微电子技术将与人工智能相结合,实现设备的智能化和自动化。

微电子技术的进展和应用前景

微电子技术的进展和应用前景近年来,随着微电子技术的不断发展,人们在各个领域中看到了它的广泛应用,从智能手机到医疗设备,再到工业自动化等方面,微电子技术的应用前景越来越广阔。

一、微电子技术的进展微电子技术是研究制造微米级别的电子元器件和集成电子系统的科学技术。

现代微电子技术主要集中在芯片制造、封装技术和智能电子系统三方面的研究与开发。

目前,微电子技术已经发展到了纳米级别,这也是未来微电子技术发展的一个新方向。

首先,芯片技术是微电子技术的核心,也是微电子技术发展的重要基础。

随着集成电路设计技术的不断发展和进步,芯片的制造工艺也在不断创新,制造出更小、更快、更精密、更可靠的芯片。

目前,集成度达到了很高的程度,所能提供的功能也越来越全面与多样化。

集成电路的设计当中,采用了CMOS技术,可以使得位于同一芯片上的晶体管达到很高的集成度,并且实现高精度晶振、波形整形电路和微处理器等高性能电子元器件。

此外,3D芯片技术的广泛应用,大大提高了系统的效率和性能。

其次,封装技术是微电子技术的辅助技术,主要是将芯片封装在器件内部,并与外部链接成一个整体。

封装技术的主要目的是保护芯片不受损坏、防潮、防尘等,同时方便芯片的安装和维护。

随着新型材料的不断发现和封装技术的创新,微电子产品的包装尺寸越来越小,处理速度越来越快。

目前,微电子产品多采用之前比较先进的LOCO封装技术,同时,还出现了COB、SMT及TSOP等多种封装技术,为微电子产品提供了更好的封装保护和升级操作能力。

最后,智能电子系统的研发和应用也是微电子技术的重要发展方向。

智能电子系统是具有智能化、自动化功能的电子系统。

随着可编程逻辑设备(芯片)技术和多晶硅技术等的不断发展,智能电子系统已经得到广泛应用,包括智能家居、智能车、智能医疗设备等。

智能电子系统不仅能提高生活水平,还能提高各个行业的效率,创造更多的价值。

二、微电子技术应用前景微电子技术在奇妙世界的应用非常广泛,尤其是在移动通信、半导体、医疗健康、汽车电子等领域。

微电子技术的新进展与新应用

微电子技术的新进展与新应用随着科技的不断进步,微电子技术也逐渐走进了人们的视野,它的应用领域也不断拓宽和深化。

本文将从微电子技术的应用领域、新的研究进展以及新的应用案例三个方面进行阐述。

一、微电子技术的应用领域1. 智能家居智能家居是智能化的住宅环境,它通过各种技术手段和设备,实现对家居设备进行远程控制和集成管理。

现阶段,微电子技术已成为智能家居实现的重要手段之一,比如支持语音识别、环境感知等技术的应用,都需要依赖于芯片技术、传感器技术和算法技术等方面的支持。

2. 物联网物联网是一个庞大的信息交互网络,它以万物互联的方式,实现设备间的互动、数据共享和控制操作等功能。

而其中一个重要的技术手段就是传感器技术,而传感器技术的核心就是微电子技术。

传感器的微型化、高灵敏度和多功能化等优势,可以极大提升物联网设备和系统的智能化和性能。

3. 人工智能人工智能是一种模拟人类智慧的技术,它通过各种算法手段,将大量数据中的模式、规律和关联性提取出来,以实现自主决策、智能推理、语音识别和人脸识别等功能。

同时,人工智能也需要依赖于微电子技术,通过实现芯片的微型化、处理速度的提升等技术,支持各种人工智能算法和应用的实现。

二、微电子技术的新的研究进展1. 集成电路集成电路是一种将大量电子元器件集成在一起的电路,它的发明和应用大大提高了电子产品的性能和质量。

而随着微电子技术的发展,集成电路也在不断迭代和进化。

例如,人工智能芯片、量子芯片、生物芯片等新型芯片的研发,使得芯片性能和功能不断提升,更好地实现各种应用场景。

2. 软硬件一体化软硬件一体化是指将软件和硬件两者集成在一起,形成一个整体,并通过软硬件互联的方式,实现更高效的性能和功能。

而在微电子技术的研发中,软硬件一体化的应用也越来越广泛。

例如,通过采用FPGA芯片、嵌入式系统等方案,实现软硬件混合开发,更好地满足各种应用的要求。

3. 微型化技术微型化技术是指将芯片的尺寸和体积缩小到微米级别或纳米级别的技术,它具有功耗低、速度快、功能强等特点。

未来微电子技术发展的主要挑战是什么?

未来微电子技术发展的主要挑战是什么?微电子技术作为现代信息技术的基石,在过去几十年中取得了惊人的进步,深刻地改变了我们的生活和社会。

从智能手机到超级计算机,从医疗设备到智能汽车,微电子技术的应用无处不在。

然而,随着技术的不断发展和应用需求的日益增长,未来微电子技术也面临着一系列严峻的挑战。

首先,制造工艺的物理极限是当前微电子技术发展面临的重大挑战之一。

随着芯片制造工艺不断推进,晶体管的尺寸已经越来越小,接近了物理极限。

当晶体管的尺寸缩小到一定程度时,量子效应开始显著影响其性能和稳定性。

例如,电子的隧穿效应会导致漏电增加,从而增加功耗和降低芯片的可靠性。

此外,制造工艺的进一步微缩也面临着巨大的技术难题,如光刻技术的精度限制、材料的性能瓶颈等。

为了突破这些限制,研究人员需要探索新的材料、器件结构和制造工艺,例如采用三维集成技术、新型半导体材料(如碳纳米管、石墨烯等)以及量子计算技术等。

其次,功耗问题也是未来微电子技术发展的一个关键挑战。

随着芯片集成度的不断提高,芯片内的晶体管数量急剧增加,导致功耗急剧上升。

高功耗不仅会导致芯片发热严重,影响其性能和可靠性,还会限制芯片在移动设备和物联网等领域的应用。

为了解决功耗问题,需要从多个方面入手。

一方面,需要优化芯片的架构和电路设计,采用低功耗的逻辑设计和电源管理技术;另一方面,需要开发新型的低功耗器件,如隧穿场效应晶体管(TFET)、负电容晶体管(NCT)等。

此外,软件层面的优化也至关重要,通过合理的算法和编程,可以有效地降低芯片的功耗。

再者,性能提升的难度日益增大也是不可忽视的挑战。

尽管芯片的性能在过去几十年中一直遵循摩尔定律快速增长,但随着制造工艺接近物理极限,单纯依靠缩小晶体管尺寸来提升性能变得越来越困难。

为了继续提高芯片的性能,需要在架构创新、多核技术、并行计算等方面取得突破。

同时,如何有效地利用这些技术,充分发挥芯片的性能,也是一个亟待解决的问题。

生物微电子学研究进展

生物微电子学研究进展生物微电子学是一门拼接生物学和电子学的新兴学科,其着眼点在于通过开发微型设备和实现细胞级别的信号检测来进行疾病的精准诊断和治疗。

本篇文章将围绕这一主题,介绍生物微电子学的研究进展。

一、微型生物芯片微型生物芯片是生物微电子学领域的一项基础研究,其主要目标是将细胞培养、细胞检测和细胞控制集成到一个芯片上,为生物学和医学领域提供高通量和高效率的解决方案。

在这方面,哈佛大学的Charles Lieber教授领导的团队取得了突破性进展。

他们成功地发展出了一种新型生物芯片,可以实现精准控制、操作和记录细胞行为。

这一芯片利用了纳米级别的传感器和去污器,可以在不伤害细胞的情况下实现细胞活动的实时监测和控制。

这一技术的进一步完善有望为医学诊断带来革命性的变革。

二、数字PCR技术PCR技术是通过扩增目标DNA片段的数量来进行体外复制的一项基础技术,但是传统的PCR技术需要进行大量的操作和检测,花费时间和精力都极大。

为此,研究人员开发出了数字PCR技术,它可以通过分割样本并在数十万个微小反应室中进行扩增并准确地计数聚合物链式反应产物。

该项技术的研发为精准医疗的实现提供了基础保障。

比如,加州大学伯克利分校的Luke Lee教授发明了一种名为“nanoPCR”的数字PCR技术,它可以在非常短的时间里完成PCR扩增,而且无需设备和供能。

预计这一技术将极大地推动医疗领域的进步。

三、基因编辑技术基因编辑技术是生物微电子学领域的重要组成部分,它可以通过修改细胞的基因组来纠正遗传性疾病。

在这方面,CRISPR-Cas9基因编辑技术备受关注。

该项技术利用特殊酶将DNA特定区域进行切割,然后将人工合成的DNA序列嵌入其中以达到基因修饰的目的。

据了解,CRISPR-Cas9技术已经被应用于治疗血友病和白化病,并在许多其它疾病治疗中表现出巨大的潜力。

然而,该技术仍存在一些安全和效果问题,需要进一步研究和完善。

四、荧光显微技术荧光显微技术是基于细胞自发荧光表现的一种生物成像技术,它可以用于疾病的早期诊断和治疗。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

西安理工大学 电子工程系 高 勇

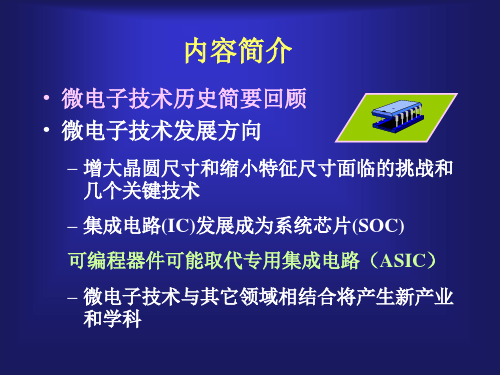

内容简介

• 微电子技术历史简要回顾 • 微电子技术发展方向

– 增大晶圆尺寸和缩小特征尺寸面临的挑战和 几个关键技术 – 集成电路(IC)发展成为系统芯片(SOC) 可编程器件可能取代专用集成电路(ASIC) – 微电子技术与其它领域相结合将产生新产业 和学科

二、微电子技术的主要发展方向(2)

集成电路追求目标3G(G=109)---3T(T=1012) 存储量(GB—TByte) 速度(GHz—THz)、 数据传输率(Gbps- Tbps, bits per second) 三个主要发展方向: 继续增大晶圆尺寸和缩小特征尺寸 集成电路(IC)将发展成为系统芯片(SOC) 可编程器件可能取代专用集成电路(ASIC) 微电子技术与其它领域相结合将产生新产业和新 学科

现场可编程门阵列 (FPGA)替代 专用集成电路(ASIC)

3. Parasitics Schottky S/D

- Reduced extrinsic resistance 4. Gate leakage High-K Dielectrics - Reduced power consumption 5. Gate depletion Metal Gate

EEI

集成电路发明50年

• 1952年5月,英国科学家G. W. A. Dummer 第一次提出了集成电路的设想

• 1958年以德克萨斯仪器公司的科学家基尔 比(Clair Kilby)为首的研究小组研制出了 世界上第一块集成电路,并于1959年公布。

EEI

获得2000年Nobel物理奖

1958年第一块集成电路: TI公司的Kilby,12个器件,Ge晶片

BULK

Si CMOS is expected to dominate for at least the next 10 - 15 years while scaling of traditional FETs is expected to slow in the next 5-10 years, so finding ways to add function and improve performance of future IC's with new materials and device structures is crucial.

• 1993年3月

• 32 Bit

• 310万晶体管

• 60到166 MHz • 0.8µm

P6 (Pentium Pro) in 1996 150 to 200 MHz clock rate 196 mm**2 5500K transistors (external cache) 0.35 micron 4 layers metal 3.3volt VDD >20W typical power Dissipation 387 pins

– 新型器件结构-高性能、低功耗晶体管 FinFET Nano Electronic Device – 新型材料体系 • SOI材料 •应变硅 • 高K介质 • 金属栅电极

Challenges to CMOS Device Scaling

5 4 3 2 1 1. Electrostatics Double Gate

SOI(Silicon-On-Insulator) 绝缘衬底上的硅技术

QUASI-PLANAR SOI FinFET

10 nm GATE LENGTH FinFET

栅介质的限制

传统的栅结构

经验关系: L T ox Xj1/3

G

硅化物 重掺杂多晶硅 SiO2

随着 t gate 的缩小,栅泄漏 电流呈指数性增长

EEI

〃1999年2月,英特尔推出Pentium III处理 器,整合950万个晶体管,0.25μm工艺制造 〃2002年1月推出的Pentium 4处理器,其整 合5500万个晶体管,采用0.13μm工艺生产

2002年8月13日,英特尔开始90nm制程的突

破,业内首次在生产中采用应变硅;2005年 顺利过渡到了65nm工艺。

The Moore’s Law

微电子技术是50年来发展最快的技术

Moore’s Law: Quantitative

EEI

第一台通用电子 计算机:ENIAC 1946年2月14日 Moore School, Univ. of Pennsylvania

18,000个电子管 70000个电阻、 10000个电容器以及 6000个继电器 组成。

增大晶圆尺寸

EEI

集成电路制造工艺

大生产的硅片直径已经从200mm转入300mm。

2015年左右有可能出现400mm--450mm直径的硅片。

Single die

Wafer

Going up to 12” (300mm)

EEI

缩小器件的特征尺寸

集成电路最主要的特征参数的设计规则从 1959年以来40年间缩小了140倍。而平均晶体管价 格降低了107倍。 特征尺寸:10微米-1.0微米-0.8µ(亚微米 ) →半微米 0.5 µ→深亚微米 0.35µ, 0.25µ, 0.18µ, 0.13µ → 纳米 90 nm →65 nm → 45nm

MEMORY Cache/SRAM or even DRAM

微米级工艺 •基于IP复用 •主流CAD:软硬件协 同设计

EISA Interface

SYSTEM-ON-A-CHIP

集成电路走向系统芯片

• SOC与IC的设计原理是不同的,它是微电子

设计领域的一场革命。 • SOC是从整个系统的角度出发,把处理机制 、模型算法、软件(特别是芯片上的操作系统 -嵌入式的操作系统)、芯片结构、各层次电 路直至器件的设计紧密结合起来,在单个芯片 上完成整个系统的功能。它的设计必须从系统 行为级开始自顶向下(Top-Down)。

第一个关键技术:Sub-100nm光刻

193nm(immersion) 光刻技术成为 Sub-100nm(90nm-32/22nm)工艺的功臣

新的一代曝光技术?

第二个关键技术:多层互连技术

·传统的铝互联(电导率低、易加工) ·铜互连首先在0.25/0.18µm技术中使用 ·在0.13µm以后,铜互连与低介电常数绝 缘材料共同使用(预测可缩到20nm) ·高速铜质接头和新型低-k介质材料,探 索碳纳米管等替代材料

器件及互连线延迟

4

3.5 3 延迟值(ns) 2.5 2 1.5 1 0.5 0 1997 1999 2001 2003 2006 2009 器件内部延迟 2厘米连线延迟 (bottom layer) 2厘米连线延迟 (top layer) 2厘米连线延迟约束

互连技术与器件特征尺寸的缩小

第三个关键技术:新器件与新材料

SOC主要三个关键支持技术

• 软、硬件的协同设计技术 面 向 不 同 系 统 的 软 件 和 硬 件 的 功 能 划 分理 论( Functional Partition Theory)。硬件和软件更加紧密 结合不仅是SOC的重要特点,也是21世纪IT业发展的 一大趋势。 • IP模块库的复用技术 IP模块有三种: 软核----主要是功能描述; 固核----主要为结构设计; 硬核----基于工艺的物理设计,与工艺相关,并经 过工艺验证的。其中以硬核使用价值最高。CMOS的 CPU、DRAM、SRAM、E2PROM和快闪存储器以及 A/D、D/A等都可以成为硬核。 • 模块界面间的综合分析技术 主要包括IP模块间的胶联逻辑技术和IP模块综合分 析及其实现技术等。

超薄栅 氧化层 大量的 晶体管

S

D

直接隧穿的泄漏电流 栅氧化层的势垒

tgate

栅氧化层厚度小于 3nm后

90nm→65nm工艺:栅极栅介质已经缩小到1.2nm了 (约等于5个原子厚度)栅极栅介质太薄,就会造成漏电电流穿透

在45nm工艺中采用High-K+金属栅极晶体管 使摩尔定律得到了延伸(可以到35nm、25nm工艺)

2007年英特尔推出45nm正式 量产工艺,45nm技术是全新的 技术,可以让摩尔定律至少再 服役10年。

多核微处理器

AMD四核“Barcelona”处理器 采用300mm晶圆, 45纳米技术制造

二、微电子技术的主要发展方向(1)

电子信息类产品的开发明显出现了两个特点: (1)开发产品的复杂程度激增; (2)开发产品的上市时限紧迫(TTM) 集成电路在电子销售额中的份额逐年提高 已进入后PC时代 • 计算机(PC)-----Computer • 通讯(Cell Telephone )---Communication • 消费类电子(汽车电子)---Consumption

世界上第一台计算机

大小:长24m,宽6m,高2.5m 速度:5000次/sec;重量:30吨; 功率:140KW;平均无故障运行时间:7min

EEI

4044

微处理器的发展

1971年第一个 微处理器4004 2000多个晶体管 10μm的PMOS工艺

1982年286微处理器 13.4万个晶体管

频率6MHz、8MHz、10MHz和12.5MHz

微电子技术面临的挑战和关键技术

(1)继续增大晶圆尺寸

(2)Sub-100nm光刻技术

(3)互连线技术

(4)新器件结构与新材料

INCREASE OF WAFER DIAMETER

COMPARISON OF PRODUCTION COSTS

(Cu/Low-K 65 nm)

Cost/wafer 200 mm Cost/cm2 Cost/wafer 300 mm From 200 mm to 300 mm Cost/cm2 Cost/wafer Cost/cm2 $ 8.92 $ 4,390 $ 6.21 + 57 % - 30 % $ 2,800