计算机组成原理 白中英 第三版(完整版)第八章输入输出系统

计算机组成原理 白中英 第三版(完整版)第八章输入输出系统

1.如果认为CPU等待设备的状态信号是处于非工作状态(即踏步等待),那么在下面几种主机与设备之间的数据传送中:()主机与设备是串行工作的;()主机与设备是并行工作的;()主程序与设备是并行运行的。

A.程序查询方式 B. 程序中断方式 C. DMA方式解: A C B2.中断向量地址是_____。

A.子程序入口地址 B. 中断服务程序入口地址C.中断服务程序入口地址指示器 C. 例行程序入口地址解: C3.利用微型机制作了对输入数据进行采样处理的系统。

在该系统中,每抽取一个输入数据就要中断CPU一次,中断处理程序接受采样的数据,将其放到主存的缓冲区内。

该中断处理需时x 秒,另一方面缓冲区内每存储n个数据,主程序就将其取出进行处理,这种处理需时y秒。

因此该系统可以跟踪到每秒_____次的中断请求。

A.N/(n×x+y) B. N/(x+y)×n C. Min(1/x, n/y)解: A4.采用DMA方式传送数据时,每传送一个数据就要占用一个____的时间。

A.指令周期 B. 机器周期C. 存储周期D. 总线周期解: C5.通道的功能是:(1)________,(2)______。

按通道的工作方式分,通道有______通道、_______通道和______通道三种类型。

解:(1)执行通道指令,组织外围设备和内存进行数据传输;(2)执行CPU的I/O指令,以及向CPU报告中断。

选择通道、字节多路通道、数组多路通道6.在教科书图8.7中,当CPU对设备B的中断请求进行服务时,如设备A提出请求,CPU能够响应中断吗?为什么?如果设备B一提出请求总能立即得到服务,问怎样调整才能满足此要求?解:(1)CPU不能响应中断(2)因为同级中断不能嵌套,而A、B设备属于同级中断(3)如果想要设备B一提出请求即能得到服务,则应该使设备B为最高优先级,这里可将设备 B单独接至3级IR,处于最高优先级。

8.设某机有5级中断:L0,L1,L2,L3,L4,其中断响应优先次序为:L0最高,L1次之,L4最低。

《计算机组成原理》教学大纲-信息与计算科学专业

《计算机组成原理》课程教学大纲一、教学大纲说明(一)、课程的地位、作用与任务《计算机组成原理》是信息类计算机应用专业学生必修的公共基础课之一,是一门涉及较多硬件知识的计算机系统软件课程。

在计算机软硬件课程的设置上,它起着承上启下的作用。

其特点是概念多、内容全面、涉及硬件内容,系统性强,其整体实现思想和技术理解有点难度。

(二)、课程的教学目的要求计算机组成原理对建立计算机整体概念,因此本课程的目的是使学生通过本课程的学习,理解计算机系统的基本概念和主要结构,掌握其工作原理,了解它的发展的新技术、新动向,从而为学生以后在各类计算机上从事开发和应用的需要。

掌握:基本概念包括:计算机系统组成及层次结构、运算方法和运算器、存储系统与指令系统、中央处理器、总线系统、外围设备、输入输出系统等。

基本知识:计算机系统的基本结构和工作原理以及有关的新技术。

理解重点:运算器结构、存储系统的管理方法、指令格式、中央处理器的结构和控制、外围设备通信控制方式。

难点:运算方法及运算器、中央处理器、输入输出控制方式。

(三)、课程的教学方法和手段1、本课程概念多、较抽象、涉及面广,因此教学形式以讲授方式为主。

2、为加强和落实动手能力的培养,应充分重视实践性教学环节,配合主教材、辅助教材、CAI、网络教材、试题库、实验教材综合使用,力求形成理论、抽象、设计三过程相统一的课程体系。

3、对关键性概念、整体实现思想方面的问题可辅以课堂讨论的形式。

4、如条件许可,应利用网络技术进行授课、答疑和讨论。

(四)、课程与其它课程的联系先修课为:计算机应用基础、操作系统原理、电子电路基础的知识(五)、教材与教学参考书教材:白中英,《计算机组成原理》(第三版、网络版) ,清华大学出版社,2008年3月二、课程的教学内容、重点和难点1.课程以文字教材为主(包括主教材和实验教材两部分),文字教材担负起形成整个课程体系系统性和完整性的任务,是学生学习的主要媒体形式。

计算机组成原理第8章 输入输出系统.ppt

2019年12月24日星期

二

25

8.1 主机与外设的连接

计算机组成原理

1. 程序查询方式

这种方式控制简单,但外设和主机不能同时 工作,各外设之间也不能同时工作,系统效率很 低,因此,仅适用于外设的数目不多,对I/O处理 的实时要求不那么高,CPU的操作任务比较单一, 并不很忙的情况。

2019年12月24日星期

二

8

8.1 主机与外设的连接

计算机组成原理

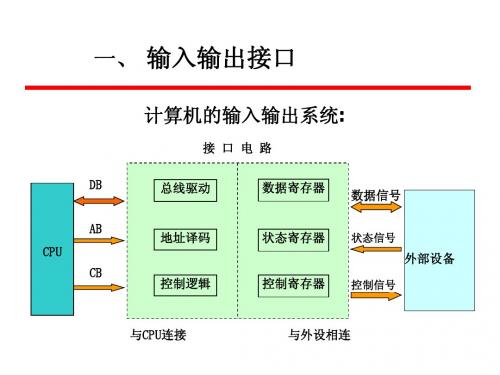

(5) 传递控制命令和状态信息

当CPU要启动某一外设时,通过接口中的控 制命令寄存器向外设发出启动命令;当外设准备 就绪时,则有状态信息送回接口中的状态寄存器, 为CPU 提供反馈信息,告诉CPU,I/O设备已经 具备和CPU交换数据的条件。当外设向CPU提出 中断请求和DMA请求时,CPU也有相应的响应信 号反馈给外设。

2019年12月24日星期

二

27

8.1 主机与外设的连接

计算机组成原理

2.

程序中断在信息交换方式中处于最重要的地 位,它不仅允许主机和外设同时并行工作,并且 允许一台主机管理多台外设。但是完成一次程序 中断需要许多辅助操作,可能使CPU应接不暇; 另外,对于一些高速外设,由于信息交换是成批 的,如果处理不及时,可能会造成信息丢失,因 此,它主要适用于中、低速外设。

任意两个连续的8位端口可作为1个16位端口 处理;四个连续的8位端口可作为1个32位端口处 理。因此,I/O地址空间最多能提供64K个8位端 口、32K个16位端口、16K个32位端口或总容量 不超过64KB的不同端口的组合。

2019年12月24日星期

二

20

8.1 主机与外设的连接

计算机组成原理

80x86的专用I/O指令IN和OUT有直接寻址和 间接寻址两种类型。直接寻址I/O端口的寻址范围 为00~FFH,至多为256个端口地址。这时程序 可以指定:

计算机组成原理(白中英)

D0

D1

D2

D3

A校验码 B校验码 C校验码 D校验码

系统结构

RAID4

I/O系统

❖ 专用奇偶校验独立存取盘阵列

❖ 数据以块(块大小可变)交叉的方式存于各盘, 奇偶校验信息存在一台专用盘上

数据块

校验码 产生器

A0

A1

A2

A3

B0

B1

B2

B3

C0

C1

C2

C3

D0

D1

D2

D3

A校验码 B校验码 C校验码 D校验码

❖ 只写一次光盘

只写一次光盘(Write Once Only):可以由用户写入 信息,不过只能写一次,写入后不能修改,可以多次读 出,相当于PROM。在盘片上留有空白区,可以把要修 改和重写的的数据追记在空白区内。

❖ 可檫写式光盘

可檫写式光盘(Rewriteable):利用磁光效应存取信 息,采纳特殊的磁性薄膜作记录介质,用激光束来记录、 再现和删除信息,又称为磁光盘,类似于磁盘,可以重 复读写。

RAID6

I/O系统

❖ 双维奇偶校验独立存取盘阵列

❖ 数据以块(块大小可变)交叉方式存于各盘, 检、纠错信息均匀分布在全部磁盘上

系统结构

A0 A1 A2

3校验码 D校验码

B0 B1

2校验码 C校验码

B2

C0

1校验码 B校验码

C1 C2

0校验码 A校验码

D1 D2 D3

校验码 产生器

7.7 光盘存储设备

– 正脉冲电流表示“1”,负脉冲电流表示“0”; – 不论记录“0”或“1”,在记录下一信息前,记录电流

恢复到零电流 – 简洁易行,记录密度低,改写磁层上的记录比较困难,

白中英计算机组成原理输入输出系统

特点

数据传送不需要经过CPU,直接由硬件控制;

外设与存储器之间的数据传送量大。

适用场合

包含有高速外设的系统中。

2020年5月14日星期四

9

通道方式

工作过程

CPU将IO控制的权利下放给通道,由通道统一管理所有的 输入输出操作。

硬件要求

需要IO通道(也称IO处理器,IOP);

通道是一个具有特殊功能的处理器。

EFFFFH

F0000H

I/O 设

FFFFFH 备

2020年5月14日星期四

12

1、设备编址——独立编址方式

独立编址方式

以20位主存地址、

将I/O系统与主存系统分别编址;

16位I/O地址为例

特点:

00000H

I/O端口地址不占用主存空间;

使用专用的I/O指令,指令字长短, 执行速度快;

与主存空间区分容易。

动画演示:8-1.swf

早期计算机中使用的一种方式,效率低。

程序中断方式

适用于随机出现的服务。

直接内存访问(DMA)方式

适用于内存和高速外围设备之间大批数据交换的场合。

通道方式

增加一个具有特殊功能的处理器——通道,将CPU的输

入输出权力下放。

外围处理机方式(PPU)

是通道方式的进一步发展。

2020年5月14日星期四

采用异步定时方式,或称为应答式数据交换;

询问信号 应答信号

CPU与外设之间通过两个相互的联络信号来决定开始数据传 送的时间。

③ 高速的外围设备 如:主存、辅存

采用同步定时方式;

由时钟脉冲控制

CPU以等间隔的速率执行输入/输出指令。

2020年5月14日星期四

白中英计算机组成原理

计算机的输入输出系统:

接 口 电 路 DB 总线驱动

数据寄存器

数据信号

状态信号

AB CPU CB

地址译码

状态寄存器

外部设备 控制逻辑 控制寄存器

控制信号

与CPU连接

与外设相连

与实验室联系后,实验安排如下:

第十三周做2个小实验:5月20日周一下午12点到3点,做实验二 算术逻辑运算 实验。

Interrupt Handler X

Interrupt Handler Y

多中断(顺序)

Multiple Interrupts – Nested

User Program

Interrupt Handler X

Interrupt Handler Y

多级中断(嵌套)

DMA传送控制方式

CPU放弃对总线的控制权, 整个传送过程由DMAC管 理,直接进行存储器与 外设之间、外设与外设 之间的数据传送。 DMA传送方式对高速大批量 数据传送特别有用。

中断优先级

内部异常中断(除单步)>INT n>NMI>INTR>单步中 断

除了单步中断以外,所有内部中断的优先权都比外部 中断的优先权高。如果在执行一个能引起内部中断 指令的同时,在NMI或INTR引脚端也产生了外部中断 请求,则CPU将首先处理内部中断。

中断响应

不可屏蔽(NMI)中断或内部中断,类型码是确 定的,中断响应过程不需要中断响应周期,可以立 即启动相应的中断服务程序. 可屏蔽(INTR)中断的响应是在执行完当前指 令后转入中断响应周期: 发中断响应信号,读中断类型码 保护现场(清除IF和TF标志,标志寄存器内容和 断点地址压入堆栈) 进入中断服务子程序

计算机组成原理(本全PPT)白中英

1、计算机五代变化 2、半导体存储器芯片的发展 3、微处理器的发展 4、计算机体系结构的变化 计算机体系结构是在冯•诺依曼结构的基础上,围 绕提高速度、提高字长、扩大存储容量、降低成本、 提高系统可靠性和方便使用等诸方面,通过新器件和 新软件提高计算机性能。 体系结构上,从指令系统、微程序设计、流水线 结构、多级存储器体系结构、输入/输出体系结构、并 行体系结构、分布式体系结构等方面的形成和发展。 体系结构发展趋势:网络化、智能化、模块化、多媒体 应用。

31

阶码和尾数各占用的位数确定了浮点数的格式 对二进制数而言: 1110.011=0.1110011×2100 0.001110011=0.1110011×2-10 - 0.001110011=-0.1110011×2-10 在将上面的数以浮点数格式存放时,只需将 红色部分按照浮点数格式要求的位数,化为相应 的补码或移码,按照浮点数格式存放。

16

(347) 8 =3×82+4×81+7×80=(103)10 (347.5) 8 =3×82+4×81+7×80+5×8-1 =(231.625)10 (34E.5) 16 =3×162+4×161+14×160+5×16-1 =(846.3125)10

17

2、不同数制间的转换 1>十进制八,十六进制二进制 法则 整数部分:除8(16)取余数 小数部分:乘8(16)取整 重复循环

本课程是计算机及相关专业的核心专业基础课, 对后续课程(操作系统、接口与通信等)的学习十分 重要。考研必考课程。

通过课程的学习主要掌握以下内容

本课程主要讲授单处理机系统的组成及工作原 理。分析和说明计算机由哪些功能部件组成(结构), 各功能部件在整机中的作用,以及它们如何完成各自 所分配的任务(工作原理)。

北京化工大学 裴颂伟-计算机组成原理-第8章 输入输出系统

裴颂伟-2019年6月5日星期三

计算机组成原理

6/230

8.1外围设备的定时方式和信息交换方式

2.慢速或中速的外围设备

由于这类设备的速度和CPU的速度并不在一个数量级,或者由于 设备(如键盘)本身是在不规则时间间隔下操作的,因此,CPU与 这类设备之间的数据交换通常采用异步定时方式。其定时过程如 下:

第四个问题,中断处理过程是由硬件和软件结合来完 成的。

裴颂伟-2019年6月5日星期三

计算机组成原理

23/230

8.3.2程序中断方式的基本接口

程序中断由外设接口的状态和CPU两方面来控制。在接口方面, 有决定是否向CPU发出中断请求的机构,主要是接口中的“准备 就绪”标志(RD)和“允许中断”标志(EI)两个触发器。在 CPU方面,有决定是否受理中断请求的机构,主要是“中断请求 ”标志(IR)和“中断屏蔽”标志(IM)两个触发器。

外设种类繁多,存在以下几种情况:

不同种类的外设数据传输速率差别很大 同一种设备在不同时刻传输速率也可能不同

高速的CPU与速度参差不齐的外设怎样在时间 上同步呢?

解决办法时在CPU和外设之间数据传送时加以定时 。

速度极慢或简单的外设

CPU只需要接受或者发送数据即可

慢速或者中速的设备

CPU发送数据的情况也与上述情况相似,外设先发出请求输出信 号,而后,CPU询问外设是否准备就绪。如果外设已准备就绪, CPU便发出准备就绪信号,并送出数据。外设接收数据以后,将 向CPU发出“数据已经取走”的通知。

通常,把这种在CPU和外设间用问答信号进行定时的方式叫做应 答式数据交换 。

设备选择器。设备选择器用来判别总线上送出的地址(或称呼叫 的设备)是否为本设备,它实际上是设备地址的译码比较电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.如果认为CPU等待设备的状态信号是处于非工作状态(即踏步等待),那么在下面几种主机与设备之间的数据传送中:()主机与设备是串行工作的;()主机与设备是并行工作的;()主程序与设备是并行运行的。

A.程序查询方式 B. 程序中断方式 C. DMA方式

A C B解:2.中断向量地址是_____。

A.子程序入口地址 B. 中断服务程序入口地址

C.中断服务程序入口地址指示器 C. 例行程序入口地址

C解:3.利用微型机制作了对输入数据进行采样处理的系统。

在该系统中,每抽取一个输入数据就要中断CPU一次,中断处理程序接受采样的数据,将其放到主存的缓冲区内。

该中断处理需时x秒,另一方面缓冲区内每存储n个数据,主程序就将其取出进行处理,这种处理需时y秒。

因此该系统可以跟踪到每秒_____次的中断请求。

A.N/(n×x+y) B. N/(x+y)×n C. Min(1/x, n/y)

A解:4.采用DMA方式传送数据时,每传送一个数据就要占用一个____的时间。

A.指令周期 B. 机器周期

C. 存储周期

D. 总线周期

C解:5.通道的功能是:(1)________,(2)______。

按通道的工作方式分,通道有______通道、_______通道和______通道三种类型。

解:(1)执行通道指令,组织外围设备和内存进行数据传输;

(2)执行CPU的I/O指令,以及向CPU报告中断。

选择通道、字节多路通道、数组多路通道

6.在教科书图8.7中,当CPU对设备B的中断请求进行服务时,如设备A提出请求,CPU能够响应中断吗?为什么?如果设备B一提出请求总能立即得到服务,问怎样调整才能满足此要求?

解:(1)CPU不能响应中断

(2)因为同级中断不能嵌套,而A、B设备属于同级中断

(3)如果想要设备B一提出请求即能得到服务,则应该使设备B为最高优先级,这里可将,处于最高优先级。

级IR单独接至 B3 设备

8.设某机有5级中断:L0,L1,L2,L3,L4,其中断响应优先次序为:L0最高,L1次

之,L4最低。

现在要求将中断处理次序改为L1→L3→L0→L4→L2,试问:

1 / 3

(1)下表中各级中断处理程序的各中断级屏蔽值如何设置(每级对应一位,该位

为ぜ表示允许中断,该位为?表示中断屏蔽)?

(2)若这5级中断同时都发出中断请求,按更改后的次序画出进入各级中断处理程序的过程示意图。

解:(1)

)(2

9.某机器CPU中有16个通用寄存器,运行某中断处理程序时仅用到其中2个寄存器,请问响应中断而进入该中断处理程序时,是否要将通用寄存器内容保存到主存中去?需保存几个寄存器?

解:响应中断而进入该中断处理程序时,需将通用寄存器内容保存到主存中去,但为减少中断处理时间,不必保存所有通用寄存器内容,这里只需将2个中断处理程序中用到的寄存器内容

保存起来。

12.下列陈述中正确的是_____。

A.在DMA周期内,CPU不能执行程序

B.中断发生时,CPU首先执行入栈指令将程序计数器内容保护起来

C. DMA传送方式中,DMA控制器每传送一个数据就窃取一个指令周期

D.输入输出操作的最终目的是要实现CPU与外设之间的数据传输

D解:2 / 3

13.Pentium系统有两类中断源:①由CPU外部的硬件信号引发的称为_____,它分为可屏蔽______和非屏蔽_____;②由指令引发的称为_______,其中一种是执行______,另一种是_______。

解:①外部中断 INTR NMI

出错或故障引发的②异常中断执行软件中断指令引发的

14.IEEE1394是______I/O标准接口,与SCSI_____I/O标准接口相比,它具有更高的______,更强的_______,提及_____,连接方便。

B A

C

D E解:15.SCSI是系统级_____,是处于主适配器和智能设备控制器之间的_____I/O接口。

SCSI-3标准允许SCSI总线上连接的设备由______个提高到_____个,可支持_____位数据传输。

A.并行 B. 接口 C. 16 D. 8 E. 32

B A D

C D解:18.若设备的优先级依次为CD-ROM、扫描仪、硬盘、磁带机、打印机,请用标准接口SCSI 进行配置,画出配置图。

解:PCI HBA → CD-ROM →扫描仪→硬盘→磁带机→打印机→终端器

3 / 3。