高频电子线路读书笔记

关于高频电子线路的收获

关于高频电子线路的收获关于高频电子线路的收获、感悟和建议(一)关于学习高频电子线路的收获高频电子线路又名通信电子线路,起初我不知道为什么。

当学习了第一章的内容我就大概明白了。

信号的传输通常需要信号工作在高频段,而信号本身通常低频的,这就需要设计把信号调制到高频段的电子线路了。

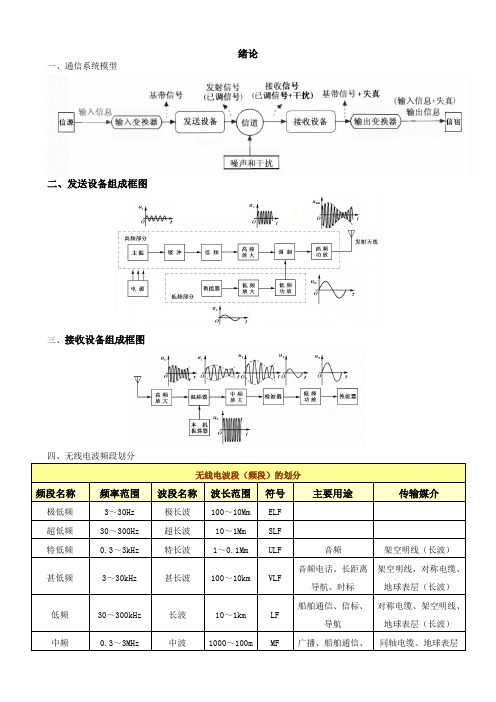

在第一章绪论里,主要讲了通信系统和通信系统的组成,这好像是一个大的框架。

我们以后要学的小信号选频放大器、高频功率放大器、正弦波振荡器等等都是通信系统要用到的。

第二章主要讲了小信号选频放大器,课本上以LC谐振回路为例对谐振回路的基本特性进行分析,然后介绍了小信号谐振放大器的组成和工作原理,为后面第三章高功率放大器的理论分析做好准备。

我了解到它是接收机中重要的组成部分,用以从众多的微弱信号选出自己需要的信号。

在这一章我知道小信号放大器为什么能从众多信号中检出自己需要的信号。

第三章是高频功率放大器,课本上以丙类谐振功率放大器为例讲了其工作原理、特性及电路组成,由于其效率不高,又延伸出了丁类和戊类谐振功率放大器。

在这一章我了解到高频功率放大器是各种无线电发射机的重要组成部分,而高频功率放大器一般采用LC谐振回路作为负载构成谐振功率放大器,这也就是为什么要把小信号选频放大器放在第二章的原因了。

第四章正弦波振荡器也就是我觉得最难的一章,课本上先讲了反馈振荡器的工作原理,然后以LC 正弦波振荡器为例介绍了电感三点式振荡器和电容三点式振荡器以及它们的改进型。

在这一章,我了解到正弦波振荡器是用来产生调制器和解调器需要的载波和想干载波的,为后面的调制器和解调器做好准备,是发射机和接收机都很重要的组成部分。

第五章是是振幅调制、解调与混频电路,课本上主要讲的振幅调制和解调,介绍振幅调制的不同类型包括普通调幅和双边带,单边带。

在这一章我们了解到振幅调制属于频谱线性搬移电路,将输入信号的频谱沿频率轴进行不失真的搬移,以便使信号与信道匹配起来。

第六章是角度调制与解调电路,讲的是用调制信号去控制载波的频率和相位,课本上首先介绍了角度调制的基本原理,然后讨论调频与解调电路的工作原理,并介绍了集成调频发射机与接收机,最后介绍了数字调制与解调的基本方法。

高频电子线路(知识点整理).doc

高频电子线路(知识点整理).doc

高频电子线路是指在射频或超高频范围内工作的电子线路,通常涉及到信号的传输、

处理和放大。

这种电子线路在通信、雷达、卫星通信、无线电等领域中被广泛应用,它有

着复杂的工作原理和设计技术。

下面就是对于高频电子线路的几个知识点整理和介绍。

1.谐振器:谐振器是高频电子线路中经常用到的一个组件,其作用是让电路产生特定

的共振频率,以便信号能够在电路中传输。

谐振器通常由其结构和材料决定,比如管型谐

振器、光纤谐振器、奇异谐振器等。

2.混频器:混频器是将两个输入频率进行混合,产生出一个输出频率的高频电子组件。

混频器主要用于转换信号的频率和增强信号的强度,比如在雷达和无线电通信中,混频器

通常用于将信号从中频转换到基带。

3.射频放大器:射频放大器是一种将低功率信号转化为高功率信号的电子器件,主要

用于放大和传输高频信号。

射频放大器的工作原理是通过对输入信号进行放大使得输出信

号的功率增大,它可以是单通道或多通道的,通常由功率放大器、隔离器等组成。

4.发射机:发射机是将信号转换成无线电波并进行发送的高频电子设备。

发射机通常

包括调制器、调谐器、放大器、射频发生器、天线等组件。

它主要将信号转化成无线电波

传输到接收机,以便实现通信或雷达探测等功能。

以上就是对于高频电子线路的几个知识点简要介绍,高频电子线路在通信、雷达、卫

星通信、无线电等领域中轮廓巨大,其涉及到很多的基础理论和设计技术,需要深入钻

研。

高频电子线路重点知识总结3

第一章绪论1.1 主要设计内容1. 无线通信系统的组成2. 无线通信系统的类型3. 无线通信系统的要求和指标4. 无线电信号的主要特性1.2 关键名词解释1. 基带信号:未调制的信号2. 调制信号:调制后的信号3. 载波:单一频率的正弦信号或脉冲信号4. 调制:用调制信号去控制高频载波的参数,是载波信号的某一个或者几个参数(振幅、频率或相位)按照调制信号的规律变化。

1.3 知识点1. 无线通信系统的组成(P1框图)详细了解一下无线通信系统的促成部分和每个部分的作用1)高频振荡器(信号源、载波信号、本地振荡信号)2)放大器(高频小信号放大器及高频放大器)3)混频和变频(高频信号变换和处理)4)调制和解调(高频信号变换和处理)2. 无线通信系统的分类1)按照工作频率和传输手段分为:中波信号、短波信号、超短波信号、微波信号、卫星通信2)按照通信方式分:全双工、半双工、单工方式3)按照调制方式分:调幅、调频、调相、混合调制4)按照传输发送信息的类型:模拟通信、数字通信3. 无线信号的特性:时间特性、频率特性、频谱特性、调制特性、传播特性4. 无线通信采用高频信号的原因:1) 频率越高,可利用的频带宽度越宽,可以容纳更多许多互不干扰的信道,实现频分复用或频分多址,方便某些宽频带的消息信号(如图像信号 2) 同时适合于天线辐射和无线传播。

5. 调制的作用:1) 通过调制将信号频谱搬至高频载波频率,使收发天线的尺寸大可缩小 2) 实现信道的复用,提高信道利用率。

第二章 高频电路基础与系统问题2.1 主要设计内容1. 高频电路中的元器件2. 高频率电路中的组件2.2 关键名词解释1. 参数效应:在高频信号中,随着信号的提高,元件(包括导线)产生的分布参数效应和由此产生的寄生参数(如导体间、导体或元件与地之间、元件之间的杂散电容,连接元件的导线的垫高和元件自身的寄生电感)。

2. 趋肤效应:在频率升高时,电流只集中在导体的表面,导致有效导电面积减小,交流电阻可能远大于直流电阻,从而是导体损耗增加,电路性能恶化。

(高频电子线路)第一章高频电路中的元器件及基本电路

广泛应用于信号产生、测量和 通信等领域。

放大电路

放大电路

放大电路的组成

利用三极管、场效应管等器件,将输入信 号进行放大,以获得足够大的输出信号的 电路。

一般由输入级、输出级、电压放大级和电 流放大级四部分组成。

放大电路的分类

放大电路的应用

根据工作频率可分为低频放大电路和高频 放大电路;根据电路结构可分为分立元件 放大电路和集成电路放大电路。

调制解调电路的应用

广泛应用于广播、电视、卫星通信、移动通信等领域。

PART 04

高频电路的性能指标与测 试方法

高频电路的性能指标

增益

带宽

衡量高频电路传输信号能力的指 标,通常指电路能够传输信号的 频率范围。

高频电路的放大能力,通常以分 贝(dB)为单位。

噪声系数

衡量高频电路信噪比性能的指标, 表示信号与噪声的相对大小。

PART 03

高频基本电路

振荡电路

振荡电路

利用电路自激振荡的原理,将直 流电能转换为具有一定频率和幅

度的交流电能输出的电路。

振荡电路的组成

一般由放大器、正反馈网络、 选频网络和稳幅环节四部分组 成。

振荡电路的分类

根据电路中元件是否含有电感器或 电容器,可分为RC振荡电路、LC振 荡电路和晶体振荡电路三大类。

https://

2023 WORK SUMMARY

高频电子线路第一章 :高频电路中的元器

件及基本电路

REPORTING

https://

目录

• 高频电子线路概述 • 高频电路中的元器件 • 高频基本电路 • 高频电路的性能指标与测试方法

PART 01

高频电子线路概述

电子行业第八章 高频电子线路

电子行业第八章高频电子线路1. 介绍高频电子线路是电子行业中非常重要的一个领域。

随着无线通信、雷达、卫星通信等技术的不断发展,高频电子线路成为实现高速数据传输和高频信号处理的关键技术。

本章将介绍高频电子线路的基本概念、原理和设计方法。

2. 高频电子线路基础知识2.1 高频信号特性在了解和设计高频电子线路之前,需要了解高频信号的特性。

高频信号具有频率高、波长短的特点,其传输和处理方式与低频信号有很大的不同。

高频信号常常需要考虑传输线路的阻抗匹配、反射损耗、时延和信号衰减等问题。

2.2 高频器件高频器件是高频电子线路的重要组成部分,包括高频放大器、射频开关、电磁波滤波器等。

这些器件的特性和参数对高频电子线路的性能有重要影响。

本节将介绍常用的高频器件的工作原理和设计要点。

3. 高频电子线路设计3.1 传输线路设计传输线路是高频电子线路设计中的重要组成部分,用于传输高频信号。

常用的传输线路包括微带线、同轴线等。

在设计传输线路时,需要考虑传输线路的长度、宽度、层间介质材料等因素。

3.2 高频功放设计高频功放是一种能够放大高频信号的电路,常用于无线通信系统和雷达系统中。

高频功放的设计需要考虑放大器的增益、输出功率、稳定性等因素。

3.3 射频开关设计射频开关是一种能够在高频信号下进行开关操作的器件,常用于无线通信和雷达系统中的信号切换。

射频开关的设计需要考虑开关速度、插入损耗、反射损耗等因素。

3.4 电磁波滤波器设计电磁波滤波器是一种用于滤除指定频率范围内的电磁波的器件,常用于高频通信系统中的波段选择和干扰抑制。

电磁波滤波器的设计需要考虑滤波器的带宽、通带损耗、回波损耗等参数。

4. 高频电子线路仿真与测试高频电子线路的仿真和测试是设计和验证高频电子线路性能的重要手段。

通过仿真和测试可以评估高频电子线路的性能,并进行必要的优化。

本节将介绍常用的高频电子线路仿真软件和测试设备。

4.1 电磁场仿真软件电磁场仿真软件能够模拟高频信号在电磁场中的传播和相互作用,帮助设计师优化高频电子线路结构。

《高频电子技术及应用》读书笔记模板

4.1振荡电路的基本功能和工作原理 4.2振荡器的组成及振荡条件 4.3 LC正弦振荡电路 4.4石英晶体振荡电路 4.5 RC正弦波振荡电路 4.6多谐振荡器(脉冲信号产生电路) 4.7实用电路——“钟声”效果发生器的电路及制作

5.1调制与解调电路的基本功能特点 5.2调制的种类 5.3调幅信号的检波电路 5.4调频信号的解调电路(鉴频器) 5.5数字信号的调制方法 5.6实用调制电路的应用与制作

6.1收音机的结构和工作原理 6.2收音机高频电路的实例分析 6.3收音机电路的检测方法

7.1电视信号的发射与接收 7.2电视信号接收电路——调谐器 7.3调谐器电路实例分析 7.4电视机中的高频电路实例

8.1有线电视系统的功能和特点 8.2有线电视系统的种类及应用范围 8.3数字有线电视接收机顶盒的结构和原理 8.4有线电视系统的检测和调试

11.1高频信号放大器的检测方法 11.2高频信号常用检测仪器

读书笔记

这是《高频电子技术及应用》的读书笔记模板,可以替换为自己的心得。

精彩摘录

这是《高频电子技术及应用》的读书笔记模板,可以替换为自己的精彩内容摘录。

作者介绍

这是《高频电子技术及应用》的读书笔记模板,暂无该书作者的介绍。

感谢观看

术在数字卫星 广播系统中的 应用

第11章频信号的测 量方法与实训

第10章频电子技术 在移动通信系统中

的应用

习题

1.1高频信号的特点及应用 1.2高频信号的传输特性 1.3高频设备和高频电路

2.1高频RLC电子元件的功能特点 2.2 RLC组合的频率均衡电路 2.3常用电子元器件的检测实训

3.1基本放大电路的结构和特点 3.2多级放大电路的结构和特点 3.3场效应晶体管放大电路 3.4晶体管放大器的检测和调试方法

高频电子线路课程设计心得体会

高频电子线路课程设计心得体会转眼间,又到了学期末了.回想起这几个月的教学,就会感觉这是我教学生涯中最轻松的日子.这要受益学校领导为我们引进的”合作探究,高效课堂模式.”用这种方式教学,学生轻松,老师也轻松.通过此次课程设计,使我更加扎实的掌握了有关高频电子线路方面的知识,在设计过程中虽然遇到了一些问题,但经过一次又一次的思考,一遍又一遍的检查终于找出了原因所在,也暴露出了前期我在这方面的知识欠缺和经验不足。

实践出真知,通过亲自动手制作,使我们掌握的知识不再是纸上谈兵。

过而能改,善莫大焉。

在课程设计过程中,我们不断发现错误,不断改正,不断领悟,不断获龋最终的检测调试环节,本身就是在践行“过而能改,善莫大焉”的知行观。

这次课程设计终于顺利完成了,在设计中遇到了很多问题,最后在老师的指导下,终于游逆而解。

在今后社会的发展和学习实践过程中,一定要不懈努力,不能遇到问题就想到要退缩,一定要不厌其烦的发现问题所在,然后一一进行解决,只有这样,才能成功的做成想做的事,才能在今后的道路上劈荆斩棘,而不是知难而退,那样永远不可能收获成功,收获喜悦,也永远不可能得到社会及他人对你的认可!建立融洽、民主的师生交流渠道,经常和学生一起反思学习过程和学习效果,互相鼓励和帮助,做到教学相长。

最后、转变机关作风,提高工作效率,要落到实处,不能成为口号,以务实的实干精神,努力完成各项工作任务,真正做到廉洁、勤政、务实、高效,有为。

课程设计诚然是一门专业课,给我很多专业知识以及专业技能上的提升,同时又是一门讲道课,一门辩思课,给了我许多道,给了我很多思,给了我莫大的空间。

同时,设计让我感触很深。

使我对抽象的理论有了具体的认识。

通过这次课程设计,我掌握了常用元件的识别和测试;熟悉了常用仪器、仪表;了解了电路的连线方法;以及如何提高电路的性能等等,掌握了焊接的方法和技术,通过查询资料,也了解了收音机的构造及原理。

当三条食物联系板书在黑板上,教学到达了研讨环节,即抽象概念。

高频电子线路笔记

绪论一、通信系统模型二、发送设备组成框图三、接收设备组成框图无线电波段(频段)的划分频段名称频率范围波段名称波长范围符号主要用途传输媒介极低频3~30Hz 极长波100~10Mm ELF超低频30~300Hz 超长波10~1Mm SLF特低频0.3~3kHz 特长波1~0.1Mm ULF 音频架空明线(长波)甚低频3~30kHz甚长波100~10km VLF音频电话、长距离导航、时标架空明线,对称电缆、地球表层(长波)低频30~300kHz长波10~1km LF船舶通信、信标、导航对称电缆、架空明线、地球表层(长波)第1章 高频小信号放大器§1.1 分散选频一、高频电压放大器的作用:放大+选频 二、选频电路分类三、分散选频电路 1、LC 串联选频电路主要参数:谐振频率 LCf π210= CL R CR RL Q 1100===ωω Q f f BW 02=∆=2、LC 并联选频电路主要参数:谐振频率 LCf π210=LC R C R LRQ ===00ωω Q f f BW 02=∆=3、耦合选频(了解)§1.2 集中选频1.石英晶体滤波器石英晶体滤波原理:逆压电效应压电效应:当晶片两面加机械力时,晶片两面将产生电荷,电荷的多少与机械力所引起的变形成正比,电荷的正负将取决于所加机械力是张力还是压力。

逆压电效应:当在晶片两面加不同极性的电压时,晶片会产生机械形变,其形变大小正比于所加的电压强度;形变是压缩还是伸张,则决定于所加电压的极性。

Lq 为石英晶片的动态等效电感 Cq 为石英晶片的动态等效电容 Rq 为石英晶片的动态等效电阻 C 0为石英谐振器的静态电容品质因数: qq qC L R Q 1= fs :串联谐振频率,即石英晶片本身的自然频率: qq 21C L f s π=fp :和石英谐振器的并联谐振频率:q S q0q 0qp 121C C f C C C C L f +==+π 2. 陶瓷滤波器原理与参数同石英晶体滤波器 3. 声表面波滤波器原理:电声效应 4.螺旋滤波器§1.3 高频小信号放大器(一)单级单调谐放大器(1)谐振频率 LCf π210=(2)通频带 Q f B 07.0= G C L G L C R C R L R Q 00001ωωωω=====(3)选择性 K 0.1 = BW 0.1 / BW 0.7 = 9.96 ≈ 10(4)电压增益 GYp p Gu u Y p p u u p u u A fe 12S S fe 12S L 2S L 0V '====(5)增益带宽乘积 CY p p B A GB π2fe 127.00V ==(二)单级双调谐放大器(1)电压增益 ()()22224fe12V 112ηηξξη++-+GY p p A = GY p p A 2fe120V =(2)通频带 Qf BW 07.02= (3)选择性 K 0.1 =3.16(三)多级调谐放大器 1.多级单调谐(1)总电压增益 ()N G Y p p A ⎥⎦⎤⎢⎣⎡=ξj 1fe 12VN + NG Y p p A ⎥⎦⎤⎢⎣⎡=fe 12V0N(2)总谐振曲线方程22022V0N VN 21111N Nf fQ A A⎥⎥⎦⎤⎢⎢⎣⎡⎪⎪⎭⎫⎝⎛∆+=⎥⎥⎦⎤⎢⎢⎣⎡+=ξα=(3)总通频带 12107.0-=N Qf BW(4)总的选择性121100111.0--=NNK 2.多级双调谐(1)谐振曲线方程 N⎪⎪⎭⎫⎝⎛+=442ξα (2)总通频带 4107.0122-=NQf BW(3)总的选择性 4111.0121100--=N NK3.多级参差调谐(1)双参差调谐放大器:两个放大器分别调谐在f1、f2上(2)三参差调谐放大器。

高频电子线路课程学习体会

高频电子线路课程学习体会This manuscript was revised by the office on December 22, 2012高频电子线路课程学习体会通过学习《高频电子线路》,对无线通信系统、线性与非线性电路、频率变换网络、通信模块的具体电路性能参数有了更加深入的认识,总的来说,通过学习,收获主要体现在:一、对通信系统中的高频电子电路的组成,工作原理及工程设计思想有了基本上的认识。

二、对电路的技术指标有了更加深入的了解,并能够分析简单的高频电路。

下面分线性和非线性进行说明,具体的叙述不是按照学习的顺序。

通信系统把原始信号转换成电信号,直到从高频功放以电磁波的形式发射到空间,低频、高频信号都是在电路中处理。

但从低频到高频,基本元件如电阻、电容、电感等集总参数发生变化,二极管、三极管的模型也不同。

另一个是非线性电路的大量应用,非线性的一个重要特点是会产生新的频率成分,使得调制、倍频、分频成了可能。

1.线性电路最主要的应用是谐振回路。

高频小信号放大电路的y参数和参数等效回路也是线性模型,但其最主要的部分仍是谐振(选频)回路。

收获之一:对频率选择性的理解。

选频网络的选频特性是因为它的阻抗是频率的函数,通过电感、电容、电阻的串并联总的阻抗函数就表现为某个频段的阻抗上升或下降。

当输入电流(或电压)信号含有多个频率成分时,在通频带内的频率成分就会放大作为输出信号,不在通频带内的成分就会被抑制,因此实现了选频。

但选频的过程并没有增加或减少频率成分,只是对原来成分的压缩和扩展,因此仍然是线性电路。

选频电路最重要的参数就是品质因数Q,Q值大则说明选频特性好。

一般串联并联谐振回路Q值较小,通频带较宽,选择性不好,但通过级联可提高选择性,另外石英晶体有很高的Q值。

串联、并联谐振回路的相频特性都是经过中心频率点的反正切函数,在微小频移下可视为线性关系。

这种在一定范围内视为线性关系的方法在后面非线性分析当中经常用到。

高频电子线路读书笔记

高频电子线路读书笔记【篇一:晶体管放大电路设计读书笔记】一、放大电路的工作1、功率开关mos管结构:在内部将大量fet并联连接起来的,每一个单元中流过的电流很小,防止局部的电流集中,同时改善高频特性。

2、耦合电容:使输入信号与电路或电路与者电路与电路的耦合。

3、电源的去耦电容:降低电源对gnd的交流阻抗的电容(旁路电容),当没有这个电容时,电路的交流特性变的很奇特,严重时电路产生震荡。

4、在低频电路中,去耦电容的安装位置不是问题;但在高频电路中,安装位置比什么都重要,引线也要短。

5、 npn型的ttl三极管可以理解为:由集电极进行输出的电流源。

6、在共射电路中,发射极接个电阻re,可以认为在改电路中加了负反馈,由于负反馈,re有抑制hfe(电流放大系数)的分散性和vbe的温度变化而产生的发射极电流变化的作用。

7、 ttl三极管共射电路中:发电极电位设定在vcc与ve的中点。

二、增强输出电路1、ttl三极管工集电路中:集电极电位设定在vcc与gnd的中点。

2、射机跟随器大多数用在电路的输出极,因为需要经常处理大电流,所以必须注意晶体管和电阻的发热问题。

3、将射极跟随器组合在共发射极放大电路上来降低输出阻抗的放大电路。

4、由于集电极电容接地,故不会发生密勒效应,因此频率特性变好。

5、在晶体管电路中,通常越提高放大率,噪音就越增加,这是由于进行放大的同时,电路内部产生的噪音也被放大的缘故。

6、当op放大器需要驱动大的负载时,需要将op放大器与射极跟随器相互结合。

三、功率放大器的制作与设计1、功率放大器的一般规律:首先电压放大得到必要的输出;之后放置能驱动低阻抗负载的电流缓冲放大器。

2、解决发热问题是制作功率放大器的重点。

3、用一个晶体管进行工作的集电极电流的适当值为最大电流的1/3左右。

四、拓宽频带特性1、由于共基极放大电路的输出阻抗比较高,所以在输出信号长距离传输时,输出阻抗与布线杂散电容形成低通滤波器,就不能够显示出共基极放大电路本来的频率特性有点,为了改进这一点,在共基极放大电路的后级接上射极跟随器。

(高频电子线路)第二章高频电路基础

低通滤波器的应用包括信号处理、 电源滤波等,可以有效地抑制高

频噪声,提高信号的信的电路。其特点是通带范围较 窄,阻带范围较宽。

高通滤波器的电路结构也有多种形式,如RC、LC等。不同结构的高通滤波器具有不 同的性能指标和适用场景。

对信号进行放大,提高信号的 幅度和功率。

振荡器

产生高频振荡,为电路提供所 需频率的信号。

信号源

产生高频信号,提供电路所需 输入信号。

滤波器

对信号进行滤波,提取所需频 率成分,抑制无用频率成分。

调制解调器

对信号进行调制和解调,实现 信号的传输和处理。

02

高频电子器件

电感器

01

02

03

04

电感器定义

差。

调相振荡器的应用

调相振荡器广泛应用于信号处理、 电子对抗和通信等领域。

锁相环路

锁相环路的定义

锁相环路是一种自动控制系统,它通过比较输入信号和输出信号的 相位差,自动调节输出信号的频率和相位。

锁相环路的工作原理

当输入信号和输出信号的相位差在一定范围内时,锁相环路会自动 调节其内部参数,使输出信号的频率和相位与输入信号保持一致。

标和适用场景。

带通滤波器的应用包括信号选频、 消除干扰等,可以有效地提取特 定频段的信号,提高信号的准确

度。

带阻滤波器

带阻滤波器是一种阻止某一频段内的信 号通过而允许其他频段信号的电路。其 特点是阻带范围较窄,通带范围较宽。

带阻滤波器的应用包括消除特定频段干 扰、抑制噪声等,可以有效地抑制特定 频段的噪声,提高信号的清晰度。

高频电路的应用领域

通信领域

高频电路广泛应用于通信 领域,如无线通信、卫星

高频电子线路chap6.2

04 高频电子线路的设计与实 现

高频电子线路的设计原则

功能性原则

确保线路能够完成预定的功能,满足设计要求。

可靠性原则

保证线路在各种工作环境下都能稳定、可靠地运行。

效率性原则

优化线路性能,降低能耗,提高工作效率。

可维护性原则

便于线路的调试、维修和升级。

高频电子线路的实现方法

模拟法

通过模拟电路元件的电气特性来实现高频电 子线路。

混频器和调制解调器

混频器和调制解调器是高频电子线路中的基本电 路之一,用于信号频率变换和调制解调。在高频 电路中,混频器和调制解调器的设计需要考虑频 率转换效率和噪声性能等因素。

高频电子线路的电路分析方法

线性时不变分析方法

非线性时不变分析方法

时域分析方法

频域分析方法

线性时不变分析方法是高频电 子线路中最常用的分析方法之 一,通过建立线性时不变电路 模型,运用线性代数和微积分 等数学工具进行分析。

非线性时不变分析方法适用于 分析具有非线性特性的高频电 子线路,通过建立非线性时不 变电路模型,运用非线性代数 和微积分等数学工具进行分析 。

时域分析方法是通过分析电路 在不同时间点的状态和行为来 分析高频电子线路的方法。通 过建立时域电路模型,运用微 分方程等数学工具进行分析。

频域分析方法是通过对电路的 频率响应进行分析来理解其性 能的方法。通过将电路模型变 换到频域,运用傅里叶变换等 数学工具进行分析。

未来展望

未来,高频电子线路将继续朝着更高频率、更高速度、更低功耗和更小体积的方向发展, 为通信、雷达和电子对抗等领域的发展提供更加有力的技术支持。

02 高频电子线路的基本原理

信号的传输原理

信号的传输方式

高频电路心得与体会

高频电路心得与体会通过高频电路原理及分析的这门课学到了很多。

比如,高频谐振放大器的原理和特性,还有正弦波振荡器与频率的调制及解调等内容。

在学习过程中,我不断领悟这门课程的思想。

这门课已经结束了,在过程中遇到了很多问题,最后在还是一一解决了。

这本书主要讨论了用于各种电子系统和电子设备中的高频电子电路。

通信的目的与任务是传递消息。

通信中传递的消息的类型很多,传输消息的方法也很多。

现代通信大多数以电(或光)信号的形式出现,因此,通常被称作电信。

传输电信号的煤质或介质可以是有线的,也可以是无线的,而无线的形式最能体现高频电路的应用。

与线性器件不同,对非线性器件的描述通常用多个参数,如直流跨导,时变跨导和平均跨导,而且大都与控制变量有关。

调制、解调与混频电路均为频率变换电路, 属于非线性电路范畴。

我应该搞清电路非线性的基本概念, 针对不同的电路, 采用不同的分析方法。

例如, 在讨论混频电路时, 首先应该明确的是电路的作用就是要将接收的高频信号变为中频信号, 即在电路的输出端具有输入端所不具有的新的频率分量, 电路的实质为非线性电路。

具体电路实现可选用非线性元件二极管或三极管, 分析方法使用非性时变分析方法, 分析过程中数学推导比较麻烦, 我们要将注意力更多放到电路输入输出频率的变换上。

调制、解调与混频电路均为频率变换电路, 属于非线性电路范畴。

我们应该搞清电路非线性的基本概念, 针对不同的电路, 采用不同的分析方法。

例如, 在讨论混频电路时, 我们首先应该明确的是电路的作用就是要将接收的高频信号变为中频信号,即在电路的输出端具有输入端所不具有的新的频率分量, 电路的实质为非线性电路。

具体电路实现可选用非线性元件二极管或三极管, 分析方法使用非线性时变分析方法,电路设计的基本思路是从系统指标提出至方案确定, 再由系统下至模块的功能和指标提出到具体电路结构设计。

高频电路的每一章节基本上对应了发射机或接收机的一个模块。

高频电子线路培训研修心得

《高频电子线路》网络培训研修心得渭南师范学院物理与电气工程学院朱高中在七月份的网络精品课程《高频电子线路》的培训中,我认真的聆听了曾教授、刘教授和陈教授精彩的网络课程讲解,从三位教授丰富的教学讲解中,我深刻的认识到自己在教学方面和教法方面知识的不足,三位教授渊博的知识、丰富的教学经验和教学方法。

是值得我们高校教师学习的榜样,故此,通过此次《高频电子线路》网络课程培训,我有以下几点收益:一、要做到各门知识的融会贯通。

对于高频电子线路这门课程来说,如果单纯的学习这门课程而不和其他课程联系起来,我们会感觉这门课程非常的难学,但高频电子线路中的知识涉及到电路、模拟电路和通信原理方面的知识,当我们把几门课融会贯通起来就会发现好多知识点是相同,这样我们就会感觉高频电子线路也不那么难学。

在网络课程培训中,我认真的聆听了三位教授的每一节课,发现三位教授在讲到课程中好多知识点的时候都会把此节的知识和前面的所学的知识联系起来,通过课程的联系、实例的讲解,把高频电子线路中许多复杂的知识简单化,把许多抽象的知识具体化。

在连续听三位教授讲解的过程中,我发现很多的知识点并不像想象中的那么难学、那么难以接受,在听完这门课之后,我现在对高频电子线路这门课程已经有相当的了解,并掌握了一定的基础知识,对我以后的教学工作会有很大的帮助。

二、要做到理论联系实际。

对于高频电子线路这门课程,只能用一句话来形容“纸上得来终觉浅”,对大多数的人来说,高频电子线路几乎就是一门哲学,两个字——抽象,要想学好高频电子线路这门课,必须要做到理论联系实际。

通过此次网络课程的学习,我发现我在平时的教学过程中,只注意到理论教学的讲解,很少将课本上的知识点和生活实践结合起来。

听了三位教授的讲解,发现三位教授很注重理论和实践的结合,比如在讲到调制这一节中,要讲清楚为什么要进行调制,就可以拿手机通信解释要调制的原因。

三、要做到教师和学生互动。

互动就是要让学生参与到教学中来,让学生主动的去学习,而不是被动的接受知识,这样才能提高学生学习的积极性和主动性。

高频电子线路课程设计心得体会

高频电子线路课程设计心得体会通过此次课程设计,使我更加扎实的掌握了有关高频电子线路方面的知识,在设计过程中虽然遇到了一些问题,但经过一次又一次的思考,一遍又一遍的检查终于找出了原因所在,也暴露出了前期我在这方面的知识欠缺和经验不足。

实践出真知,通过亲自动手制作,使我们掌握的知识不再是纸上谈兵。

过而能改,善莫大焉。

在课程设计过程中,我们不断发现错误,不断改正,不断领悟,不断获龋最终的检测调试环节,本身就是在践行“过而能改,善莫大焉”的知行观。

这次课程设计终于顺利完成了,在设计中遇到了很多问题,最后在老师的指导下,终于游逆而解。

在今后社会的发展和学习实践过程中,一定要不懈努力,不能遇到问题就想到要退缩,一定要不厌其烦的发现问题所在,然后一一进行解决,只有这样,才能成功的做成想做的事,才能在今后的道路上劈荆斩棘,而不是知难而退,那样永远不可能收获成功,收获喜悦,也永远不可能得到社会及他人对你的认可!课程设计诚然是一门专业课,给我很多专业知识以及专业技能上的提升,同时又是一门讲道课,一门辩思课,给了我许多道,给了我很多思,给了我莫大的空间。

同时,设计让我感触很深。

使我对抽象的理论有了具体的认识。

通过这次课程设计,我掌握了常用元件的识别和测试;熟悉了常用仪器、仪表;了解了电路的连线方法;以及如何提高电路的性能等等,掌握了焊接的方法和技术,通过查询资料,也了解了收音机的构造及原理。

我认为,在这学期的实验中,不仅培养了独立思考、动手操作的能力,在各种其它能力上也都有了提高。

更重要的是,在实验课上,我们学会了很多学习的方法。

而这是日后最实用的,真的是受益匪浅。

要面对社会的挑战,只有不断的学习、实践,再学习、再实践。

这对于我们的将来也有很大的帮助。

以后,不管有多苦,我想我们都能变苦为乐,找寻有趣的事情,发现其中珍贵的事情。

就像中国提倡的艰苦奋斗一样,我们都可以在实验结束之后变的更加成熟,会面对需要面对的事情。

回顾起此课程设计,至今我仍感慨颇多,从理论到实践,在这段日子里,可以说得是苦多于甜,但是可以学到很多很多的东西,同时不仅可以巩固了以前所学过的知识,而且学到了很多在书本上所没有学到过的知识。

高频电路笔记

调幅AM调角FM/PM:瞬时频率 、瞬时相位

无线电发射机:

信号

无线电接收机:

信号

直接放大式:无混频+本振(变频),不同接收频率灵敏度、选择性不同。

超外差式:中频放大器选择性、增益与接收频率无关。

零中频式(直接变换式):正交变换。

1.3

双绞线:低频、低速

陶瓷片两面用银作为电极,经过直流高压极化,具有和石英晶体相类似的压电效应,等效电路与晶体相同。

优点:容易焙烧,可制成各种形状;适于小型化;且耐热耐湿性好。

等效品质因数为几百,比石英晶体低但比LC滤波高

四端陶瓷滤波器:由多个谐振子组成四端滤波器。谐振子数目愈多,滤波器的带外衰减性能愈强。

电路组成原则:中心频率是串臂的串联谐振频率和并臂的并联谐振频率,

设 ,

回路中储存的能量不变,只在电感与电容间转换,外加电源提供回路电阻所消耗的能量。

回路一个周期的损耗:

,

电源内阻与负载电阻的影响:

有载Q值

考虑信号源内阻及负载电阻后,串联谐振回路的选择性变坏,通频带加宽。

1.4

高频电子线路中,信号源多为工作于放大区的有源器件(晶体管、场效应管),可看做恒流源,一般采用并联谐振回路。

反射电抗的性质与原回路总电抗的性质相反

反射电阻和反射电抗的值与耦合阻抗的平方值成正比。

初、次级回路同时调谐到与激励频率谐振(即 )时,反射阻抗为纯阻。

1.7.2

设回路参数相同, , , ,

则 ,

广义失谐量

耦合因数:耦合振荡回路的耦合系数与临界耦合系数之比。

各种耦合电路都可定义耦合系数,但只能对双谐振回路定义耦合因数。

高频电子线路网络培训心得体会

高频电子线路网络培训心得体会在六月的网络精品课?高频电子线路?的培训中,我认真的聆听了曾教授、刘教授和陈教授他们的精彩讲解,对知识的全面解析和教学教法方面做了很多很深化的分析,我深化的体会到这三位教授渊博的知识和耐心的教学方式,丰富的表情和恰如其分的肢体语言,确实是我们一线教师的楷模。

通过这次精品课的培训,我有几点收益:一,在听课过程中,我认真的听了每一次课,对?高频电子线路?这一门学科来说,我没有专业的系统的学习过,很多东西都是在相关课程中有所理解,故听课开始有点难度,但是后来连续的听课过程中,我发现了很多东西是可以快速的学习和承受的,我如今对这门课已经有相当的理解,并且掌握了一定的根底知识,对后续教学必定有很大的帮助。

二,我院在示范性建立中,很多的课程都要求建立精品课,在各方面来说都有一定的压力,尤其是制作课件这一块,我深化体会到这三为教授的图文并茂的教学手段和精湛的制作手法,我在后续的工作和学习中可以学习他们的制作精华,进步课件的制作程度。

三,我院有的教师一旦用课件,根本上不用黑板参与教学,这样的方式学生听课效率不是很高,学习效果不是很好,我体会到三位教授都强调了课件是一种教学手段,但是还是建议少用,并且立足于黑板,有强烈的教学效果,很利于教学互动,我受益很深。

四,课程建立是很重要的,我们在这方面也存在的很多问题,尤其是教学目的不够明确,学生学习的目的和意义也不够明晰,组织教学的方式也相当单调,学生的动手才能尽管有一定的进步,但是还远达不到当代教学的目的,我在听课的过程中我深化体会到三为教授的这方面都有很高的造诣,许多方面是值得我们学习的。

五,互动教学是一种比较好的方式,通过三为教授的分析讲解课程后,留有一定的时间给大家进展交流,大家在很多问题上的难题得到理解决,并且通过这样的方式,对我们以后的教学产生很大的影响,我们许多教师在教学互动方面存在一定的缺陷,有的教师上完课就走人,学生许多问题得不到及时解决。

高频电子线路课程设计心得体会

高频电子线路课程设计心得体会

在高频电子线路课程设计过程中,我收获了很多知识和经验。

首先,我学会了如何设计高频电子线路的基本原理和步骤。

高频电子线路设计需要考虑信号的传输和干扰抑制,因此需要合理选择器件和电路结构,以及进行信号仿真和优化设计。

其次,我学会了如何使用电路设计软件进行仿真和优化。

在设计过程中,我使用了ADS、CST和HFSS等软件进行电路仿真和优化。

通过仿真,我能够分析信号的传输特性和电路的性能,找出潜在问题并作出相应的改进。

此外,我还学会了如何进行实际的电路布局和调试。

高频电子线路的布局需要考虑信号的传输路径、阻抗匹配和严格控制电磁干扰等因素。

在调试过程中,我学会了使用示波器和频谱分析仪等测试设备进行信号测量和分析,找出问题点并进行修复。

通过课程设计,我深入了解了高频电子线路的基本原理和设计方法,掌握了电路仿真和优化的技巧,提高了电路布局和调试的能力。

这些经验对我今后的学习和工作都具有重要的参考价值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

高频电子线路读书笔记【篇一:晶体管放大电路设计读书笔记】一、放大电路的工作1、功率开关mos管结构:在内部将大量fet并联连接起来的,每一个单元中流过的电流很小,防止局部的电流集中,同时改善高频特性。

2、耦合电容:使输入信号与电路或电路与者电路与电路的耦合。

3、电源的去耦电容:降低电源对gnd的交流阻抗的电容(旁路电容),当没有这个电容时,电路的交流特性变的很奇特,严重时电路产生震荡。

4、在低频电路中,去耦电容的安装位置不是问题;但在高频电路中,安装位置比什么都重要,引线也要短。

5、 npn型的ttl三极管可以理解为:由集电极进行输出的电流源。

6、在共射电路中,发射极接个电阻re,可以认为在改电路中加了负反馈,由于负反馈,re有抑制hfe(电流放大系数)的分散性和vbe的温度变化而产生的发射极电流变化的作用。

7、 ttl三极管共射电路中:发电极电位设定在vcc与ve的中点。

二、增强输出电路1、ttl三极管工集电路中:集电极电位设定在vcc与gnd的中点。

2、射机跟随器大多数用在电路的输出极,因为需要经常处理大电流,所以必须注意晶体管和电阻的发热问题。

3、将射极跟随器组合在共发射极放大电路上来降低输出阻抗的放大电路。

4、由于集电极电容接地,故不会发生密勒效应,因此频率特性变好。

5、在晶体管电路中,通常越提高放大率,噪音就越增加,这是由于进行放大的同时,电路内部产生的噪音也被放大的缘故。

6、当op放大器需要驱动大的负载时,需要将op放大器与射极跟随器相互结合。

三、功率放大器的制作与设计1、功率放大器的一般规律:首先电压放大得到必要的输出;之后放置能驱动低阻抗负载的电流缓冲放大器。

2、解决发热问题是制作功率放大器的重点。

3、用一个晶体管进行工作的集电极电流的适当值为最大电流的1/3左右。

四、拓宽频带特性1、由于共基极放大电路的输出阻抗比较高,所以在输出信号长距离传输时,输出阻抗与布线杂散电容形成低通滤波器,就不能够显示出共基极放大电路本来的频率特性有点,为了改进这一点,在共基极放大电路的后级接上射极跟随器。

2、在共基极放大电路中,发射极等效于交流接地。

3、在共基极放大电路中,可以将信号直接输入到发射极上。

但由于由于电路的输入阻抗只有数欧那样低的值,所以它通常难以使用,为此,除了在高频范围,一般不使用该电路。

五、视频选择器的设计和制作1、在高频电路中,用一定的输出阻抗进行发送,用一定的输入阻抗进行接收,以此来作为信号的传送。

2、通常晶体管流过大一些的发射极电流时,则频率特性变好。

【篇二:电子电路读书笔记】电子电路读书笔记1、 hc为coms电平,hct为ttl电平2、 ls输入开路为高电平,hc输入不允许开路, hc一般都要求有上下拉电阻来确定输入端无效时的电平。

ls 却没有这个要求3、 ls输出下拉强上拉弱,hc上拉下拉相同4、工作电压:ls只能用5v,而hc一般为2v到6v5、 cmos可以驱动ttl,但反过来是不行的。

ttl电路驱动coms电路时需要加上拉电阻,将2.4v~3.6v之间的电压上拉起来,让cmos 检测到高电平输入6、驱动能力不同,ls一般高电平的驱动能力为5ma,低电平为20ma;而cmos的高低电平均为5ma7、 rs232电平为+12v为逻辑负,-12为逻辑正8、 74系列为商用,54为军用9、 ttl高电平2.4v,ttl低电平0.4v, 噪声容限0.4v10、 oc门,即集电极开路门电路(为什么会有oc门?因为要实现“线与”逻辑),od门,即漏极开路门电路,必须外界上拉电阻和电源才能将开关电平作为高低电平用。

否则它一般只作为开关大电压和大电流负载,所以又叫做驱动门电路。

并且只能吸收电流,必须外界上拉电阻和电源才才能对外输出电流11、 coms的输入电流超过1ma,就有可能烧坏coms12、当接长信号传输线时,在coms电路端接匹配电阻13、在门电路输入端串联10k电阻后再输入低电平,输入端出呈现的是高电平而不是低电平14、如果电路中出现3.3v的coms电路去驱动5v cmos电路的情况,如3.3v单片机去驱动74hc,这种情况有以下几种方法解决,最简单的就是直接将74hc换成74hct的芯片,因为3.3v cmos 可以直接驱动5v的ttl电路;或者加电压转换芯片;还有就是把单片机的i/o口设为开漏,然后加上拉电阻到5v,这种情况下得根据实际情况调整电阻的大小,以保证信号的上升沿时间。

15、逻辑门输出为高电平时的负载电流(为拉电流),逻辑门输出为低电平时的负载电流(为灌电流)16、由于漏级开路,所以后级电路必须接一上拉电阻,上拉电阻的电源电压就可以决定输出电平。

这样漏极开路形式就可以连接不同电平的器件,用于电平转换。

需要注意的一点:在上升沿的时候通过外部上拉无源电阻对负载进行充电,所以上升沿的时间可能不够迅速,尽量使用下降沿17、几种电平转换方法:(1) 晶体管+上拉电阻法就是一个双极型三极管或mosfet,c/d极接一个上拉电阻到正电源,输入电平很灵活,输出电平大致就是正电源电平。

(2) oc/od 器件+上拉电阻法跟 1) 类似。

适用于器件输出刚好为 oc/od 的场合。

(3) 74xhct系列芯片升压(3.3v→5v)凡是输入与 5v ttl 电平兼容的 5v cmos 器件都可以用作3.3v→5v电平转换。

——这是由于 3.3v cmos 的电平刚好和5v ttl电平兼容(巧合),而 cmos 的输出电平总是接近电源电平的。

廉价的选择如 74xhct(hct/ahct/vhct/ahct1g/vhct1g/...)系列 (那个字母 t 就表示 ttl 兼容)。

(4) 超限输入降压法(5v→3.3v, 3.3v→1.8v, ...)凡是允许输入电平超过电源的逻辑器件,都可以用作降低电平。

这里的超限是指超过电源,许多较古老的器件都不允许输入电压超过电源,但越来越多的新器件取消了这个限制 (改变了输入级保护电路)。

例如,74ahc/vhc 系列芯片,其 datasheets 明确注明输入电压范围为0~5.5v,如果采用3.3v 供电,就可以实现5v→3.3v 电平转换。

(5) 专用电平转换芯片最著名的就是 164245,不仅可以用作升压/降压,而且允许两边电源不同步。

这是最通用的电平转换方案,但是也是很昂贵的 (俺前不久买还是¥45/片,虽是零售,也贵的吓人),因此若非必要,最好用前两个方案。

(6) 电阻分压法最简单的降低电平的方法。

5v电平,经1.6k+3.3k电阻分压,就是3.3v。

(7) 限流电阻法18、无极性电容和有极性电容:前者的封装基本为0805,0603。

后者用的最多为铝电解电容,好一点的钽电容19、 pqfp(plastic quad flat package,塑料四边引出扁平封装),bga(ball grid arraypackage,球栅阵列封装),pga(pin grid array package,针栅阵列封装),plcc(plastic leaded chipcarrier,塑料有引线芯片载体),sop(small outline package,小尺寸封装),tosp(thin small outlinepackage,薄小外形封装),soic(small outline integrated circuitpackage,小外形集成电路封装)集成电路常见的封装形式qfp(quad flat package)四面有鸥翼型脚(封装)bga(ball grid array)球栅阵列(封装)plcc(plastic leaded chip carrier)四边有内勾型脚(封装)soj(small outline junction) 两边有内勾型脚(封装)soic(small outline integrated circuit)两面有鸥翼型脚(封装)20、屏蔽线对静电有很强的抑制作用,双绞线对电磁感应也有一定的抑制效果21、模拟信号采样抗干扰技术:可以采用具有差动输入的测量放大器,采用屏蔽双胶线传输测量信号,或将电压信号改变为电流信号,以及采用阻容滤波等技术22、闲置不用的ic管脚不要悬空以避免干扰引入。

不用的运算放大器正输入端接地,负输入端接输出。

单片机不用的i/o口定义成输出。

单片机上有一个以上电源、接地端,每个都要接上,不要悬空23、电阻阻值色环表示法:普通的色环电阻器用4环表示,精密电阻器用5环表示24、电阻的作用为分流、限流、分压、偏置、滤波(与电容器组合使用)和阻抗匹配等25、电容的作用:隔直流,旁路,耦合,滤波,补偿,充放电,储能等26、一般电容的数字表示法单位为pf,电解电容一般为uf27、电容器的主要性能指标: 电容器的容量(即储存电荷的容量),耐压值(指在额定温度范围内电容能长时间可靠工作的最大直流电压或最大交流电压的有效值)耐温值(表示电容所能承受的最高工作温度。

).28、电感器的作用:滤波,陷波,振荡,储存磁能等29、电感器的分类:空芯电感和磁芯电感.磁芯电感又可称为铁芯电感和铜芯电感等30、半导体二极管的分类a 按材质分:硅二极管和锗二极管;b按用途分:整流二极管,检波二极管,稳压二极管,发光二极管,光电二极管,变容二极管。

31、场效应管是电压控制元件,而晶体管是电流控制元件。

在只允许从信号源取较少电流的情况下,应选用场效应管;而在信号电压较低,又允许从信号源取较多电流的条件下,应选用晶体管32、 socket是一种插座封装形式,是一种矩型的插座; slot是一种插槽封装形式,是一种长方形的插槽33、晶振的测量方法:用万用表rx10k档测量石英晶体振荡器的正,反向电阻值.正常时应为无穷大.若测得石英晶体振荡器有一定的阻值或为零,则说明该石英晶体振荡器已漏电或击穿损坏34、 io口输出高电平时,驱动能力最低,对外显示为推电流;io口输出低电平时,驱动能力最大,对外显示为拉电流35、外围集成数字驱动电路如果驱动的是感性负载,必须加限流电阻或钳住二极管36、 9013提供的驱动电流有300ma37、输出数据应该锁存(外围速度跟不上,所以需要锁存),输入数据应该有三态缓冲(加入了高阻状态,不至于对内部的数据总线产生影响)38、 8位并行输出口(必须带有锁存功能):74ls377,74ls273.8位并行输入口(必须是三态门):74ls373,74ls24439、串行口扩展并行口,并行输入口:74ls165。

并行输出口:74ls16440、键盘工作方式有三种:1、编程扫描方式2、定时扫描方式3、中断方式。

还可以专门设计一个io口用来进行双功能键的设计(上档键和下档键)41、对于ttl负载,主要应考虑直流负载特性,因为ttl的电流大,分布电容小。