fifo_read

USB连续采集卡 wwSFIFO模块说明

USB连续采集卡 wwSFIFO模块说明●针对USB连续采集模块的应用●以DLL方式提供采集缓冲及内存管理函数●功能:实现任意长度采集数据的读出北京双诺测控技术有限公司2009 10目录目录 (2)实现功能 (2)使用方法 (2)函数说明 (2)操作流程 (5)实现功能该动态库主要是针对客户要求连续采集卡返回定长数据开发的。

通过调用该动态库的函数客户可以返回定长采样数据。

文件目录 \USB\SFIFO使用方法客户使用前学要将该动态库WWSFIFO.DLL复制到当前目录下。

VC客户需要将WWSFIFO.H,WWSFIFO.lib文件同时复制到当前目录下。

完成以上步骤就可以调用WWSFIFO.DLL中的函数进行读取定长采样数据了。

以上文件在光盘\USB\定长存储模块\函数说明wwSFIFO模块包函数分为:1.模块信息函数:用于返回模块的版本信息,主要包括可以创建的内存空间个数。

2.创建内存空间函数:创建客户要求大小的内存空间。

3.写函数:将数据写入创建的内存空间。

4.查询函数:查询内存空间的数据长度。

5.读函数:从内存空间中读取定长的数据。

6.释放内存空间函数:释放创建的内存空间。

该模块通过不同的index号来区分多个内存空间,应用ww_SFIFO_Information可以得到可创建内存空间的个数。

文件目录 \USB\SFIFO❑为编号为index的板卡开辟内存空间用于保存采样数据函数:long ww_SFIFO_Create (long index, long FLEN)功能:为第index块卡开辟内存空间。

参数:✧index:板卡的序号,如0、1、2…,基础版本只支持一块板卡,因此index=0✧FLEN:sfifo 可以容纳的最大采样点数✧返回值:0创建成功, -1 内存不足, -2 错误板号…注:建议用户开辟内存空间的大小在秒级以上,如果开辟空间太小没必要用该模块去实现。

sfifo 定义为_int32类型,最大支持32位有符号数❑释放编号为index的板卡开辟内存空间函数:long ww_SFIFO_Close(long index)功能:释放编号为num的板卡开辟内存空间参数:✧index:板卡的序号,如0、1、2…✧返回值:0释放成功,-1失败,-2 错误板号…❑读取板卡信息函数:long ww_SFIFO_Information (char *pversion)功能:读取板卡信息参数:✧pversion:板卡信息。

fifo读写

fifo读写

FIFO,全称为First In First Out,即先进先出,是一种常见的数据结构。

在计算机领域中,FIFO通常指的是一种管道(pipe)的实现方式,也称为命名管道(named pipe),用于进程间通信。

在FIFO中,数据的读取和写入都是按照先进先出的原则进行的。

当一个进程向FIFO中写入数据时,数据会被存储在FIFO的尾部,而当另一个进程从FIFO中读取数据时,数据会从FIFO的头部开始读取。

FIFO的读写操作可以分为阻塞和非阻塞两种方式。

在阻塞模式下,当FIFO中没有数据可读时,读取进程会被阻塞,直到有数据可读为止;当FIFO已满时,写入进程会被阻塞,直到有空间可写为止。

在非阻塞模式下,读取进程和写入进程不会被阻塞,而是会立即返回一个错误码。

FIFO的实现方式可以基于内存或磁盘。

在基于内存的实现方式中,FIFO的数据存储在内核缓冲区中,因此读写速度较快;而在基于磁盘的实现方式中,FIFO 的数据存储在磁盘文件中,因此读写速度较慢。

FIFO的应用场景非常广泛,例如在Linux系统中,FIFO常用于进程间通信、日志记录等方面。

在多线程编程中,FIFO也可以用于线程间通信,实现线程安全的数据传输。

总之,FIFO作为一种先进先出的数据结构,在计算机领域中有着广泛的应用,其读写操作的实现方式和应用场景也非常丰富。

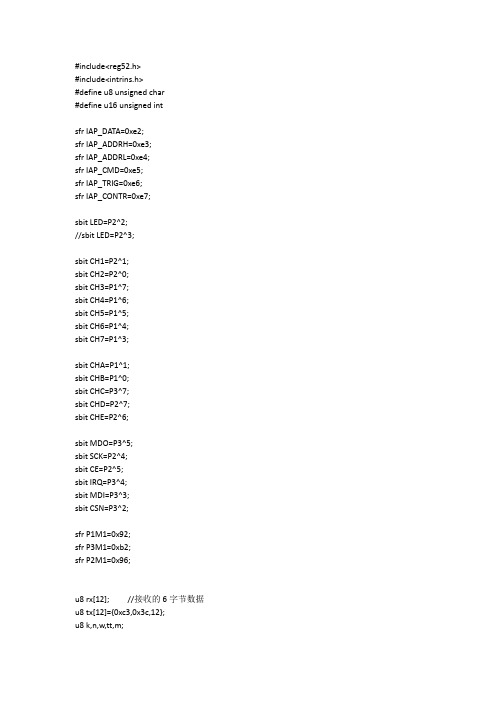

51单片机的FM1702射频卡例程

51单片机的FM1702射卡程序历程许昌美景电子产品有限公司#include<reg52.h>#include<intrins.h>#include<FM1702.h>#define uchar unsigned char#define uint unsigned intuchar Fbuff[16]; //发送FIFO缓存uchar Jbuff[16]; //接收FIFO缓存uchar UID[7]; //卡型及卡号uchar Data[4]; //按键值存储区uchar code seg[16]={0xC0,0xF9,0xA4,0xB0,0x99,0x92,0x82,0xF8,0x80,0x90,0x88,0x83,0xC6, 0xA1,0x86,0x8E}; //数码管段选对应0~fuchar count=0 ; //按键回传的值uchar shuaka,chongzhi,keyflag=0;sbit k2=P3^5; //充值‘加值键(实现加1或者加10)sbit k3=P3^2; //刷卡’减值键(实现减1或者减10)sbit k4=P3^3; //确认键sbit nWR=P2^4; //74hc373片选/*****************1702函数声明**************************/uchar spi(uchar m);void fifo_clear();void resig_write(uchar reg,uchar da);uchar resig_read(uchar reg);uchar fifo_read(uchar count,uchar *s);void fifo_write(uchar count,uchar *s);uchar inti_1702();void card_halt();uchar request();uchar card_anticoll();uchar card_select();uchar card_authtication(uchar m) ;uchar card_read(uchar m);uchar card_write(uchar m);uchar loadkey();void delay(uchar m);/********************按键显示函数声明***************/void display();void keyscan() ;void data1deal() ;void data2deal(uchar m);void lcdclear();/***********************子函数解释******************//*********************************************************///解释:这是spi总线的读写时序,所有的寄存器操作基于此时序,非常重要//////输入:要写入的16进制参数//////输出:内部传回的16进制参数///********************************************************/uchar spi(uchar m){uchar i,temp=0;for(i=0;i<8;i++){sck=0;if(m&0x80)mosi=1;elsemosi=0;m<<=1;sck=1;temp<<=1;if(miso)temp|=0x01;}sck=0;mosi=0;return temp;}/*********************************************************///解释:写寄存器函数//////输入:寄存器地址以及要写入的参数//////输出:////注意!!在所有的资料中都没有给出寄存器寻址时的格式,下边的有,看仔细了,如果连寄存器都找不到,后边的就不用看了/********************************************************/void resig_write(uchar reg,uchar da){sck=0;reg<<=1;cs=0;reg=reg&0x7e;spi(reg);spi(da);cs=1;}/*********************************************************///解释:读寄存器函数//////输入:寄存器地址//////输出:该寄存器目前的值////注意!!读写寄存器时指令不一样,仔细看。

fifo读写

FIFO读写概述FIFO(First In, First Out)是一种常用的数据结构,也称为队列。

它的特点是按照先进先出的原则进行数据读写,即先进入的数据首先被读取或使用。

FIFO读写操作广泛应用于计算机科学和软件工程领域,能够有效地管理数据传输和处理。

FIFO的实现方式FIFO可以通过数组或链表来实现。

数组实现数组实现的FIFO需要两个指针,分别指向队列的头部和尾部。

数据的读取和写入都是通过移动头部和尾部指针的方式来完成的。

1.初始化一个大小为n的数组,并设定头部指针head和尾部指针tail的初始位置为0。

2.数据写入时,将数据存储在tail位置,并将tail指针向后移动一位。

如果tail超过了数组的长度n,则将tail指针重置为0。

3.数据读取时,将head位置的数据读取出来,并将head指针向后移动一位。

如果head超过了数组的长度n,则将head指针重置为0。

链表实现链表实现的FIFO使用一个链表结构来存储数据,每个节点包含数据和指向下一个节点的指针。

1.初始化一个空链表。

2.数据写入时,创建一个新节点,将数据存储在节点中,并将该节点放置在链表末尾。

3.数据读取时,读取链表头部节点中的数据,并将该节点从链表中删除。

FIFO的应用场景FIFO读写操作在各种场景中都得到了广泛应用。

任务调度在操作系统中,任务调度器使用FIFO读写操作来管理进程的执行顺序。

先进入队列的任务先被调度执行,保证了任务的顺序性。

缓存管理在计算机硬件中,缓存是一种用于加速访问速度的存储设备。

FIFO读写操作可以实现缓存数据的替换策略。

当缓存区满时,新的数据会替换掉最旧的数据。

数据传输在网络通信中,FIFO读写操作常用于数据包的传输。

数据包按照到达的顺序进入队列,然后按照先进先出的方式进行发送,保证数据的有序性。

并发控制在并发编程中,FIFO读写操作可以实现互斥锁的队列。

多个线程按照先进先出的顺序申请锁,避免了死锁和优先级反转等并发问题。

点焊路径调试

1.焊点轨迹调试进行车身焊点轨迹调试需具备以下KUKA机器人的基础知识:➢具有KRC编程基础,对点焊指令和机器人移动指令有一定了解。

➢熟悉机器人三种动作模式,熟练掌握示教器的基本操作。

➢掌握四种坐标系之间的对应关系,特别是车身坐标系。

➢电阻焊的原理以及伺服焊枪基本技术参数。

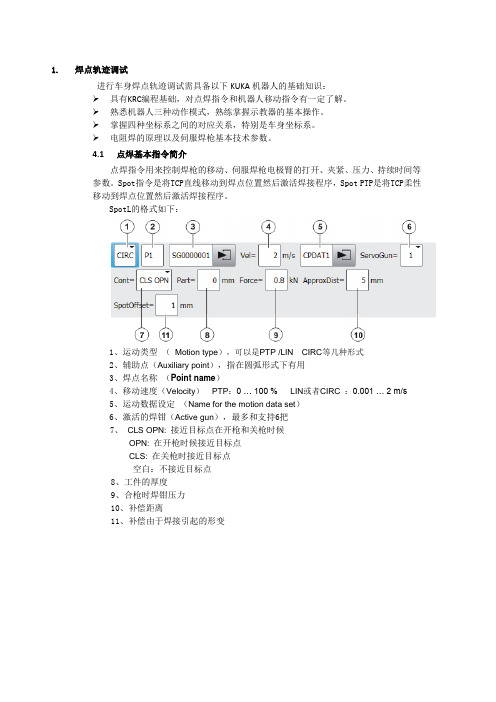

4.1点焊基本指令简介点焊指令用来控制焊枪的移动、伺服焊枪电极臂的打开、夹紧、压力、持续时间等参数。

Spot指令是将TCP直线移动到焊点位置然后激活焊接程序,Spot PTP是将TCP柔性移动到焊点位置然后激活焊接程序。

SpotL的格式如下:1、运动类型(Motion type),可以是PTP /LIN CIRC等几种形式2、辅助点(Auxiliary point),指在圆弧形式下有用3、焊点名称(Point name)4、移动速度(Velocity)PTP:0 … 100 %LIN或者CIRC :0.001 … 2 m/s5、运动数据设定(Name for the motion data set)6、激活的焊钳(Active gun),最多和支持6把7、CLS OPN: 接近目标点在开枪和关枪时候OPN: 在开枪时候接近目标点CLS: 在关枪时接近目标点空白:不接近目标点8、工件的厚度9、合枪时焊钳压力10、补偿距离11、补偿由于焊接引起的形变12、程序号选项13、调用的焊接程号示意图如下所示:图5.34 点焊示意图调试时候注意事项:1、要执行INT指令,否则在执行焊接指令时候会报轨迹未编程2、第一条运动指令必须为PTP3、编程时候要点击“选择”4、修改焊点名称时候,要将机器人移动到该焊点位置,否则焊点位置会被记录成修改名称的位置。

5、调试时候焊钳静臂要贴到工件上6、调试时候在T1模式下,T2验证时候要注意改成虚拟焊接模式(TEST模式)7、注意4轴和6轴数据,上下目标点机器人不要角度变化过大4.1焊点轨迹调试4.3.1调试流程焊点轨迹调试就是让机器人抓着焊枪从home点出发,依次焊完所有焊点后,再回到home点的整个调试过程。

非阻塞IO与阻塞IO区别

⾮阻塞IO与阻塞IO区别⼀、介绍1、阻塞⽅式:1) 写进程未退出,read阻塞,等待写端的输⼊2) 写进程终⽌了或关闭了该FIFO,read⾮阻塞,为FIFO的读进程产⽣⼀个⽂件结束标志,read的返回值为0。

2、⾮阻塞⽅式:假设⼀个进程以⾮阻塞读⽅式打开⼀个FIFO.该FIFO之前已经被以写⽅式被其他进程打开,但⽆数据被写⼊,那么此时读进程需要⽴刻返回,那么应该返回什么呢?我们知道如果 read()读数据时第⼀个读到的是⽂件结束标志,那么就返回0。

如果像我们想的那样没有数据读应该返回0 ,那么这个0就具有⼆义性。

因为我们不知道是没有数据造成的返回0还是写端关闭造成的返回0.所以POSIX.1要求,对⼀个⾮阻塞的描述符如果⽆数据可读,则read返回-1,⽽且 errno被设置为 EAGAIN。

1) 如果在随后调⽤read函数之前,如果另⼀个进程已经以写⽅式打开了该FIFO,并写⼊了数据,那么正常读取数据。

2) 如果在随后调⽤read函数之前,如果另⼀个进程已经以写⽅式打开了该FIFO,但是并未写⼊数据,read调⽤会⽴刻出错返回-1,并设置errnno为EAGAIN。

3)如果在随后调⽤read函数之前,没有其他进程以写⽅式打开该FIFO,或是曾经有但是在read读时已经关闭了,那么read返回0,表⽰读到⽂件结束标志。

⼆、mkfifo介绍#include <sys/types.h>#include <sys/stat.h>int mkfifo( const char*pathname, mode_t mode);参数:pathname:FIFO的路径名+⽂件名。

mode:mode_t类型的权限描述符,同open的参数。

返回值:成功:返回0失败:如果⽂件已经存在,则会出错且返回-1。

三、操作FIFO⽂件时的特点:系统调⽤的I/O函数都可以作⽤于FIFO,如open、close、read、write等。

简述 fifo 使用场景和使用方法

FIFO使用场景和使用方法介绍FIFO(First In, First Out)是一种有序列表的数据结构,其中首先进入的元素会被最先取出,类似于队列的工作原理。

FIFO常用于多线程或多进程的应用程序中,用于实现线程间或进程间的数据共享和通信。

FIFO的使用场景FIFO的使用场景很广泛,特别是在并发编程和多线程环境中,下面列举了一些常见的使用场景:1. 生产者-消费者模型生产者-消费者模型是一种常见的并发编程模式,其中生产者线程将数据放入FIFO 队列,而消费者线程则从队列中取出数据进行处理。

这种模型可以实现数据的生产与消费之间的解耦,提高程序的健壮性和效率。

2. 进程间通信在多进程的应用程序中,不同进程之间需要进行数据的传输和共享。

FIFO可以作为进程间通信的一种方式,一个进程将数据写入FIFO队列,而另一个进程则通过读取队列获取数据。

这种方式可以实现进程间的数据交换和共享,避免了复杂的进程间通信机制。

3. 网络编程在网络编程中,FIFO可以用于实现数据的传输和协调。

例如,多个客户端连接到服务器并发送数据,服务器通过FIFO队列接收并处理这些数据,从而实现了多个客户端与服务器之间的数据交互。

4. 缓存FIFO可以作为缓存的一种实现方式,适用于需要按照特定顺序处理数据的场景。

例如,在图像处理中,可以使用FIFO队列存储待处理的图像数据,然后逐个取出进行处理,确保按照先进先出的顺序处理图像。

FIFO的使用方法1. 创建FIFO队列首先,需要创建一个FIFO队列,可以使用系统调用函数(如mkfifo)创建一个命名管道,或者使用编程语言提供的FIFO类或库函数创建一个内存中的FIFO队列。

2. 向FIFO队列写入数据使用write系统调用函数(或编程语言提供的写入方法),将数据写入FIFO队列。

写入的数据会按照写入的顺序被存储在队列中,等待被读取和处理。

3. 从FIFO队列读取数据使用read系统调用函数(或编程语言提供的读取方法),从FIFO队列中读取数据。

fifo的read latency

fifo的read latency先进先出(FIFO)是一种常用的存储数据结构,它的读取延迟是一个重要的性能指标。

读取延迟是指从数据被放入队列到被读取出来所需的时间。

在这篇文章中,我们将探讨FIFO的读取延迟以及它对系统性能的影响。

在计算机系统中,FIFO是一种非常常见的数据结构,用于管理数据的存储和读取顺序。

它遵循“先进入队列的数据先被读取”的原则。

当数据被放入FIFO队列中时,它们会按照顺序排列,等待被读取。

读取延迟是指从数据进入队列开始到被读取出来所经过的时间。

FIFO的读取延迟受多种因素的影响。

首先是数据存储的方式。

如果数据存储在内存中,那么读取延迟主要取决于内存的访问速度。

内存越快,读取延迟越低。

另一方面,如果数据存储在磁盘或网络中,读取延迟将受到存储介质和网络传输速度的限制。

其次,读取延迟还取决于队列中等待读取的数据量。

如果队列中的数据量很大,那么读取延迟可能会较长。

这是因为读取操作需要遍历整个队列才能找到要读取的数据。

相反,如果队列中的数据量很小,读取延迟将会很短。

此外,系统的负载情况也会对FIFO的读取延迟产生影响。

在高负载情况下,系统可能会优先处理其他任务,从而延迟了对FIFO队列的读取操作。

因此,FIFO的读取延迟可能会随着系统负载的增加而增加。

FIFO的读取延迟对系统性能有着重要的影响。

如果读取延迟较短,系统将能更快地获取所需的数据,并加快整体的处理速度。

相反,如果读取延迟较长,系统的响应时间将变慢,可能导致性能下降。

为了减少FIFO的读取延迟,可以采取一些优化策略。

首先,可以尽量提高数据存储的速度,例如使用高速内存或快速存储设备。

其次,可以通过增加系统资源来减少负载情况。

例如,增加处理器的数量或提高网络带宽。

此外,可以实施合理的数据管理策略,如定期清空队列中的数据,以确保队列的数据量保持在一个较低的水平。

总结起来,FIFO的读取延迟是指从数据进入队列到被读取出来所需的时间。

FIFO的实现

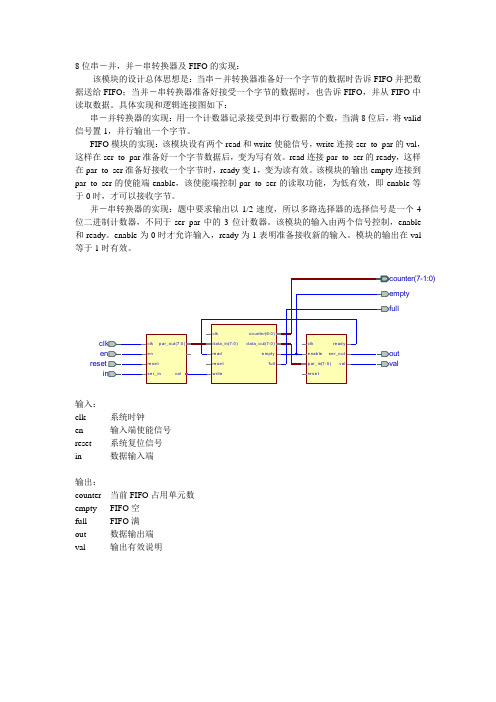

8位串-并,并-串转换器及FIFO的实现:

该模块的设计总体思想是:当串-并转换器准备好一个字节的数据时告诉FIFO并把数据送给FIFO;当并-串转换器准备好接受一个字节的数据时,也告诉FIFO,并从FIFO中读取数据。

具体实现和逻辑连接图如下:

串-并转换器的实现:用一个计数器记录接受到串行数据的个数,当满8位后,将valid 信号置1,并行输出一个字节。

FIFO模块的实现:该模块设有两个read和write使能信号,write连接ser_to_par的val,这样在ser_to_par准备好一个字节数据后,变为写有效。

read连接par_to_ser的ready,这样在par_to_ser准备好接收一个字节时,ready变1,变为读有效。

该模块的输出empty连接到par_to_ser的使能端enable,该使能端控制par_to_ser的读取功能,为低有效,即enable等于0时,才可以接收字节。

并-串转换器的实现:题中要求输出以1/2速度,所以多路选择器的选择信号是一个4位二进制计数器,不同于ser_par中的3位计数器。

该模块的输入由两个信号控制,enable 和ready。

enable为0时才允许输入,ready为1表明准备接收新的输入。

模块的输出在val 等于1时有效。

reset

输入:

clk 系统时钟

en 输入端使能信号

reset 系统复位信号

in 数据输入端

输出:

counter 当前FIFO占用单元数

empty FIFO空

full FIFO满

out 数据输出端

val 输出有效说明。

使用FIFO完成数据传输与同步_上_

今年快闪存储记忆卡出口额增幅将达 100%

环球资源近日发表“中国采购资讯报告:快闪存储记忆卡与读卡器”;报告显示中国大陆制造商 在 2005 年将出口价值 3 亿 240 万美元的快闪存储记忆卡及价值 2,520 万美元的读卡器—— —比 2004 年分别增加 100%与 20%。

此外,制造商的生产重点正转向 miniSD 卡(mini Secure Digital)与 RS 多媒体卡(Reduced- Size MultiMediaCards) ,这两种卡的尺寸约为原来尺寸的一半。

CIC 中国集成电路 China lnte gra te d Circult

设计开发

使用 F IF O 完成数据传输与同步( 上)

中关村益华软件技术学院 赵震甲

摘要:将数据从一个时钟域同步至另一个时钟域,常用的两个方法为: 1、使用握手(handshake)信号; 2、使用 FIFO。使用握手方法的缺点是传递及辩识用于数据传输的所有握手信号所需的潜伏时间 (latency) 会增加延迟并降低传输效率。因此时钟域之间传递数据最常用的方法是使用 FIFO。异步 FIFO 的运作(operation)方法是: 数据从一个时钟域写入 FIFO,该数据从另一个时钟域自 FIFO 读出。 本文讨论两种异步 FIFO 的设计技巧: 1、比较同步指针;2、比较异步指针。 关键词: 先进先出存储存器 FIFO (First-In-First-Out memories),位 (bit),时钟边界(clock boundary),时钟域 (clock domain),时钟沿 (clock edge),格雷码 (Gray code),亚稳定状态 (metastability),指 针 (pointer),读 指 针 (read pointer),写 指 针 (write pointer),读 时 钟 (read clock),写时钟 (write clock),读运作 (read operation),写运作 (write operation),同步 (synchronize),同步作用(synchronization),同步器(synchronizer),异步(asynchronous)。

航模12通接收机 51单片机C程序

CE=0;

RX_mode();//CRC,8 bit,Power on,TX

channel_set(66);

TX_power_set(1);

TX_size_set(8);

//TX_address(address);

}

void initial()

initial();

TR0=1;//打开定时器0,开始统计信号

LED=1;

channel_set(hopping[0]);

lose=1;

while(1)

{

while(IRQ&&lose);TR1=1;//等待无线模块的中断信号,直到第一个有效信号再开始输出6通道信号

if(lose)

{

tt=0;m=0;jump_1=0;jump_2=0;//收到有效信号后刷新定时器0、跳频器

RX_address(address);

}

else

{

RX_address(address);

}

//while(1);

}

main()

{

delay1ms();delay1ms();delay1ms();delay1ms();delay1ms();

delay1ms();delay1ms();delay1ms();delay1ms();delay1ms();

sfr IAP_TRIG=0xe6;

sfr IAP_CONTR=0xe7;

sbit LED=P2^2;

//sbit LED=P2^3;

sbit CH1=P2^1;

sbit CH2=P2^0;

sbit CH3=P1^7;

fifo读写时序

fifo读写时序

FIFO是一种先进先出的缓冲区,主要用于数据传输和同步。

在FIFO中,读写时序非常重要。

本文将介绍FIFO的读写时序。

首先,我们需要了解FIFO的结构。

FIFO由一个读指针和一个写指针组成。

当数据写入FIFO时,写指针向前移动,当数据从FIFO中读取时,读指针向前移动。

如果FIFO已满,则不能再写入数据,如果FIFO为空,则不能再读取数据。

接下来,我们将介绍FIFO的读写时序。

当FIFO为空时,读指针和写指针指向同一位置。

当数据写入FIFO时,写指针向前移动。

如果写指针到达FIFO的末尾,则它将被重置到FIFO的起始位置。

如果FIFO已满,则不能再写入数据。

当数据从FIFO中读取时,读指针向前移动。

如果读指针到达FIFO的末尾,则它将被重置到FIFO的起始位置。

如果FIFO为空,则不能再读取数据。

需要注意的是,FIFO的读写时序会受到时钟信号的影响。

时钟信号可以控制FIFO的读写速度和方向。

如果时钟信号的频率过高,则数据可能会被写入或读取过快,导致数据错误。

如果时钟信号的频率过低,则数据可能会被写入或读取过慢,导致FIFO无法满足系统的实时要求。

因此,在设计FIFO的读写时序时,需要考虑时钟信号的频率和数据的传输速率。

通过合理的时序设计,可以确保FIFO的正确性和可靠性。

- 1 -。

fifo的read latency

fifo的read latency摘要:1.介绍FIFO2.读取延迟的概念3.FIFO 的读取延迟的影响因素4.降低FIFO 读取延迟的方法5.总结正文:一、介绍FIFOFIFO(First In First Out,先进先出)是一种数据结构,通常用于在计算机系统中缓存数据。

它的原理是按照数据输入的顺序进行存储,当需要读取数据时,也是按照数据输入的顺序进行读取。

这种数据结构在很多场景下都能看到,例如操作系统的进程调度、网络数据传输等。

二、读取延迟的概念读取延迟,顾名思义,是指从请求读取数据到实际读取到数据所需要的时间。

在FIFO 中,读取延迟主要受到FIFO 的容量、读取数据的速度以及数据的输入速度等因素的影响。

三、FIFO 的读取延迟的影响因素1.FIFO 的容量:容量越大,读取延迟通常会越小,因为其中有更多的数据可以被快速读取。

但是,容量的增大也会导致FIFO 需要更多的时间来处理数据,因此也会在一定程度上增加读取延迟。

2.读取数据的速度:读取数据的速度越快,读取延迟就会越小。

这通常取决于读取数据的硬件设备以及处理数据的算法。

3.数据的输入速度:数据的输入速度越快,读取延迟就可能越大。

因为如果输入速度过快,FIFO 可能无法及时处理所有的数据,导致读取延迟增大。

四、降低FIFO 读取延迟的方法1.增加FIFO 的容量:如果读取延迟主要受到FIFO 容量的影响,那么增加FIFO 的容量是一个有效的方法。

2.优化读取数据的算法:优化读取数据的算法可以提高读取速度,从而降低读取延迟。

3.控制数据的输入速度:通过控制数据的输入速度,可以避免数据的输入速度过快导致读取延迟增大。

五、总结总的来说,FIFO 的读取延迟是一个复杂的问题,需要综合考虑FIFO 的容量、读取数据的速度以及数据的输入速度等多种因素。

萝丽6通道接收机二代A版C程序

byte<<=1; //数据左移

byte|=MDO; //单片机读取数据

SCK=0; //时钟信号的下降沿后无线模块输出新数据

}

return byte;

}

void REG_write(u8 address,u8 command) //写配置寄存器

CE=0;

REG_write(0x07,0x40); //清除无线模块中断信号

CE=1;

if(rx[0]==0xaa&&rx[1]==0x55)channel=rx[2],connecting=0;

}

connecting=1;

while(connecting)

{

main()

{

initial();

TR0=1; //打开定时器0,开始统计信号

LED=1;

while(1)

{

while(IRQ);TR1=1; //等待无线模块的中断信号,直到第一个有效信号再开始输出6通道信号

tt=0; //收到有效信号后刷新定时器0

{

tt++;w++;

if(tt==255)tt=31;

if(w==15) //每秒统计接收到的有效信号数量,小于20个点亮LED示警,表示信号微弱

{

if(k<20)LED=0;

else LED=1;

k=0;w=0;

}

if(tt>30)rx[2]=0; //如果tt增长到30,表示已经有两秒未收到有效信号,关闭电机防止飞机飞丢

i = 8;

异步fifo的读写

异步fifo的读写这⾥不讨论异步fifo是如何实现的,⽽是在实现fifo的前提下,对fifo的读写。

现在遇到的问题是:总线的数据不能写⼊fifo中,但是地址能加⼀。

代码如下:if( !fifo_tx_full && cpu_write_fifo_en ) beginfifo_r[ write_addr[ADDR_SIZE - 1'b1 : 0] ] <= cpu_2_fifo;write_addr <= write_addr + 1'b1;end接收到的数据位00.可能是时序约束问题,在之前我确实没有约束。

改了译码的编写后就好了,在此,没有译码必须是1个1的译码,不然就会出错。

但是,地址不够,我要如何改,现在还不确定。

但是译码必须是1 个 1.//控制三态always @(cpu_read_req or intrp_en_en or fifo_con_en) beginif(cpu_read_req)en_tri = 1'b1;elseen_tri = 1'b0;end由于read和write是同⼀地址,所以这样总线就冲突了。

这样读总线上的读数据就都是0.always @(cpu_read_req or intrp_en_en or fifo_con_en) begin if(cpu_read_req && cpu_read_clk ) en_tri = 1'b1; else en_tri = 1'b0;end修改后的代码,读请求和cpu_read_clk同时有效,才使能输出。

这样总线就不会冲突了。

结果正确。

注:通过这个,知道总线上只能有⼀个是发数据,其他的设备只能是接收数据。

不然就会冲突,且此时接收可能为0。

一同步FIFO的意思是说FIFO的读写时钟是同一个时钟不

一、同步FIFO的意思是说FIFO的读写时钟是同一个时钟,不同于异步FIFO,异步FIFO的读写时钟是完全异步的。

同步FIFO的对外接口包括时钟,清零,读请求,写请求,数据输入总线,数据输出总线,空以及满信号。

下面分别对同步FIFO的对外接口信号作一描述:1.时钟,输入,用于同步FIFO的读和写,上升沿有效;2.清零,输入,异步清零信号,低电平有效,该信号有效时,FIFO被清空;3.写请求,输入,低电平有效,该信号有效时,表明外部电路请求向FIFO写入数据;4.读请求,输入,低电平有效,该信号有效时,表明外部电路请求从FIFO中读取数据;5.数据输入总线,输入,当写信号有效时,数据输入总线上的数据被写入到FIFO中;6.数据输出总线,输出,当读信号有效时,数据从FIFO中被读出并放到数据输出总线上;7.空,输出,高电平有效,当该信号有效时,表明FIFO中没有任何数据,全部为空;8.满,输出,高电平有效,当该信号有效时,表明FIFO已经满了,没有空间可用来存贮数据。

使用VHDL描述的FIFO将以上面的接口为基础,并且可以参数化配置FIFO 的宽度和深度。

二、同步FIFO内部通过控制电路和RAM实现,控制电路主要包括写指针管理电路,读指针管理电路,以及FIFO状态判断电路,对于同步FIFO来讲,读和写的指针管理电路实际上就是二进制计数器。

现在的FPGA都具有Block RAM,通过VHDL描述可以对其进行调用,为了能够实现任意深度和宽度的FIFO,那么在用VHDL描述RAM的时候需要使用generic 使得RAM的调用能够参书化。

同样,对于读写指针计数器,也需要参数化的描述方法。

下面主要对FIFO的状态判断如何判断进行一些说明。

假设宽度任意而深度为8的FIFO,当读指针read_pointer和写指针write_pointer的值一样的时候,很显然,这时FIFO的状态为空。

比较麻烦的是对FIFO是否已经满的状态的判断,因为存在两种情况,第一种情况时写指针write_pointer比读指针read_pointer 大,比如writer_pointer = 7而read_pointer = 0,还有一种情况时写指针writer_pointer比读指针read_pointer小,比如writer_pointer = 2而read_pointer = 3。

西门子plc指令含义大全详解

西门子plc指令含义大全详解指令(英文全称意思 ) :指令含义1、LD ( Load 装载 ) :动合触点2、LDN ( Load Not 不装载 ) :动断触点3、A ( And 与动合) : 用于动合触点串联4、AN ( And Not 与动断 ) :用于动断触点串联5、O ( Or 或动合 ) :用于动合触点并联6、ON ( Or Not 或动断 ) : 用于动断触点并联7、= ( Out 输出 ) :用于线圈输出8、OLD ( Or Lode):块或9、ALD ( And Lode): 块与10、LPS ( Logic Push ) :逻辑入栈11、LRD ( Logic Read ) :逻辑读栈12、LPP ( Logic Pop ) :逻辑出栈13、NOT ( not 并非 ) :非14、NOP ( No Operation Performed ) : 无操作15、AENO ( And ENO ) :指令盒输出端ENO相与16、S ( Set 放置 ) :置117、R ( Reset 重置,清零 ) :清零18、P ( Positive) :上升沿19、N ( Negative) :下降沿20、TON ( On_Delay Timer ) :接通延时定时器21、TONR ( Retentive On_Delay Timer ) : 有记忆接通延时定时器22、TOF ( Off_ Delay Timer ) :断开延时定时器23、CTU ( Count Up ) : 增计数器24、CTD ( Count Down ) : 减计数器25、CTDU ( Count Up/ Count Down ) :增减计数器26、ADD ( add 加 ) : 加注意//ADD_I (_ I 表示整数)ADD_DI( DI表示双字节整数)ADD-R (R 表示实数)它们都是加运算只是数的大小不同。

27、SUB ( Subtract 减去,减少) :减28、MUL ( Multiply ) : 乘29、DIV ( Divide ) : 除30、SQRT ( Square root ) : 求平方根31、LN ( Napierian Logarithm 自然对数 ) : 求自然对数32、EXP ( Exponential 指数的 ) :求指数33、INC_B ( Increment 增加 ) :增1//其中_B代表数据类型还有W(字节)、DW双字后面几个都是这样的。

fifo算法例题解析

fifo算法例题解析FIFO算法(先进先出队列算法)是一种常见的数据结构算法,用于处理需要按照顺序处理的数据。

以下是FIFO算法的一些例题解析: 1. 装填FIFO队列假设有一个装填FIFO队列的程序,要求从队列中取出一个元素并将其放入另一个队列中,以保持FIFO队列的顺序。

下面是一个简单的例题:```pythonQueue = []def add(queue, element):queue.append(element)def take(queue):while queue:element = queue.pop(0)print(element)```在这个例题中,我们定义了一个名为`add`的函数,用于将元素添加到队列中,以及一个名为`take`的函数,用于从队列中取出一个元素并将其放入另一个队列中。

在`add`函数中,我们首先将一个新元素`element`添加到队列的末尾。

然后,我们使用一个 while 循环来不断从队列中取出一个元素并将其放入另一个队列中。

当队列为空时,我们返回`element`并将其打印出来。

在`take`函数中,我们使用`pop(0)`方法从队列中取出第一个元素,并将其放入另一个队列中。

下面是一个运行示例:```[1] /[2] /[3] /[4] /[5] /[6] /[1] /[2] /[3] /[4] /[5] /[6] /[0] /[--输出--] /[5] / /[6] / /[1] / /[2] / /[3] / /[4] / /[0] / /[--输出--] /[--输出--] /[--输出--] /```在这个示例中,我们从第一个元素开始取出,直到队列为空为止,并将结果打印出来。

输出结果如下:```123456[1] /[2] /[3] /[4] /[5] /[6] /[1] /[2] /[3] /[4] /[0] /[--输出--] /[5] / /[6] / /[1] / /[2] / /[3] / /[4] / /[0] / /[--输出--] /[--输出--] /[--输出--] /```2. 读写FIFO队列假设有一个读写FIFO队列的程序,用于读取和写入队列中的元素,以保持FIFO队列的顺序。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

/********************************************************说明:1、该模块是自定义的fifo读操作控制器2、avalon总线信号,每次操作时仅维持一个时钟周期3、读操作有两个时钟的等待4、状态读的是fifo的usedw,位数可调,默认6bit5、fifo外设的数据位数可调,默认12bit********************************************************/module fifo_read_avalon(clk,reset_n,chipselect,byteenable,address,read,readdata,write,writedata,//fifo接口q,empty,usedw,rdreq,//读缓存fifo数据,rd=‘0’时开始读flag,//rd为0标志wrreq,//ad控制口cs_control,//写通道使能控制cs为低,写通道wr_control,//写启动转换wr=0channel_address);parameter bits_of_q=16;parameter bits_of_usedw=8;input clk;//总线时钟input reset_n;//总线复位input chipselect;//片选input[1:0]address;//地址线input read;//读请求output[31:0]readdata;//读数据input write;//写请求input[31:0]writedata;//写数据input[3:0]byteenable;input[bits_of_q-1:0]q;//读取fifo数据input empty;//fifo空标志input flag;input[bits_of_usedw-1:0]usedw;//fifo使用情况output rdreq;//读fifo请求output wrreq;//fifo写请求//输出输入描述reg[31:0]readdata;reg rdreq;reg wrreq;reg wait_ready;//等待周期标志reg ready;//控制读的时钟标志//fifo寄存器wire[31:0]read_data_reg;//读数据寄存器wire[31:0]read_usedw_reg;//读状态寄存器reg read_data_reg_sel;//读数据寄存器使能reg read_usedw_reg_sel;//读状态寄存器使能//ad寄存器reg[2:0]channel_reg;//ad控制寄存器reg start_reg;reg channel_reg_sel;//控制csreg start_reg_sel;//控制wroutput cs_control;output wr_control;output[2:0]channel_address;reg cs_control;reg wr_control;//对控制寄存器地址进行译码,非阻塞always@(address)beginread_data_reg_sel=1'b0;read_usedw_reg_sel=1'b0;channel_reg_sel=1'b0;start_reg_sel=1'b0;case(address)2'b00:channel_reg_sel=1'b1;//使能读取数据寄存器2'b01:start_reg_sel=1'b1;//使能读取状态寄存器2'b10:read_data_reg_sel=1'b1;//使能读取状态寄存器2'b11:read_usedw_reg_sel=1'b1;//使能读取状态寄存器default:beginread_data_reg_sel=1'b0;read_usedw_reg_sel=1'b0;channel_reg_sel=1'b0;start_reg_sel=1'b0;endendcaseend//写通道寄存器寄存器always@(posedge clk or negedge reset_n)beginif(reset_n==1'b0)channel_reg=0;elsebeginif(write&chipselect&channel_reg_sel)begincs_control=1'b0;//cs至0写通道if(byteenable[0])channel_reg=writedata[2:0];end//else//cs_control=1'b1;endend//输出地址assign channel_address=channel_reg;//写至端口//写开使寄存器寄存器always@(posedge clk or negedge reset_n)beginif(reset_n==1'b0)start_reg=0;elsebeginif(write&chipselect&start_reg_sel)beginwr_control=1'b0;//wr至0,开始转换if(byteenable[0])start_reg=writedata[0];end//else//wr_control=1'b1;endend//读fifo请求always@(flag or clk or reset_n)beginif(!reset_n)wrreq=1'b0;else if(!flag)//wait_ready为0,rdreq信号只持续一个时钟,由wait_ready引起wrreq=1'b1; //empty为0即不为空elsewrreq=1'b0;end//读fifo请求always@(read or chipselect or read_data_reg_sel or empty or flag or wait_ready or ready) beginrdreq=1'b0;if(read&chipselect&read_data_reg_sel)//wait_ready为0,rdreq信号只持续一个时钟,由wait_ready引起rdreq=1'b1;//empty为0即不为空else//& &!flag&!flag//&!wait_readyrdreq=1'b0;//&!empty&!empty&!readyend//控制时钟周期的标志always@(posedge clk or negedge reset_n)if(!reset_n)wait_ready<=1'b0;else if(read&chipselect&!wait_ready&!ready&(read_data_reg_sel|read_usedw_reg_sel)) //fifo收到rdreq的上升沿,即等待周期中wait_ready<=1'b1;else if(wait_ready)//第二个时钟上升沿,readdata将返回q值wait_ready<=1'b0;elsewait_ready<=1'b0;always@(posedge clk or negedge reset_n)if(!reset_n)ready<=1'b0;else if(wait_ready)//fifo收到rdreq的上升沿,即等待周期中ready<=1'b1;elseready<=1'b0;//读取fifo寄存器数值always@(posedge clk or negedge reset_n)if(!reset_n)readdata=32'h88888888;else if(wait_ready)//等待一个时钟后返回结果标志if (wait_ready)if(rdreq=1'b1)case(address)2'b10:readdata=read_data_reg;//返回数据值2'b11:readdata=read_usedw_reg;//返回空状态default:readdata=32'h88888888;endcasewire[32-bits_of_q-1:0]tmp1;wire[32-bits_of_usedw-1:0]tmp2;assign tmp1=0;assign tmp2=0;assign read_data_reg={tmp1,q};//读入fifo输出的数据assign read_usedw_reg={tmp2,usedw};//读fifo状态tmp2都为零了endmodule。