数字逻辑电路-学习指南

数字逻辑电路基础知识整理

数字逻辑电路基础知识整理数字逻辑电路是电子数字系统中的基础组成部分,用于处理和操作数字信号。

它由基本的逻辑门和各种组合和顺序逻辑电路组成,可以实现各种功能,例如加法、减法、乘法、除法、逻辑运算等。

下面是数字逻辑电路的一些基础知识整理:1. 逻辑门:逻辑门是数字逻辑电路的基本组成单元,它根据输入信号的逻辑值进行逻辑运算,并生成输出信号。

常见的逻辑门包括与门、或门、非门、异或门等。

2. 真值表:真值表是描述逻辑门输出信号与输入信号之间关系的表格,它列出了逻辑门的所有输入和输出可能的组合,以及对应的逻辑值。

3. 逻辑函数:逻辑函数是描述逻辑门输入和输出信号之间关系的数学表达式,可以用来表示逻辑门的操作规则。

常见的逻辑函数有与函数、或函数、非函数、异或函数等。

4. 组合逻辑电路:组合逻辑电路由多个逻辑门组合而成,其输出信号仅取决于当前的输入信号。

通过适当的连接和布线,可以实现各种逻辑操作,如加法器、多路选择器、比较器等。

5. 顺序逻辑电路:顺序逻辑电路由组合逻辑电路和触发器组成,其输出信号不仅取决于当前的输入信号,还取决于之前的输入信号和系统状态。

顺序逻辑电路可用于存储和处理信息,并实现更复杂的功能,如计数器、移位寄存器、有限状态机等。

6. 编码器和解码器:编码器将多个输入信号转换成对应的二进制编码输出信号,解码器则将二进制编码输入信号转换成对应的输出信号。

编码器和解码器可用于信号编码和解码,数据传输和控制等应用。

7. 数字信号表示:数字信号可以用二进制表示,其中0和1分别表示低电平和高电平。

数字信号可以是一个比特(bit),表示一个二进制位;也可以是一个字(word),表示多个二进制位。

8. 布尔代数:布尔代数是逻辑电路设计的数学基础,它通过符号和运算规则描述了逻辑门的操作。

布尔代数包括与、或、非、异或等基本运算,以及与运算律、或运算律、分配律等运算规则。

总的来说,数字逻辑电路是由逻辑门和各种组合和顺序逻辑电路组成的,它可以实现各种基本逻辑运算和数字信号处理。

数字逻辑电路基础知识整理(属于个人笔记)

让信念坚持下去,梦想就能实现!! Cx5692855@

1

定正飞的收藏

编/译码器主要有 2/4、3/8 和 4/16 译码器 74X139、 74X138、74X154 等。 4:计数器 计数器主要有同步计数器 74 X161 和异步计数器 74X393 等。 5:寄存器 寄存器主要有串-并移位寄存器 74X164 和并-串寄存器 74X165 等。 6:触发器 触发器主要有 J-K 触发器、带三态的 D 触发器 74X374、不带三态的 D 触发器 74X74、 施密特触发器等。 7:锁存器 锁存器主要有 D 型锁存器 74X373、寻址锁存器 74X25 9 等。 8:缓冲驱动器 缓冲驱动器主要有带反向的缓冲驱动器 74X24 0 和不带反向的缓冲驱动器 74X244 等。 9:收发器 收发器主要有寄存器收发器 74X543、通用收发器 74X245、总线收发器等。 10:总线开关 < br />总线开关主要包括总线交换和通用总线器件等。 11:背板驱动器 背板驱动器主要包括 TTL 或 LVTTL 电平与 GTL/GTL+(GTLP)或 BTL 之间的电平转换 器件。 12:包含特殊功能的逻辑器件 A.总线保持功能(Bus hold) 由内部反馈电路保持输入端最后的确定状态,防止因输入端浮空的不确定而导致器 件振荡自激损坏;输入端无需外接上拉或下拉电阻,节省 PCB 空间,降低了器件成本开销 和功耗。ABT、LVT、ALVC、ALVCH、 ALVTH、LVC、GTL 系列器件有此功能。 命名特征为 附加了“H& rdquo;如:74ABTH16244。

定正飞的收藏

高级 CMOS 逻辑器件 与 TTL 电平兼容高级 CMOS 逻辑器件 高级高速 CMOS 与 TTL 电平兼容高级高速 CMOS 高级低压 CMOS 技术 高级超低压 CMOS 逻辑器件 高级超低功耗 CMOS 逻辑 高级超低压 CMOS 逻辑器件 低压高带宽总线开关技术 低压转换器总线开关技术 Crossbar 技术 具有下冲保护的 CBT 低压 Crossbar 技术 CMOS 逻辑器件 快速 CMOS 技术 发射接收逻辑器件(GTL+) 高速 CMOS 逻辑器件 与 TTL 电平兼容高速 CMOS 逻辑器件 其电路含 AC、ACT 及 FCT 系列 低压 CMOS 技术 低压 CMOS 技术 低压 CMOS 技术 内部集成电路 内部集成电路 残余连续终结低压逻辑器件

数字电路与逻辑设计第1章数字逻辑电路基础知识

统自动完成,并不需要人们手工去做,学 习汇编语言,就必须了解二进制(还有八 进制/十六进制)。 数制也称计数制,是用 一组固定的符号和统一的规则来表示数值 的方法。人们通常采用的数制有十进制、 二进制、八进制和十六进制。

1.2.1 常用数制的转换

(一)十进制数(D) 十进制计数法是 相对二进制计数法而言的,是我们日常使 用最多的计数方法,如0、1、2、3、4、5 、6、7、8、9共十个数。它的进位原则 是“逢十进一” 它的定义是:“每相邻的两 个计数单位之间的进率都为十”的计数法 则,就叫做“十进制计数法”。

实际上,任意一个十进制数N都可以通过权位展开其 公式形式如下:

式中的任(意NK 一)i 1 0其个表中具示体K任的意表数十示。进第制i 数位N的;基数,它可以是0到9中

1 0 n 其中10表示第 i 的权,每一个数字符号的权

值是基数的为10的不同次幕。

【例1-1】

上面的等式是由十进制数247.76通过 权位展开的形式,称为十进制数的多项 式的表示法。十进制数除了(247.76)

意一个; 2 i 表示第 i 位的权。m、n 均

为整数, 为小数位上的整数, 为整 数位上的整数。

例1-2 ( 1 0 1 1 0 . 1 1 0 ) 2 = 1 2 4 + 0 2 3 + 1 2 2 + 1 2 1 + 0 2 0 + 1 2 - 1 + 1 2 - 2 + 0 2 - 3 = ( 2 2 . 7 5 ) 1 0

数字电路与数字电子技术广泛的应用于电视、

达、通信、电子计算机、自动控制、航天等科 学技术各个领域。

组合逻辑电路简称组合电路,它由最基本

的逻辑门电路组合而成。特点是:输出值只与 当时的输入值有关,即输出由当时的输入值决 定。电路没有记忆功能,输出状态随着输入状 态的变化而变化,类似于电阻性电路,如加法 器、译码器、编码器、数据选择器等都属于此 类。

数字逻辑电路基础知识整理(属于个人笔记)

数字逻辑电路基础知识整理

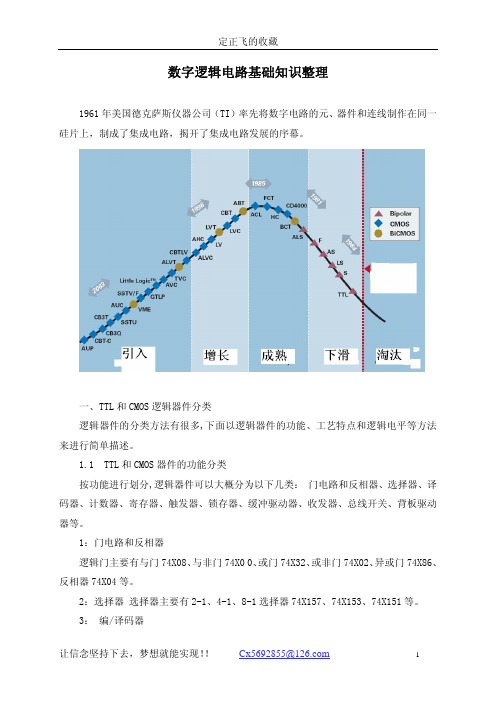

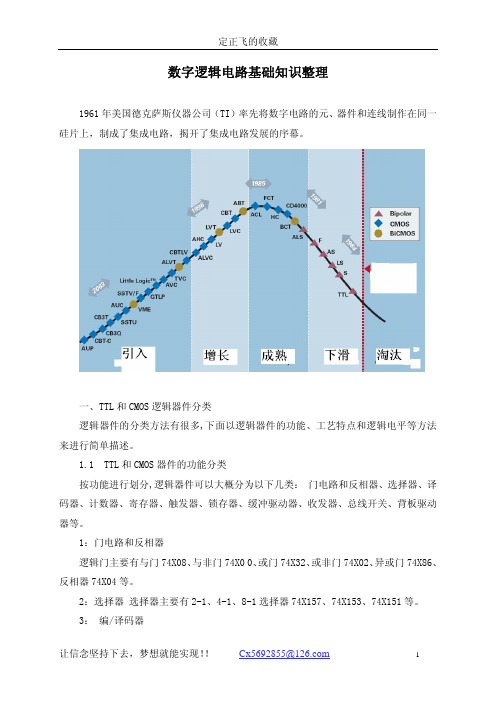

1961 年美国德克萨斯仪器公司(TI)率先将数字电路的元、器件和连线制作在同一 硅片上,制成了集成电路,揭开了集成电路发展的序幕。

一、TTL 和 CMOS 逻辑器件分类 逻辑器件的分类方法有很多,下面以逻辑器件的功能、工艺特点和逻辑电平等方法 来进行简单描述。 1.1 TTL 和 CMOS 器件的功能分类 按功能进行划分,逻辑器件可以大概分为以下几类: 门电路和反相器、选择器、译 码器、计数器、寄存器、触发器、锁存器、缓冲驱动器、收发器、总线开关、背板驱动 器等。 1:门电路和反相器 逻辑门主要有与门 74X08、与非门 74X0 0、或门 74X32、或非门 74X02、异或门 74X86、 反相器 74X04 等。 2:选择器 选择器主要有 2-1、4-1、8-1 选择器 74X157、74X153、74X151 等。 3: 编/译码器

ABTE

高级 BiCMOS 技术/增强型收发器逻辑器件

ALB

高级低压 BiCMOS

ALVT

与 TTL 电平兼容高级低压 CMOS 技术

BCT

BiCMOS 总线接口技术

FB

背板收发器逻辑器件Fra bibliotekGTL

喷射收发器逻辑器件

HSTL

高速收发器逻辑器件

JTAG

JTAG 边界扫描支持

LVT

低压 BiCMOS 技术

SSTL

B.串联阻尼电阻(series damping res istors)

输出端加入串联阻尼电阻可以限流,有助于降低信号上冲/下冲噪声,消除线路振铃,

改善信号质量。如图 6-4 所示。具有此特征的 ABT、LVC、LVT、ALVC 系列器件在命名

中加入了“2”或“R”以示区别,如 ABT 162245,ALVCHR162245。对于单向驱动器件,串

数字逻辑电路基础知识

第一章数字逻辑电路基础知识1.1 数字电路的特点1.2 数制与转换1.3 二进制代码1.4 基本逻辑运算.本章重点1.数字电路的特点2.二进制、十进制、八进制、十六进制的表示3. 二进制、十进制、八进制、十六进制转换4.掌握BCD码编码方法5.了解ASCII码1.1 数字电路的特点数字电路的基本概念1. 数字量与数字信号模拟量:具有时间上连续变化、值域内任意取值的物理量。

例如温度、压力、交流电压等就是典型的模拟量。

数字量:具有时间上离散变化、值域内只能取某些特定值的物理量。

例如训练场上运动员的人数、车间仓库里元器件的个数等就是典型的数字量。

表示模拟量的电信号叫作模拟信号;表示数字量的电信号叫作数字信号。

正弦波信号、话音信号就是典型的模拟信号,矩形波、方波信号就是典型的数字信号。

数字信号通常又称为脉冲信号。

脉冲信号具有边沿陡峭、持续时间短的特点。

广义讲,凡是非正弦信号都称为脉冲信号。

数字信号有两种传输波形,一种称为电平型,另一种称为脉冲型。

010011010电平型信号脉冲型信号2. 数字电路及其优点模拟电路:产生、变换、传送、处理模拟信号的电路数字电路:产生、存储、变换、处理、传送数字信号的电数字电路主要具有以下优点:1)电路结构简单,制造容易,便于集成,成本低。

2)数字电路不仅能够完成算术运算,而且能够完成逻辑运算,因此被称为数字逻辑电路或逻辑电路。

3)数字电路组成的数字系统,抗干扰能力强,可靠性高,稳定性好。

数字集成电路的发展趋势大规模、低功耗、高速度、可编程、可测试、多值化1.2 数制数制1.数制数制:表示数值大小的各种方法的统称。

一般都是按照进位方式来实现计数的,称为进位计数制,简称进位制。

基数:数制中允许使用的数符个数;R进制的基就等于R。

权:处于不同位置上的相同数符所代表的数值大小。

2. 数制转换任意进制数转换为十进制数:按权展开法。

例:将二进制数(1011001.101)2和十六进制数(AD5.C) 16转换为十进制数。

《数字逻辑电路》课程标准

《数字逻辑电路》课程标准一、课程基本信息课程名称:数字逻辑电路学生对象:电子工程、计算机科学等相关专业的本科生课程时长:一学年,每周4小时二、课程目标与内容1. 知识与技能目标:学生应掌握数字逻辑电路的基本原理、概念和设计方法,包括逻辑门、触发器、寄存器、计数器等基本元件,以及数字系统设计、仿真和测试等技能。

2. 过程与方法目标:学生应学会数字逻辑电路的分析和设计方法,通过实践操作培养独立思考和团队协作的能力。

3. 情感态度价值观:培养学生严谨的科研态度,提高逻辑思维能力,增强对数字系统的兴趣和热爱。

三、教学内容与安排1. 数字逻辑电路基础(第1-2周):介绍数字电路的基本概念、分类和特点,以及数字信号和模拟信号的转换原理。

2. 逻辑门电路(第3-4周):讲解基本逻辑门如AND、OR、NOT等的功能和设计,以及CMOS和TTL等不同类型门电路的特点和应用。

3. 触发器和寄存器(第5-6周):介绍触发器和寄存器的原理和应用,包括SR、JK、D等类型,以及它们在数字系统设计中的重要作用。

4. 计数器和其他复杂元件(第7-8周):讲解计数器、移位寄存器、译码器等复杂元件的功能和应用,以及它们在数字系统设计中的组合应用。

5. 数字系统设计(第9-12周):通过实际案例,指导学生进行数字系统设计,包括系统需求分析、方案制定、硬件选择、软件编程等步骤。

6. 课程实验与项目(第13-16周):安排多个实验项目,如设计简单数字系统、制作集成电路等,培养学生动手能力和团队协作精神。

四、教学方法与评估1. 教学方法:采用理论授课、实验操作、项目实践等多种方式,注重实践操作和案例教学。

2. 评估方法:包括平时作业、实验报告、项目成果、期末考试等。

其中,期末考试占50%,平时作业和实验报告占30%,项目成果占20%。

3. 评估标准:根据学生掌握知识和技能的情况,以及在实验和项目中的表现进行评估。

五、教学资源与支持1. 教学资源:提供数字逻辑电路相关教材、实验设备(如集成电路板、实验箱等)、网络资源(如教学视频、论坛等)等。

数字逻辑电路基础知识整理

数字逻辑电路基础知识整理数字逻辑电路是由离散的数字信号构成的电子电路系统,主要用于处理和操作数字信息。

它是计算机和其他数字系统的基础。

以下是一些数字逻辑电路的基础知识的整理:1. 逻辑门:逻辑门是数字电路的基本构建单元。

它们根据输入信号的逻辑关系生成输出信号。

常见的逻辑门有与门、或门、非门、异或门等。

其中,与门输出仅当所有输入都为1时才为1;或门输出仅当至少一个输入为1时才为1;非门将输入信号取反;异或门输出仅当输入中的1的数量为奇数时才为1。

2. 逻辑运算:逻辑运算是对逻辑门的扩展,用于实现更复杂的逻辑功能。

常见的逻辑运算包括与运算、或运算、非运算、异或运算等。

与运算将多个输入信号进行AND操作,返回结果;或运算将多个输入信号进行OR操作,返回结果;非运算对输入信号进行取反操作;异或运算将多个输入信号进行异或操作,返回结果。

3. 编码器和解码器:编码器将多个输入信号转换为较少数量的输出信号,用于压缩信息;解码器则将较少数量的输入信号转换为较多数量的输出信号,用于还原信息。

常用的编码器有优先编码器和BCD编码器,常用的解码器有二进制-十进制解码器和译码器。

4. 多路选择器:多路选择器根据选择输入信号从多个输入信号中选择一个信号输出。

它通常有一个或多个选择输入信号和多个数据输入信号。

选择输入信号决定了从哪个数据输入信号中输出。

多路选择器可用于实现多路复用、数据选择和信号路由等功能。

5. 触发器和寄存器:触发器是存储单元,用于存储和传输信号。

常见的触发器有弗洛普触发器、D触发器、JK触发器等。

寄存器由多个触发器组成,用于存储和传输多个比特的数据。

6. 计数器和时序电路:计数器用于计数和生成递增或递减的序列。

它通过触发器和逻辑门组成。

时序电路在不同的时钟脉冲或控制信号下执行特定的操作。

常见的时序电路有时钟发生器、定时器和计数器。

7. 存储器:存储器用于存储和读取数据。

常见的存储器包括随机存取存储器(RAM)和只读存储器(ROM)。

数字逻辑电路基础入门 第一章

+(1 23+0 22+0 21+1 20) 160]D =(59)H

B—H:以小数点为基准,分别向左、右每 四位分为一组,转换为相应的十六进制数

(11101.011000111) B = (0001 1101 . 0110 0011 1000) B =

( 1

D .

6

3

8

)H

=(1D.638)H

u

t

1. 1

1.1.2

模拟信号与数字信号

数字信号 周期性:Duty Frequency、Period、Pulse

数字信号

bit、bit time、 bit rate比 特率

Width脉宽、 Ratio占空比、Amplitude

非周期性:

正逻辑

Frequency=? Period=? Amplitude=? Pulse width (tw) =? Duty ratio (q) =? 1 0 1 0 1

二、 十、二进制数之间的转换

1. B—D:二进制数按位(权)展开相加 例: (11010.011)2 = 124 +123+022+121+020+ 021+122+123

= (26.375)10

2.D—B 整数和小数部分分别转换,最后相加

整数除二,取出余数再除二,直到商为零 小数乘二,取出整数部分再乘二,直到满足误差要求

(4E6)H= 4162+14 161+6 160 =(1254)D

2.B—H:以小数点为基准,分别向左、右每 四位分为一组,转换为相应的十六进制数

每四位2进 B—H 制数对应 一位16进 制数 (0101 1001)B= [027+1 26+0 25+1 24

数字逻辑大一知识点

数字逻辑大一知识点数字逻辑是计算机科学中的一个重要分支,涵盖了许多大一学生需要学习的知识点。

本文将介绍数字逻辑的一些基础概念,包括逻辑门、布尔代数、半加器和全加器、多路选择器以及寄存器等。

希望能够对大家理解数字逻辑有所帮助。

一、逻辑门逻辑门是数字逻辑中的基本元件,用于进行逻辑运算。

其中包括与门、或门、非门、异或门等。

与门接受两个输入,并且只有当两个输入都为1时,输出才为1;或门接受两个输入,并且只要有一个输入为1,输出就为1;非门接受一个输入,并将输入取反作为输出;异或门接受两个输入,当两个输入相同时,输出为0,当两个输入不同时,输出为1。

二、布尔代数布尔代数是数字逻辑的数学基础,用于描述和分析逻辑运算。

布尔代数包括运算符号、运算规则和公式等。

其运算规则包括交换律、结合律、分配律、吸收律等。

通过布尔代数中的运算,可以对逻辑表达式进行简化和优化。

三、半加器和全加器半加器用于对两个输入进行相加,并给出结果和进位的输出。

全加器是半加器的扩展,可以处理三个输入的相加运算,并给出两个输出,一个是结果,一个是进位。

半加器和全加器在数字电路设计中经常被使用。

四、多路选择器多路选择器用于选择多个输入信号中的一个输出信号。

它拥有一个或多个选择信号,根据选择信号的不同,可以选择不同的输入信号作为输出。

多路选择器在计算机中的数据选择和控制信号选择等方面起到重要作用。

五、寄存器寄存器是一种用于存储和传输数据的数字逻辑元件。

它能够在时钟信号的控制下,根据输入信号的变化将数据存储在其中,并在需要的时候传输出来。

寄存器在计算机的寄存器堆、存储器和高速缓存等方面被广泛使用。

综上所述,数字逻辑是计算机科学中的一门重要课程,其中涉及到的一些基础知识点包括逻辑门、布尔代数、半加器和全加器、多路选择器以及寄存器等。

通过学习这些知识点,大一的学生可以初步了解数字逻辑的基本原理和应用。

希望本文对大家有所帮助,能够更好地理解和掌握数字逻辑。

数字逻辑电路大全PPT课件(2024版)

第6页/共48页

Rb1 4kΩ

Rc 2 1.6kΩ

Vc 2

1

+VCC( +5V) Rc4 130Ω

3

T2 4

1

3

A

31

2T2

D Vo

B

T1

C

Ve 2

1

3

2T 3

Re2

1kΩ

输入级

中间级

输出级

第7页/共48页

2.TTL与非门的逻辑关系

(1)输入全为高电平3.6V时。

T2、T3导通,VB1=0.7×3=2.1(V ),

列。 6 . 74AS 系 列 —— 为 先 进 肖 特 基 系

列, 它是74S系列的后继产品。 7.74ALS系列——为先进低 功耗肖特基系列, 是74LS系列的后继产品。

第30页/共48页

2.3

一、 NMOS门电路 1.NMOS非门

MOS逻辑门电路

VDD (+12V)

VDD (+12V)

VDD (+12V)

0.4V

高 电 平 噪 声 容 限 第1V5页NH/共=48V页OH ( min ) - VON = 2.4V-2.0V =

四、TTL与非门的带负载能力

1.输入低电平电流IIL与输入高电平电流IIH (1)输入低电平电流IIL——是指当门电路的输入端

接低电平时,从门电路输入端流出的电流。

& Vo G0

呈 现 高 阻 , 称 为 高 阻 态 , 或 禁 止 态+V。CC

Rc2

Rc4

Rb1

Vc2 1

3

T2 4

A

&

B

L

EN

数字逻辑电路基础

常用 BCD 码

十进制数 8421 码 余 3 码 格雷码 2421 码

0

0000 0011 0000 0000

1

0001 0100 0001 0001

2

0010 0101 0011 0010

数字逻辑电路基础

第一章 数字逻辑电路基础

1.1 数字电路的基本概念 1.2 数制和码制 1.3 基本逻辑运算 1.4 逻辑函数的表示方法 1.5 逻辑代数运算 1.6 逻辑门电路

1.1 数字电路基本概念

一、模拟信号与数字信号

模拟信号——时间连续数值也连续的信号。如速度、压 力、温度等。 数字信号——在时间上和数值上均是离散的。如电子表 的秒信号,生产线上记录零件个数的记数信号等。 数字信号在电路中常表现为突变的电压或电流。

晶体管工作在开关状 态

1、数字信号的特点

•使用高低电平来表示信号。 •门电路起开关作用。 •逻辑状态只有0,1。 •易于存储。 •抗干扰,对元件的要求不高。 •集成度高,通用性强。

2、用逻辑电平描述的数字波形:

数字波形

逻辑电平对时间的图形表示。 脉冲波: 当某波形仅有两个离散值时。 分为:周期波和非周期波

即:(1234)10=1×103 +2×102+3×101+4×100

又如:(209.04)10= 2×102 +0×101+9×100+0×10-1+4 ×10-

2、二进制

数码为:0、1;基数是2。 运算规律:逢二进一,即:1+1=10。 二进制数的权展开式: 如:(101.01)2= 1×22 +0×21+1×20+0×2-1+1 ×2

数字逻辑电路 (2)

数字逻辑电路引言数字逻辑电路是计算机硬件中的基本组成部分之一。

它由逻辑门和触发器等元件组成,用于处理数字信号,执行各种逻辑运算。

本文将介绍数字逻辑电路的基本原理、常见的逻辑门和触发器,并展示一些典型的数字逻辑电路应用。

数字逻辑电路的基本原理数字逻辑电路是基于二进制系统的逻辑运算电路。

在数字逻辑电路中,二进制数据通过逻辑门的开关操作来实现各种逻辑运算。

逻辑门由晶体管等电子元件构成,通过开关控制传输信号的路径。

数字逻辑电路中最基本的逻辑门有与门、或门和非门。

与门(AND gate)输出高电平仅当所有输入都是高电平时;或门(OR gate)输出高电平当任意一个输入是高电平时;非门(NOT gate)输出与输入相反的电平。

在数字逻辑电路中,不同逻辑门可以组合成更复杂的功能电路。

例如,使用与门、或门和非门可以构建出与非门(NAND gate)和异或门(XOR gate)等。

与非门的输出与与门的输出相反,异或门的输出为其输入的异或结果。

触发器是数字逻辑电路中常用的存储元件。

它可以存储一个比特(bit)的数据,并在特定的时钟信号下改变输出。

触发器常用于存储和传输数据,并实现状态的存储和控制。

常见的逻辑门与门 (AND gate)与门是数字逻辑电路中最基本的逻辑门之一。

它具有两个输入和一个输出。

当且仅当所有的输入信号均为高电平时,与门的输出信号才为高电平。

与门的真值表如下所示:输入1输入2输出000010100111与门的逻辑符号为:A B Output0 0 00 1 01 0 01 1 1或门 (OR gate)或门是另一个常见的逻辑门,也具有两个输入和一个输出。

当任意一个输入信号为高电平时,或门的输出信号为高电平。

或门的真值表如下所示:输入1输入2输出000011101111或门的逻辑符号为:A B Output0 0 00 1 11 0 11 1 1非门 (NOT gate)非门是一个仅具有一个输入和一个输出的逻辑门。

大一数字逻辑电路知识点

大一数字逻辑电路知识点数字逻辑电路是电子工程中的重要基础知识之一。

它涉及电子元件和逻辑门的组合与运算,是计算机科学和电子工程学习的基石。

在大一学习数字逻辑电路时,我们需要掌握一些基本的知识点,包括布尔代数、逻辑运算、逻辑门和多路选择器等。

下面将逐一介绍这些知识点的基本内容。

1. 布尔代数布尔代数是一种数学工具,用于描述逻辑关系。

它包括逻辑运算符(与、或、非)和逻辑常数(真、假),通过这些运算符和常数可以构建逻辑表达式。

在数字逻辑电路中,布尔代数可以用于描述逻辑门的功能和操作。

2. 逻辑运算逻辑运算是布尔代数的基础,常见的逻辑运算有与(AND)、或(OR)、非(NOT)等。

其中,与运算是指同时满足多个条件时结果为真,或运算是指满足任意一个条件时结果为真,非运算是指将输入的逻辑值反转。

3. 逻辑门逻辑门是数字逻辑电路的基本组成单元,它可以实现特定的布尔逻辑功能。

常见的逻辑门有与门(AND)、或门(OR)、非门(NOT)、异或门(XOR)等。

通过将逻辑门进行组合和连接,可以构建出更复杂的数字逻辑电路。

4. 多路选择器多路选择器是一种能根据控制信号选取输入端数据的电路。

它有多个输入通道和一个输出通道,通过控制信号的不同选择,可以将任意输入通道的数据输出。

多路选择器在数字逻辑电路中常用于构建多路复用器、解码器等电路。

5. 数制转换在数字逻辑电路中,我们常常需要进行不同进制之间的转换,包括二进制、十进制、八进制和十六进制。

了解不同数制之间的转换方法可以帮助我们更好地理解和分析数字逻辑电路。

6. 真值表真值表是用于描述布尔函数的一种表格形式。

通过真值表,我们可以清楚地了解输入和输出之间的逻辑关系,并判断逻辑电路的正确性和功能。

在学习数字逻辑电路时,掌握真值表的编写和分析方法是非常重要的。

7. 逻辑代数运算逻辑代数运算是指在布尔代数中对逻辑表达式进行化简和变换的方法。

通过使用逻辑代数运算,我们可以简化复杂的逻辑表达式,减少逻辑门的数量和电路的复杂性,提高电路的性能和可靠性。

数字逻辑电路设计知识点汇总

数字逻辑电路设计知识点汇总数字逻辑电路是电子信息类专业的重要基础课程,它在计算机、通信、控制等领域有着广泛的应用。

下面为大家汇总一下数字逻辑电路设计的主要知识点。

一、数制与编码数制是用来表示数量的规则,常见的数制有二进制、八进制、十进制和十六进制。

二进制是数字逻辑电路中最常用的数制,因为它只有 0 和 1 两个数字,便于用电子器件的导通和截止来表示。

编码则是用特定的代码来表示信息。

例如,BCD 码(Binary Coded Decimal)用四位二进制数来表示一位十进制数;格雷码(Gray Code)相邻两个编码之间只有一位发生变化,常用于减少数字电路中的误差。

二、逻辑代数基础逻辑代数是数字逻辑电路的理论基础,它包括基本逻辑运算(与、或、非)、逻辑函数的表示方法(真值表、逻辑表达式、逻辑图、卡诺图等)以及逻辑函数的化简。

与运算只有当所有输入都为 1 时,输出才为 1;或运算只要有一个输入为 1 ,输出就为 1;非运算则是将输入取反。

逻辑函数的化简是为了得到更简单、更经济的电路实现。

常用的化简方法有公式法和卡诺图法。

三、门电路门电路是实现基本逻辑运算的电子电路,包括与门、或门、非门、与非门、或非门、异或门等。

TTL (TransistorTransistor Logic)门电路和 CMOS (Complementary Metal Oxide Semiconductor)门电路是常见的两种类型。

TTL 门电路速度快,但功耗较大;CMOS 门电路功耗低,但速度相对较慢。

在实际设计中,需要根据具体的性能要求选择合适的门电路类型。

四、组合逻辑电路组合逻辑电路的输出仅取决于当前的输入,没有记忆功能。

常见的组合逻辑电路有编码器、译码器、加法器、数据选择器、数据分配器等。

例如,加法器是实现两个数相加的电路,半加器和全加器是加法器的基本单元。

译码器则是将输入的二进制编码转换为特定的输出信号。

五、时序逻辑电路时序逻辑电路的输出不仅取决于当前的输入,还与电路的过去状态有关,具有记忆功能。

数字逻辑电路教程PPT第2章逻辑门电路

TTL与非门的电压传输特性及 抗干扰能力

CD段(过渡区):

1始也、.3导都TV5管<通处有v, 于I<一T导21、 小通.4V段T状3,、时态TT间,54管管同T开4 时导通,故有很大电流

流TT,电平52管、过T压vO4=T管很RvO054管急电 趋大.3V趋剧阻 于的。于下, 截基饱降止极T2和管到,电导提低输流通供电出,

TTL与非门的电压传输特性及 抗干扰能力

AB段(截止区): vI<0.6V,输出电压vO不

随输入电压vI变化,保持 在高电平VH。 VC1<0.7V,T2和T5管截 止,T3、T4管导通,输出 为高电平,VOH=3.6V。 由于这段T2和T5管截止, 故称截止区。

TTL与非门的电压传输特性及 抗干扰能力

⒉工作原理

当输入端A、B、C中有任一

个输入信号为低电平 (VIL=0.3V)时,相应的发射结 导通,T1工作在深度负饱和 状态,使T1管的基极电位VB1 被箝制在 VB1=VIL+VBE1=0.3+0.7=1V, 集电极电位 VC1=VCES1+VIL=0.1+0.3=0.4V 使T2管截止,IC2=0, VE2=VB5=0V,故T5管截止。

TTL与非门的电压传输特性及 抗干扰能力

CD段(过渡区): 由于vI的微小变化而

引起输出电压vO的急 剧下降,故此段称为 过渡区或转折区。

TTL与非门的电压传输特性及 抗干扰能力

CD段中点对应的输入电压 ,既是T5管截止和导通的分 界线,又是输出高、低电平 的分界线,故此电压称阈值 电压VT(门槛电压), VT=1.4V。

第二章 集成逻辑门电路

集成逻辑门电路,是把门电路的所 有元器件及连接导线制作在同一块 半导体基片上构成的。

大一数字逻辑基础知识点

大一数字逻辑基础知识点数字逻辑是计算机科学与工程中的重要基础知识,它研究的是用来处理和传输数字信息的逻辑系统。

作为计算机科学专业的学生,了解和掌握数字逻辑的基础知识点对于日后的学习和工作都非常重要。

本文将介绍大一学生应该了解的数字逻辑基础知识点,帮助他们在学习过程中更好地理解和应用这些概念。

1. 数字逻辑的基本理论数字逻辑是计算机中的基础,它由布尔代数和逻辑电路两部分组成。

在布尔代数中,常用的逻辑运算包括与、或、非、异或等。

学生需要了解这些逻辑运算的定义、真值表和基本性质。

逻辑电路是基于布尔代数的实际应用,它由门电路和触发器等组件构成。

学生需要了解常见的门电路类型(如与门、或门、非门等)以及它们的真值表和符号表示。

2. 数字系统数字逻辑是用来处理数字信息的,因此了解不同的数字系统是非常重要的。

常见的数字系统包括二进制、十进制、八进制和十六进制系统。

学生需要了解这些数字系统的表示方法、转换规则以及它们在计算机中的应用。

3. 逻辑函数和逻辑表达式逻辑函数描述了输入和输出之间的关系,它是数字逻辑中的重要概念。

学生需要了解不同逻辑函数的定义和常见的逻辑运算符(如与、或、非、异或等)在逻辑函数中的应用。

逻辑表达式是逻辑函数的一种表示形式,学生需要了解逻辑表达式的表示方法和计算规则。

4. 组合逻辑电路组合逻辑电路是由逻辑门组成的电路,它的输出只取决于当前的输入状态。

学生需要了解组合逻辑电路的基本原理,包括逻辑门的连接方式、逻辑表达式的转换、卡诺图的应用等。

5. 时序逻辑电路时序逻辑电路是由触发器组成的电路,它的输出不仅取决于当前的输入状态,还取决于过去的输入状态。

学生需要了解时序逻辑电路的基本原理,包括触发器的工作原理、时钟信号的作用、状态转换图的应用等。

6. 存储器和寄存器存储器和寄存器是计算机中用来存储数据的重要组件。

学生需要了解不同类型的存储器(如随机存取存储器和只读存储器)的特点和应用,以及寄存器在计算机中的作用和用法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

。

A.强制位电平在Sa时有效B.强制位电平在S0时有效

C.预置位电平在Sa时有效D.预置位电平在Sa+1时有效

10、4LS169为一个同步四位二进制可逆计数器,有下列说法成立。

A.置输入信号UP/DN= 0,则为加1计数;

B.置输入信号UP/DN= 0,则为减1计数;

C.Rco仅为进位信号;

D.计数器不能用跳跃的方法实现任意模数的计数。

四、讨论函数。

1.写出函数F的反函数。

F = AB +(A + C)(C + DE)

2.写出函数G的最小项表达式。

G = AC + BC + B(AC +AC)

3.化简函数P为最简与或式。

P ( A, B, C, D ) = ∑m( 0,5,8,13,14,15 ) + ∑d( 2,9,10,12 )

4.写出当输入无反变量时函数Q的与非~与非表达式。

Q ( A, B, C, D ) = ∑m( 0,1,6,10,11,14 ) + ∑d( 4,8,12,15 )

5.若函数F=A ( B + C ) (A + B + C)( A B C),则写出函数F的最简与或式和最简或与式。

6.在时序电路的设计中,挂起问题是由于什么原因引起的?为了使电路具有“自恢复”功能,即能使电路在有限个节拍中进入到什么状态,就解挂?设计解挂的关键步骤是什么?

(XY)(XZ)(YZ)

三、单选题

1.A2.D3.B4.C5.B6 C7.A8.A9.C10B

四、讨论函数

1.F=(/A+/B)(A/C+/C(/D+E))

2.G=∑m( 1,5,7)

3.P=/B/D+AB+B/CD

4.Q=/{[/A/C·/(BD)][AC·/(BD)][BC·/(BD)]}

5.F=A+/(/BC)=(A+C)(A+/B))

20.( )比较器74LS86采用超前比较电路,旨在提高电路速度。

二、填空题

1.在数制转换中,二进制数1100010001对应的十进制数是__________,对应的十六进制数是__________,十进制数2010.621对应的二进制数是___________。

2.若x = +120,y = +72,则用8位二进制数代码表示:[x-y]反=________+________=________;[y-x]补=_______+________=________。

2.01111000,10110111,00110000;10010000,10001000,

11010000

3.684,100110110111,11010000100

4.100,1101

5.1,0,/A/B+AB,1,/A/B+AB,0

6.m(3,4,5,6,7,11)

7.最小覆盖,1,0

8.传递性,(BC),不具有传递性,

7.为什么用4位二进制加法器74LS283实现两个1位BCD码加法运算时,结果(也是BCD码)需要做修正?修正的具体过程是什么?

8.试说明脉冲异步时序电路输入信号x不允许出现的情况是什么?

9.若F1=∑m3(3,5,7),F2=∑m3(1,3,5,6),F3=∑m3(1,3,5,6,7),则:

⑴写出如下函数的标准与或式:F4=F1+F2,F5=F1•F2,F6=F1的反函数

11.( )根据Gray码的特点,其相邻码的特点是在n位二进制Gray码中只能有一位不同。

12.( )任意两个最小项之和为1。

13.( )R-S锁存器是带有约束条件的双稳态元件。

14.( )函数F的标准或与式是将其最小项用逻辑或运算组成的表达式。

15.( )二进制正数的原码、反码和补码的三种表示都是相同的。。

5.()在带符号数的代码表示中,符号位是用“0”或“1”表示的。

6.()超前进位加法器比行波加法器要简单。

7.()逻辑约定是说明逻辑电路中信号的物理量(即逻辑电平)与逻辑状态表示之间的关系。

8.()一个触发器必须有两个稳定状态,可以表示两位二进制码。

9.()简单PLD是由与阵列和或阵列构成的。

10.()数字系统由控制单元和信息处理单元组成。

C.共有6个相邻最小项D.m4、m21、m13、m38是它的相邻项

7.在状态化简中,判断状态等效与状态相容时不同点是_________。

A.传递性B.次态应满足的条件

C.隐含表的作用D.最大等效类与最大相容类的的确定

8.使触发器呈计数状态的控制函数是。

A.J = K = 1B.D = QC./S = Q,/R = QD.T =0

=_________,AB·+A⊙B=( AB+AB)·(_______)=_______。

6.有逻辑函数F = (AB+ABD)(B+CD),则属于使函数F为1的最小项是。

7.一般无关项在卡诺图上用“d”标注出来,它们可以参与到函数F的,当它们被圈入到F的卡诺圈时,取值为,而当它们没有被圈入到F的卡诺圈时,取值为。

6.多余状态,多余状态的次态为有效状态,参考教材P191例3的解挂讨论

7.因为74LS283是模16加法器,而两个1位BCD码加法运算是模10加法,所以运算结果要修正,修正的算法参考教材P163例1的校正表(P164)和电路(P165)。

8.输入信号x不允许在两根或两根以上输入线上同时有输入信号和前一个输入引起状态变化未稳定前下一个输入达到的情况。

输入为2421码ABCD,输出为余3码Y3Y2Y1Y0

的码制转换电路。

九、

D2=y1, D1=y0,D0=y2⊕y0;y2n+1=y1, y1n+1=y0,y0n+1=y2⊕y0

模7计数,001→011→111→110→101→010→100→001→…;有挂起,000→000;

解挂:000→001, My=/y2/y1/y0,D0=y2⊕y0+My=y2⊕y0+/y2/y1/y0

A.[x]原= 100000B.[x]反= 100001

C.[x]补= 101111D.[x]补= 110000

3.奇偶校验码满足___。

A.能纠错的要求B.发现单错的能力

C.对码的位序有特定要求D.传输正确的代码的校验和必为零

4.在n变量的逻辑函数F中,有___。

A.若mi为1,则Mi也为1B.若F所有mi为0,则F为1

9.⑴F4=∑m(1,3,5,6,7),F5=∑m(3,5),F6=∑m(0,1,2,4,6)

⑵F1与F3互为对偶函数

五:

F = A/B+/BC+D

六、

Y3=0当<5

Y3=1当≥5

七、

八、

Y3= A,Y2=/AB +/AC +/AD + BCD,Y1=/A/C/D+ A/CD + /ACD + AC/D,Y0=/D

十五、某电路的状态图如下所示,试分析这个状态图是不是最简状态图T 4.T 5.T 6.F 7.T 8.F 9.T 10.T

11.T12.F13.T14.F15.T16.F 17.T 18.T 19.F 20.T

二、1.785,311,11111011010.1001

十一、已知函数F=A+B+C+D+(A⊕B⊕C⊕D),试设计实现函数F的电路(请采用多路选择器74LS151)。

十二、试化简如图所示完全确定的原始状态表。

十三、试用4位二进制加法器74LS283和若干逻辑门设计将两个一位余3码相加的加法电路(结果也是余3码表示)。

十四、试分析如图所示电路的功能,画出波形图。

⑵判断以上F1~F3中,哪两个函数互为对偶函数。

五、分析如下图所示逻辑电路,先写出输出函数F的表达式,并画出F的卡诺图,最后用多路选择器74LS151实现函数F。

六、已知电路输入为余3码Y3~Y0,要求:当输入小于5时,输出为输入数加0010,否则输出为输入数加0110。试用4位二进制加法器74LS283及若干逻辑门实现该电路。

C.若F所有Mi为1,则F为1D.F的任一最小项标记为mni( i = 1~2n)

5.输入无反变量函数F的化简,讨论的是___。

A.函数F的标准与或式B.用禁止逻辑法寻找F的共享禁止项

C.函数F中不能出现非运算D.在F的卡诺图上所有的质蕴涵

6.符合六变量m5的相邻最小项,有下列说法成立。

A.共有5个相邻最小项B.m0、m4、m7、m13是它的相邻项

16.( )最大等效类要经过覆盖性和闭合性的讨论后才能确定。

17.( )在一个数字系统中,控制单元发出控制操作序列,信息处理单元按照这个的控制序列执行相应的操作。

18.( )由n个触发器构成的计数器,其计数模值的范围是m(2≤

m≤2n)。

19.( )同步与异步时序电路的根本区别在于其电路中各触发器的控制端的输入信号设置不同。

十、

十一、

十二、

8.等效状态具备_________,如果满足( A, B )、( A, C ),则有_________;而相容状态_________,如果要( X, Y, Z )成立,则必须满足_________。

三、单选题

1.一个最大4位的十进制数转换成二进制数,至少需要_位。

A.12B.10C.9D.7

2.当x=-10000时,则有___。

3.2421码110011100100对应的十进制数是_______,对应的余3码是______,对应的BCD码是_______。

4.若收到的海明码是1101110,则校验和S3S2S1是______,应所传送的信息位B4B3B2B1是________。