移位寄存器功能测试及应用

实验8移位寄存器逻辑功能测试及应用

实验8移位寄存器逻辑功能测试及应用一、实验目的1.了解移位寄存器的基本原理及逻辑功能。

2.掌握移位寄存器的逻辑功能测试方法。

3.学会使用移位寄存器进行逻辑功能的实际应用。

二、实验器材数字逻辑实验箱、示波器、连接线。

三、实验原理移位寄存器是一种能够存储和移动数据的逻辑电路。

它由多个触发器组成,每个触发器都与相邻的触发器连接,形成环形结构。

移位寄存器中的数据可以通过输入口输入,通过时钟信号控制触发器的状态变化,从而实现数据的移动。

移位寄存器有三种基本的逻辑功能:1.移动功能:数据可以向左或向右移动一个位置。

2.并行转移功能:数据可以从一个移位寄存器转移到另一个移位寄存器。

3.并行加载功能:可以将数据同时加载到多个触发器中。

四、实验步骤1.按照实验电路图连接实验电路。

将四个LED灯分别连接到74LS194寄存器的Q0、Q1、Q2、Q3输出端,将四个开关分别连接到74LS194寄存器的A、B、C、D输入端。

将实验箱提供的方波电压输入到74LS194寄存器的CP时钟输入端。

2.打开示波器,并将示波器的探头连接到74LS194寄存器的CP时钟输入端。

3.调整示波器的时间基准,使波形在示波器的显示屏上能够清晰可见。

调整示波器的垂直放大倍数,使波形的幅度适中。

4.分别将开关1、2、3、4打开或关闭,观察LED灯的亮灭情况,并观察示波器上的波形变化。

五、实验结果分析根据实验步骤中的操作,可以得到如下运行结果:1.当开关1打开时,移位寄存器内的数据向右移动一个位置,即Q3→Q2→Q1→Q0→Q3、LED灯的亮灭情况和示波器上的波形变化均符合预期,实验成功。

2.当开关2打开时,移位寄存器内的数据向左移动一个位置,即Q0→Q3→Q2→Q1→Q0。

LED灯的亮灭情况和示波器上的波形变化均符合预期,实验成功。

3.当开关3打开时,移位寄存器内的数据从最右端向左移动一个位置,即Q3→Q3→Q2→Q1→Q0。

LED灯的亮灭情况和示波器上的波形变化均符合预期,实验成功。

实验六 寄存器及应用

实验六 移位寄存器及应用一、实验目的1、了解并掌握四位单向、双向移位寄存器的逻辑功能;2、熟悉移位寄存器的基本使用方法。

二、实验器材和仪器设备 1、实验仪器设备(1)DLC —1数字电子技术实验箱 (2)万用表2、实验器件:74LS194、74LS04、74LS20 等 三 实验原理1、在数字系统中能寄存二进制信号,并进行移位的逻辑部件称为移位寄存器。

根据移位输入和输出信号的方式有:串入串出、串入并出、并入串出、并入并出四种形式,按移位方向有左移、右移两种。

2、集成双向移位寄存器集成移们寄存器的种类很多,现以典型芯片74194为例来介绍其逻辑功能。

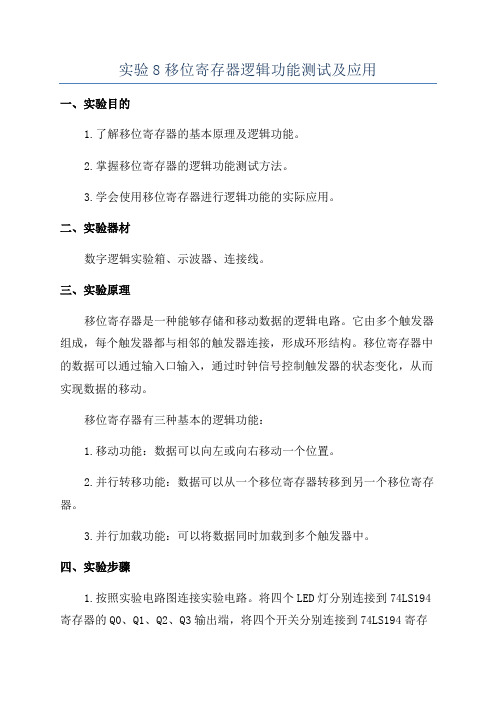

下图是74LS194芯片,它有16个引脚。

其功能真值表如表所示。

图5-3 四位双向移位寄存器74194引脚图R C :异步清零端; CP:时钟送数脉冲输入端; S 1S 0 :控制方式选择端, S R :右移串行输入数据端; S L :左移输入端。

Q 3:右移串行输出端;Q 0:左移串行输出端。

D 0-D 3:并行输入;Q 0-Q 3:并行输出。

表5-2 74194双向移位功能表........① 清0功能。

当CR =0时,双向移位寄存器置0。

Q 0-Q 3 都为0状态。

② 保持功能。

当CR =1、CP= 0或1 CR 、S 1S 0 =00时,双向移位寄存器保持原状态不变。

③ 并行送数功能。

当CR =1、S 1S 0 =11时,在CP 上升沿作用下,使D 0-D 3 端输入的数码d 0-d 3并行送入寄存器,显然是同步并行送数。

④ 右移串行送数功能。

当CR =1、S 1S 0 =01时,在CP 上升沿作用下,执行右移功能,D SR 端输入的数码依次送入寄存器。

⑤ 左移串行送数功能。

当CR =1、S 1S 0 =10时,在CP 上升沿作用下,执行左移功能,D SL 端输入的数码依次送入寄存器。

四、实验内容1.验证74LS194 双向移位寄存器的逻辑功能(70分)D 0、D 1、 D 2、D 3分别接数据开关K 1、K 2、K 3、K 4。

移位寄存器及其应用实验报告

移位寄存器及其应用实验报告1. 背景在数字电路中,移位寄存器是一种常见的基本电路元件。

它可以将输入数据按照一定规则进行移位操作,并输出处理后的数据。

移位寄存器通常由触发器构成,分为串行移位寄存器和并行移位寄存器。

在实际应用中,移位寄存器常用于数据存储、数据传输、脉冲发生器等方面。

本实验旨在通过设计移位寄存器电路及其应用电路的实验,加深对移位寄存器工作原理的理解,掌握其应用。

2. 实验目的1.了解移位寄存器的基本原理;2.学会设计移位寄存器电路及其应用电路;3.掌握移位寄存器的应用方法。

3. 实验原理与方法3.1 移位寄存器原理移位寄存器将输入数据按照一定规则进行移位操作,并输出处理后的数据。

常见的移位规则包括:左移、右移、循环左移、循环右移等。

移位寄存器通常由触发器构成,触发器的状态决定了寄存器中存储的数据。

本实验主要探究两种常用的移位寄存器:串行移位寄存器和并行移位寄存器。

3.1.1 串行移位寄存器串行移位寄存器中,数据是按照位的顺序逐个进行移位的。

串行移位寄存器可以通过级联多个D触发器实现,每个D触发器的输出与下一个D触发器的输入相连。

3.1.2 并行移位寄存器并行移位寄存器中,数据的位同时进行移位。

并行移位寄存器可以通过级联多个D 触发器实现,每个D触发器的输入都与移位数据的对应位相连。

3.2 实验所用材料与方法3.2.1 材料•移位寄存器芯片•发光二极管(LED)•电路连接线3.2.2 方法1.实验预备:准备实验所需的移位寄存器芯片、LED和电路连接线。

2.按照移位寄存器原理,设计移位寄存器电路并进行布线连接。

3.使用示波器检查电路的正确性。

4.进行实验验证,观察移位寄存器的运行情况,并记录实验结果。

4. 实验结果与分析本实验设计了一个4位串行移位寄存器电路,并进行了验证实验。

首先,按照原理部分的描述,我们选择了一个基于D触发器的4位串行移位寄存器芯片。

通过连接四个D触发器,将其串联起来,即可构成一个4位的串行移位寄存器。

移位寄存器实验报告结果

一、实验目的本次实验的主要目的是通过搭建移位寄存器实验电路,验证移位寄存器的逻辑功能,并了解其在数字系统中的应用。

实验内容包括:移位寄存器的基本原理、实验电路搭建、实验现象观察和结果分析。

二、实验原理移位寄存器是一种具有移位功能的寄存器,它可以实现数据的串行输入和串行输出。

在时钟脉冲的作用下,移位寄存器中的数据可以依次左移或右移。

根据移位寄存器存取信息的方式不同,可分为串入串出、串入并出、并入串出、并入并出四种形式。

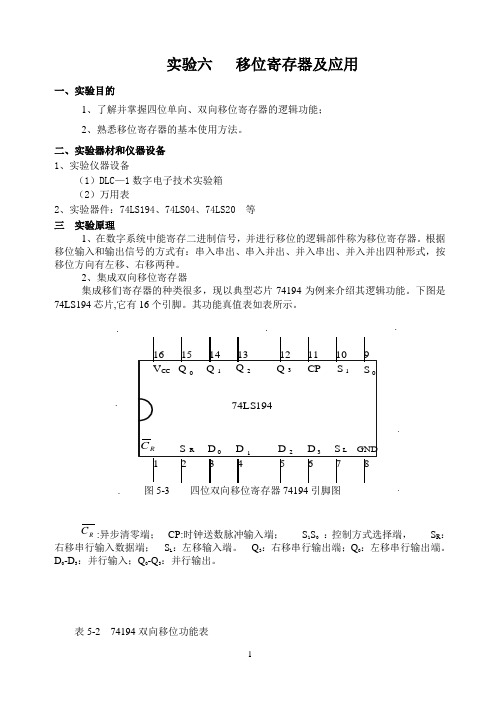

本实验选用的是4位双向通用移位寄存器,型号为74LS194或CC40194。

74LS194具有5种不同操作模式:即并行送数寄存、右移、左移、保持及清零。

其逻辑符号及引脚排列如图1所示。

图1 74LS194的逻辑符号及其引脚排列三、实验电路搭建1. 电路元件准备:74LS194芯片、电阻、电容、二极管、连接线等。

2. 电路搭建:按照图1所示,将74LS194芯片的引脚与电阻、电容、二极管等元件连接,形成移位寄存器实验电路。

3. 电源连接:将电源正负极分别连接到电路板上的VCC和GND端。

四、实验现象观察1. 实验现象一:串行输入,并行输出。

(1)将74LS194的SR端接地,SL端接高电平,S1、S0端接高电平,CR端接地。

(2)使用串行输入端输入数据,观察并行输出端的数据变化。

(3)实验现象:当输入串行数据时,并行输出端依次输出对应的数据。

2. 实验现象二:并行输入,串行输出。

(1)将74LS194的SR端接地,SL端接高电平,S1、S0端接低电平,CR端接地。

(2)使用并行输入端输入数据,观察串行输出端的数据变化。

(3)实验现象:当输入并行数据时,串行输出端依次输出对应的数据。

3. 实验现象三:左移、右移操作。

(1)将74LS194的SR端接地,SL端接高电平,S1、S0端分别接高电平和低电平,CR端接地。

(2)观察移位寄存器中的数据在时钟脉冲的作用下左移或右移。

(3)实验现象:在时钟脉冲的作用下,移位寄存器中的数据依次左移或右移。

移位寄存器功能测试及应用

实验八移位寄存器功能测试及应用一、实验目的:1.掌握中规模4位双向寄存器逻辑功能及使用方法。

2.熟悉移位寄存器的应用,实现数据的串行、并行转换和构成环形计数器二、实验仪器及材料a) TDS-4数电实验箱、双踪示波器、数字万用表。

b) 参考元件:74LS194一片。

三、预习要求及思考题1.预习要求:1) 复习有关寄存器有关内容。

2)熟悉74LS194逻辑功能及引脚排列。

3)用multisim软件对实验进行仿真并分析实验是否成功。

2.思考题:1) 使寄存器清零,除采用输入低电平外,可否采用右移或左移的方法?可否使用并行送数法?若可行,如何进行操作?2) 环行计数器的最大优点和缺点是什么?四、实验原理1.位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。

既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。

根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。

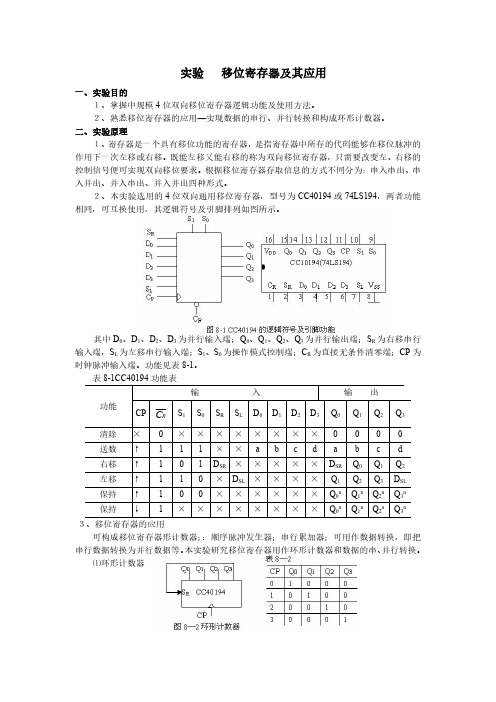

本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚图如图8-1所示。

图8-1 74LS194的逻辑符号图及引脚功能图.其中D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;S R为右移串行输入端;S L为左移串行输入端;S0、S1为操作模式控制端;C R为直接无条件清零端;CP为时钟脉冲输入端。

74LS194有5种不同操作模式:即并行送数寄存,右移(方向由Q0-->Q3),左移(方向由Q3→Q0),保持及清零。

S1、S0和C R端的控制作用如表8-12、移位寄存器应用很广,可构成移位寄存器型计数器:顺序脉冲发生器;串行累加器;可用数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。

本实验研究移位寄存器用作环形计数器和数据的串、并行转换。

实验九 移位寄存器及其应用

实验九移位寄存器及其应用一、实验目的1.掌握中规模四位双向移位寄存器的逻辑功能2.熟悉移位寄存器的应用——实现数据的串行-并行转换和构成环形计数器二、实验设备及器件1.数字电路实验箱2.74LS194(CC40194)×2,CC4011(74LS00),CC4068(74LS30)三、实验内容及步骤1.测试74LS194的逻辑功能按图9-5接线,CR、S1、S0、S L、S R、D0、D1、D2、D3、Q0、Q1、Q2、Q3分别接至逻辑电平显示器的输入插口,CP接单次脉冲源。

按表9-5测试(1)清零令CR=0,其它输入为任意状态,这时寄存器输出Q0、Q1、Q2、Q3应均为零(2)送数令1CR,S0=S1=1,送入任意四位二进制数,如D0D1D2D3=abcd,加CP脉冲,观察CP=0、CP由0→1、CP由1→0三种情况下寄存器输出状态的变化,观察寄存器输出状态变化是否发生在CP脉冲上升沿(3)左移令1CR、S1=0、S0=1,由右移串行输入端S L送入二进制数码如1111,=由CP端连续加四个CP脉冲,观察输出端情况,记录之(4)右移令1CR、S1=0、S0=1,由右移串行输入端S R送入二进制数码如0100,=连续加四个CP脉冲,观察输出,记录之(5)保存寄存器预置任意四位二进制数码abcd,然后令1CR、S1=S0=0,加=CP脉冲,观察输出,记录之表9-52、环行计数器自拟实验线路用并行送数法预置寄存器为某二进制数(如0100),然后进行右移循环,观察寄存输出,记入表9-6中表9-63、实现数据的串行-并行转换(1)串行输入-并行输出按图9-3接线,进行右移串入-并出实验,串入数码自定;改接线路用左移方式实现并行输出。

自拟表格,记录之(2)并行输入-串行输出按图9-4接线,进行右移并入-串出实验,并入数码自定。

再改接线路用左移方式实现串行输出。

自拟表格,记录之。

实验6移位寄存器及其应用

实验六 移位寄存器及其应用一、实验目的1、 掌握移位寄存器功能的测试方法2、 掌握4位双向移位寄存器的逻辑功能 二、实验仪器及设备1、 EEL-II 型电工电子实验台2、 集成器件74LS194 三、实验内容1、 在数字实验箱中插入74LS194,按图6.1接线V CC S 1S 0D SR A D SL B C D GNDQ A Q B Q C Q DCRCP逻辑电平显示器数 据 开 关+5v复位按钮SB单次脉冲74LS194图6.1 74LS194管脚排列图和逻辑功能测试图2、 接线完毕,检查无误后,进行基本功能测试 复位:CR =0,电路复位,Q A Q B Q C Q D =0000 保持:CR 非=1,S 1=S 0=0,Q A ~Q D 状态不变使CR =1,S 1、S 0(工作状态控制端)任意,CP=0或CP=1,则Q A ~Q D 状态也不变表6.1 74LS194双向4位移位寄存器功能表并行置数:置CR=1,S1=S0=10,数据输入端DCBA置为0101,输入单次脉冲,则Q D Q C Q B Q A=0101,如果改变DCBA数据,再按单次脉冲,新数据将置入。

右移位:置CR=1,S1=0,S0=1,D SR=1,D SL=*,输入单次脉冲,则Q A=1,Q B=Q An,Q C=Q Bn,Q D=Q Cn左移位:置CR=1,S1=1,S0=0,D SR=*,D SL=1,输入单次脉冲,则Q D=1,Q C=Q Dn,Q B=Q Cn,Q A=Q Bn3、循环右移应用如将上图中的D SR端接到Q D端,并将寄存器Q D~Q A置为1000,且满足右移条件,在寄存器会右移一个“1”,每4个时钟脉冲完成一次循环。

4、用74LS194组成8位移位寄存器原理如图6.2所示。

逻辑状态显示器图6.2 用74LS194组成8位移位寄存器原理图四、实验报告整理各项测试结果。

实验 MSI移位寄存器及其应用 (2)共30页

例1:用CT1195构成M=4 的环形计数器

态序表

Q0

Q1

Q2

Q3

1

0

0

0

0

1

0

0

0

0

1

0

0

0

0

1

环形计数器

注意:

1 电路除了有效计数循环外, 还有五个无效循环

2 不能自启动

3 工作时首先在SH/LD加启动 信号进行预置

扭环形计数器设计

CT74194功能表

输

入

R CP DSR D0 …… D3 MB MA DSL

0φ φ φ φ φ φ φ

1 0φ φ φφ φ φ

1 ↑ φ d0 …… d3 1 1 φ 1 ↑1 φ φ0 1 φ

1 ↑0 φ φ0 1 φ

1 ↑φ φ φ1 0 1

1 ↑φ φ φ1 0 0

1 φφ φ φ0 0 φ

四位双向移位寄存器(P243)1个

三三输入或非门

1个

四二输入与非门(P241) 1个

二四输入与非门(P242) 1个

74LS27管脚图

引脚

3 4 5 6

1 2 13 12

9 10 11 7 GND 14 Vcc

8

四、实验任务

P114任务2,3,4

串——并转换

(1)0011低位在前DSL (2)0111高位在前DSR

实验五 MSI移位寄存器及其应用

一、实验目的

1、掌握中规模集成电路移位寄存 器原理及逻辑功能。 2、学习移位寄存器的灵活应用。

二.实验原理

概念:具有移位功能的寄存器,即指寄 存器中所存代码能够在移位脉冲作用下 依次左移或右移。

实验七---移位寄存器及其应用

集成移位寄存器74LS194功能表:

附:74LS194引脚图

四、实验内容

1、测试四位双向移位寄存器74LS194的逻 辑功能:(测试数据记录表5中)

(1)清除功能 (2)送数功能 (3)右移、左移功能 (4)保持功能 注:CR、S1、S0、SL、SD以及D0-D7分别

接数据开关,CP接逻辑开关,Q0-Q7接发 光二极管显示器。

2、根据实验内容2的结果,画出4 位 环形计数器的状态转换图及波形图。

3、分析串/并行、并/串行转换器所 得结果的正确性。

实验七、移位 寄存器

一、实验目的

1、掌握中规模4位双向移位寄存 器的逻辑功能及使用方法。

2、掌握移位寄存器的典型应用。 3、熟悉移位寄存器的调试方法。

二、实验设备

1、电子技术实验箱

一台

2、数字示波器

一台

3、数字万用表

一块

4、芯片:74LS194*2、74LS00

三、理论准备

移位寄存器是一种由触发器链 型连接的同步时序网络 ,每个 触发器的输出连到下一级触发 器的控制输入端,在时钟脉冲 作用下,存贮在移位寄存器中 的信息逐位左移或右移。

2、环形计数器:自拟实验电路及数据 记录表格。

3、实现数据的串/并转换:按图3、图 4连接电路,输入数码自定,自拟记录 表格。

注:串行输入/并行输出及并行输入/ 串行输出转换电路中只做右移部分; 改接电路,用左移方式的内容放在实 验报告中完成(画出电路图)

波形图:

五、实验报告要求

ห้องสมุดไป่ตู้、分析表5的实验结果,总结移位寄 存器的逻辑功能,并写入表格总结功 能一栏中。

移存器功能测试及应用

移存器功能测试及应用一、实验目的1、熟悉移位寄存器(移存器)的电路结构和工作原理。

2、掌握D触发器74HC(LS)74及集成移位寄存器74HC(LS)194的逻辑功能和使用方法。

3、了解简单数字系统实验、调试及故障排除方法。

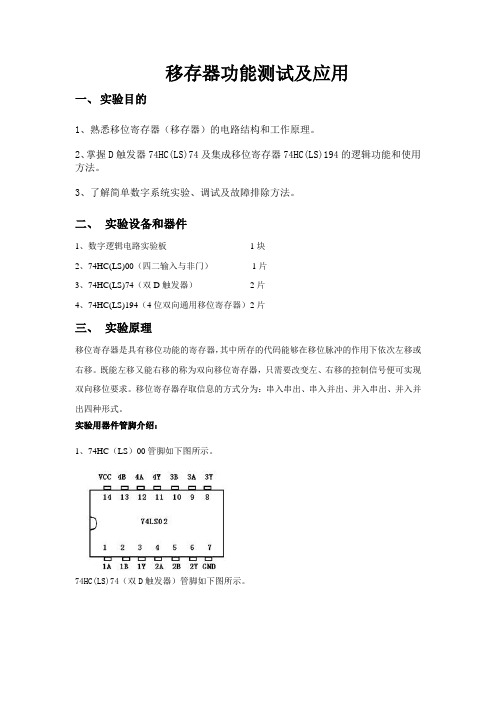

二、实验设备和器件1、数字逻辑电路实验板1块2、74HC(LS)00(四二输入与非门)1片3、74HC(LS)74(双D触发器)2片4、74HC(LS)194(4位双向通用移位寄存器)2片三、实验原理移位寄存器是具有移位功能的寄存器,其中所存的代码能够在移位脉冲的作用下依次左移或右移。

既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。

移位寄存器存取信息的方式分为:串入串出、串入并出、并入串出、并入并出四种形式。

实验用器件管脚介绍:1、74HC(LS)00管脚如下图所示。

74HC(LS)74(双D触发器)管脚如下图所示。

2、74HC(LS)194(4位双向通用移位寄存器)管脚如下图所示。

四、实验内容与步骤1、利用两块74HC(LS)74(四个D触发器)构成一个单向的移位寄存器(基本命题)参照用两块74HC(LS)74(四个D触发器)构成一个单向移位寄存器的实验电路图连接电路,Q输出依次接LED指示灯,加电后在移位输入端加入不同信号观察LED指示灯变化。

置1电路图置0电路图※实验结果:置0时,LED灯依次变亮;置1时,LED灯依次熄灭。

※实验中出现的问题:LED灯的变化不是依次进行,而是同时点亮、同时熄灭。

※解决方法:重新接线,确认所用每一根导线没有问题;排查电路,确认接线没有问题;替换元件,解决问题。

产生问题的原因是由于两个74元件不是相同型号。

2、测试74HC(LS)194的功能(基本命题)例如,Q输出依次接LED指示灯,改变S1、S0的值配合其它输入观察LED的变化。

※实验结果:置数:LED显示状态与置数端相同。

左移:LED从下往上(QD到QA)依次变亮。

移位寄存器及其应用

实验移位寄存器及其应用一、实验目的1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。

2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。

二、实验原理1、寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下一次左移或右移。

既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。

根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。

2、本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图所示。

其中D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;S R为右移串行输入端,S L为左移串行输入端;S1、S0为操作模式控制端;C R为直接无条件清零端;CP为时钟脉冲输入端。

功能见表8-1。

表8-1CC40194功能表功能输入输出CP R C S1S0S R S L D0D1D2D3Q0Q1Q2Q3清除×0××××××××0000送数↑111××a b c d a b c d右移↑101D SR×××××D SR Q0Q1Q2左移↑110×D SL××××Q1Q2Q3D SL保持↑100××××××Q0n Q1n Q2n Q3n保持↓1××××××××Q0n Q1n Q2n Q3n3、移位寄存器的应用可构成移位寄存器形计数器;:顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据等。

实验三移位寄存器及其应用

CR

Q0' Q1' Q2' Q3'

M1

O

CT74LS194(2) M0

1

DSR CR D0 D1 D2 D3 DSL

X

X XX X

13进制扭环 计数器及其 状态转换表

双向移位寄存器设计

工作原理:

当X=1时,M1=0, M0=1,执行右移功能;

n=3,其模值 M=2×3=6;

当X=1时,M1=1, M0=0,执行左移功能。

说明 置零

1 × × 0 × × ××××

保持

111 101

× × d0 d1 d2 d3 d0 d1 d2 d3 并行置数

× 1 × × × × 1 Q0 Q1 Q2 右移输入1

101

× 0 × × × × 0 Q0 Q1 Q2 右移输入0

110

1 × × × × × Q1 Q2 Q3 1 左移输入1

辑功能、管脚排列及其各种应用方法。 ❖ 设计出实验要求的电路图……

74LS194构成的顺序脉冲发生器及其波形

74LS194构成的七进制扭环形计数器 74LS194构成的六进制扭环形计数器 请根据移位原理,自行推导其工作过程,

移位寄存器的级联

&

Q0 Q1 Q2 Q3

M1

O

CT74LS194(1) M0

1

DSR CR D0 D1 D2 D3 DSL

X

CP

X XX X

❖ 时间安排: ❖ 讲授: ❖ 实验用时: ❖ 随堂考试准备时间: ❖ 考试时间:

20分钟 40分钟 30分钟 50分钟

四、思考题

❖ 顺序脉冲发生器可用于流水灯控制吗?有什 么区别?

❖ 若设计M=20的扭环形计数器,需要几片 74LS194?如何连接?

7 移位寄存器及其应用

实验七 移位寄存器及其应用一、实验目的:1.掌握中规模4位双向移位寄存器的逻辑功能及使用方法。

2.熟悉移位寄存器的应用——实现数据的串/并转换、构成环形计数器和扭环型计数器。

二、实验原理:寄存器是计算机和其它数字系统中用来存储代码或数据的逻辑部件。

它的主要组成部分是触发器。

一个触发器能存储1位二进制代码,所以要存储n 位二进制代码的寄存器就需要用n 个触发器组成。

把若干个触发器串接起来,就可以构成一个移位寄存器。

移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。

既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。

根据移位寄存器在存取信息时的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。

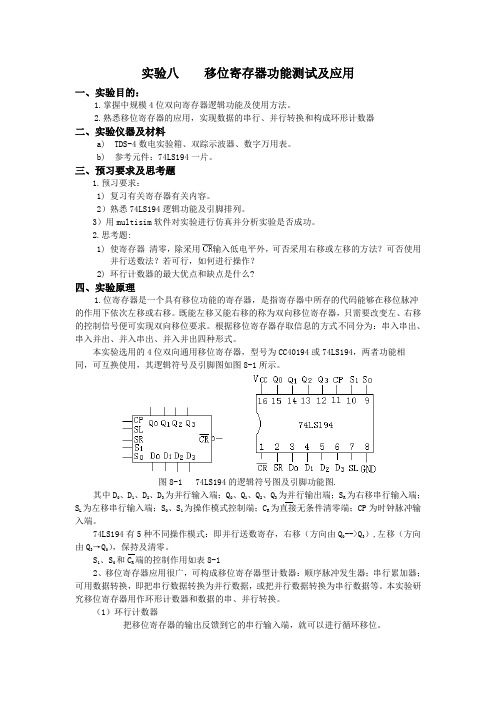

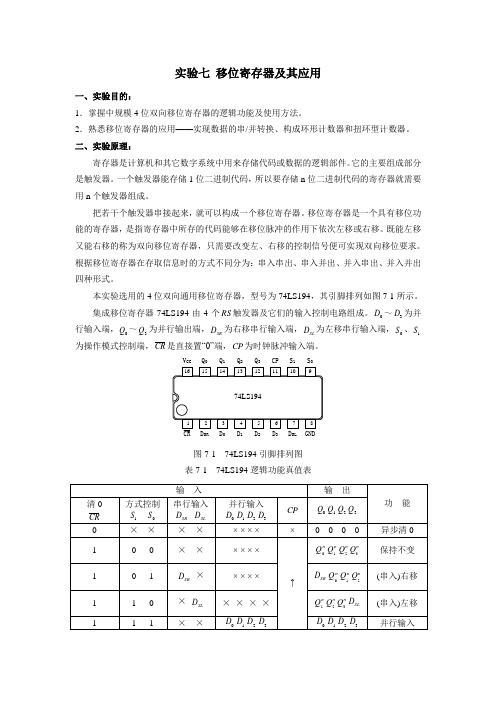

本实验选用的4位双向通用移位寄存器,型号为74LS194,其引脚排列如图7-1所示。

集成移位寄存器74LS194由4个RS 触发器及它们的输入控制电路组成。

0D ~3D 为并行输入端,0Q ~3Q 为并行输出端,SR D 为右移串行输入端,SL D 为左移串行输入端,0S 、1S 为操作模式控制端,CR 是直接置“0”端,CP 为时钟脉冲输入端。

V CCQ 0Q 1Q 2Q 3CPS 1S 0图7-1 74LS194引脚排列图 表7-1 74LS194逻辑功能真值表1.环形计数器环形计数器具有如下特点:⑴ 进位模数与移位寄存器触发器数相等; ⑵ 结构上其反馈函数n n Q Q Q Q f =)(21 。

图7-2是用74LS194构成的四位环形计数器及其状态迁移图。

如起始态为10003210=Q Q Q Q ,其状态迁移为1000 → 0100 → 0010 → 0001,但存在无效循环和死态(如0000和1111),即无自校正功能。

图7-2 四位环形计数器2.扭环形计数器扭环形计数器(又称为约翰逊计数器)具有如下特点: ⑴ 进位模为移位寄存器触发器级数n 的二倍,即为2n ; ⑵ 电路结构上其反馈函数n n Q Q Q Q f =)(21 ; ⑶ 相邻两个态仅有一位代码不同。

实验47验证性实验——移位寄存器逻辑功能测试和应用.docx

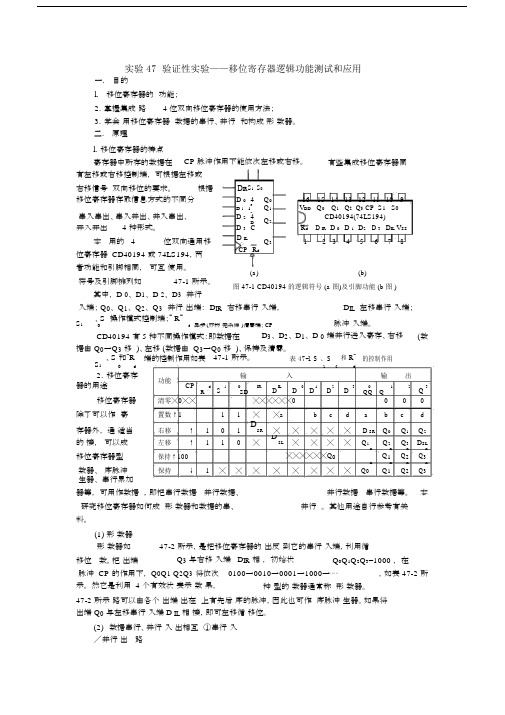

实验 47 验证性实验——移位寄存器逻辑功能测试和应用一. 目的l . 移位寄存器的 功能; 2.掌握集成 路 4 位双向移位寄存器的使用方法;3.学会 用移位寄存器 数据的串行、并行 和构成 形 数器。

二. 原理l .移位寄存器的特点寄存器中所存的数据在CP 脉冲作用下能依次左移或右移。

有些集成移位寄存器同有左移或右移控制端, 可根据左移或右移信号 双向移位的要求。

根据 D IR S 1 S 0Q 01615 14 13 12 11 10 9移位寄存器存取信息方式的不同分D 0 49Q 1V DD Q 0 Q 1 Q 2 Q 3 CP S 1 S 0D 1 1串入串出、串入并出、并入串出、D 2 0CD40194(74LS194)4Q 24 种形式。

D 3 DR dD IR D 0 D 1 D 2 D 3 D IL V SS并入并出C本 用的 4位双向通用移D ILQ 312 345678CP R d位寄存器 CD40194 或 74LS194,两者功能和引脚相同, 可互 使用。

(a)(b)符号及引脚排列如47-1 所示。

图 47-1 CD40194 的逻辑符号 (a 图)及引脚功能 (b 图 )其中, D 0、 D 1、 D 2、 D 3 并行入端; Q 0、 Q 1、 Q 2、 Q 3 并行 出端: D IR 右移串行 入端,D IL 左移串行 入端;S 1 、S 操作模式控制端;ˉ R ˉ脉冲 入端。

d 异步 (亦称 无条件 )清零端; CPCD40194 有 5 种不同操作模式:即数据在D 3、 D 2、 D 1、 D 0 端并行送入寄存、右移(数据由 Q 0→Q 3 移 )、左移 (数据由 Q 3→Q 0 移 )、保持及清零。

S 1 、S 和ˉR 端的控制作用如表 47-1 所示。

表 47-1 S 、S 0和 R ˉ 的控制作用0 d 1 d2.移位寄存 功能 输 入输 出器的用途 CP SD D D D DQd 1 0 IRIL 0 1 2 3 0 1 23R ˉ SDQQ Q移位寄存器清零╳0╳╳ ╳╳╳╳╳╳00 0 0 除了可以作 寄 置数↑1 11 ╳ ╳a bc d abc d存器外, 通 适当 右移 ↑ 1 0 1 DSR╳╳ ╳ ╳ ╳ D SR Q 0 Q 1Q 2的 接, 可以成 左移↑11╳DSL╳╳╳ ╳Q 1Q 2Q 3 D SL移位寄存器型 保持↑100n n n n╳╳╳╳╳╳Q 0Q 1 Q 2 Q 3 数器、 序脉冲1nnnn保持↓╳╳ ╳╳╳╳╳ ╳Q 0Q 1Q 2Q 3生器、 串行累加器等, 可用作数据 ,即把串行数据 并行数据、 并行数据 串行数据等。

实验6-移位寄存器功能测试和应用-(实验报告要求)

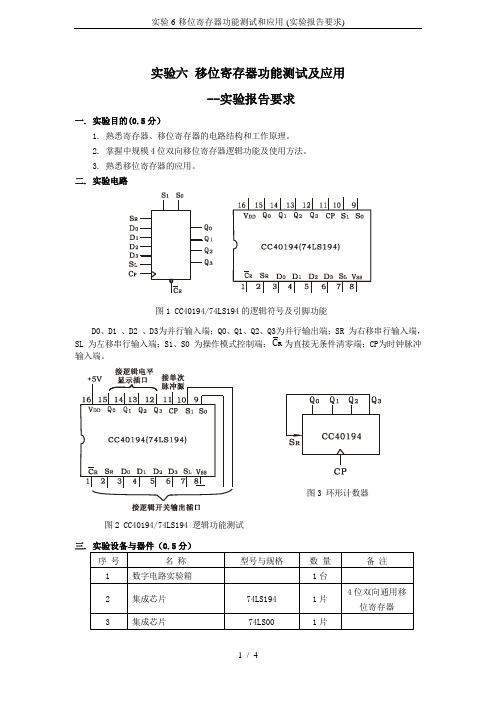

实验六 移位寄存器功能测试及应用--实验报告要求一. 实验目的(0.5分)1. 熟悉寄存器、移位寄存器的电路结构和工作原理。

2. 掌握中规模4位双向移位寄存器逻辑功能及使用方法。

3. 熟悉移位寄存器的应用。

二. 实验电路D0、D1 、D2 、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;SR 为右移串行输入端,SL 为左移串行输入端;S1、S0 为操作模式控制端;R C 为直接无条件清零端;CP 为时钟脉冲输入端。

三图2 CC40194/74LS194逻辑功能测试图1 CC40194/74LS194的逻辑符号及引脚功能图3 环形计数器四. 实验原理(0.5分)1.移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。

既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。

根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。

本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用。

74LS194有5种不同操作模式:即并行送数寄存,右移(方向由Q0-->Q3),左移(方向由Q3→Q0),保持及清零。

2.移位寄存器应用很广,可构成移位寄存器型计数器:顺序脉冲发生器;串行累加器;可用数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。

本实验研究移位寄存器用作环形计数器和数据的串、并行转换。

(1)环行计数器把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位。

(2)实现数据、并行转换器a)串行∕并行转换器串行∕并行转换器是指串行输入的数码,经转换电路之后变换成并行输出。

b)并行∕串行转换器并行∕串行转换器是指并行输入的数码经转换电路之后,换成串行输出。

五. 实验内容与步骤(共1分)1.测试74LS194的逻辑功能(0.5分)(1)在实验箱上选取一个16P插座,按定位标记插好74LS194集成块。

实验八 移位寄存器及其应用

实验八 移位寄存器及其应用一、实验目的1.熟悉移位寄存器的结构及工作原理 2.了解移位寄存器的应用。

二、实验原理移位寄存器是具有移位功能的寄存器。

它是一种由触发器链型连续组成的同步时序网络。

代码的移位是在统一的位移脉冲CP 控制下进行的。

每来一个移位位脉冲,原存贮于寄存器的信息代码就按规定的方向(左方或右方)同步移一位。

移位寄存器的类型,按移位的方式可分为左移﹑右移和双向移位寄存器;按其输入输出方式可分为并行输入—并行输出﹑并行输入—串行输出﹑串行输入—并行输出和串行输入—串行输出等几种。

移位寄存器应用较广。

利用移位寄存器可以构成计数分频电路﹑序列信号发生器、串/并行代码转换器、延时电路等。

移位寄存器的状态转移是按移存规律进行的,一般称为移存型计数器。

常用的移存型计数器有环行计数器和扭环形计数器。

下面介绍几种常用的MSI 移位寄存器及其应用。

74LS195为4位并行存取移位寄存器;74LS194为4位双向通用移位寄存器,它具有左移﹑右移﹑并行输入数据﹑保持及清除等五种功能。

它们的功能表及管脚图见附录. 应用举例:(一)移存型计数器 (1) 环形计数器环形计数器的特点是环形计数器的计数模数M=移位寄存器位数N ,且工作状态是依次循环出1或0,如4为环形计数器状态为0001-0010-0100-1000或1110-1101-1011-0111。

设计该类计数器往往要求电路能自启动。

(2) 扭环计数器扭环计数器又称为约翰逊计数器。

其特点是四位扭环计数器具有N=2n=8个有效计数状态,且相邻两状态间只有一位代码不同,因此扭环计数器的输出所驱动的组合网络不会产生功能竞争。

(3) 任意进制移存型计数器只要状态转移关系符合移存规律的计数器,就称为移存型计数器。

移存型计数器只要M ≠2N 时,就要考虑计数器的自启动问题。

移存型计数器子启动的方法有两种:①、 改变移位寄存器串行输入D 0的反馈方程,例如:让循环出“1”的4位环形计数器的D 0=012Q Q Q ++,使全“0”状态时的的D 0=1;如果是循环出“0”的4位环形计数器,则0120Q Q Q D =,使全“1”状态时的D 0=0,从而实现自启动。

实验8移位寄存器逻辑功能测试及应用

实验八移位寄存器逻辑功能测试及应用一、实验目的:1、掌握中规模4位双向移位寄存器逻辑功能及使用方法;2、熟悉移位寄存器的应用一一构成环形计数器和实现数据的串行、并行转换。

二、实验原理:移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。

既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。

本实验选用的4位双向移位寄存器,型号为74LS194,其引脚排列如图11 —1所示。

移位寄存器不仅可以组成串行一并行数码转换器,还可以方便地组成移位寄存器型计数器、脉冲分配器等电路。

常用的移位寄存器有环行计数器和扭环型计数器。

图11 —1 74LS194引脚排列及功能三、实验仪器及器材:实验仪器设备:DGJ —2型电工技术实验装置(D71 —2数电实验挂箱)集成块:74LS194 74LS04四、实验内容与步骤:1、验证移位寄存器74LS194的逻辑功能:计数脉冲由单次脉冲源提供,清零端上,、工作状态控制端M1 M2、并行数据输入端D 0—D3、DS L为左移串行数据输入端、DS R右移串行数据输入端分别接逻辑电平开关,输出端Q o—Q3均接逻辑电平显示。

按如下逐项测试并判断该集成块的功能是否正常。

(1)异步清零功能:当-I,=o时,这时Q3Q2Q1Q O=OOOO,双向移位寄存器清零。

其它输入信号都不起作用,与CP无关,故称为异步清零。

(2)保持功能:当-上=1,且CP=0或M1 =M2=0时,双向移位寄存器保持状态不变。

(3)同步并行送数功能:当_t.=1,M1 =M2=1时,在CP上升沿操作下,并行输入数据d3 d2 d1 d0 送入寄存器。

(4)右移串行送数功能:当-h=1,M1 =0、M2=1时,在CP上升沿操作下,可依次把加在讣端的数据从时钟触发器行送入寄存器中。

(5)左移串行送数功能:当 -上=1,M1 =1、M2=0时,在CP上升沿操作下,可依次把加在DS L端的数据从时钟触发器串行送入寄存器中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验八移位寄存器功能测试及应用

一、实验目的:

1.掌握中规模4位双向寄存器逻辑功能及使用方法。

2.熟悉移位寄存器的应用,实现数据的串行、并行转换和构成环形计数器

二、实验仪器及材料

a) TDS-4数电实验箱、双踪示波器、数字万用表。

b) 参考元件:74LS194一片。

三、预习要求及思考题

1.预习要求:

1) 复习有关寄存器有关内容。

2)熟悉74LS194逻辑功能及引脚排列。

3)用multisim软件对实验进行仿真并分析实验是否成功。

2.思考题:

1) 使寄存器清零,除采用输入低电平外,可否采用右移或左移的方法?可否使用

并行送数法?若可行,如何进行操作?

2) 环行计数器的最大优点和缺点是什么?

四、实验原理

1.位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。

既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。

根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。

本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相

同,可互换使用,其逻辑符号及引脚图如图8-1所示。

图8-1 74LS194的逻辑符号图及引脚功能图.

其中D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;S R为右移串行输入端;S L为左移串行输入端;S0、S1为操作模式控制端;C R为直接无条件清零端;CP为时钟脉冲输入端。

74LS194有5种不同操作模式:即并行送数寄存,右移(方向由Q0-->Q3),左移(方向由Q3→Q0),保持及清零。

S1、S0和C R端的控制作用如表8-1

2、移位寄存器应用很广,可构成移位寄存器型计数器:顺序脉冲发生器;串行累加器;可用数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。

本实验研究移位寄存器用作环形计数器和数据的串、并行转换。

(1)环行计数器

把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位。

(2)实现数据、并行转换器

a)串行∕并行转换器

串行∕并行转换器是指串行输入的数码,经转换电路之后变换成并行输出b)并行∕串行转换器

并行∕串行转换器是指并行输入的数码经转换电路之后,换成串行输出。

表8-1

功能输入输出CP S1S0 S R S L D0 D1 D2 D3 Q0 Q1 Q2 Q3

清零×0 ××××××××0 0 0 0

送数↑ 1 1 1 ×× a b c d a b c d

右移↑ 1 0 1 D SR ×××××D SR Q0 Q1 Q2

左移↑ 1 1 0 ×D SL ××××Q1 Q2 Q3 D SL

保持↑ 1 0 0 ××××××Q n0 Q1n Q2n Q3n

保持↓ 1 ××××××××Q0n Q1n Q2n Q3n

五、实验内容

1、测试74LS194的逻辑功能完成表8-2

按图8-1接线、S1、S0、S L、S R、D0、D1、D2、D3分别接至逻辑开关;Q0、Q1、Q2、Q3接至发光二极管。

CP端接单次脉冲源。

按表7-1所规定的输入状态,逐项进行测试。

74LS194逻辑功能测试

(1)清除:令=0,其它输入均为任意态,这时寄存器输出Q0、 Q1、 Q2 、Q3应均为0。

清除后,至=1。

(2)送数:令=S1=S0=1 ,送入任意4位二进制数,如D0、D1、D2、D3=abcd,加CP 脉冲,观察CP=0、CP由1→0、三种情况下寄存器输出状态的变化,观察寄存输出状态变化是否发生在CP脉冲的上升沿。

(3)右移:清零后,令=1, S1=0 S0=1,由右移输入端SR送入二进制数码如0100,由CP端连续加4个脉冲,观察输出情况,记录之。

(4)左移:先清零或予至,再令=1 S1=1,S0=0,由左移输入端SL送入二进制数码如1111,连续加四个CP脉冲,观察输出端情况,记录之。

(5)保持:寄存器予置任意4位二进制数码abcd,令=1,S1=S0=0,加CP脉冲,观察

寄存器输出状态,记录之。

表8-2

清除模式时钟串行输入输出功能总

结

C R S1S0CP S R S L D0 D1 D2 D3 Q0 Q1 Q2 Q3

0 ×××××××××

1 1 1 ↑×× a b c d

1 0 1 ↑0 ×××××

1 0 1 ↑ 1 ×××××

1 0 1 ↑0 ×××××

1 0 1 ↑0 ×××××

1 1 0 ↑× 1 ××××

1 1 0 ↑× 1 ××××

1 1 0 ↑× 1 ××××

1 1 0 ↑× 1 ××××

1 0 0 ↑××××××

2、环形计数器

自拟实验步骤.用并行送数法予置寄存器为某二进制数码(如0100),然后进行右移循环,观察寄存器输出端状态的变化,记入表8-3中。

表8-3

CP Q0 Q1 Q2 Q3

0 0 1 0 0

1

2

3

4

六、实验报告要求:

1.根据实验内容1的实验步骤完成表8-2。

2.根据实验内容2的完成表8-3,并画出4位环形计数器的状态转换图及波形图。