多芯片封装MCP

材料的封装和封装技术

材料的封装和封装技术材料的封装是指为了保护和改善材料特性而对其进行包装的过程。

封装技术则是使用各种方法和材料将元器件或产品封装起来,以提供保护、连接、散热、防护和美观等功能。

在现代工业和科技领域中,封装技术在材料应用和电子器件行业中起着至关重要的作用。

一、材料的封装意义和现实需求材料的封装具有多重意义和现实需求。

首先,封装可以提供保护作用,防止材料或器件受到机械损伤、化学腐蚀、湿氧反应等不利环境因素的影响。

其次,封装还可以改善材料的特性,如提高电子器件的传导性能、隔离性能和稳定性能等。

此外,封装还能提供连接功能,使得材料或器件能够与其他设备或系统进行有效连接和交互。

最后,封装还能增加美观性和使用便利性,使得材料能够更好地融入到生活和工作环境中。

二、常见的封装材料和技术1. 封装材料常见的封装材料包括塑料、金属、陶瓷和复合材料等。

塑料封装材料具有重量轻、成本低、绝缘性能好等特点,广泛应用于电子器件领域。

金属封装材料具有高强度、良好的导热性和机械稳定性等优点,适用于高功率元器件和高温环境中的封装需求。

陶瓷封装材料具有优异的绝缘性能、高温稳定性和耐腐蚀性等特点,广泛应用于高性能压电器件和传感器等领域。

复合材料是由两种或更多种材料组成的复合结构,具有综合性能优异、多功能化等特点,可满足不同封装需求。

2. 封装技术目前常见的封装技术包括贴片封装、球栅阵列封装(BGA)、无焊盖封装(LGA)、晶圆级封装(WLP)和多芯片封装(MCP)等。

贴片封装是指将芯片颗粒或者芯片模块粘贴到基板上,并通过焊接或粘接方式与基板连接。

BGA封装是一种无引线封装技术,具有高容积、高可靠性和良好的散热性能等特点,适用于高密度器件和大功率器件。

LGA封装是通过接触垫与基板进行电气连接的技术,具有较大的接触面积和良好的电气性能,广泛应用于通信设备和计算机领域。

WLP封装是通过在晶圆上直接封装芯片,不需要外部基板的一种封装方式,具有体积小、集成度高的特点,适用于微型尺寸和超薄设备的封装需求。

SIP与MCP封装

MCP封装

• MCP(Multi Chip Package,多芯片封装),即将多个芯片封装 在一处。MCP中叠层的多个芯片一般为同一种类型,以芯 片之间不能进行信号存取和交换的存储器为主,从整体来 讲为一多芯片存储器。

对比

• SIP: • MCP: • 长电科技 ,天水华天,南通富士通

Thank!

SIP封装与MCP封装

SSDC 2011-7-19

兔年吉祥

封装 SIP封装 MCP封装 对比 相关企业 OVER

芯片封装

• 芯片封装技术就是将内存芯片包裹起来,以避免芯片与外 界接触,防止外界对芯片的损害的一种工艺技术。空气中 的杂质和不良气体,乃至水蒸气都会腐蚀芯片上的精密电 路,进而造成电学性能下降。不同的封装技术在制造工序 和工艺方面差异很大,封装后对内存芯片自身性能的发挥 也起到至关重要的作用。 随着光电、微电制造工艺技术 的飞速发展,电子产品始终在朝着更小、更轻、更便宜的 方向发展,因此芯片元件的封装形式也不断得到改进。芯 片的封装技术多种多样,有DIP、POFP、TSOP、BGA、QFP、 CSP等等,种类不下三十种,经历了从DIP、TSOP到BGA的 发展历程。芯片的封装技术已经历了几代的变革,性能日 益先进,芯片面积与封装面积之比越来越接近,适用频率 越来越高,耐温性能越来越好,以及引脚数增多,引脚间 距减小,重量减小,可靠性提高,使用更加方便。DIP封 装 TSO封装

• SIP(system in package,系统级封装),指将不同种类的元 器件,通过不同种技术,混载于同一封装体内,由此构成 系统集成封装形式。SIP中可搭载不同类型的芯片,芯片之 间可进行信号的存取和交换,从而以一个系统的规模而具 备某种功能。

SIP封装类型:2D SIP,3D SIP, 堆叠 SIP

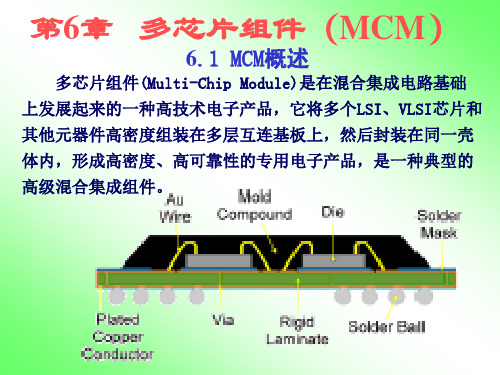

第6章 多芯片组件(MCM)(精简版)

用了面积为152mm2、运算能力为1.25亿次/秒的MCM作为处理组

件,使整个处理系统的尺寸由原来的机框变成了一块插件,系

统运算能力达到5亿次/秒,经扩展可达80亿次/秒。

6.2 MCM的概念、分类与特性

至今对MCM尚无统一的定义,综合国外专家对MCM所下的定 义,MCM原则上应具备以下条件: (1)多层基板有4层以上的导体布线层。 (2)封装效率(芯片面积/基板面积)大于20%。

(3)封装壳体通常应有100个以上的I/O引脚。

其他附加条件:布线宽度每英寸从250根到500根,有多个 LSI和(或)VLSI裸芯片等。 从组装(或封装)对MCM定义为:两个或更多的集成电路裸芯 片电连接于共用电路基板上,并利用它实现芯片间互连的组件。

脚数可达到300∽2500个。

3.高散热性能 MCM多有散热装置,并采用一些新的散热技术,因此具有高散

热性能。

4.低成本性能 MCM安装工艺技术比原来的一般安装技术在封装密度和组件工 作频率两方面高2∽4倍,因此可实现产品相对低的成本。

6.3 MCM的BGA封装

6.8.1 概述

早期的MCM采用QFP和PGA,现在采用BGA,称为MCM BGA。 传统的MCM BGA封装采用模塑封装,MCM中芯片、BGA基板、 WB均形成于单一整体结构中,如图所示的AT&T公司用于电话中 的MCM BGA模塑封装。

MCM—C/D(with Thin Film Deposited on Ceramic

Substrate):厚、薄膜混合多层基板制成的MCM; MCM—Si(with Silicon Substrate) :Si基板制成的MCM;

MCM的特性:

1.高速性能

MCM产品,采用多个裸芯片高密度安装在一起,缩短了芯片间 的距离,信号延迟大大减少,使LSI的信号工作频率得到提高。 2.高密度性能 MCM具有高密度布线特性和高引脚密度特性,在1cm2面积内引

sip工艺技术介绍

sip工艺技术介绍SIP技术,全称为System in Package,是一种封装技术,将多个芯片组件和其他组件封装在一个单一的模块内,形成一个完整的系统。

SIP技术可以提高电子设备的性能、可靠性和集成度,并且能够更好地满足不同应用场景的需求。

SIP技术主要包括芯片封装、电路设计、芯片组件选择和测试等环节。

在芯片封装方面,常用的封装方式有多芯片模块(MCM)和多芯片封装(MCP)等。

MCM是将多个芯片组件封装在一个模块内,通过晶圆级封装技术实现高集成度和高性能。

MCP是将多个芯片堆叠在一起,通过晶圆级封装或者探针级连接技术实现。

在电路设计方面,SIP技术需要考虑模块内芯片组件的互连和供电等问题。

为了实现高速信号传输和良好的电磁兼容性,需要采用高速互连技术,如高速差分信号线和层间互连。

同时,为了保证电路的稳定供电,采用电源管理技术和射频滤波器等组件。

在芯片组件选择方面,SIP技术需要根据应用需求选择合适的芯片。

不同的应用场景需要不同的功能和性能,比如高性能处理器、射频收发器、传感器等。

同时,还需要考虑芯片组件之间的互连方式,如通过焊接、直接连接或者探针连接等。

在测试方面,SIP技术需要进行系统级测试和可靠性测试。

系统级测试可以验证整个模块的功能和性能,并且保证各个芯片组件之间的互连正常。

可靠性测试可以评估模块的寿命和稳定性,如温度循环测试、振动测试和湿度测试等。

SIP技术在电子设备中有广泛的应用,尤其是在移动通信、消费电子和汽车电子等领域。

SIP技术可以实现更小型化的设备尺寸、更高性能的功能和更低功耗的设计。

例如,在手机中,SIP技术可以将处理器、射频芯片、传感器和存储芯片等集成在一个模块内,大大减少了设备的体积,提高了整体性能。

总之,SIP技术是一种有效的封装技术,可以将多个芯片组件和其他组件封装在一个模块内,形成一个完整的系统。

通过合理的芯片封装、电路设计、芯片组件选择和测试等环节,可以实现高性能、可靠性和集成度的电子设备设计。

多芯片封装(MCM)方案(一)

多芯片封装(MCM)方案一、实施背景随着科技的飞速发展,电子产品对高性能、小型化和低成本的需求日益增强。

其中,多芯片封装(MCM)技术成为满足这些需求的关键。

MCM方案通过将多个芯片集成到一个封装内,提高了芯片间的通信效率,降低了功耗,并减少了产品体积。

这种技术对于推动产业结构改革,尤其是在高集成度、高性能和低功耗的领域,具有重大意义。

二、工作原理MCM技术利用先进的封装工艺,将多个芯片(如处理器、存储器和模拟芯片等)集成到一个封装内。

通过缩短芯片间的距离,提高互连密度,降低信号传输延迟,从而提高整个系统的性能。

此外,MCM技术还通过优化散热设计,降低芯片工作温度,提高系统的稳定性。

三、实施计划步骤1.需求分析:首先明确产品的需求,包括性能、尺寸、功耗等。

这将有助于确定所需芯片类型及数量。

2.芯片选择:根据需求分析,选择适合的芯片。

这需要考虑芯片的性能、功耗、成本等因素。

3.封装设计:设计适合多芯片封装的架构,包括芯片的布局、互连设计、散热设计等。

4.制造与测试:利用所选的芯片和设计,进行MCM的制造和测试。

这包括前道制造和后道测试等环节。

5.验证与优化:对制造和测试的结果进行验证,根据结果进行优化,以提高产品的性能和稳定性。

四、适用范围MCM技术适用于多种领域,如移动设备、云计算、人工智能、物联网等。

在移动设备中,MCM可以提高设备的性能并降低功耗;在云计算中,MCM可以实现高速数据传输和低延迟处理;在人工智能和物联网中,MCM可以提高设备的计算能力和通信效率。

五、创新要点MCM技术的创新点在于其高集成度、高性能和低功耗的特点。

通过将多个芯片集成到一个封装内,不仅提高了芯片间的通信效率,还降低了功耗和产品体积。

此外,MCM技术还通过优化散热设计,提高了系统的稳定性。

六、预期效果与收益预期通过实施MCM方案,可以带来以下效果和收益:1.提高性能:MCM技术将多个芯片集成到一个封装内,提高了芯片间的通信效率,从而提高了整个系统的性能。

芯片封装结构

芯片封装结构随着科技的发展,芯片已经成为现代电子设备中不可或缺的关键组件。

而芯片的封装结构则是保护和连接芯片的重要环节。

本文将介绍几种常见的芯片封装结构,包括无封装、单片封装、多芯片封装和三维封装。

1. 无封装在早期的电子设备中,芯片通常是无封装的。

即芯片直接暴露在外,没有任何保护措施。

这种结构简单直接,但由于芯片易受外部环境影响,容易受到机械损伤、尘埃、湿气等因素的侵蚀,对芯片的稳定性和可靠性有较大影响。

因此,无封装结构已经很少在现代电子设备中使用。

2. 单片封装单片封装是目前应用最广泛的芯片封装结构之一。

它采用一层封装材料将芯片封装在内部,保护芯片免受外界环境的侵蚀。

常见的单片封装材料有塑料和陶瓷。

塑料封装常用于低成本的消费电子产品,而陶瓷封装则常用于高性能和高可靠性的工业和军事设备。

单片封装的结构相对简单,尺寸较小,适合集成度较低的芯片。

它通常包括芯片、封装基板、引脚和封装材料。

芯片通过焊接或黏贴的方式固定在封装基板上,引脚通过焊接与芯片连接。

封装材料填充在芯片和封装基板之间,起到保护和固定芯片的作用。

3. 多芯片封装随着电子设备的功能需求越来越复杂,单片封装已经无法满足需求。

多芯片封装应运而生。

多芯片封装是将多个芯片封装在同一个封装体中,实现不同芯片之间的连接和协同工作。

多芯片封装的结构相对复杂,需要在封装体内部进行芯片之间的布局和连接。

常见的多芯片封装结构有多芯片模块(MCM)、多芯片封装(MCP)和片上系统(SoC)等。

多芯片模块将多个芯片封装在同一个封装体中,实现不同功能的集成。

多芯片封装则是将多个芯片封装在同一个封装体中,实现更高的集成度和性能。

片上系统是将整个电子系统集成在一块芯片中,实现更高的集成度和性能。

4. 三维封装三维封装是近年来发展起来的一种封装技术。

它通过将多个芯片在垂直方向上堆叠,实现更高的集成度和性能。

三维封装可以大大减小芯片之间的距离,减少信号传输的延迟和功耗,提高系统的工作效率和性能。

mcp芯片

mcp芯片MCP(Multi-Chip Package),中文名称为多芯片封装,是一种集成了多个芯片的封装技术。

它将多个芯片封装在一个包内,通过高密度的互连线路将芯片之间进行连接。

MCP芯片常用于需要高度集成和较小尺寸的应用场景,如移动设备、嵌入式系统等。

MCP芯片的核心技术是通过三维堆叠封装技术将多个芯片层叠在一起,并通过互连线路实现芯片之间的通信。

这种技术能够大大提高芯片的集成度,减少设备的尺寸,并提高系统的性能。

MCP芯片通常由主控芯片、存储芯片、射频芯片等多个功能模块组成。

封装方式可以是球栅阵列封装(BGA)或者无焊盖封装(FCBGA),常见的MCP芯片封装尺寸从几毫米到几厘米不等。

MCP芯片的优势主要体现在以下几个方面:1. 高集成度:MCP芯片可以将多个芯片集成在一个包内,实现多个功能模块的集成。

这样不仅可以减小设备的尺寸,提高设备的性能,还能降低系统成本。

2. 低功耗:MCP芯片通过在一个封装内集成多个功能模块,可以有效减少功耗。

各个芯片之间通过短距离的互连线路进行通信,能够降低传输功耗,提高系统的能效。

3. 高性能:MCP芯片集成了多个芯片,能够实现不同功能模块之间的高速通信和协同工作。

通过集成多个功能模块,可以提高系统的整体性能,满足高性能应用的需求。

4. 灵活性:MCP芯片可以根据应用的需求进行定制设计。

不同功能模块可以选择不同的芯片,灵活组合,实现定制化的功能需求。

5. 可靠性:MCP芯片通过三维堆叠封装技术,能够实现芯片之间的密集互连,减少因互连线路导致的问题。

同时,MCP芯片还可以通过多重备份机制提高系统的可靠性,降低故障率。

MCP芯片在移动设备、嵌入式系统等领域有着广泛的应用。

在手机中,MCP芯片可以集成处理器、内存、无线模块等多个芯片,实现高性能和低功耗的手机设计。

在汽车电子系统中,MCP芯片可以集成多个功能模块,如车载娱乐系统、导航系统等,提供丰富的车载应用。

总之,MCP芯片作为一种高度集成的封装技术,在提高设备性能、减小尺寸、降低功耗等方面有着独特的优势。

电子元器件的封装与封装技术进展

电子元器件的封装与封装技术进展随着电子科技的不断发展,电子元器件在现代社会中起着关键的作用。

而电子元器件的封装和封装技术则是保证其正常运行和长期可靠性的重要环节。

本文将介绍电子元器件封装的概念、封装技术的发展以及未来的趋势。

一、电子元器件封装的概念电子元器件封装是指将裸露的电子器件(如芯片、晶体管等)进行包装,并加入保护层,以充分保护元器件的性能、提高连接可靠性,并便于安装和维护。

合理的封装设计能够保护电子器件不受外界环境的影响,同时提高电子器件在电磁环境中的工作稳定性。

二、封装技术的进展随着电子技术的不断创新和发展,电子元器件的封装技术也在不断进步。

以下是一些主要的封装技术进展:1. 芯片封装技术芯片封装技术是将芯片包装在塑料、陶瓷或金属封装中。

近年来,微型封装技术的发展使得芯片的封装更加紧凑,能够将更多的功能集成在一个芯片中,从而提高了元器件的性能和可靠性。

2. 表面贴装技术(SMT)表面贴装技术是指将元器件直接通过焊接或贴合等方式固定在印刷电路板表面的技术。

与传统的插针连接方式相比,SMT可以提高元器件的连接可靠性,同时减小了电路板的尺寸。

3. 多芯片封装(MCP)多芯片封装是将多个芯片封装在同一个封装体中。

通过这种方式,可以将不同功能的芯片集成在一个封装中,同时减少了电路板上元器件的数量,提高了整体系统的紧凑性和可靠性。

4. 三维封装技术三维封装技术是将多个芯片层叠在一起,并通过微连接技术进行连接。

这种封装方式大大提高了元器件的集成度和性能,同时减小了系统的体积。

三、未来的趋势随着电子技术的不断发展,电子元器件封装技术也将朝着以下几个方向发展:1. 进一步集成化未来的电子元器件封装技术将会更加注重集成化,将更多的功能集成在一个封装中。

这样可以提高整体系统的紧凑性,减小系统的体积,并提供更高性能的元器件。

2. 更高的可靠性和稳定性未来的封装技术将注重提高元器件的可靠性和稳定性。

通过采用先进的封装材料和工艺,可以提高元器件在极端环境下的工作性能,如高温、高湿等。

封装技术介绍

塑料封装技术摘要塑料封装是指对半导体器件或电路芯片采用树脂等材料的一类封装,塑料封装一般被认为是非气密性封装。

它的主要特点是工艺简单、成本低廉、便于自动化大生产。

塑料产品约占IC封装市场的95%,并且可靠性不断提高,在3GHz以下的工程中大量使用。

标准塑料材料主要有约70%的填充料、18%环氧树脂、外加固化剂、耦合剂、脱模剂等。

各种配料成分主要取决于应用中的膨胀系数、介电常数、密封性、吸湿性、强韧性等参数的要求和提高强度、降低价格等因素。

Plastic packaging is a means of semiconductor devices or circuit chips such as resin used for a class of packaging materials, plastic packaging generally found to be non-hermetic package. Its main feature is a simple process, low-cost and easy to automate large-scale production. IC packaging plastic products account for about 95% of the market, and continuously improve the reliability, and 3GHz in the following widely used in the project. Standard plastic materials, about 70% of the principal filler, epoxy resin and 18%, plus curing agent, coupling agent, such as release agent. The main components of a variety of ingredients depending on the application of expansion coefficient, dielectric constant, tightness, moisture absorption, strength and toughness, and other parameters of the requirements and increase the intensity, lower prices and other factors.关键字塑料封装技术发展引言电子封装技术是微电子工艺中的重要一环,通过封装技术不仅可以在运输与取置过程中保护器件还可以与电容、电阻等无缘器件组合成一个系统发挥特定的功能。

多芯片封装MCP

多芯片封装MCP多芯片封装(Multi-Chip Package,MCP)是将两个或多个芯片封装在同一个封装内,形成一种更小、更集成化的封装方式。

在今天的电子产品中,MCP已经成为一种更加常见的封装方式。

本文将讨论MCP的特点、优势和应用。

MCP的特点和优势1.小尺寸高密度MCP封装方式将多个芯片封装在一个封装内,有效地降低了芯片的空间占用,使得整个芯片的体积更小、更紧凑。

同时,高度集成化的设计,使得MCP芯片可以用于一些空间较小的电子设备中。

2.高可靠性和稳定性MCP的封装方式还可以有效的降低芯片的热量而且降低芯片的使用温度,从而有效的提高芯片的可靠性和稳定性。

对于那些需要长时间运行的电子设备,使用MCP芯片可以有效的提高设备的使用寿命和稳定性,减少设备的维修和更换次数。

3.节省成本使用MCP封装可以节省封装占用的PCB面积,同时降低芯片的制造成本。

MCP芯片的生产线比单独生产多个芯片的生产线要简单和便捷,这使得MCP芯片的成本低廉,特别是对于大批量生产或定制化生产的芯片而言。

4.多功能集成MCP芯片的封装方式通过将各个芯片的功能集成在同一个封装内,使电子设备的制造更加简单和方便,节省了设计时间和成本。

MCP在不同领域的应用MCP芯片的应用涉及多个领域,如计算机、通信、医疗设备、军工等,以下是部分领域的应用案例。

1.计算机MCP芯片可用于计算机的主板、内存,存储、网络、声音等各个不同的部件上,实现对计算机系统的完整集成和逻辑控制。

同时,这些芯片也可以用于笔记本电脑、平板和便携式设备中,使设备更加小巧和轻便。

2.通信MCP芯片在通信领域的应用非常多,如手机、电视、游戏机、照相机等设备都可以使用MCP芯片。

MCP芯片可以集成各种通信模块,如WiFi、蓝牙、移动通信等,可以减少设备占用空间和加快设备通信速度,提供更加完整的通信功能。

3.医疗设备MCP芯片也被广泛应用于医疗设备领域,如血压计、心率监测器等设备中。

半导体封装工艺介绍

半导体封装工艺介绍半导体封装工艺是在半导体芯片制造过程中的最后一个重要环节,它是将成品芯片连接到封装材料(如封装盖、引线、基板等)上的过程。

封装工艺的主要目的是为了保护芯片免受外部环境的影响,并提供连接外部电路所需的物理支持。

以下是半导体封装工艺的介绍。

1.封装材料选择封装材料的选择非常重要,它必须具备良好的热传导能力、高的可靠性和稳定性,以及良好的防尘、防湿、防腐蚀等性能。

常见的封装材料有陶瓷、塑料和金属等。

选择适当的封装材料可以提高芯片的性能和可靠性。

2.芯片倒装封装芯片倒装封装是指将芯片倒置,将芯片连接到封装基板上。

倒装封装可以减小芯片尺寸,提高集成度,减小信号传输距离,增加工作速度。

倒装封装需要进行焊接、接线、封装盖等工艺步骤。

3.球栅阵列封装(BGA)球栅阵列封装是一种常见的封装方式,它可以提供更多的引脚数量,并且引脚布局紧密,有利于功耗分布和信号传输。

BGA封装采用焊球连接芯片和封装基板,可以提高焊接可靠性和热传导能力。

4.多芯片封装(MCP)多芯片封装是将多个芯片集成在同一个封装盖内,节省空间、提高性能的封装技术。

MCP封装可以集成多个芯片,如存储芯片、逻辑芯片、功率芯片等,从而实现更高的集成度和性能。

5.系统级封装(SiP)系统级封装是将多个不同功能的芯片集成在同一个封装盖内,形成一个完整的系统。

系统级封装可以实现更高的集成度、更小的尺寸和更高的性能。

SiP封装通常包含各种芯片、射频模块、天线、滤波器等。

6.低温共热封装(LTCC)低温共热封装是一种在低温条件下封装的技术,可以提高封装成本和性能。

LTCC封装可以通过控制温度和时间来实现芯片和封装材料之间的结合,有利于提高封装精度和工艺稳定性。

7.高温共热封装(HTCC)高温共热封装是一种在高温条件下封装的技术,适用于对高温环境具有高要求的应用。

HTCC封装可以提供更大的功率传导和散热能力,增加芯片的可靠性和稳定性。

总之,半导体封装工艺是将芯片连接到封装材料上的过程,它直接影响到芯片的性能、可靠性和稳定性。

mcp存储器分类及其工作原理

mcp存储器分类及其工作原理MCP存储器分类及其工作原理MCP存储器是一种集成了多个存储单元的存储器,其中MCP代表Multi-Chip Package,意味着多芯片封装。

MCP存储器常用于手机、平板电脑等小型电子设备中,因为它具有体积小、功耗低等优点。

本文将介绍MCP存储器的分类及其工作原理。

一、MCP存储器分类根据存储介质的不同,MCP存储器可以分为以下几种类型:1. NOR Flash MCP:NOR Flash MCP是一种非易失性存储器,可以用于存储程序代码和数据。

它具有读取速度快的特点,适用于需要频繁读取数据的应用。

NOR Flash MCP常用于手机等设备的固件存储。

2. NAND Flash MCP:NAND Flash MCP也是一种非易失性存储器,常用于存储大容量的数据。

相比于NOR Flash MCP,NAND Flash MCP的读取速度较慢,但写入速度更快,适用于需要频繁写入数据的应用。

NAND Flash MCP常用于存储手机的照片、视频等大容量数据。

3. PSRAM MCP:PSRAM(Pseudo Static Random Access Memory)MCP是一种伪静态随机存取存储器,结合了静态随机存取存储器(SRAM)和动态随机存取存储器(DRAM)的特点。

PSRAM MCP具有较快的读写速度和相对较低的功耗,适用于高速缓存和数据存储等应用。

二、MCP存储器的工作原理MCP存储器由多个存储芯片组成,每个存储芯片都包含若干存储单元。

这些存储单元以网格状的方式排列,每个存储单元由一个晶体管和一个电容组成。

MCP存储器的工作原理可以简单描述为以下几个步骤:1. 地址译码:当系统需要读取或写入数据时,首先需要将逻辑地址转换为物理地址。

地址译码器会将逻辑地址转换为对应的存储单元地址。

2. 读取数据:当需要读取数据时,MCP存储器会根据物理地址找到对应的存储单元,并通过晶体管控制电容的充放电状态,将存储单元中的数据读取到电路中。

多芯片封装技术

多芯片封装技术

多芯片封装技术可以提供更高的集成度和性能,同时减小封装体积和功耗。它在移动设备 、无线通信、计算机、消费电子、汽车电子等领域得到广泛应用。然而,多芯片封装技术也 面临着封装复杂性、互连可靠性和热管理等挑战,需要综合考虑设计、制造和测试等方面的 问题。

多芯片封装技术

多芯片封装技术(Multi-Chip Package,MCP)是一种集成电路封装技术,它将多个芯 片集成在一个封装中。这种封装技术可以在一个封装内实现多个功能模块的集成,提高集成 度和性能,同时减小封装体积和功耗。

多芯片封装技术通常包括以下几种形式:

1. 多芯片模块(Multi-Chip Module,MCM):在一个封装中集成多个芯片,每个芯片 可以是不同的功能模块,如处理器、存储器、传感器等。这些芯片通过高密度互连技术(如 焊球、焊盘、线缆等)进行连接。MCM可以提供高速、高带宽的数据传输和低延迟的通信。

多芯片封装技术

2. 堆叠封装(Stacked Package):将多个芯片堆叠在一起,形成一个垂直的结构。每个 芯片可以是不同的功能模块,通过封装内的互连技术进行连接。堆叠封装可以实现更高的集 成度和更小的封装体积,同时提高芯片之间的通信速度和带宽。

3. 系统级封装(System-in-Package,SiP):将多个芯片和其他组件(如电容器、电感 器、滤波器等)集成在一个封装中,形成一个完整的功能模块。SiP可以实现更高Байду номын сангаас集成度和 更小的封装体积,同时提供更好的电磁兼容性和热管理。

3D封装技术简介

3D封装技术简介3D晶圆级封装,英文简称(WLP),包括CIS发射器、MEMS封装、标准器件封装。

是指在不改变封装体尺寸的前提下,在同一个封装体内于垂直方向叠放两个以上芯片的封装技术,它起源于快闪存储器(NOR/NAND)及SDRAM的叠层封装。

主要特点包括:多功能、高效能;大容量高密度,单位体积上的功能及应用成倍提升以及低成本。

一:封装趋势是叠层封(PoP);低产率芯片似乎倾向于PoP。

二:多芯片封装(MCP)方法,而高密度和高性能的芯片则倾向于MCP。

三:以系统级封装(SiP)技术为主,其中逻辑器件和存储器件都以各自的工艺制造,然后在一个SiP封装内结合在一起。

大多数闪存都采用多芯片封装(MCP,Multichip Package),这种封装,通常把ROM和RAM封装在一块儿。

多芯封装(MCP)技术是在高密度多层互连基板上,采用微焊接、封装工艺将构成电子电路的各种微型元器件(裸芯片及片式元器件)组装起来,形成高密度、高性能、高可靠性的微电子产品(包括组件、部件、子系统、系统)。

技术上,MCP追求高速度、高性能、高可靠和多功能,而不像一般混合IC技术以缩小体积重量为主。

但随着Flash闪存以及DRAM闪存追求体积的最小化,该封装技术由于使用了金属丝焊接,在带宽和所占空间比例上都存在劣势,而WSP封装技术将会是一个更好解决方案。

离子注入 Ion Implantation晶圆衬底是纯硅材料的,不导电或导电性极弱。

为了在芯片内具有导电性,必须在晶圆里掺入微量的不纯物质,通常是砷、硼、磷。

掺杂可以在扩散炉中进行,也可以采用离子注入实现。

一些先进的应用都是采用离子注入掺杂的。

离子注入有中电流离子注入、大电流/低能量离子注入、高能量离子注入三种,适于不同的应用需求。

热处理 Thermal Processing利用热能将物体内产生内应力的一些缺陷加以消除。

所施加的能量将增加晶格原子及缺陷在物体内的振动及扩散,使得原子的排列得以重整。

功率模块封装技术

功率模块封装技术功率模块封装技术是将功率电子设备(如功率半导体器件、散热器等)进行封装以达到保护、散热和连接电路的目的。

以下是一些常见的功率模块封装技术:1.多芯片模块封装(MCM):MCM技术是将多个功率器件(如晶体管、二极管等)和其他电子组件(如电感、电容等)集成在同一封装中。

这种封装方式具有高集成度和小封装尺寸的优点,能够提供更高的功率密度和更好的电热性能。

2.厚膜集成电路(HTCC)封装:HTCC封装是一种利用陶瓷基板进行封装的技术。

它使用陶瓷基板作为功率模块的载体,通过厚膜技术将功率器件和其他电子元件集成在陶瓷基板上。

HTCC封装具有良好的散热性能、耐高温和高电压的特点,适用于高功率和高频率应用。

3.薄膜封装技术:薄膜封装是将功率电子器件通过薄膜封装在基底上的技术。

薄膜封装可以提供更小的封装尺寸和更好的散热性能。

常见的薄膜材料包括有机瓦楞纸板(OPCB)、聚酰亚胺(PI)膜等。

4.直插式封装(DIP):DIP封装是一种传统的封装技术,适用于中低功率的应用。

功率器件通过导线插入直插式封装的孔中,然后通过焊接固定。

DIP封装具有良好的耐压性能和便于维修的特点,但功率密度相对较低。

5.表面贴装封装(SMT):SMT封装是一种现代化的封装技术,适用于小型、低功耗电子设备。

制造工艺简单,通过把功率电子器件直接贴附在印刷电路板(PCB)的表面上,并通过焊接连接。

SMT封装具有封装尺寸小、重量轻、制造成本低等优点。

这些封装技术可以根据功率模块的具体需求和应用领域进行选择。

不同的封装技术在功率密度、散热性能、尺寸、制造成本等方面有差异,并适用于不同功率范围的应用需求。

挤出空间降低成本从MCPeMCP与eMMC看移动设备内存的整合

挤出空间降低成本从MCPeMCP与eMMC看移动设备内存的整合随着移动终端的发展,移动设备的性能日益增强。

然而,这种性能提升也伴随着对内存需求的不断增加。

然而,内存和成本之间的关系一直是一个悬而未决的问题。

为了克服这个问题,MCP和eMMC技术被广泛使用,这两种技术提供了挤出空间降低成本的可能性。

本文将从MCP和eMMC两个方面分析移动设备内存的整合。

MCP技术MCP(Multi-Chip Package)是一种集成多个芯片的封装技术。

它将多个硅芯片和其他元器件封装在一个封装中,形成一个完整的功能模块。

在MCP中,通常会有CPU、Flash、RAM等多个核心芯片,这些核心芯片的不同封装方式和封装技术决定了MCP的分类和规格。

MCP技术具有内存集成、降低成本、高密度和灵活性等优点。

通过MCP技术,内存可以容易地加入和升级。

此外,MCP技术还可以使得设备的占用空间减少并降低成本。

MCP技术被广泛应用于移动设备等领域,成为了目前移动设备内存整合的主要方式。

无论是手机、平板电脑、笔记本电脑还是其他移动设备,都可以使用MCP技术。

eMMC技术eMMC(Embedded Multimedia Card)是一种内置在主板上的存储器。

它是一种集成式存储解决方案,主要由控制器和Flash存储单元组成。

eMMC还包括了所有的固件和控制电路,可以在极小的空间内提供高度集成的存储。

eMMC技术因其高速、高可靠性和低功耗的特点,目前被广泛应用于移动终端设备。

随着eMMC技术的发展,eMMC内存容量得到了极大的提升,能够满足更大的存储需求。

此外,eMMC技术还支持各种不同的主板接口并提供了更好的功耗效率。

MCP与eMMC整合虽然MCP和eMMC都有其优点,但也存在一些缺点。

例如,MCP技术需要占用更多的空间,而eMMC技术的容量受限。

因此,MCP和eMMC的整合被提出。

MCP与eMMC的整合可以实现更小空间内提高存储容量。

富士通开发出8层MCP封装技术

2 o . s n t 1 3 c m 9 O 2 5 q  ̄@ 6 .o

能 够 使 有 线 电 视 系 统 运 营 商 为 其 用 户 提 供 诸 长 到 2 91亿 美 元 , 幅 为 3. % 。 便 携 式 P 半 增 9 C 如 视 频 点播 服 务 和 电子 商 务 等 增 值 服 务 。

e— B x公 司 提 供 的 基 础 设 施 包 括 前 端 设 o 导 体 市 场 将 增 长 1 6 , 从 2 01年 的 8 亿 美 . % 0 3

话 , 字 音 频 /视 频 设 备 和 I 卡 等 方 面 ; 数 C 据 该 公 司 人 员 称 , 这 种 8 层 叠 M cP 是 利

世 代 。而 为 了 配 合 2 5 与 3 产 品 对 耗 电 量 的 .G G 严 苛 要 求 ,新 一 代 快 闪 记 忆 体 工 作 电 压 更 由 原 的 3伏 特 降 低 至 1 8伏 特 。 而 基 于 消 费 性 电 子 .

锋 和 夏普 ; 国 的 国 家 半 导 体 公 司 、 国讯 盟科 美 美 研 设 计 有 限 公 司 ( i maDe in ̄ 、i S g sg ) VAS 岱 司 T 和 M O e d o l I e 公 司 以 及 中 国 台 湾 d m Vi e Fi m n . 地 区 的 中环 有 限 公 司 ( CM C M a n tc ) g e is 。

面 积 。 由 于 2. G 夸 年 才 慢 慢 被 市 场 接 受 , 以 5 所

0. 2 毫 米 的 晶 圆 , 而 可 缩 短 生 产 周 期 , 低 05 从 降 设 备 成 本 ,简 化 生 产 环 境 。 惜 助 先 进 的 封 装 技

英 特 尔 策 略 上 希 望 在 市 场 正 式 起 飞 之 时 推 出 整 台 度 最 高 的 产 品 , 而 非 只 为 了 宣 示 进 军 无 线

什么是MCP

什么是MCP一.什么是MCP:MCP=Multi-Chip Package 中文意思是多制层封装芯片,其主要应用领域为手机等手持智能终端设备。

二.MCP的优点:体积小,能适应各种手持设备节省空间的原则。

成本方面较独立的芯片组和要有优势。

三.三星MCP的发展情况及其发展策略:三星从2004年开始致力于手机内存芯片的推广,2005年在全球取得了不到10%市场份额,当时这方面的前两位分别是INTEL和SPANSION这两个厂商。

2006年是三星MCP内存芯片市场份额大幅提高的一年,在2006年下半年由于SPANSION的128+32和64+16/64+31NOR+SRAM的MCP大面积缺货给了三星一次很好的机会,三星在8月开始逐步进入手机MCP领域,其推出的128+32MCP 芯片只要在软件方面作一些简单的调整就可以PIN TO PIN取代SPANSION的129系列产品,并且价格比当时的SPANSION 128+32的同类产品要低0.5USD,这使得中国大陆这一B类手机制造基地的设计公司和厂家纷纷切入到三星的MCP中来。

在2007年年初,三星又推出了其最新128+32的产品2931和2731,这两款产品的推出,将冲击SPANSION很大的市场份额。

四.三星的MCP产品做个简单的介绍:介绍从MCP制成和具体型号以及配合手机的主方案进行:MCP大致有三类:A;替换目前市场主流的SPANSION的NOR+SRAM(PSRAM)系列32+8型号为K5A3281CT(B)M--此款MCP主要可以应用于一些低端手机,包括英飞凌等低端方案,都可采用此款MCP。

64+16型号为K5J6316CT(B)M:三星已经在2007年将此款IC 停产,转移产能大量生产64+32制成的MCP64+32型号为K5J6332T(B)M:这使三星2007年主要推广的MCP之一,目前已经有很多方案认可,包括MTK 6226/6219以及展讯的6600D等方案都广泛采用此款芯片。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

多芯片封装

多芯片封装(Multi Chip Package;MCP)

封装形式的概念

所谓封装形式就是指安装半导体集成电路芯片用的外壳。

它不仅起着安装、固定、密封、保护芯片及增强电热性能等方面的作用,而且还通过芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印刷电路板上的导线与其他器件相连接。

衡量一个芯片封装技术先进与否的重要指标是芯片面积与封装面积之比,这个比值越接近1越好。

一般来说,出现一代新的CPU,就伴随着一种新的封装形式。

随各式便携式信息装置对内存特性需求日益多元化,可将数个芯片封装在一处的多芯片封装(Multi Chip Package;MCP)亦逐渐受到重视,全球包含三星电子、现代电子、英特尔等重量级IC厂商,近期纷纷看好此型内存市场前景,竞推出相关产品。

MCP的优点在于能将2至3种不同特性的芯片封装在一块,可因此减少占据的空间,当前主要为内存所采用。

而利用该封装做出的内存产品适于有复杂内存特性需求的信息装置使用。

目前内存厂商主要利用该技术将闪存(Flash)与SRAM做在一块。

-薄芯片处理是一种特殊的晶圆支持技术,能使芯片被琢磨到只有0.025毫米的厚度。

多重堆叠封装技术能利用无铅锡焊球把安装的芯片的板块堆叠起来。

这种封装在功能上相当于单一封装(single package)。

MCM(Multi Chip Model)多芯片组件-质量

为了解决单一的芯片集成度和功能不够完善的问题,把多个高集成度、高性能、高可靠性的芯片,在高密度多层互联基板上用SMD技术组成多种多样电子组件系统,从而出现了MCM多芯片组件系统

MCM具有以下特点:

封装延迟时间缩小,易于实现组件高速化

缩小整机/组件封装尺寸和重量。

系统可靠性大大提高。

总之,随着CPU和其他超大规模集成电路的进步,集成电路的封装形式也将得到相应的变化,而且封装形式的进步又将反过来促进芯片技术向前发展。

不久以前,高密度薄膜和多芯片封装(MCP)还被认为只是一种用于太空、军事、高端服务器以及大型主机等系统的新型技术,这种技术可以减小最终封装件及系统的尺寸

和重量、减少故障提高可靠性、使用更短和负载更轻的信号线增加速度并使系统具有良好的热性能。

如今,薄膜MCP的各种优点已能够在价格低廉的商用和消费类产品中得以实现,为批量生产而开发的低成本流水线薄膜生产工艺使这项技术由实验室进入到了工厂。

这种新工艺采用硅片覆膜高密度互连基板,对于装配车间来说看上去感觉就像是另一个芯片一样。

它把用不同工艺制造的器件集成在一个封装内,在功能上满足市场快速变化的要求,并在不改变封装引脚尺寸的前提下提高设计的性能。

MCM(MCP)-Multi Chip Module

MCM(MCP)-Multi Chip Module 是单芯片封装在两维空间里的延伸,也是专用集成电路封装的一种模式。

MCM 具有系统尺寸小、引线框架互连基板芯片、系统功能强、节省PCB 空间、屏蔽和频率特性好、开发风险小、成本低。

上个世纪末,MCM 的应用受到KGD、基板费用高、封装费用高的限制,被戏称为MCMs(Must Cost Millions)-“必须花费几百万”。

如今美国互连与封装学会把MCM按照不同的互连衬底介质分为L、C、D 三种类型:即层压介质高密度印刷线路板模块、陶瓷或玻璃混合电路和共烧陶瓷多层陶瓷模块和在聚合物和介质材料薄膜上淀积金属布线模块。

南通的MCM 属于第三类,采用陶瓷或硅基板,封装外形采用DIP、QFP 封装

_

薄膜工艺流程:首先在一个200mm(8英寸)晶圆上作4个铝层(两个互连层和两个电源层),中间用苯环丁烯(BCB)绝缘层隔开。

电源层金属溅射厚度为1μm,信号层为3

μm,溅射的铝符合半导体规范要求(含0.5%铜),线宽为20μm,线距为25μm,电源层之间介质厚度为3μm,信号层之间为7μm。

BCB的介电常数很低,只有2.65,耗散因子也低至0.0008。

对于速度为10GHz的信号,它的性能有点类似陶瓷,但频率再高上去其性能就开始下降,在95GHz时1cm线上会有3dB衰减。

因为金属层很薄,所以存在一定的直流电阻,约为5Ω/cm,这一点在设计时要考虑到,远端应用应使用较短的布线,但它对改善系统内的耗散噪声有一定帮助。

设计中使用的通孔直接在BCB上作出。

3x 制作使用50μm焊盘和30μm导孔,孔壁略为倾斜,接触点约为20μm。

通孔电阻很小,能通过较大电流,通孔成形过程比目前90%设计工艺都要好。

BCB每层形成后都要经过一次软固化,最后一次固化温度为250℃。

固化使叠层各层相互连接,形成一个中间有引线的固化BCB。

基底材料耐温性使之可用于无铅贴装工艺,包括倒装芯片裸片贴装工艺。

另外还有一种热通孔用于直接连接硅晶圆载体,并为大功率元件提供一个低阻热通道。

该项工艺的主要工序为:旋转涂覆、热固化、溅射、掩膜对位和UV曝光、显影、湿法及干法刻蚀。

基片以晶圆形式提供给最终用户。

趋势及未来展望:

六西格玛品质论坛小型MCP的增长需求来自于一些大批量应用消费类产品,如移动电话、掌上电脑和上网记事本、MP3播放机以及其它手持装置,这些产品不仅对价位很敏感,而且要求有较短的产品和改进周期,而这两个要求系统级芯片ASIC技术和嵌入式存储器技术制造工艺却又无法满足。

低成本多芯片封装可作为这些市场所追求的“快速廉价”解决方案,许多来自半导体供应商和OEM的应用都要求将一个快闪

存储器和一个逻辑电路,如微处理器、DSP或ASIC结合在一起。

这些非常简单的MCP设计装配和测试成品率都大于98%,避免了“原本好裸片后来又不好”(KGD)

之类的问题。

今后还将把裸片以倒装芯片形式与硅基底相连,或者与一个重新布线的载体裸片相连用于叠层元件封装中,这种布线技术能在制成的半导体晶圆裸片上提供高密度多层再布线和感应极小的功率分配。

最后,在多芯片封装中将多个倒装芯片贴到硅基底上,这个基底就可以作为封装件,再用大的回流焊球或柱将基底贴到线路板上。

多芯片模块虽然可以提供极高的互连密度,但其高昂的成本一直限制了它的使用。

近年来研究人员又提出了一种和多芯片相对的少芯片封装概念,它克服了以往设计的不足,能满足目前电子产品在成本和功能上的要求。

90年代初期,多芯片模块(MCM)曾被认为是最佳互连封装技术,可以满足不断发展的电子工业的要求。

MCM技术将多个裸片固定在一个基板上连在一起,裸片之间非常接近,可以减少互连延迟。

L

当时一个典型的MCM可能含有二十多个裸片,密封在一块低温共烧陶瓷(LTCC)或沉积基板上。

MCM通常用于军事、航天或高性能计算机设备上,这类应用一般不太计较价格。

虽然IBM和富士通都在他们的大型计算机中使用了MCM并取得成功,但MCM 从未在商业上达到预期的效果。

由于裸片测试和基板返修方面的原因,MCM一直没有能在PC/工作站这个利润非常高的庞大市场中得到广泛采用。

此外只要一个器件失效,基板连带上面好的器件都得扔掉,所以这是一种商用上无法接受的高成本技术。

最近两三年来,MCM技术通过少芯片封装(FCP)的形式获得了新生。

FCP有时也称为多重芯片封装(MCP),已有越来越多的公司出于技术和商业的原因正在接受FCP。

虽然这些FCP看起来与它们的单芯片同类没什么区别,但它们确实完全不同于90年代初期的MCM,今天的FCP不再使用多达二十个的裸片,一般只用2~4个裸片装在球栅阵列封装基板上(图1)。

这一“再生”应部分归功于裸片测试和运送技术的改善以及低成本高性能基板的出现,随着FCP逐渐成为系统级芯片(SoC)的替代方案,进一步还产生了系统级封装(SiP)。