IT公司速查手册-IT人士求职参考-2008

it行业的简历模板(标准版)

it行业的简历模板一份好的求职简历,是it行业求职者推销自己的有力宣言。

以下是要与大家分享的it行业的简历模板,供大家参考!it行业的简历模板(一) 基本资料姓名: xxx性别:男民族:汉族政治面貌:党员出生日期: 1985年9月婚姻状况:未婚学历:本科毕业院校: xx大学毕业时间: 20xx年06月所学专业:电子信息工程外语水平:英语 (一般)电脑水平:熟练联系方式:个人邮箱:求职意向工作类型:全职单位性质:不限期望行业:计算机、互联网、电子商务、通讯、电信业期望职位:网络工程师、IT工程师、系统管理员工作地点:不限期望月薪:面议教育经历20xx.09-20xx.06 xx大学通信与电子学院电子信息程本科主修课程计算机、网络工程、ESP、机械制图、单片机、交换原理、数据库、通信网、C语言、电路原理工作经验20xx.07-20xx.06 电脑城技术人员工作内容:1、负责电脑装机及系统按装2、结构化布局及调3、售后服务及系统维护4、熟悉internet/intranet网的调试及维护专业技能精通办公自动化软件的应用及管理,网络维护与应用能熟练使用PHOTOSHOP/ACDSEE看图工具对网络安全知识了解了解交换机、路由器及虚拟网专网的配置自我评价本人是一个工作认真负责积极主动善于团结工作的人。

对工作有极高的热情,乐于接受新的挑战,且独立完成工作能力强,性格开朗,善于与人交往,有团队精神。

精力充沛对未来的工作和生活充满信心。

it行业的简历模板(二) 刘先生目前所在:天河区年龄: 27户口所在:汕尾国籍:中国婚姻状况:未婚民族:汉族身高: 172 cm体重:求职意向人才类型:普通求职应聘职位:后期制作,平面设计师,文案/策划/美术指导工作年限: 3职称:求职类型:全职可到职日期:一个月月薪要求:希望工作地区:广州,深圳,工作经历**公司起止年月:20xx-07 ~至今公司性质:外商独资所属行业:机械/机电/设备/重工担任职位: IT工程师工作描述:主要负责公司平面设计工作(海报设计,书刊排版,视频编辑,网站美工,展会与门市布置设计等),主导其他人员的设计工作及资料管理。

IT企业员工手册.doc

IT企业员工手册公司鼓励员工发扬开拓创新精神,能适应市场竞争的形势,锐意革新,敢于在强手如林的同行中创出一流的水平。

2.公司鼓励员工有积极进取的价值观和人生观,关心社会问题,关心公益事业。

在公司和住所都要处理好与社区的关系,争创最佳的社会形象。

3.公司参与社会的公平竞争,以合理的价格,周到的服务,服务于社会。

4.公司要求员工全力维护公司形象,爱护并宣扬公司名、公司徽标、公司商标、商品名、商品的包装等。

二、从个体上塑造公司形象作为公司朝气激情的创业团队中的一员,各位员工的仪表、仪容、谈吐、举止、行为,不再仅仅是个人文化素质的直观反映,更是公司形象的再现。

公众的亲疏,客户的取舍,将与每一位员工的个体形象息息相关。

1.、形象意识公司要求员工必须具备强烈的形象意识,从基本做起,塑造良好个人形象。

2.、员工仪容仪表员工衣着应当合乎企业形象及部门形象,原则上员工穿着及修饰应稳重大方,整齐清爽,干净利落。

3、社交、谈吐(1)在交谈中善于倾听,不随便打断他人谈话,不鲁莽提问,不问及他人隐私,不要言语纠缠不清或语带讽刺,更勿出言不逊,恶语伤人。

(2)与客户交谈诚恳、热情、不卑不亢,语言流利、准确。

业务之外,注意话题健康、客观。

采用迎送礼节,主动端茶送水。

(3)与同行交谈,注意措辞分寸,谦虚谨慎,维护公司形象,不互相倾轧,客观正派,不涉及同行机密。

4、举止、行为(1)遵守考勤制度,准时上、下班,不迟到、早退。

病假、事假需及时申请或通知部门主管,填报请假单。

(2)办公室内禁止吸烟,保持良好的精神状态,精力饱满,乐观进取。

(3)对待上司要尊重,对待同事要热情,处理工作保持头脑冷静,提倡微笑待人,微笑服务。

(4)开诚布公,坦诚待人,平等尊重,团结协作,不将个人喜好带进工作中,不拉帮结派,党同伐异。

(5)热情接待每一位来宾,不以貌取人,不盛气凌人,与客人约见要准时,如另有客人来访需等待时,应主动端茶道歉。

(6)保持良好坐姿、行姿,切勿高声呼叫他人。

ARM指令速查手册

ARM Instruction SetQuick Reference CardKey to Tables{cond}Refer to Table Condition Field {cond}<a_mode2>Refer to Table Addressing Mode 2<Oprnd2>Refer to Table Operand 2<a_mode2P>Refer to Table Addressing Mode 2 (Post-indexed only)<fields>Refer to Table PSR fields<a_mode3>Refer to Table Addressing Mode 3{S}Updates condition flags if S present<a_mode4L>Refer to Table Addressing Mode 4 (Block load or Stack pop) C*, V*Flag is unpredictable after these instructions in Architecture v4 and earlier<a_mode4S>Refer to Table Addressing Mode 4 (Block store or Stack push) Q Sticky flag. Always updates on overflow (no S option). Read and reset using MRS and MSR<a_mode5>Refer to Table Addressing Mode 5x,y B meaning half-register [15:0], or T meaning [31:16]<reglist> A comma-separated list of registers, enclosed in braces ( { and } )<immed_8r> A 32-bit constant, formed by right-rotating an 8-bit value by an even number of bits{!}Updates base register after data transfer if ! present<immed_8*4> A 10-bit constant, formed by left-shifting an 8-bit value by two bits§Refer to Table ARM architecture versionsOperation§Assembler S updates Q Action NotesMove Move MOV{cond}{S} Rd, <Oprnd2>N Z C Rd := Oprnd2NOT MVN{cond}{S} Rd, <Oprnd2>N Z C Rd := 0xFFFFFFFF EOR Oprnd2SPSR to register3MRS{cond} Rd, SPSR Rd := SPSRCPSR to register3MRS{cond} Rd, CPSR Rd := CPSRregister to SPSR3MSR{cond} SPSR_<fields>, Rm SPSR := Rm (selected bytes only)register to CPSR3MSR{cond} CPSR_<fields>, Rm CPSR := Rm (selected bytes only)immediate to SPSR3MSR{cond} SPSR_<fields>, #<immed_8r>SPSR := immed_8r (selected bytes only)immediate to CPSR3MSR{cond} CPSR_<fields>, #<immed_8r>CPSR := immed_8r (selected bytes only)Arithmetic Add ADD{cond}{S} Rd, Rn, <Oprnd2>N Z C V Rd := Rn + Oprnd2with carry ADC{cond}{S} Rd, Rn, <Oprnd2>N Z C V Rd := Rn + Oprnd2 + Carrysaturating5E QADD{cond} Rd, Rm, Rn Q Rd := SAT(Rm + Rn)No shift/rotate.double saturating5E QDADD{cond} Rd, Rm, Rn Q Rd := SAT(Rm + SAT(Rn * 2))No shift/rotate.Subtract SUB{cond}{S} Rd, Rn, <Oprnd2>N Z C V Rd := Rn - Oprnd2with carry SBC{cond}{S} Rd, Rn, <Oprnd2>N Z C V Rd := Rn - Oprnd2 - NOT(Carry)reverse subtract RSB{cond}{S} Rd, Rn, <Oprnd2>N Z C V Rd := Oprnd2 - Rnreverse subtract with carry RSC{cond}{S} Rd, Rn, <Oprnd2>N Z C V Rd := Oprnd2 - Rn - NOT(Carry)saturating5E QSUB{cond} Rd, Rm, Rn Q Rd := SAT(Rm - Rn)No shift/rotate.double saturating5E QDSUB{cond} Rd, Rm, Rn Q Rd := SAT(Rm - SAT(Rn * 2))No shift/rotate.Multiply2MUL{cond}{S} Rd, Rm, Rs N Z C*Rd := (Rm * Rs)[31:0]accumulate2MLA{cond}{S} Rd, Rm, Rs, Rn N Z C*Rd := ((Rm * Rs) + Rn)[31:0]unsigned long M UMULL{cond}{S} RdLo, RdHi, Rm, Rs N Z C*V*RdHi,RdLo := unsigned(Rm * Rs)unsigned accumulate long M UMLAL{cond}{S} RdLo, RdHi, Rm, Rs N Z C*V*RdHi,RdLo := unsigned(RdHi,RdLo + Rm * Rs)signed long M SMULL{cond}{S} RdLo, RdHi, Rm, Rs N Z C*V*RdHi,RdLo := signed(Rm * Rs)signed accumulate long M SMLAL{cond}{S} RdLo, RdHi, Rm, Rs N Z C*V*RdHi,RdLo := signed(RdHi,RdLo + Rm * Rs)signed 16 * 16 bit5E SMULxy{cond} Rd, Rm, Rs Rd := Rm[x] * Rs[y]No shift/rotate.signed 32 * 16 bit5E SMULWy{cond} Rd, Rm, Rs Rd := (Rm * Rs[y])[47:16]No shift/rotate.signed accumulate 16 * 165E SMLAxy{cond} Rd, Rm, Rs, Rn Q Rd := Rn + Rm[x] * Rs[y]No shift/rotate.signed accumulate 32 * 165E SMLAWy{cond} Rd, Rm, Rs, Rn Q Rd := Rn + (Rm * Rs[y])[47:16]No shift/rotate.signed accumulate long 16 * 165E SMLALxy{cond} RdLo, RdHi, Rm, Rs RdHi,RdLo := RdHi,RdLo + Rm[x] * Rs[y]No shift/rotate.Count leading zeroes5CLZ{cond} Rd, Rm Rd := number of leading zeroes in RmLogical Test TST{cond} Rn, <Oprnd2>N Z C Update CPSR flags on Rn AND Oprnd2 Test equivalence TEQ{cond} Rn, <Oprnd2>N Z C Update CPSR flags on Rn EOR Oprnd2AND AND{cond}{S} Rd, Rn, <Oprnd2>N Z C Rd := Rn AND Oprnd2EOR EOR{cond}{S} Rd, Rn, <Oprnd2>N Z C Rd := Rn EOR Oprnd2ORR ORR{cond}{S} Rd, Rn, <Oprnd2>N Z C Rd := Rn OR Oprnd2Bit Clear BIC{cond}{S} Rd, Rn, <Oprnd2>N Z C Rd := Rn AND NOT Oprnd2No operation NOP R0 := R0Flags not affected.Shift/Rotate See Table Operand 2. Compare Compare CMP{cond} Rn, <Oprnd2>N Z C V Update CPSR flags on Rn - Oprnd2negative CMN{cond} Rn, <Oprnd2>N Z C V Update CPSR flags on Rn + Oprnd2Vector Floating Point Instruction SetQuick Reference CardKey to Tables{cond}See Table Condition Field (on ARM side).{E} E : raise exception on any NaN. Without E : raise exception only on signaling NaNs.<S/D>S (single precision) or D (double precision).{Z}Round towards zero. Overrides FPSCR rounding mode.<S/D/X>As above, or X (unspecified precision).<VFPregs> A comma separated list of consecutive VFP registers, enclosed in braces ( { and } ).Fd, Fn, Fm Sd, Sn, Sm (single precision), or Dd, Dn, Dm (double precision).<VFPsysreg>FPSCR, or FPSID.Operation Assembler Exceptions Action NotesVector arithmetic Multiply FMUL<S/D>{cond} Fd, Fn, Fm IO, OF, UF, IX Fd := Fn * Fmnegative FNMUL<S/D>{cond} Fd, Fn, Fm IO, OF, UF, IX Fd := - (Fn * Fm)accumulate FMAC<S/D>{cond} Fd, Fn, Fm IO, OF, UF, IX Fd := Fd + (Fn * Fm)deduct FNMAC<S/D>{cond} Fd, Fn, Fm IO, OF, UF, IX Fd := Fd - (Fn * Fm)Exceptionsnegate and accumulate FMSC<S/D>{cond} Fd, Fn, Fm IO, OF, UF, IX Fd := -Fd + (Fn * Fm)IO Invalid operationnegate and deduct FNMSC<S/D>{cond} Fd, Fn, Fm IO, OF, UF, IX Fd := -Fd - (Fn * Fm)OF Overflow Add FADD<S/D>{cond} Fd, Fn, Fm IO, OF, IX Fd := Fn + Fm UF UnderflowSubtract FSUB<S/D>{cond} Fd, Fn, Fm IO, OF, IX Fd := Fn - Fm IX Inexact resultDivide FDIV<S/D>{cond} Fd, Fn, Fm IO, DZ, OF, UF, IX Fd := Fn / Fm DZ Division by zeroCopy FCPY<S/D>{cond} Fd, Fm Fd := FmAbsolute FABS<S/D>{cond} Fd, Fm Fd := abs(Fm)Negative FNEG<S/D>{cond} Fd, Fm Fd := -FmSquare root FSQRT<S/D>{cond} Fd, Fm IO, IX Fd := sqrt(Fm)Scalar compare FCMP{E}<S/D>{cond} Fd, Fm IO Set FPSCR flags on Fd - Fm Use FMSTAT to transfer flags.Compare with zero FCMP{E}Z<S/D>{cond} Fd IO Set FPSCR flags on Fd - 0Use FMSTAT to transfer flags.Scalar convert Single to double FCVTDS{cond} Dd, Sm IO Dd := convertStoD(Sm)Double to single FCVTSD{cond} Sd, Dm IO, OF, UF, IX Sd := convertDtoS(Dm)Unsigned integer to float FUITO<S/D>{cond} Fd, Sm Fd := convertUItoF(Sm)Signed integer to float FSITO<S/D>{cond} Fd, Sm IX Fd := convertSItoF(Sm)Float to unsigned integer FTOUI{Z}<S/D>{cond} Sd, Fm IO, IX Sd := convertFtoUI(Fm)Float to signed integer FTOSI{Z}<S/D>{cond} Sd, Fm IO, IX Sd := convertFtoSI(Fm) Save VFP registers FST<S/D>{cond} Fd, [Rn{, #<immed_8*4>}][address] := FdMultiple, unindexed FSTMIA<S/D/X>{cond} Rn, <VFPregs>Saves list of VFP registers, starting at address in Rn.increment after FSTMIA<S/D/X>{cond} Rn!, <VFPregs>synonym: FSTMEA (empty ascending)decrement before FSTMDB<S/D/X>{cond} Rn!, <VFPregs>synonym: FSTMFD (full descending) Load VFP registers FLD<S/D>{cond} Fd, [Rn{, #<immed_8*4>}]Fd := [address]Multiple, unindexed FLDMIA<S/D/X>{cond} Rn, <VFPregs>Loads list of VFP registers, starting at address in Rn.increment after FLDMIA<S/D/X>{cond} Rn!, <VFPregs>synonym: FLDMFD (full descending)decrement before FLDMDB<S/D/X>{cond} Rn!, <VFPregs>synonym: FLDMEA (empty ascending) Transfer registers ARM to single FMSR{cond} Sn, Rd Sn := RdSingle to ARM FMRS{cond} Rd, Sn Rd := SnARM to lower half of double FMDLR{cond} Dn, Rd Dn[31:0] := Rd Use with FMDHR.Lower half of double to ARM FMRDL{cond} Rd, Dn Rd := Dn[31:0]Use with FMRDH.ARM to upper half of double FMDHR{cond} Dn, Rd Dn[63:32] := Rd Use with FMDLR.Upper half of double to ARM FMRDH{cond} Rd, Dn Rd := Dn[63:32]Use with FMRDL.ARM to VFP system register FMXR{cond} <VFPsysreg>, Rd VFPsysreg := Rd Stalls ARM until all VFP ops complete.VFP system register to ARM FMRX{cond} Rd, <VFPsysreg>Rd := VFPsysreg Stalls ARM until all VFP ops complete.FPSCR flags to CPSR FMSTAT{cond}CPSR flags := FPSCR flags Equivalent to FMRX R15, FPSCRFPSCR format Rounding(Stride - 1)*3Vector length - 1Exception trap enable bits Cumulative exception bits 3130292824232221201817161211109843210 N Z C V FZ RMODE STRIDE LEN IXE UFE OFE DZE IOE IXC UFC OFC DZC IOC FZ: 1 = flush to zero mode.Rounding: 0 = round to nearest, 1 = towards +∞, 2 = towards -∞, 3 = towards zero.(Vector length * Stride) must not exceed 4 for double precision operands.If Fd is S0-S7 or D0-D3, operation is Scalar (regardless of vector length).If Fd is S8-S31 or D4-D15, and Fm is S0-S7 or D0-D3, operation is Mixed (Fm scalar, others vector).If Fd is S8-S31 or D4-D15, and Fm is S8-S31 or D4-D15, operation is Vector.S0-S7 (or D0-D3), S8-S15 (D4-D7), S16-S23 (D8-D11), S24-S31 (D12-D15) each form a circulating bank of registers.All Thumb registers are Lo (R0-R7) except where specified. Hi registers are R8-R15.Operation§Assembler UpdateflagsAction NotesMove Immediate MOV Rd, #<immed_8> Rd := immed_88-bit immediate value.Lo to Lo MOV Rd, Rm Rd := RmHi to Lo, Lo to Hi, Hi to Hi MOV Rd, Rm!Rd := Rm Not Lo to LoArithmetic Add ADD Rd, Rn, #<immed_3> Rd := Rn + immed_33-bit immediate value.Lo and Lo ADD Rd, Rn, Rm Rd := Rn + RmHi to Lo, Lo to Hi, Hi to Hi ADD Rd, Rm!Rd := Rd + Rm Not Lo to Loimmediate ADD Rd, #<immed_8> Rd := Rd + immed_88-bit immediate value.with carry ADC Rd, Rm Rd := Rd + Rm + C-bitvalue to SP ADD SP, #<immed_7*4>!SP := SP + immed_7 * 49-bit immediate value (word-aligned).form address from SP ADD Rd, SP, #<immed_8*4>!Rd := SP + immed_8 * 410-bit immediate value (word-aligned).form address from PC ADD Rd, PC, #<immed_8*4>!Rd := (PC AND 0xFFFFFFFC) + immed_8 * 410-bit immediate value (word-aligned).Subtract SUB Rd, Rn, Rm Rd := Rn - Rmimmediate 3SUB Rd, Rn, #<immed_3> Rd := Rn - immed_33-bit immediate value.immediate 8SUB Rd, #<immed_8> Rd := Rd - immed_88-bit immediate value.with carry SBC Rd, Rm Rd := Rd - Rm - NOT C-bitvalue from SP SUB SP, #<immed_7*4>!SP := SP - immed_7 * 49-bit immediate value (word-aligned).Negate NEG Rd, Rm Rd := - RmMultiply MUL Rd, Rm Rd := Rm * RdCompare CMP Rn, Rm update CPSR flags on Rn - Rm Can be Lo to Lo, Lo to Hi, Hi to Lo, or Hi to Hi.negative CMN Rn, Rm update CPSR flags on Rn + Rmimmediate CMP Rn, #<immed_8> update CPSR flags on Rn - immed_88-bit immediate value.No operation NOP!R8 := R8Flags not affected.Logical AND AND Rd, Rm Rd := Rd AND RmExclusive OR EOR Rd, Rm Rd := Rd EOR RmOR ORR Rd, Rm Rd := Rd OR RmBit clear BIC Rd, Rm Rd := Rd AND NOT RmMove NOT MVN Rd, Rm Rd := NOT RmTest bits TST Rn, Rm update CPSR flags on Rn AND RmShift/rotate Logical shift left LSL Rd, Rm, #<immed_5> Rd := Rm << immed_55-bit immediate shift. Allowed shifts 0-31.LSL Rd, Rs Rd := Rd << RsLogical shift right LSR Rd, Rm, #<immed_5> Rd := Rm >> immed_55-bit immediate shift. Allowed shifts 1-32.LSR Rd, Rs Rd := Rd >> RsArithmetic shift right ASR Rd, Rm, #<immed_5> Rd := Rm ASR immed_55-bit immediate shift. Allowed shifts 1-32.ASR Rd, Rs Rd := Rd ASR RsRotate right ROR Rd, Rs Rd := Rd ROR RsBranch Conditional branch B{cond} label R15 := label label must be within -252 to +258 bytes of current instruction.See Table Condition Field (ARM side). AL not allowed.Unconditional branch B label R15 := label label must be within ±2Kb of current instruction.Long branch with link BL label R14 := R15 - 2, R15 := label Encoded as two Thumb instructions.label must be within ±4Mb of current instruction.Branch and exchange BX Rm R15 := Rm AND 0xFFFFFFFE Change to ARM state if Rm[0] = 0.Branch with link and exchange5T BLX label R14 := R15 - 2, R15 := labelChange to ARM Encoded as two Thumb instructions.label must be within ±4Mb of current instruction.Branch with link and exchange5T BLX Rm R14 := R15 - 2, R15 := Rm AND 0xFFFFFFFEChange to ARM if Rm[0] = 0SoftwareInterruptSWI <immed_8>Software interrupt processor exception8-bit immediate value encoded in instruction. Breakpoint5T BKPT <immed_8>Prefetch abort or enter debug stateENGLANDARM LtdFulbourn RoadCherry HintonCambridge CB1 9JNUKTelephone:+44 1223 400400 Facsimile:+44 1223 400410 Email:info@ GERMANYARM LtdOtto-Hahn Str. 13b85521 Ottobrun-RiemerlingMunichGermanyTelephone:+49 89 608 75545Facsimile:+49 98 608 75599Email:info@USAARM Inc750 University AvenueSuite 150,Los Gatos CA 95032USATelephone:+1 408 579 2207Facsimile:+1 408 579 1205Email:info@JAPANARM KKPlustaria Building 4F,3-1-4 Shinyokohama, Kohoku-ku,Yokohama-shi, 222-0033JapanTelephone:+81 45 477 5260Facsimile:+81 45 477 5261Email:info@KOREAARMRoom #1115, Hyundai Building9-4, Soonae-Dong, Boondang-KuSungnam, Kyunggi-DoKorea 463-020Telephone:+82 342 712 8234Facsimile:+82 342 713 8225Email: info@Operation§Assembler Action NotesLoad with immediate offset, word LDR Rd, [Rn, #<immed_5*4>]Rd := [Rn + immed_5 * 4]halfword LDRH Rd, [Rn, #<immed_5*2>]Rd := ZeroExtend([Rn + immed_5 * 2][15:0])Clears bits 31:16byte LDRB Rd, [Rn, #<immed_5>]Rd := ZeroExtend([Rn + immed_5][7:0])Clears bits 31:8 with register offset, word LDR Rd, [Rn, Rm]Rd := [Rn + Rm]halfword LDRH Rd, [Rn, Rm]Rd := ZeroExtend([Rn + Rm][15:0])Clears bits 31:16signed halfword LDRSH Rd, [Rn, Rm]Rd := SignExtend([Rn + Rm][15:0])Sets bits 31:16 to bit 15byte LDRB Rd, [Rn, Rm]Rd := ZeroExtend([Rn + Rm][7:0])Clears bits 31:8signed byte LDRSB Rd, [Rn, Rm]Rd := SignExtend([Rn + Rm][7:0])Sets bits 31:8 to bit 7 PC-relative LDR Rd, [PC, #<immed_8*4>]Rd := [(PC AND 0xFFFFFFFC) + immed_8 * 4]SP-relative LDR Rd, [SP, #<immed_8*4>]Rd := [SP + immed_8 * 4]Multiple LDMIA Rn!, <reglist>Loads list of registers Always updates base register. Store with immediate offset, word STR Rd, [Rn, #<immed_5*4>][Rn + immed_5 * 4] := Rdhalfword STRH Rd, [Rn, #<immed_5*2>][Rn + immed_5 * 2][15:0] := Rd[15:0]Ignores Rd[31:16]byte STRB Rd, [Rn, #<immed_5>][Rn + immed_5][7:0] := Rd[7:0]Ignores Rd[31:8] with register offset, word STR Rd, [Rn, Rm][Rn + Rm] := Rdhalfword STRH Rd, [Rn, Rm][Rn + Rm][15:0] := Rd[15:0]Ignores Rd[31:16]byte STRB Rd, [Rn, Rm][Rn + Rm][7:0] := Rd[7:0]Ignores Rd[31:8] SP-relative, word STR Rd, [SP, #<immed_8*4>][SP + immed_8 * 4] := RdMultiple STMIA Rn!, <reglist>Stores list of registers Always updates base register.Push/ Pop Push PUSH <reglist>Push registers onto stack Full descending stack. Push with link PUSH <reglist, LR>Push LR and registers onto stackPop POP <reglist>Pop registers from stackPop and return POP <reglist, PC>Pop registers, branch to address loaded to PCPop and return with exchange5T POP <reglist, PC>Pop, branch, and change to ARM state if address[0] = 0Proprietary NoticeARM is the trademark of ARM Ltd.Neither the whole nor any part of the information contained in, or the product described in, this reference card may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.The product described in this reference card is subject to continuous developments and improvements. All particulars of the product and its use contained in this reference card are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warrantiesof merchantability, or fitness for purpose, are excluded.This reference card is intended only to assist the reader in the use of the product. ARM Ltd shall not be liable for any loss or damage arising from the use of any information in this reference card, or any error or omission in such information, or any incorrect use of the product.Document NumberARM QRC 0001DChange LogIssue Date By ChangeA June 1995BJH First ReleaseB Sept 1996BJH Second ReleaseC Nov 1998BJH Third ReleaseD Oct 1999CKS Fourth ReleaseOperation§Assembler Action NotesBranch Branch B{cond} label R15 := label label must be within ±32Mb ofcurrent instruction.with link BL{cond} label R14 := R15-4, R15 := label label must be within ±32Mb ofcurrent instruction.and exchange4T BX{cond} Rm R15 := Rm, Change to Thumb if Rm[0] is 1with link and exchange (1)5T BLX label R14 := R15 - 4, R15 := label, Change to Thumb Cannot be conditional.label must be within ±32Mb ofcurrent instruction.with link and exchange (2)5T BLX{cond} Rm R14 := R15 - 4, R15 := Rm[31:1]Change to Thumb if Rm[0] is 1Load Word LDR{cond} Rd, <a_mode2>Rd := [address]User mode privilege LDR{cond}T Rd, <a_mode2P>branch (and exchange)LDR{cond} R15, <a_mode2>R15 := [address][31:1](§ 5T: Change to Thumb if [address][0] is 1)Byte LDR{cond}B Rd, <a_mode2>Rd := ZeroExtend[byte from address]User mode privilege LDR{cond}BT Rd, <a_mode2P>signed4LDR{cond}SB Rd, <a_mode3>Rd := SignExtend[byte from address]Halfword4LDR{cond}H Rd, <a_mode3>Rd := ZeroExtent[halfword from address]signed4LDR{cond}SH Rd, <a_mode3>Rd := SignExtend[halfword from address]Load multiple Pop, or Block data load LDM{cond}<a_mode4L> Rd{!}, <reglist-pc>Load list of registers from [Rd]return (and exchange)LDM{cond}<a_mode4L> Rd{!}, <reglist+pc>Load registers, R15 := [address][31:1](§ 5T: Change to Thumb if [address][0] is 1)Use from exception modes only.and restore CPSR LDM{cond}<a_mode4L> Rd{!}, <reglist+pc>^Load registers, branch (§ 5T: and exchange),CPSR := SPSRUser mode registers LDM{cond}<a_mode4L> Rd, <reglist-pc>^Load list of User mode registers from [Rd]Use from privileged modes only. Store Word STR{cond} Rd, <a_mode2>[address] := RdUser mode privilege STR{cond}T Rd, <a_mode2P>[address] := RdByte STR{cond}B Rd, <a_mode2>[address][7:0] := Rd[7:0]User mode privilege STR{cond}BT Rd, <a_mode2P>[address][7:0] := Rd[7:0]Halfword4STR{cond}H Rd, <a_mode3>[address][15:0] := Rd[15:0]Store multiple Push, or Block data store STM{cond}<a_mode4S> Rd{!}, <reglist>Store list of registers to [Rd]User mode registers STM{cond}<a_mode4S> Rd{!}, <reglist>^Store list of User mode registers to [Rd]Use from privileged modes only. Swap Word3SWP{cond} Rd, Rm, [Rn]temp := [Rn], [Rn] := Rm, Rd := tempByte3SWP{cond}B Rd, Rm, [Rn]temp := ZeroExtend([Rn][7:0]),[Rn][7:0] := Rm[7:0], Rd := tempCoprocessors Data operations2CDP{cond} p<cpnum>, <op1>, CRd, CRn, CRm, <op2>Coprocessor defined5CDP2 p<cpnum>, <op1>, CRd, CRn, CRm, <op2>Cannot be conditional.Move to ARM reg from coproc2MRC{cond} p<cpnum>, <op1>, Rd, CRn, CRm, <op2>5MRC2 p<cpnum>, <op1>, Rd, CRn, CRm, <op2>Cannot be conditional.Move to coproc from ARM reg2MCR{cond} p<cpnum>, <op1>, Rd, CRn, CRm, <op2>5MCR2 p<cpnum>, <op1>, Rd, CRn, CRm, <op2>Cannot be conditional.Load2LDC{cond} p<cpnum>, CRd, <a_mode5>5LDC2 p<cpnum>, CRd, <a_mode5>Cannot be conditional.Store2STC{cond} p<cpnum>, CRd, <a_mode5>5STC2 p<cpnum>, CRd, <a_mode5>Cannot be conditional.SWI{cond} <immed_24>Software interrupt processor exception24-bit value encoded in instruction. SoftwareinterruptBreakpoint5BKPT <immed_16>Prefetch abort or enter debug state Cannot be conditional.ARM Addressing ModesQuick Reference CardAddressing Mode 2 - Word and Unsigned Byte Data Transfer ARM architecture versionsPre-indexed Immediate offset[Rn, #+/-<immed_12>]{!}n ARM architecture version n and above.Zero offset[Rn]Equivalent to [Rn,#0]n T T variants of ARM architecture version n and above.Register offset[Rn, +/-Rm]{!}M ARM architecture version 3M, and 4 and above excluding xM variantsScaled register offset[Rn, +/-Rm, LSL #<immed_5>]{!}Allowed shifts 0-31n E E variants of ARM architecture version n and above.[Rn, +/-Rm, LSR #<immed_5>]{!}Allowed shifts 1-32[Rn, +/-Rm, ASR #<immed_5>]{!}Allowed shifts 1-32[Rn, +/-Rm, ROR #<immed_5>]{!}Allowed shifts 1-31Operand 2[Rn, +/-Rm, RRX]{!}Immediate value#<immed_8r>Post-indexed Immediate offset[Rn], #+/-<immed_12>Logical shift left immediate Rm, LSL #<immed_5>Allowed shifts 0-31 Register offset[Rn], +/-Rm Logical shift right immediate Rm, LSR #<immed_5>Allowed shifts 1-32Scaled register offset[Rn], +/-Rm, LSL #<immed_5>Allowed shifts 0-31Arithmetic shift right immediate Rm, ASR #<immed_5>Allowed shifts 1-32 [Rn], +/-Rm, LSR #<immed_5>Allowed shifts 1-32Rotate right immediate Rm, ROR #<immed_5>Allowed shifts 1-31[Rn], +/-Rm, ASR #<immed_5>Allowed shifts 1-32Register Rm[Rn], +/-Rm, ROR #<immed_5>Allowed shifts 1-31Rotate right extended Rm, RRX[Rn], +/-Rm, RRX Logical shift left register Rm, LSL RsLogical shift right register Rm, LSR RsAddressing Mode 2 (Post-indexed only)Arithmetic shift right register Rm, ASR RsPost-indexed Immediate offset[Rn], #+/-<immed_12>Rotate right register Rm, ROR RsZero offset[Rn]Equivalent to [Rn],#0Register offset[Rn], +/-RmScaled register offset[Rn], +/-Rm, LSL #<immed_5>Allowed shifts 0-31PSR fields(use at least one suffix)[Rn], +/-Rm, LSR #<immed_5>Allowed shifts 1-32Suffix Meaning[Rn], +/-Rm, ASR #<immed_5>Allowed shifts 1-32c Control field mask byte PSR[7:0][Rn], +/-Rm, ROR #<immed_5>Allowed shifts 1-31f Flags field mask byte PSR[31:24][Rn], +/-Rm, RRX s Status field mask byte PSR[23:16]x Extension field mask byte PSR[15:8]Addressing Mode 3 - Halfword and Signed Byte Data TransferPre-indexed Immediateoffset[Rn, #+/-<immed_8>]{!}Zero offset[Rn]Equivalent to [Rn,#0]Condition Field {cond}Register[Rn, +/-Rm]{!}Mnemonic Description Description (VFP)Post-indexed Immediate offset[Rn], #+/-<immed_8>EQ Equal Equal Register[Rn], +/-Rm NE Not equal Not equal, or unorderedCS / HS Carry Set / Unsigned higher or same Greater than or equal, or unordered Addressing Mode 4 - Multiple Data Transfer CC / LO Carry Clear / Unsigned lower Less thanBlock load Stack pop MI Negative Less thanIA Increment After FD Full Descending PL Positive or zero Greater than or equal, or unordered IB Increment Before ED Empty Descending VS Overflow Unordered (at least one NaN operand) DA Decrement After FA Full Ascending VC No overflow Not unorderedDB Decrement Before EA Empty Ascending HI Unsigned higher Greater than, or unorderedLS Unsigned lower or same Less than or equal Block store Stack push GE Signed greater than or equal Greater than or equalIA Increment After EA Empty Ascending LT Signed less than Less than, or unorderedIB Increment Before FA Full Ascending GT Signed greater than Greater thanDA Decrement After ED Empty Descending LE Signed less than or equal Less than or equal, or unordered DB Decrement Before FD Full Descending AL Always (normally omitted)Always (normally omitted)Addressing Mode 5 - Coprocessor Data TransferPre-indexed Immediate offset[Rn, #+/-<immed_8*4>]{!}Key to tablesZero offset[Rn]Equivalent to [Rn,#0]{!}Updates base register after data transfer if ! present. (Post-indexed always updates.) Post-indexed Immediate offset[Rn], #+/-<immed_8*4><immed_8r> A 32-bit constant, formed by right-rotating an 8-bit value by an even number of bits. Unindexed No offset[Rn], {8-bit copro. option}+/-+ or -. (+ may be omitted.)。

IT公司名录

IT公司名录一、引言IT行业是指信息技术产业,是当今社会中最为繁荣和快速发展的行业之一。

IT公司是这个行业中的重要参与者,为各种企业和个人提供信息技术相关的产品和服务。

本文将为大家介绍一些知名的IT公司,以便读者了解并选择适合自己需求的合作伙伴。

二、知名IT公司名录1. 谷歌(Google)谷歌是全球最大的互联网公司之一,成立于1998年。

该公司以搜索引擎技术起家,如今已发展成为提供广告服务、云计算、硬件设备、操作系统等多种产品和服务的综合性科技公司。

谷歌的创新能力和技术实力备受业界认可,是众多企业和开发者的首选合作伙伴。

2. 微软(Microsoft)微软是全球领先的软件和云服务提供商,成立于1975年。

该公司的产品包括操作系统、办公软件、开发工具、数据库等,广泛应用于个人和企业领域。

微软以其稳定可靠的产品和服务而闻名,为用户提供了丰富的选择和灵活的解决方案。

3. 苹果(Apple)苹果是全球著名的科技公司,成立于1976年。

该公司以设计、开发和销售消费电子产品和软件为主,旗下知名产品包括iPhone、iPad、Mac、Apple Watch等。

苹果以其独特的设计理念和卓越的用户体验而深受消费者喜爱,是全球IT行业的领军企业之一。

4. 亚马逊(Amazon)亚马逊是全球最大的电子商务和云计算公司,成立于1994年。

该公司以在线零售业务起家,如今已发展成为提供电子商务、云计算、人工智能等多元化服务的巨头企业。

亚马逊的强大供应链和丰富的产品种类吸引了众多消费者和企业的关注。

5. 腾讯(Tencent)腾讯是中国领先的互联网科技公司,成立于1998年。

该公司以即时通讯软件QQ起家,如今已发展成为提供社交媒体、在线游戏、云服务等多个领域的综合性科技企业。

腾讯以其强大的用户基础和丰富的互联网生态系统而著名,是中国IT行业的重要代表。

6. 阿里巴巴(Alibaba)阿里巴巴是中国著名的电子商务巨头,成立于1999年。

【中文版】华为认证手册 V3.0-20190509

8 如何获得华为认证

获得HCIA认证

• 通过HCIA笔试 • 证书有效期:三年 • 考试地点:Pearson VUE考试中心

获得HCIP认证

• 18个月内通过HCIP的一门或多门笔试 • 证书有效期:三年 • 考试地点:Pearson VUE考试中心

获得HCIE认证

• 18个月内通过HCIE的三门考试(笔试、实验、面试) • 证书有效期:两年 • 考试地点:Pearson VUE考试中心(笔试)&HCIE考试中心(实验与面试)

9 第三方考试平台介绍

认证考试是华为认证项目的组成部分,Pearson VUE作为华为认证笔试考试服务提供商,为考生提供良好的考试解决方案,通过计算 机化的考试模式,对涉及到实际应用的ICT学科的相关知识、能力和技巧进行评估。

Pearson VUE简介

Pearson VUE是全球计算机考试领域的领导者,业务以顶尖技术为基础,为全球客户和应试者提供可靠、高水平的考试发送服务。全 球已有450+家组织选择Pearson VUE帮助开发、管理、发送和推广考试项目。 Pearson VUE考试网络遍及180个国家,在全球拥有5000+个考试中心,其中在中国70个城市设置了近170家考试中心。

Pearson VUE考试操作指导

【特别提醒】考生首次使用华为账号在 Pearson VUE 预约华为认证考试前,须先在 Pearson VUE 网站补充完整的个人信息。

10.2.2 / 支付考试费用

考生在 Pearson VUE 支付考试费用主要有以下几种方式: (1)考试券支付(网站/客户服务中心/考试中心):考生在网站、考试中心或客户服务中心预约考试时可使用考试券。 (2)信用卡支付(网站/客户服务中心):考生在网站或者通过客户服务中心预约考试时可以选择信用卡支付。 (3)现金支付(考试中心):考生在考试中心现场可以通过现金支付认证考试费用。

职业信息库

职业信息库1.厦门易告网络科技有限公司职位职能:销售代表岗位职责:一份以QQ、MSN为主要沟通工具、电话辅助,主流客户为网络游戏运营商、网上商城等电子商务公司,无需拜访、无需出差的IT广告方案销售工作。

1、通过游戏开服列表、网站广告链接、关键字搜索、游戏运营群等各种方式寻找、联系合适的客户。

2、通过聊天工具、电话与客户保持联系、进行沟通,根据客户需求并结合公司情况,为意向客户提供适宜的市场推广方案。

岗位要求:1、能吃苦耐劳,亲和力,有良好的服务意识和团队合作精神,勇于挑战高薪,女性优先考虑;2、良好的表达沟通能力,有一定网络营销经验和技巧;3、中专以上学历,电子计算机、广告传媒等相关专业毕业优先;4、有互联网及网络广告相关工作经验,及有意向从事网络方面工作者,优先考虑。

2.得尔利(厦门)贸易有限公司职位职能:区域销售经理职位描述:岗位要求:两年以上销售经验,学历:高中,20-35岁。

底薪2000元以上。

职位描述:1、负责贯彻落实公司营销策略、政策和计划;2、负责制订本区域市场开拓、新产品推广计划,并组织实施与效果评估;3、负责对行业市场的目标客户进行攻关,并协助经销商进行市场开拓;4、负责收集、分析、整理、归档客户需求、竞争对手等市场信息;5、负责经销商和客户的业务接洽、咨询及关系维护;6、负责销售计划的分解、落实,并进行跟踪与评估;7、协助财务部做好经销商的信用管理工作;8、负责正常类、关注类和可疑不良类应收账款的催收,并协助做好呆账催收工作;9、负责经销商和客户的合同、资料和档案管理;10、负责品牌、价格管理,并协调处理业务冲突;提供市场违规行为的信息,并协助处理。

3.厦门市斯巴特进出口有限公司职位职能:市场/营销/拓展专员市场分析/调研人员职位描述:【岗位职责】1.协助策划与实施品牌活动;2.协助做好品牌管理;3.进行市场调查,收集消费者反馈信息,充分了解竞品情况;4.协助各项市场计划的具体实施。

CDP-01中文参考手册

检测中心线的校准

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

检测断开的印刷边的校准

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

检测断开线的校准

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-18

寻边传感器的停止区的设定 (对于寻线传感器 SE-26 可参见 “寻线传感器

SE-26停止区的设定") . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-18

1-721-B

CDP-01

05-25-07

目录表

目录

常规

关于CDP-01 运输和储存 产品包装

安全措施

机械安全措施 电气安全措施

安装

安装场所 安装

机械附件 电气连接 传感器/执行器的连接

启动

1. 插入连接的检查 2. 传感器的校准 3. 自动校准

操作使用的介绍

1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

批注本地保存成功开通会员云端永久保存去开通

CDP-01参考手册

05-25-07

CDP-01

1-721-B

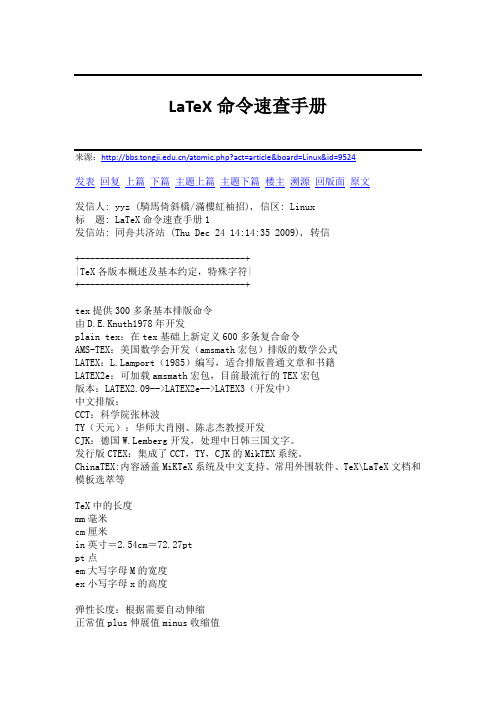

LaTeX命令速查手册

LaTeX命令速查手册来源:/atomic.php?act=article&board=Linux&id=9524发表回复上篇下篇主题上篇主题下篇楼主溯源回版面原文发信人: yyz (騎馬倚斜橋/滿樓紅袖招), 信区: Linux标题: LaTeX命令速查手册1发信站: 同舟共济站 (Thu Dec 24 14:14:35 2009), 转信+---------------------------------+|TeX各版本概述及基本约定,特殊字符|+---------------------------------+tex提供300多条基本排版命令由D.E.Knuth1978年开发plain tex:在tex基础上新定义600多条复合命令AMS-TEX:美国数学会开发(amsmath宏包)排版的数学公式LATEX:mport(1985)编写,适合排版普通文章和书籍LATEX2e:可加载amsmath宏包,目前最流行的TEX宏包版本:LATEX2.09-->LATEX2e-->LATEX3(开发中)中文排版:CCT:科学院张林波TY(天元):华师大肖刚、陈志杰教授开发CJK:德国W.Lemberg开发,处理中日韩三国文字。

发行版CTEX:集成了CCT,TY,CJK的MikTEX系统。

ChinaTEX:内容涵盖MiKTeX系统及中文支持、常用外围软件、TeX\LaTeX文档和模板选萃等TeX中的长度mm毫米cm厘米in英寸=2.54cm=72.27ptpt点em大写字母M的宽度ex小写字母x的高度弹性长度:根据需要自动伸缩正常值plus伸展值minus收缩值实际长度可超过正常值和伸展值之和,但不能小于正常值和收缩值之差\documentclass[11pt]{article}%11pt字体,普通文章%导言区,全局命令\usepackage{CJK}%使用CJK宏包\begin{document}%主环境\begin{CJK}{GBK}{song}%汉字必须放入CJK环境%其它字体:song,kai,fs,hei,li,you%CJK的两种环境CJK和CJK*%GBK是采用的字符集:GB,GBK,Bg5,GbtHi,This is my first \LaTeX file祝贺你,MikTex和CJK安装成功了\end{CJK}\ent{document}CJK和CJK*环境之间的切换\CJKspace和\CJKnospace\CJKtilde 重新定义~的长度基本约定分组{......}注释符:%西文标点后要加空格各种环境的开始和结束命令最好独占一行换行:连续两个回车,一个仅为空格输入特殊字符前加\的有:#$%{}~_^&\=\textbackslash|,<,>=$|$,$<$,$>$,$*$(中间星)*=*上面星特殊符号\s \p \dag \ddag \copyrigh版权号,\pounds 磅\TeX \LaTeX \LaTeXe \AmS-\LaTeX(最后这个要amsmath宏包)单引号:`'(1键前面的)双引号:``"+------------------------------+|段落、行距、水平间距、缩进命令|+------------------------------+强制分行:\\或\\*[和下行间距离]、\newline建议分行:\linebreak[0-4,数越大建议力度越大]\linebreak增加字间距,强制换行\nolinebreak[n]建议不分行\mbox{内容}内容保持在同一行分段:\par,或两个回车分页:自动分页强制分页:\newpage建议分页:\pagebreak[n],\nopagebreak[n]增加当前页高度有时可以避免难看的分页\enlargethispage{尺寸}可增加的最大高度\enlargethispage*{尺寸}指定增加高度水平间距:\quad 插入空白相当于当前字体大小\qquad=\quad×2\ ,=\quad×3/18~=好象比\ 小\hspace{宽度大小},\hspace*{宽度大小}\hfill弹性长度:hspace{\hfill}插入空白,撑满整行\hphantom{文本内容},占据文本内容的宽度\vphantom[文本内容},\phantom{文本内容}导引线:\dotfill,\hrulefill垂直间距:\vspace{高度}和\vspace*{高度}\vfill:相当于\vspace{\fill}\smallskip:-->\vspace{\smallskipamount}\medskip:-->\vspace{\medskipamount}\bigskip:-->\vspace{\bigskipamount}段落首行缩进:\setlength{\parindent}{2em},2个M\setlength{\parindent}{0pt},首行不缩进\CJKindent:两个汉字\indent与\noindent每节的第一段首行不会自动缩进\hspane{\parindent}在导言区加入:\usepackage{indentfirst}段落间距:\lineskip+\parskip可用\setlength修改以上值行距:\baselineskip:相邻两行基线间距离\baselinestretch:伸展因子修改改变行距:\renewcommand{\baselinestretch}[1.2] 放在\begin{document}之后,字体尺寸改变时才生效+----------------------------------+|西文字体属性、及中文字体属性、命令|+----------------------------------+字体有5种属性族:\rmfamily:罗马字体\sffamily:无衬线字体\ttfamily:打字机字体形状:(shape)直立斜\upshape:直立\itshape:意大利斜体\slshape:斜体\scshape:小体大写系列:(series)宽度黑度\mdseries:中等权重(黑)\bfseries:粗体\normalfont:默认字体,中等权重直立罗马字体西文尺寸:10pt,11pt,12pt\em强调,一般为斜体以上命令称为声明(无参数)每一声明对应字体命令命令只对其参数中的文本起作用族:\testrm{},\testsf{},\testtt{}形状\textup{},\textit{},\textsl{},\textsc{}系列\textmd{},\textbf{}默认值:\textnormal{}强调:\emph{}定义了基本尺寸后,可使用下面的声明来改变字体\tiny 5pt\scriptsize 7pt\footnotesize 8pt\small 9pt\normalsize 10pt\large 12pt\Large 14.4pt\LARGE 17.28pt\huge 20.74pt\Huge 24.88pt以上尺寸是基本尺寸为10pt时的大小所有西文字体命令对中文同样起作用italic和slanted斜体对中文一样中文书籍基本字号为5号约等于11pt使用GBK编码时,可同时输入简繁体。

客户开发专员简历模板

客户开发专员简历模板客户开发专员简历模板(一)个人基本简历姓名:国籍:中国目前所在地:民族:汉族户口所在地:身材: cm kg婚姻状况:未婚年龄:求职意向及工作经历人才类型:普通求职应聘职位:计算机类:软件工程师电子/邮电/通讯类软件工程师计算机类软件工程师工作年限: 4职称:无职称求职类型:全职可到职- 随时月薪要求:希望工作地区:个人工作经历: xx/07 -- 至今: xx通讯科技有限公司| 技术开发部 | 软件工程师负责公司相关网站的开发,及公司电信增值业务中短信与声讯的开发及维护。

对增值业务有比较深的了解。

在职期间有过短信业务与声讯业务的非常好的推广。

xx年3月 xx市xx科技发展有限公司(计算机职业技能培训中心)担任教师。

xx年7月 xx市xx科技发展有限公司分公司担任部门技术主管。

在职期间,主要负责该公司的C、C++、JAVA教学和网络维护工作及新项目的研究与开发。

能对一些突发事件做出应急的方案。

具有良好的服务意识。

xx年1月 xx市xx科技发展有限公司分公司xx职业技术学校xx职业技术培训中心,担任教务处长。

主要负责新项目的开展包括教材的定购、教师的聘请、学期的定制、教务的安排、证书的颁发等。

教育背景毕业院校: xx大学最高学历:本科毕业- xx-07-01所学专业:计算机科学与技术受教育培训经历: xx/09 -- xx/07:xx大学 | 计算机科学与技术 | 本科语言能力外语:英语良好国语水平:优秀粤语水平:一般工作能力及其他专长1.精通JAVA编程,有JSP、JAVABEAN、JDBC、SERVLET/JSP等开发经验;2.熟悉Tomecat、WebLogic等开发平台;3.熟练掌握Struts、Hibernate等框架的使用;4.熟练掌握Oracle,Sql Server,MySql等数据库;5.熟练应用面向对象的设计思想和设计模式,对MVC架构有很深入的了解;详细个人自传* 诚实守信,认真细致,有责任心,具有进取精神、实事求是的态度和自我管理能力* 自学能力强,并能够积极主动高效地学习新技术知识,有较好的文档编写能力* 能够与他人良好沟通、协作,具有良好的人际关系和交流能力,具有团队意识客户开发专员简历模板(二)个人信息大专1-2年工作经验现居xxx求职意向:求职程序员、软件工程师、手机软件开发工程师、集成电路/应用工程、CAD设计/制图、招聘专员/助理、游戏设计/开发、数据库管理/DBA想在 xx 工作期望薪资面议爱学习团队精神工作经验xx科技有限公司工作时间:xx年02月-xx年05月薪资水平: 5000-8000元/月在职职位:Android开发工程师工作职责:在工作中主要是项目中android的程序的编写,负责androidUI的搭建,根据产品的需求文档编写相应的代码,同时参与整个项目的逻辑分析和项目的整体进度,与项目经理进行沟通解决工作中存在的问题,使用一些常用及最新的框架及成熟的技术完成具体的任务和项目,和团队一起进行项目的跟进及的新技术发展,编写设计开发及实现文档,与团队一起参与产品需求分析并协助制定技术实施方案,帮助同事解决工作中遇到的难题,一起去完成公司中的项目,保证产品的正常运行,完成软件产品的开发及后期的维护。

IT行业知识介绍

IT行业知识介绍1. 什么是IT行业?IT(Information Technology)是指信息技术,广义指的是人类利用计算机和通信设备等信息工具进行信息的输入、处理、存储、传输和输出等活动的总称。

狭义上,IT专指计算机技术及其应用。

IT行业是指从事与计算机和通信技术相关的行业。

随着信息技术的快速发展,IT行业已经成为了现代社会的基石,涵盖了软件开发、网络技术、数据库管理、信息安全、云计算等多个领域。

2. IT行业的发展历程IT行业的发展从20世纪50年代开始,随着计算机的发明和普及,计算机技术也逐渐成为了一种行业。

最早的计算机是用来进行科学计算和数据处理的,而随着计算机的发展,人们开始将其应用到商业领域。

20世纪80年代,随着个人计算机的普及,IT行业进入了一个快速发展的阶段。

个人计算机给人们的生活和工作带来了巨大的便利,逐渐成为了人们生活中不可或缺的一部分。

随着互联网的兴起,IT行业进入了一个全新的时代。

互联网为人们提供了无限的学习、交流和创新空间,各种新型应用和服务也在不断涌现。

互联网的发展给IT行业带来了巨大的机遇,成为了IT行业最重要的发展驱动力。

3. IT行业的就业前景随着信息技术的不断进步和应用领域的扩大,IT行业的就业前景非常广阔。

根据统计数据显示,IT行业是全球最受欢迎的行业之一,每年都有大量的就业机会。

尤其是在、大数据、云计算和物联网等领域,IT行业的就业需求更加旺盛。

IT行业的就业前景不仅仅局限于技术岗位,还包括项目管理、产品设计、市场营销和顾问等职位。

IT行业需要各种各样的人才来推动其发展,因此有着广泛的就业机会,同时也为人们提供了丰厚的薪酬和发展空间。

4. IT行业需要具备哪些技能?在IT行业工作需要具备一定的技术和专业知识。

以下列举了一些常见的IT技能:•编程语言:掌握至少一门编程语言(如Java、Python、C++等)是进入IT行业的基本要求。

编程语言是开发软件和应用的基础,对于软件开发人员来说尤为重要。

组态王命令语言函数速查手册三

组态王命令语言函数速查手册北京亚控科技发展有限公司1命令语言函数速查手册“组态王”支持使用内建的复杂函数,其中包括字符串函数、数学函数、系统函数、控件函数、报表函数及其他函数,下面依次介绍各个函数(函数名不区分大小写,按字母排序):Abs此函数用于计算变量值的绝对值,使用格式如下:Abs(变量名或数值);返回值:整值或实型值;例如:Abs(14); 返回值为14Abs(-7.5); 返回值为7.5Abs(距离); 返回内存模拟变量“距离”的绝对值。

Ack对变量进行报警确认,或对报警组进行报警确认。

如果函数参数为变量名称,则只对该变量进行报警确认;如果函数参数为报警组名称,则确认所有属于该报警组及其子报警组的变量。

该函数的参数只能是变量名或报警组名,不可以为字符串变量。

此函数常用于按钮命令语言,当发生报警时,用此函数进行报警确认,它将产生确认报警事件。

调用格式:Ack(报警组名);或 Ack(变量名);例如:Ack(全厂);或 Ack(反应罐液位);组态王命令语言函数速查手册北京亚控科技发展有限公司2AckByTagName对变量进行报警确认。

函数参数可以是一个字符串变量,也可以是一个表示变量名的字符串。

调用格式:AckByTagName("tag_name");参数:tag_name:变量名。

例如:AckByTagName ("\\本站点\液位");AckByTagName(Varname);其中Varname 为字符串变量。

AckByGroupName对报警组进行确认。

调用格式:AckByGroupName( "station_name", "group_name" );station_name 为产生报警的IO 服务器名,group_name 为报警组名。

函数参数可以是字符串变量,也可以是表示IO 服务器名或报警组名的字符串。

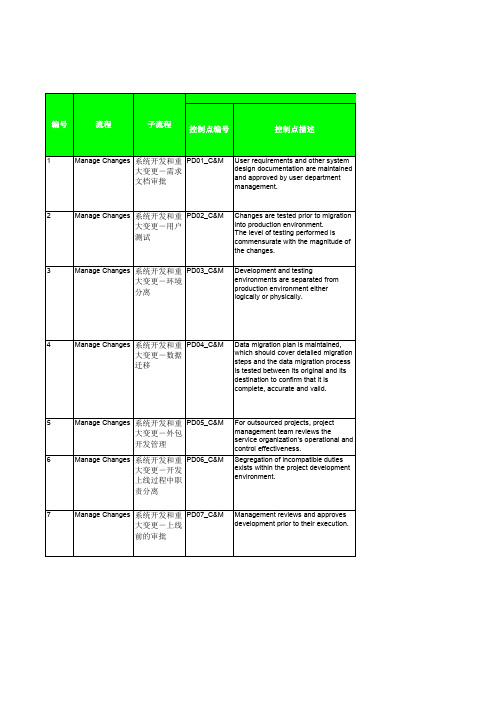

IT一般控制检查列表(中文版)

-紧急变更的

change process in a timely basis.

监控

21

Manage Changes 紧急程序变更 EC06_C&M Change development and testing

-环境分离

environments are separated from production environment either

destination to confirm that it is

complete, accurate and valid.

5

Manage Changes 系统开发和重 PD05_C&M For outsourced projects, project

大变更-外包 开发管理

management team reviews the service organization’s operational and control effectiveness.

logically or physically.

22

Manage Changes 配置/参数变 CP01_C&M The relevant management approval is

更-申请的审

required before implementing

批

configuration/parameter change to the

9

Manage Changes 系统日常变更 PC02_C&M Normal program change are tested

-用户测试

prior to migration into production environment.

伊顿产品速查手册V4

伊顿产品速查手册册 Eaton product

quick reference brochure

1

本手册为客户提供了 伊顿数据中心整体解决方案、典型应 用场景及推荐的 UPS 产品、Eaton 各系列 UPS、配电、 制冷、机柜产品 的优势介绍、主要参数,同时提供了常见问题的

回复术语和相关计算指导,使用者可以通过该手册快速查找到伊顿产 在不同行业的推荐应用方案,并根据产品特性及参数有针对性的进 行快速选型。 希望能够通过使用此速查手册,快速提升产品的拓展和应用能力。

热风 Eaton STS

DX RT 6K + 电池箱

冷风

解决方案组件

电源 ● DX RT ● 5PX ● 9PX

配电 ● STS ● ePDU

6

机柜 ● E系列机柜

H3C-ICG-信息通信网关速查手册

H中小型企业和行业机构对信息化要求日益强烈,但这类机构普遍缺少专业精细化的信息系统一体化方案。

采购支出与维护成本高,信息系统彼此割裂,缺乏持续保障的升级与维护,严重影响了中小型机构生产与办公效率。

华三通信技术有限公司(“以下简称H3C”)研制开发的业内首款信息通信网关(Information Communication Gateway,ICG)是专门为中小企业、行业区县机构和大型企业分支推出的综合信息通信服务产品。

信息通信网关产品简介H3C ICG(Information Communication Gateway)定位于运营商为行业用户、商业用户提供高水准的基础信息服务,目前有ICG1000、ICG 1800、ICG2000B、ICG2000、ICG 2000C、ICG3000、ICG5000等多款设备。

作为业界首个完善的信息通信网关产品系列,H3C ICG主要有以下产品特色:高度集成:ICG在硬件层面将路由器、交换机、防火墙、VPN网关、IAD、无线AP、应用加速器等设备集成为一台设备,提供丰富的WAN、LAN、语音、专线、无线、EPON等物理接口,从而达到便捷运营、统一维护的目的。

集中管理: ICG 产品适合运营商集中部署与维护,支持SNMP和TR069两种远程管理规范,可以采用H3C的智能网管中心iMC进行统一管理,也可以无缝集成到运营商现有的网管平台中。

ICG 产品也支持图形化界面的Web管理,方便企业管理人员简便维护与配置。

一站购齐: ICG内置软件业务丰富,政商企用户可以从运营商快捷购齐“线路+设备+业务+维护”的一站式服务。

ICG除了支持基础的路由、交换、NAT、DHCP、防火墙、访问策略控制、包过滤等功能外,更为大客户专门定制了防攻击、防病毒、应用限制、流量控制等高级业务,比现有的ADSL Modem或路由器、交换机设备更能满足客户多元化需求。

增值业务:通过扩展业务模块,ICG还能实现更多的应用层业务,为客户提供更精细的信息化服务。

IT企业员工手册内容简介

IT企业员工手册内容简介IT企业员工手册内容简介一、公司概况1. 公司介绍:包括公司的发展历史、使命和愿景、核心价值观等。

2. 组织结构:呈现公司的组织结构图和每个部门的职能和任务。

二、员工权益和责任1. 入职手续:包括入职需要准备的材料和手续,如身份证、劳动合同等。

2. 员工权益和福利:详细列出员工享受的各类福利和权益,如工资、加班补贴、五险一金、带薪年假等。

3. 员工责任和义务:概述员工在工作中应该遵守的规章制度和道德准则,如工作纪律、保守公司机密等。

三、办公流程和规章制度1. 办公时间和考勤:规定上班和下班时间,以及考勤制度和请假流程。

2. 工作目标和绩效评估:明确每个岗位的工作目标和绩效评估方式,并解释绩效奖励和升职机制。

3. 保密和知识产权保护:阐明员工在工作中对公司机密和客户信息的保护义务,以及对知识产权的尊重和保护。

4. 通信和信息安全:规定员工在使用公司通信设备和互联网时需要遵守的规定,如禁止传播违法信息、保护公司机密等。

5. 离职和解约:解释员工离职和解约的流程和注意事项。

四、培训和提升机会1. 入职培训:介绍新员工入职培训的内容和安排,以帮助他们尽快适应工作环境。

2. 职业发展和培训:概述公司提供的职业发展和培训机会,如内部培训、参加外部培训和会议等。

3. 员工关怀和激励:列举公司为员工提供的关怀和激励方式,如定期员工活动、团建等。

五、员工关系和合作1. 团队合作和文化:介绍公司的团队合作文化和价值观,鼓励员工之间的合作和沟通。

2. 内部沟通:说明内部沟通的渠道和工具,如公司内部邮件系统、工作交流平台等。

3. 员工关系处理:提供员工之间关系处理的建议和途径,如冲突解决渠道和积极的沟通方式。

六、安全和紧急处理1. 安全意识和防范:提醒员工在工作中注意安全,如防止意外伤害、电脑系统安全、数据备份等。

2. 紧急处理:列举紧急情况处理的应急电话和流程,如火灾、地震等。

七、企业文化和社会责任1. 企业文化:介绍公司的企业文化,并鼓励员工积极融入和践行企业文化。

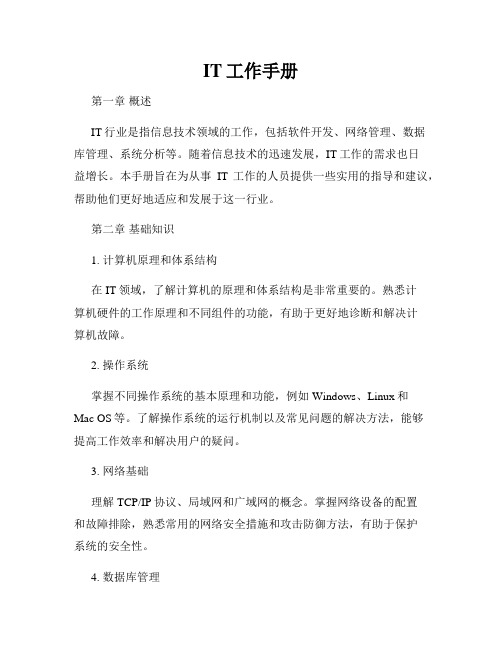

IT工作手册

IT工作手册第一章概述IT行业是指信息技术领域的工作,包括软件开发、网络管理、数据库管理、系统分析等。

随着信息技术的迅速发展,IT工作的需求也日益增长。

本手册旨在为从事IT工作的人员提供一些实用的指导和建议,帮助他们更好地适应和发展于这一行业。

第二章基础知识1. 计算机原理和体系结构在IT领域,了解计算机的原理和体系结构是非常重要的。

熟悉计算机硬件的工作原理和不同组件的功能,有助于更好地诊断和解决计算机故障。

2. 操作系统掌握不同操作系统的基本原理和功能,例如Windows、Linux和Mac OS等。

了解操作系统的运行机制以及常见问题的解决方法,能够提高工作效率和解决用户的疑问。

3. 网络基础理解TCP/IP协议、局域网和广域网的概念。

掌握网络设备的配置和故障排除,熟悉常用的网络安全措施和攻击防御方法,有助于保护系统的安全性。

4. 数据库管理熟悉关系型数据库的设计和管理,例如MySQL和Oracle等。

了解SQL语言和数据库优化的基本原则,能够提高数据库的性能和稳定性。

第三章技术技能1. 编程语言在IT行业中,掌握一门或多门编程语言是必不可少的。

常见的编程语言包括Java、Python、C++和JavaScript等。

根据工作需求选择合适的编程语言,熟练掌握其语法和应用,能够进行软件开发和系统维护。

2. Web开发了解HTML、CSS和JavaScript等前端开发技术,能够构建用户友好的网页界面。

熟悉Web服务器的配置和管理,具备后端开发技术,例如PHP或Node.js等,能够实现服务器端的逻辑处理和数据存储。

3. 数据分析IT行业对数据分析的需求越来越高。

学习和掌握数据分析工具和技术,例如Excel、Python的pandas库和SQL查询等,能够有效地分析和处理大量的数据,为企业的决策提供支持。

第四章软技能1. 沟通能力IT工作往往需要与团队成员、客户和其他部门进行沟通。

提升沟通能力,包括口头表达和书面沟通,在解决问题和协调工作中起到重要的作用。

嵌入式开发资料_Linux系统错误速查手册

33

EDOM

Math argument out of domain of func

esult not representable

35

EDEADLK

Resource deadlock would occur

EDEADLOCK

36

ENAMETOOLONG

CMS_SUBSYSTEM

CMS subsystem

D

DATA_MGMT_SUBSYSTEM

Data Management subsystem

E

MEMORY_ADMIN_SUBSYSTEM

Memory Management subsystem

F

FRAMEWORK_SVCS_SUBSYSTEM

Framework Service subsystem

I

IPT_SUBSYSTEM

IP Tunnel subsystem

KITS_SUBSYSTEM

Kits subsystem

K

KERNEL_SUBSYSTEM

Kernel subsystem

N

NETUTIL_SUBSYSTEM

Net utility subsystem

O

OM_SUBSYSTEM

Object Management subsystem

77

EBADFD

File descriptor in bad state

78

EREMCHG

Remote address changed

79

ELIBACC

Can not access a needed shared library

80

ELIBBAD

对it行业需要收集哪些资料

对it行业需要收集哪些资料对IT行业需要收集哪些资料1. 市场研究资料作为IT行业从业者,了解市场状况对于决策和规划至关重要。

以下是一些需要收集的市场研究资料:行业统计数据:收集行业整体发展数据,包括市场规模、增长率、竞争对手数量等。

趋势分析:关注当前和未来的技术趋势,参考相关报告和研究,了解行业的发展方向。

消费者需求:了解目标用户的需求和喜好,包括他们的痛点、偏好和购买习惯。

竞争分析:收集竞争对手的信息,了解他们的产品、服务、定价策略以及市场份额。

2. 技术资料IT行业是一个快速变化的领域,持续学习和掌握最新技术是非常重要的。

以下是一些需要收集的技术资料:官方文档:获取官方技术文档,了解产品、框架或工具的使用方法和功能特性。

开发者文档:查阅开发者社区、论坛或博客,了解他们的经验和教程,从中学习技术实践。

行业标准:掌握行业标准和最佳实践,以确保在开发和实施项目时合规和安全。

论文和研究:阅读学术论文和技术研究,了解前沿技术和解决方案。

3. 法律和合规资料在IT行业中,理解和遵守相关法律和合规要求至关重要。

以下是一些需要收集的法律和合规资料:个人隐私保护:掌握个人数据保护法规,了解如何妥善处理和保护用户的个人信息。

知识产权:了解软件版权、专利和商标等知识产权的相关法律法规,确保合法使用和保护知识产权。

电子商务:熟悉电子商务法规,包括在线支付、数据交换和交易保障等方面的合规要求。

安全和网络保护:了解网络安全法规以及数据安全和网络防御的最佳实践,建立合规的安全保护措施。

4. 经济和财务资料对于IT行业中的企业或个人来说,了解经济和财务状况至关重要。

以下是一些需要收集的经济和财务资料:预算和成本管理:了解项目预算和成本管理的方法和工具,以确保项目按时交付且在预算范围内。

财务报告:掌握财务报表的概念和要求,了解企业的盈亏状况、资产负债和现金流。

投资分析:学习如何进行投资分析,包括ROI(投资回报率)和NPV(净现值)等指标的计算和评估。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

上海慧龙网络技术有限公司 北京互信互通科技(成都)

-74.722 -75.1

-74.545 -72 -74.211 -63.8

-73.333 -82.3

北京中欧博雅科技有限公司 25

22 gameloft智乐

24.545 30.1 24.151 32.3 23.636 58.4 23.333 56

23.182

39.5

深圳市深信服电子科技有限 21.25 33 公司

/top10.php(第 2/5 页)2008-11-26 19:49:22

-74.3

红黑榜-IT公司速查手册(公司评论)-情报资料最全,评论人数最多,从2002年开始的Bewww-公司...T公司速查手册,查询,讨论,分析,指正,IT公司评论与评价,IT公司排名,专注于业内公司的评论服务]

265 258 239 232 230 198 196 193 192 187 183 171 161 159 157

10 利库(上海)软件有限公司 11 EMC中国研发中心 12 上海华泰软件工程有限公司 13 14

北京摩软科技有限公司

29.167 39.5 28.125 55.8 27.917 42.7 26.957 62.8 26.5 32

上海华依科技有限公司

群硕软件开发(上海)有限公司 上海惠普/GDCC 上海中和软件有限公司 杭州科澜信息技术有限公司 INFOSYS TECNOLOGIES

上海优尔信息技术有限公司 -93.019 -89.4 成都瑞智朗新科技有限公司 -90.909 -65.6 北京英泰科隆科技有限公司

-90

苏州工业园区视算科技有限 40 公司

/top10.php(第 1/5 页)2008-11-26 19:49:22

红黑榜-IT公司速查手册(公司评论)-情报资料最全,评论人数最多,从2002年开始的Bewww-公司...T公司速查手册,查询,讨论,分析,指正,IT公司评论与评价,IT公司排名,专注于业内公司的评论服务]

15 卡斯柯信号有限公司 16 博克软件(杭州)有限公司 17

大连博华计算机科技有限公 -75 17 司

18 武汉环大科技开发有限公司 -75

CSTS花旗软件技术服务(上海)有 限公司

诺基亚西门子网络 Nokia Siemens Networks

26.207 50.3 26

26

趋势科技南京研发中心 18 Trend 上海金仕达卫宁医疗技术有 19 限公司

29 四川川大智胜软件股份公司 30 上海新致软件公司 31 广州拓欧信息技术有限公司 32 新蛋科技(成都)有限公司 33 高知特(上海)信息技术有限公司 34 上海思策软件 35 易保网络技术有限公司 36

上海大数智能系统有限公司 上海盛鑫信息科技有限公司

16.8 38.7 29.2 12.8

宇龙计算机通讯科技有限公 23 司

新蛋信息技术(西安)有限 20.253 43.9 公司

20 41.2

上海小樱计算机科技有限公 36 司

37 38

-69.565 -70.1 -69.5

37 上海农业信息有限公司

上海复讯农业科技有限公司 凡安德咨询科技公司 上海文思创新软件技术公司

-89

48 自协软件科技上海有限公司 49 浙江省公众信息产业有限公司 50 上海若雅软件系统有限公司 51 大展科技有限公司 52 深圳太极软件有限公司 53

北京光宇华夏科技有限责任 23 公司 凡安德(成都)资讯科技有限 24 公司

25 26

27 EDS电子资讯系统(上海)有限公司 153 28 宇龙计算机通信科技有限公司 152 144 143 141 140 136 133 129 124 124 124 121 119 118 116 109

-73.043 -80 -73.043 -79.5 -72.973 -87.2 -72.667 -85.4

全国黑榜Top100

Company Name Point↑ -94.872 -59.1 1 2 3 4 5 6 7 8 9

全国热门榜Top100

Company Name Notes 1032 947 465 414 379

IBM/ISSC/SH/铃木(狗 熊)专版 BM/ISSC/SH/小松刘锋专 版

上海山丽信息安全有限公司 -77.143 -38.6

-76.863 -89.1

EDS Wuhan Global Service Center 日立信息系统(上海)有限公 司北京分公司

14 深圳太极软件有限公司 15

上海世范软件技术有限公司 -76.269 -71.2

-76.09

16 上海思策软件

-80.1 -55.7 -24.1

9.7 -5.3 10 -11.7

陕西时光软件有限公司 上海中和软件有限公司

-66.667 -62.6 -66.667 -29.4 -66.667 -26.8

-66.489 -84.3

50 大连创盛科技有限公司 51 上海迪巨特 52 53 54 55

深圳市优迈科技发展有限公 52 司

53

浙江建达科技有限公司

红黑榜-IT公司速查手册(公司评论)-情报资料最全,评论人数最多,从2002年开始的Bewww-公司...T公司速查手册,查询,讨论,分析,指正,IT公司评论与评价,IT公司排名,专注于业内公司的评论服务]

搜索IT公司评论

公司名

首页 公司列表 网友评论 信息反馈 IT公司速查 同事录-7yes白领圈 人物评论 TOP100

37 博彦科技(北京)有限公司 38 文思创新软件技术有限公司 39 北京摩软科技有限公司 40 宏界传播 41 北京紫光华宇软件股份有限公司 42 深圳联友科技有限公司 43 卓银软件(深圳)有限公司

中华网软件上海研发部(希达 31 软件)

32

0.9

上海邦信信息技术有限公司 21.429 50.3

23

22.895

深圳中博科创信息技术有限 27 公司

28

27 上海数慧系统技术有限公司 28

南通范思软件有限公司

-72.222 -71.4 -72.222 -66.1

新电信息科技(苏州)有限 公司

29 上海贝信软件有限公司 30 31 32 33 34

深圳龙岗嶂背赐昌实业有限 22.778 30.1 29 公司

30 PTC 22.069 40.6

21.765

善诚科技发展(上海)有限 -71.765 -69 公司 广州市龙泰信息技术有限公 司 上海飞乐纽康 浙江贝尔技术有限公司 元亨科技开发(深圳)有限 公司

-71.395 -87 -71.099 -87.3 -70.588 -81 -70

谷歌(Google)中国工程研究院 (Shanghai)

34 威盛旭上电子(via) 35 广州安正软件科技有限公司 36

21.081 37.4 20.556 34.5

35

上海理想信息产业(集团) -70 有限公司

-45.1

44 上海新逸科技有限公司 45 安复仕软件 46 上海远界网络科技有限公司 47 深圳市深信服电子科技有限公司

109 108 105 104 104 104 102 102 102 100 99 99 95 95 94 91 91 91 90 90 89 88

-94.5

Marvell Technology Ltd. 39.318 59.7 Shanghai Branch 上海蓝盟网络技术有限公司 36.875 79.1 陕西锐力信息技术有限公司 35 河南省现代机械电子研究所 SAP(中国)研究院 - SAP Labs

33.684

大连菱科数据通信技术有限 -83.333 -82.9 公司 上海维豪信息安全技术有限 -83.333 -31.4 公司 上海市康时信息系统有限公 -83.077 -15.4 司 宏界传播 漕河泾开发区软件园培训中 心

9

安徽康樱网络科技有限公司 30.909 35.9

30 30 60.8 45.9

10 神州数码通用软件公司上海 11 上海国响信息技术有限公司 12 13

-78.652 -63.3

-77.647 -83.3 -77.603 -93.2

12 SAP(中国)研究院 - SAP Labs 13 IBM/ISSC/SH/铃木(狗熊)专版 14 凌志软件 15 上海先锋商泰电子技术有限公司 16 IBM/ ISSC 17 新蛋信息技术(西安)有限公司 18 泰为信息科技(上海)有限公司 19 上海世范软件技术有限公司 20

-68.519 -82.6 -67.647 -82.1 -67.6

55 金华业软件系统有限公司 56 汇丰银行HSBC广州开发中心GLTC 57 纬泓软件上海公司珠海分公司 58 开目佰钧成软件资源有限责任公司

上海飞旗网络有限公司(F7 NETWORKS)

-77.5

中国工商银行软件开发中心 17.941 33 47 杭州研发部

42 麒麟远创 43 中国太平洋人寿保险 44 京信通信系统有限公司 45 太极计算机股份有限公司 46 18.667 21.8 18.333 34.8 18.182 38.1 18.182 19.4 18 68.5

浙江公众信息系统集成有限 -68.75 -9.8 41 公司 重庆正大软件(集团)有限公 42 司

-80.168 -90.8 -79.474 -86.8

捷开通讯公司 356 欧特克(Autodesk)中国研究院 (ACRD) 上海互联网软件有限公司

354 337 287 282

46.2 -7.1

31.208 71.5

10 大连晟峰中天软件有限公司 11 神州数码通用软件公司上海

20 21 中兴南京研究所 22 瞬联软件科技 23 北京Oracle 24 西安活跃网络有限公司 25 上海圣诺软件技术有限公司 26