Matlab_Simulink和modelsim联合仿真

AMESim与Simulink联合仿真设置步骤与实例

1. 联合仿真环境设置:软件环境:AMESimR10VC++6.0MA TLAB/Simulink2010a1.将VC++中的"vcvar32.bat"文件从Microsoft Visual C++目录(通常是. \Microsoft Visual Studio\VC98\Bin中)拷贝至AMESim目录下。

2.环境变量确认:1) 选择“控制面板-系统”或者在“我的电脑”图标上点右键,选择“属性”;在弹出的“系统属性”窗口中选择“高级”页,选择“环境变量”;2) 在弹出的“环境变量”窗口中找到系统变量“AME”,它的值就是你所安装AMESim的路径,选中改环境变量;比如AMESim10安装目录(即AMESim10安装文件的存储目录)是:C:\AMESim\v1000(D:\AMESim就是错误的),那么“AME”的值就是C:\AMESim\v1000, 点击“确认”按键,该变量就会加到系统中;3) 按上述步骤设置系统变量“MATLAB”,该值为MA TLAB文件所安装的路径,例如Matlab 2010a按照文件的存储路径为:D:\Program Files\MATLAB\R2011a,那么“MA TLAB”的值就是D:\Program Files\MATLAB\R2010a,点击“确认”按键,该变量就会加到系统中;4) 同样的方式定义系统变量LM_LICENSE_FILE,值为C:\AMESim\v1000\licensing\license.dat,值就是AMESim软件许可文件的存储路径。

即LM_LICENSE_FILE=C:\AMESim\v1000\licensing\license.dat。

3. 在AMESim中选择VC作为编译器。

具体操作在AMESim->Opions-> AMESimPreferences->Compilation中;进去后选择Microsoft Visual C++项,然后点击OK确认。

Simulink_modelsim联合仿真

simulink/modelsim联合仿真XX学生的师傅2016年5月13日Simulink/Modelsim 联合仿真操作步骤本人使用的matlab版本为:matlab R2014a ; modelsim版本为:Modelsim SE-64 10.1c。

以下内容是参考自matlab帮助文档,结合自己第一次联合仿真的经验得出,如有不到之处,不能帮助解决问题还请原谅。

第一次使用markdown,如阅读体验不好,你咬我啊以下正文1.新建目录2.在matlab中配置cosimulation block1.在matlab中运行cosimWizard。

2.按要求配置。

3.在simulink或matlab中搭建仿真模型4.从matlab或simulink中启动modelsim两种方法:•在matlab中运行vism或vism('socketsimulink'),4449 ,其中4449为端口号,根据实际情况确定。

之后需在modelsim中加载verilog文件,并输入vsimulink work.uq_pmsm ,其中uq_pmsm为实体名,根据实际情况替换。

•双击simulink中的Launch HDL Simulator块启动modelsim。

以下两种情况: - 方法一启动实体仿真、方法二modelsim加载实体完成后,若一直显示loading。

- 直接在simulink中运行仿真时出现错误,提示change port。

可进入任务管理器结束lmutil.exe进程。

黑科技,不确保有效。

5.在simulink中启动仿真,此时modelsim会同步进行仿真。

AMEsim与Matlab_simulink联合仿真技术

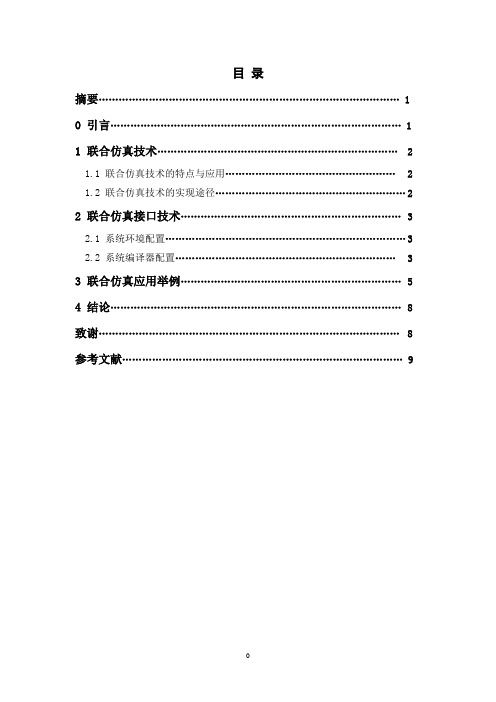

目录摘要 (1)0 引言 (1)1 联合仿真技术 (2)1.1 联合仿真技术的特点与应用 (2)1.2 联合仿真技术的实现途径 (2)2 联合仿真接口技术 (3)2.1 系统环境配置 (3)2.2 系统编译器配置 (3)3 联合仿真应用举例 (5)4 结论 (8)致谢 (8)参考文献 (9)AMESim与Matlab_Simulink联合仿真技术机械电子系0802班李敏M200870228摘要:根据AMESim与Matlab/Simulink软件各自的特点,对两者联合仿真技术进行了研究,解决了联合仿真的接口与实现问题,并把该技术应用于电液位置伺服系统的仿真,取得了良好的效果。

关键词:AMESim;Matlab/Simulink;联合仿真;接口Abstract:United Matlab/Simulink technique with AMESim and Matlab/Simulink was discussed based on their own characteristics. The problem of their interface and realization were solved. As an applied example, Matlab/Simulink of electro hydraulic servo-system was shown. Good results were achieved.Keywords:AMESim;Matlab/Simulink;United simulation;Interface0 引言传统的设计方法往往是通过反复的样品试制和试验来分析该系统是否达到设计要求,结果造成大量的人力和物力投入在样品的试制和试验上。

随着计算机仿真技术的发展,在工程系统的软件设计开发中,大量地采用了数值成型的方法,即通过建立系统的数值模型,利用计算机仿真使得大量的产品设计缺陷在物理成型之前就得到了处理,从而可以使企业在最短的时间、以最低的成本将新产品投放到市场。

Matlab中的Simulink和SimMechanics做仿真

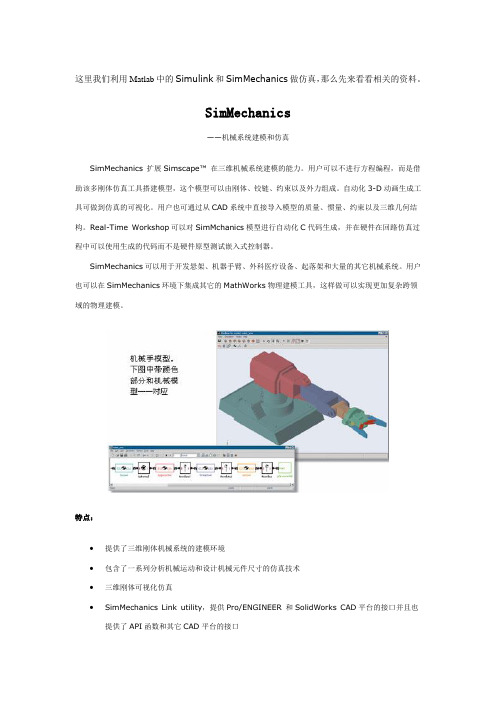

这里我们利用Matlab中的Simulink和SimMechanics做仿真,那么先来看看相关的资料。

SimMechanics——机械系统建模和仿真SimMechanics 扩展Simscape™ 在三维机械系统建模的能力。

用户可以不进行方程编程,而是借助该多刚体仿真工具搭建模型,这个模型可以由刚体、铰链、约束以及外力组成。

自动化3-D动画生成工具可做到仿真的可视化。

用户也可通过从CAD系统中直接导入模型的质量、惯量、约束以及三维几何结构。

Real-Time Workshop可以对SimMchanics模型进行自动化C代码生成,并在硬件在回路仿真过程中可以使用生成的代码而不是硬件原型测试嵌入式控制器。

SimMechanics可以用于开发悬架、机器手臂、外科医疗设备、起落架和大量的其它机械系统。

用户也可以在SimMechanics环境下集成其它的MathWorks物理建模工具,这样做可以实现更加复杂跨领域的物理建模。

特点:∙提供了三维刚体机械系统的建模环境∙包含了一系列分析机械运动和设计机械元件尺寸的仿真技术∙三维刚体可视化仿真∙SimMechanics Link utility,提供Pro/ENGINEER 和SolidWorks CAD平台的接口并且也提供了API函数和其它CAD平台的接口∙能够把模型转化为C代码(使用Real-Time Workshop)∙由于集成在Simulink环境中,因此可以建立高精度、非线性的模型以支持控制系统的开发和测试。

强大功能:搭建机械系统模型使用SimMechanics用户仅需要收集物理系统信息即可建立三维机械系统模型。

使用刚体、坐标系、铰链和作用力元素定义和其它Simulink模型直接相连的部分。

这个过程可以重用Simulink模型以及扩展了SimMechanics工具的能力。

用户还可把Simulink模型和SimMechnics模型集成为一个模块,并可封装成可在其它模型中复用的子系统。

simulink和modelsim联合仿真的简单例子

使用Link for ModelSim ,你可以建立一个有效的环境来进行联合仿真、器件建模、以及分析和可视化。

进行如下的实例的开发。

1 :可以在MA TLAB或Simulink 中针对HDL实体开发软件测试基准(test bench) 。

2 :可以在Simulink 中对包含在大规模系统模型的HDL 模型进行开发和仿真。

3 :可以生成测试向量进行测试、调试,以及同MA TLAB/Simulink下的规范原形进行HDL 代码的验证。

4 :提供在MA TLAB/Simulink下的对HDL行为级的建模能力。

5 :可以在MA TLAB/Simulink下对HDL的实现进行验证、分析、可视化。

Link for ModelSim中MA TLAB与ModelSim 接口和Simulink与ModelSim 接口是独立的。

这使得你可以单独使用一个接口或同时使用两个。

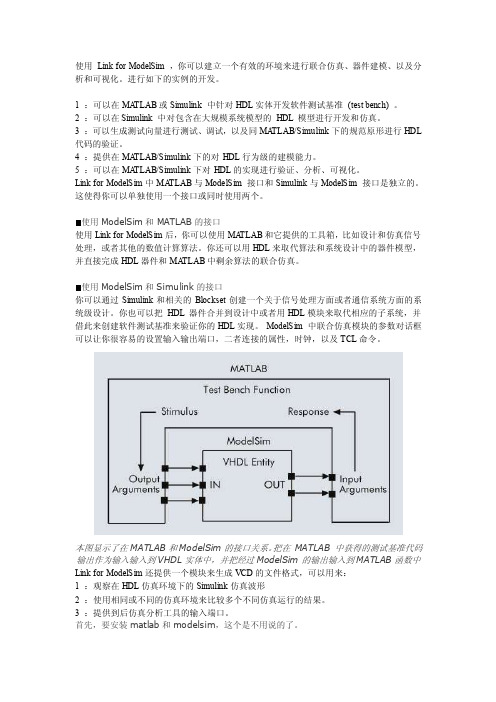

使用ModelSim和MATLAB的接口使用Link for ModelSim后,你可以使用MA TLAB和它提供的工具箱,比如设计和仿真信号处理,或者其他的数值计算算法。

你还可以用HDL来取代算法和系统设计中的器件模型,并直接完成HDL器件和MA TLAB中剩余算法的联合仿真。

使用ModelSim和Simulink的接口你可以通过Simulink和相关的Blockset创建一个关于信号处理方面或者通信系统方面的系统级设计。

你也可以把HDL 器件合并到设计中或者用HDL模块来取代相应的子系统,并借此来创建软件测试基准来验证你的HDL实现。

ModelSim 中联合仿真模块的参数对话框可以让你很容易的设置输入输出端口,二者连接的属性,时钟,以及TCL命令。

本图显示了在MATLAB和ModelSim的接口关系。

把在MATLAB 中获得的测试基准代码输出作为输入输入到VHDL实体中,并把经过ModelSim的输出输入到MATLAB函数中Link for ModelSim还提供一个模块来生成VCD的文件格式,可以用来:1 :观察在HDL仿真环境下的Simulink仿真波形2 :使用相同或不同的仿真环境来比较多个不同仿真运行的结果。

simulink与AMESim联合仿真

Simulink与AMSIM联合仿真的方法虽然随着新材料、电机技术、控制学和先进制造技术等的发展,出现了用以取代目前所依赖的功率液压传动的功率电传技术,但是在现阶段,液压伺服作动系统仍然占据航空作动系统的主导地位。

主要原因是液压伺服作动系统具有其它伺服作动系统无法比拟的优势,具有容易得到大功率输出、高功率/重量比、响应快和低俗特性好的特点。

航空液压作动系统是目前飞机上最成熟的液压作动方式,大多直接采用飞机的中央液压源提供的恒压油,通过(伺服)阀来控制执行机构的双腔流量完成指令动作,精度高、响应快。

航空也要作动系统根据其发展历程一般分为以下四类:液压助力器、电液指令作动器、复合式伺服作动器和直接驱动阀式伺服作动器。

本文将主要对其关键技术进行深入分析,并提出关键技术的解决途径。

1 建模仿真技术由于对航空液压作动系统自身结构比较复杂,对其自身的性能要求比较高,需要满足包括输出载荷、中立位置、额定行程、最大行程、行程余量、额定速度、最大速度、极限载荷、主控阀剪切力、门限、位置精度和滞环等的静态特性,满足包括频率响应和阶跃响应的动态特性,以及稳定性和阻抗特性要求。

银次,在研制航空液压作动系统的过程中,对其进行建模仿真非常重要。

通过仿真,可以对所设计的作动器性能有全面的了解,便于改进和完善设计。

传统的建模仿真分析手短一般采用数学推到加Simulink仿真的方式进行。

Simulink是美国Match Works公司开发的MA TLAB软件的可视化仿真环境,具有丰富的线性/非线性、连续/离散等控制系统仿真功能模块,具备神经网络、模糊控制等一系列先进的智能控制工具箱,非常适合进行航空液压作动系统的建模与分析,但其前提是基于用户建立的数学模型和其自身提供的结构参数化的功能模块。

而这已无法满足现在对仿真高精度和高准确度的要求。

而且Simulink本身没有专门针对液压流体仿真的工具箱,用户使用时要自己建立模型。

AMESim是法国Imagine公司推出的基于功率键合图的液压/机械系统建模、仿真机动力学分析软件,采用图形化的物理建模方式,具有复杂液压元件结构参数化的功能模块,也同样非常适合进行航空液压作动系统的结构参数化建模与分析,但是他的控制系统仿真功能模块相对较少,不具备神经网络、模糊控制等一系列先进的智能控制工具箱。

Matlab和modelsim联合仿真

• ModelSim

– 利用hdl coder生成的批命令和测试平台,然 后用Modelsim进行单独仿真

– Matlab/Simulink和Modelsim协同仿真

Matlab/Simulink ModelSim仿真

Matlab Link ModelSim

1. 建立连接通道 MATLAB

1. hdldaemon('socket',端口号)

in TCP/IP socket mode端口号,0表示由系 统分配可用端口

或 2 Hdldaemon

in shared memory mode

MATLAB连接ModelSim流程例

• 2 从MATLAB环境启动ModelSim vsim 或 vsim('vsimdir','D:\Modeltech_6.1f\win32\')

Altera仿真库-从Quartus 中提取

• 还可以再编译其他器件系列的库 • 修改ModelSim 安装目录下的

ModelSim.ini文件只读属性为可写,以便 记录仿真库的路径及映射关系

ModelSim用户界面

库文件视图

命令控制台

ModelSim> 设计加 载前的提示符

VSIM> 设计加载后 的提示符

• 布局布线后仿真(时序仿真)

– 验证是否存在时序违规。电路已经映射到具体 的工艺环境,综合考虑电路的门延迟和路径延 迟

ModelSim仿真

• 设置断点 • 单步运行 • 查看当前信号值 • 从仿真波形回溯源代码

ModelSim的安装

1. 运行setup,安装程序。选择“Full product”选项 。当询问security key的时候,选择 NO。 当看 见“ License Wizard”对话框时候,选择“close” 。

Modelsim与MATLAB联合仿真技术研究及应用

随着系统规模和复杂度的提升,产品规范的制 定难度成倍增加,缺陷问题日益突出。只有到了设 计的后期缺陷才能被发现,工程师们急需一种能够 支持系统开发的方法。

基于 MATLAB 平台的 Simulink 是动态系统仿真 领域中著名的仿真集成环境,它在众多领域得到广 泛应用。Simulink 仿真库里提供的 link for modelsim

首先,在 MATLAB 中产生仿真所需要的输入信 号(信号加噪声),以十六进制的形式存放在数据文 件中;其次,在 ModelSim 中用 VHDL 编写仿真测试文 件(TestBench)[2],用 IEEE 的 TEXTIO 库中的 READ 和 RESDLINE 函数将上述仿真数据文件中的测试向量 读入,在 ModelSim 中做布局布线后的仿真(时序仿 真),并调用 WRITE 和 HWRITE 函数将仿真结果写入 另外一个数据文件中;最后,在 MATLAB 中将 Model⁃ Sim 仿真输出数据文件中的数据读入一个数组中,可 以 做 图 分 析 ,或 做 进 一 步 的 误 差 分 析 。 还 可 以 将 ModelSim 中的仿真结果与 MATLAB 中做出的理论结 果相比较来验证设计的正确性。这样可以比直接用 人工方法将输入数据通过波形输入,再用人工方法 通过对比输出波形中的数据来验证设计的正确性要 直观、方便的多。

1 联合仿真系统搭建

Link for modelsim 是一个联合仿真的接口,它将 Mathwoks 工具整合到 EDA 工作环境中,使其应用于 FPGA 和 ASIC 的开发。这个接口在 HDL 仿真器 Mod⁃ elSim SE/PE 和 MathWorks 的产品 MATLAB 和 Simu⁃ Link 间提供了一个双向连接,以指导硬件的设计验 证和联合仿真。这种整合可以分别充分发挥 MAT⁃ LAB/SimuLink 和 ModelSim 各自的优势。图 1 显示 了在 MATLAB/SimuLink 和 ModelSim 的接口关系。

Modelsim与Simulink协同仿真

Modelsim与Simulink协同仿真当使⽤硬件描述语⾔(HDL)完成电路设计时,往往需要编写Testbench对所设计的电路进⾏仿真验证,测试设计电路的功能是否与预期的⽬标相符。

⽽编写Testbench难度之⼤,这时可以借助交互式图形化环境Simulink来产⽣模拟激励,并且可以观察测试模块的输出响应。

⾸先,⽤Verilog描述⼀个反相器,代码如下:module inverter(clk,sin,sout);input clk ;input [7:0] sin ;output [7:0] sout ;reg [7:0] sout;always@(posedge clk)sout <= ~ sin;endmodule在modelsim分别输⼊命令vlib work;vmap work work;vlog interver.v 编译成功后,启动Simulink建⽴模型,模型如下。

注意Matlab和Modelsim的⼯作路径要保持⼀致。

模块HDL Cosimulation位于HDL Verifier库中For use with Mentor Graphics Modelsim⼦库中。

双击HDL Cosimulation进⾏相关参数设置,并对Simulink模块进⾏仿真参数设置。

点击Simulation--Start开始仿真。

Modelsim多次仿真结果如下另外,Simulink还提供了⽐较直观的cosimWizard命令来配置协同仿真。

具体使⽤说明参见HDL Cosimulation Wizard Tutorials(doc cosimWizard)参考资料及⼯程⽂件见: 提取码8zyf。

AMEsim和Simulink联合仿真教程

软件准备:MATLAB2016bAMEsim2020.2Visual studio 2013软件不宜过新。

上面是恒仔使用的、联合成功的版本。

步骤:一:复制文件将D:\Program Files (x86)\Microsoft Visual Studio 12.0\VC\bin下的nmake.exe 、vcvars32.bat和D:\Program Files (x86)\Microsoft Visual Studio 12.0\VC\bin\amd64下的vcvars64.bat复制到D:\Program Files\Simcenter\2020.2\Amesim中覆盖。

(全文所提到路径皆为自己软件的安装路径,可根据自己安装情况更改)二:环境配置在安装完Visual Studio 2013、Amesim 2020.2 、Matlab 2016b之后,需要配置环境变量。

在windows桌面,右键“计算机”-“属性”-“高级系统设置”-“环境变量”里添加用户变量和系统变量。

1、用户变量添加变量名:HOME,变量值:D:\添加变量名:MATLAB,变量值:D:\Program Files\MATLAB\R2016b2、双击Path变量,添加:配置完成后,重启电脑,以使用户变量和系统变量生效。

三、软件设置:1、首先打开Matlab 2016b,在命令窗口输入:mex -setup将C和C++编译器都设置为Visual C++ 2013.2、打开Amesim2020.2 ,进入Tools-Preferences-Compilation,将Active Compiler设置为Microsoft Visual C++ (64bit)。

软件配置完成。

四、联合仿真例程运行在Amesim 2020.2-Help-Help里,输入simulink,打开“Hybrid_bus_steps_simulink”例程:点击Open this demo,下面一串链接,将其复制到指定目录并打开:点击Amesim 2020.2-Tools-MATLAB®,它会自动打开MATLAB2017b,并自动添加AMESIM的相关路径到MATLAB PATH里,然后它会自动打开Hybrid_bus_steps_simulink.mdl。

Modelsim和Simulink协同仿真

Modelsim和Simulink协同仿真(欢迎批评指正:jackhuan@)1 在Matlab里配置Modelsim1)>>configuremodelsim;2)File/Set path…,加入Modelsim.exe所在路径。

一般是$Modelsim\Win32。

2 在Matlab里检查Matlab server是否运行,方法hdldaemon(‘status’)若matlab server已经运行,则显示:DLDaemon socket server is running on port 4449 with 0 connections否则显示:DLDAEMON is now Runing。

如果已经运行,则将matlab server关闭:hdldaemon(‘kill’);3 在Modelsim里编辑VHDL程序1)启动modelsim,设置当前路径File/Set Current Path2)vlib work3)vmap work work4)edit myadder.vhd5)编辑完毕后,保存,并编译vcom myadder.vhdmyadder.vhd内容如下:`timescale 10ns/1nsmodule adder4(clk,a,b,cin,sum,cout);input clk,cin;input[3:0] a,b;output cout;output[3:0] sum;reg cout;reg[3:0] sum;always@(posedge clk)begin{cout,sum} = a+b+cin;endendmodule4 创建Simulink模型1)启动matlab,并启动simulink;将当前路径设置到存放vhd的路径之中。

2)编辑模型.从commonly used blocks中选择const模块,从sources中选择counter free-running模块,从sink中选择float scope模块,从link for modelsim中选择VHDL cosimulation block,放入编辑器,设置后做如下连接。

AMESim与Simulink联合仿真设置步骤与实例

1. 联合仿真环境设置:软件环境:AMESimR10VC++6.0MA TLAB/Simulink2010a1.将VC++中的"vcvar32.bat"文件从Microsoft Visual C++目录(通常是. \Microsoft Visual Studio\VC98\Bin中)拷贝至AMESim目录下。

2.环境变量确认:1) 选择“控制面板-系统”或者在“我的电脑”图标上点右键,选择“属性”;在弹出的“系统属性”窗口中选择“高级”页,选择“环境变量”;2) 在弹出的“环境变量”窗口中找到系统变量“AME”,它的值就是你所安装AMESim的路径,选中改环境变量;比如AMESim10安装目录(即AMESim10安装文件的存储目录)是:C:\AMESim\v1000(D:\AMESim就是错误的),那么“AME”的值就是C:\AMESim\v1000, 点击“确认”按键,该变量就会加到系统中;3) 按上述步骤设置系统变量“MATLAB”,该值为MA TLAB文件所安装的路径,例如Matlab 2010a按照文件的存储路径为:D:\Program Files\MATLAB\R2011a,那么“MA TLAB”的值就是D:\Program Files\MATLAB\R2010a,点击“确认”按键,该变量就会加到系统中;4) 同样的方式定义系统变量LM_LICENSE_FILE,值为C:\AMESim\v1000\licensing\license.dat,值就是AMESim软件许可文件的存储路径。

即LM_LICENSE_FILE=C:\AMESim\v1000\licensing\license.dat。

3. 在AMESim中选择VC作为编译器。

具体操作在AMESim->Opions-> AMESimPreferences->Compilation中;进去后选择Microsoft Visual C++项,然后点击OK确认。

AMESim-MATLAB联合仿真详细设置+部分问题解决步骤

AMESim-MATLAB联合仿真详细设置+部分问题解决步骤AMESim-Matlab 的联合仿真设置1. 联合仿真的前期准备1.1. AMESim 与Matlab 的版本匹配问题AMESim 与Matlab 的联合仿真有两类接口:接口(将AMESim 模型导入到Simulink 中)接口(将Simulink 模型导入到AMESim 中)两种不同的接口,对应的AMESim-Matlab 联合仿真的软件兼容列表,分别如图 1 和 2 所示。

图中,"Probable"表示未经AMESim 官方测试,但仍然可以正常使用。

"Yes"表示经AMESim 官方测试,确定可以正常使用。

"No"表示该组合不能实现联合仿真。

如图1 所示,"AMESim to Simulink" 接口对软件的版本要求较低,基本上AMESim Rev7(或者更高的版本)与Mablab R2007b (或者更高的版本)可以自由组合进行联合仿真。

如果想使用"Simulink to AMESim" 接口,建议安装AMESim Rev11 以上的版本,Malab 只要求R2007b 以上即可。

图 1 "AMESim to Simulink" 接口图 2 "Simulink to AMESim" 接口1.2. Microsoft Visual C++编译器(VC++)的版本选择?AMESim 支持的VC++版本分别如图1(32 位编译器),图2(64 位编译器)所示。

图1 和图2 中,"Probable","Yes","No"表示的意思同上。

经测试,AMESim Rev9 可以正常调用VS2010 版的VC++(32 位)。

另外,从图 1 中,可以看到,VC++ 6.0 不能支持AMESim Rev11 以上的版本。

AMESim与MATLAB Simulink联合仿真技术及应用

第26卷 第5期 情报指挥控制系统与仿真技术 Vol.26 No.5 2004年10月Information Command Control System & Simulation Technology Oct.2004文章编号邓卫华北京 100081分析了AMESim 与MATLAB/Simulink 的特点解决了联合仿真的接口问题取得了良好效果AMESim联合仿真TP391.9 文献标识码China)Abstract: United simulation technique with AMESim and MATLAB/Simulink is discussed in the paper. As anapplied example, simulation of active suspension system is shown.Key words: AMESimunited simulation高级工程系统仿真建模环境迄今已发展到4.0版本液体及气体控制它具有丰富的模型库1000多个模块用户可以采用基本元素法按照实际物理系统来构建自定义模块或仿真模型其次它采用复合接口简化了模型的规模采用变步长变类型而且具有稳态仿真批处理仿真得到精度和稳定性很高的仿真结果2004-01-01作者简介1979-女研究方向为车辆仿真技术男研究方向为车辆悬架系统设计与计算机辅助设计而且整个仿真模型可以生成C 或Fortran 代码由于具有齐全的线性分析模型简化工具修改内置有与CMATLAB/Simulink 的接口用户可以在AMESim 环境中访问任何C 或Fortran 程序优化工具及能谱分析等工具而整个仿真过程仅仅采用鼠标基于这些优点Ford ZFSimulink 借助于MATLAB 强大的数值计算能力在各个工程领域发挥着巨大的作用但MATLAB 存在不能有效地处理代数环问题等缺点利用AMESim 对Simulink 的接口技术就能既发挥AMESim 突出的流体机械的仿真效能取长补短这种联合仿真的技术对多领域系统的仿真效果更是无与伦比62 李谨AMESim 与MA TLAB/Simulink 联合仿真技术及应用 第26卷1 AMESim与MATLAB/Simulink联合仿真技术 作为一个图形化的开发环境在模型中描述所有系统和零部件的功能对于一个复杂的工程系统AMESim则突破性地实现了多个领域仿真而专注于物理系统本身的设计我们又必须对所研究的系统的某个子系统进行深入研究这时在AMESim中建模就不如在MATLAB/Simulink 中方便而在AMESim 中对其余系统建模这样一方面可以减小建模的工作量为了实现二者的联合仿真AMESim4.0与MATLAB6.1上版本1设置方法为在环境变量设置对话框中设置变量名例如则变量值为设置MATLAB 环境变量MATLAB例如则变量值为确认在系统变量中包括Windows 安装路径添加上可能会出现各种错误则可以运行AMESim 和MATLAB/Simulink 进行联合仿真讲述联合仿真技术的实现步骤建立物理模型如图1把系统分为机械系统和控制系统两部分控制系统模型由Simulink建立1绘图模式先根据物理模型然后为Simulink 的控制模型构造一个图标在Sketch mode 中界面选择Create export icon ,在绘图区出现的创建输出图标对话框中选择输入定义图标名称标准界面(Simulink)SimulCosim将模型与界面图标相对应的部分连接起来如图2中所示在AMESimSubmodel Mode中为系统的各个模块选择合适的子模型及合适的数学模型active suspension. ame考虑到本文介绍的是AMESim 与Simulink 联合仿真技术3参数模式输入系统的各个模块的参数第5期 情报指挥控制系统与仿真技术 63图2 AMESim构建的主动悬架模型 4运行模式开始运行运行结束5因为主动悬架控制目标就是使车辆获得高平顺性和操纵稳定性同时限制悬架的动挠度从便于控制的角度来说在这里采用汤姆逊控制律主动律最佳极点配置方法来设计主动悬架控制器的设计6S-Functionactive suspension_注意S 函数名中不能缺少符号 1 0.01其中第一个参数表示是否生成AMESim 结果文件0表示不生成7Demux在AMESim 中提供了两种与Simulink 接口的接口界面标准界面两种接口界面的区别在于AMESim 和Simulink 中共同采用Simulink 中选定的求解器二者则各自采用各自的求解器AMESim 模型在Simulink 中被看作是时间连续模块这使得其与在Simulink 中建立的AMESim 模型的控制器十分匹配这里采用的是标准界面在联合仿真界面时输入仿真参数注意仿真时AMESim 模型不能关闭生成的S 函数将会自动压缩为一个文件下面是使用这种方法对某车悬架垂直振动仿真结果图3 Simulink建造的控制系统模型万方数据64 李谨AMESim与MA TLAB/Simulink联合仿真技术及应用第26卷图4 车身垂直位移与时间关系图 图5 车身垂直速度与时间关系图 图6 车身垂直减速度与时间关系图 图7 轮胎垂直位移与时间关系图 图8 轮胎垂直速度与时间关系图 图9 轮胎垂直加速度与时间关系图 3 总结 从上面可以看出AMESim与MATLAB/Simulink联合仿真技术开创了一条效果很好而又不很复杂的仿真新途径相互取长补短由此可以断言必将在工程领域内得到广泛应用[1] 周云山北京理工大学出版社, 1999. [2] 夏德钤. 反馈控制理论[M]. 哈尔滨马彪兵器工业出版社。

协同仿真Cosimulation的简单应用不带IP核

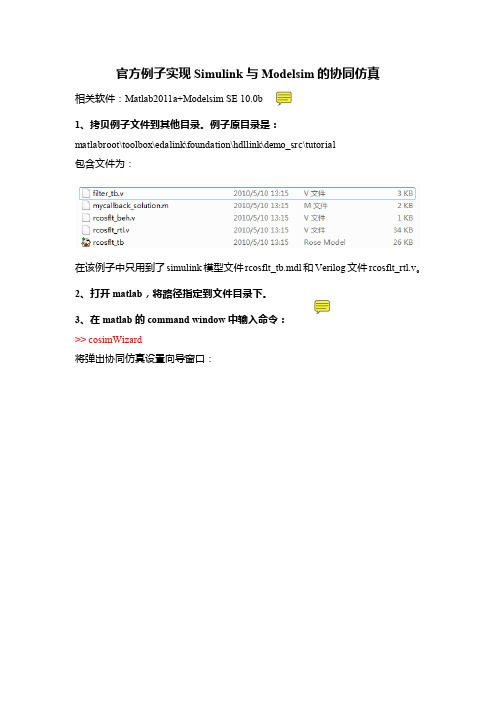

官方例子实现Simulink与Modelsim的协同仿真相关软件:Matlab2011a+Modelsim SE 10.0b1、拷贝例子文件到其他目录。

例子原目录是:matlabroot\toolbox\edalink\foundation\hdllink\demo_src\tutorial包含文件为:在该例子中只用到了simulink模型文件rcosflt_tb.mdl和Verilog文件rcosflt_rtl.v。

2、打开matlab,将路径指定到文件目录下。

3、在matlab的command window中输入命令:>> cosimWizard将弹出协同仿真设置向导窗口:(1)指定协同仿真类型(Specify Cosimulation Type)①HDL cosimulation with:使用Simulink②HDL Simulator:使用Modelsim③HDL仿真执行软件,默认即可(由于自己的有Modelsim Altera6.5b不支持协同仿真,所以需要人为指定Modelsim SE10.0b的版本)上述三步完成后,如下图所示:(2)选择HDL文件(Select HDL Files)这里只需要添加rcosflt_rtl.v文件。

(3)指定HDL编译命令(Specify HDL Compilation Commands)由于使用Modelsim,在“-incr”后紧接着添加:-vlog01compat选择Next后会看到编译信息。

(4)选择协同仿真的HDL模块(Select HDL Modules for Cosimulation)①选择协同仿真文件:rcosflt_rtl。

如果下拉中没有,可直接输入文件名②去掉Simulation Options中的“-novopt”(5)指定端口类型(Specify Port Types)默认即可。

需要注意,input port提供的四种类型中,只有input类型的会连接到simulink,output port提供的两种类型中,只有output类型的会连接到simulink。

MATLAB,Simulink与Modelsim联合仿真步骤及实例

目录1:什么是link for modelsim2:link for modelsim的安装与设置3:使用link for modelsim仿真的实例什么是link for modelsimLink for modelsim是一个联合仿真的接口,它将MathWorks工具整合到EDA工作环境中,使其应用于FPGA和ASIC的开发。

这个接口在HDL仿真器ModelSim SE/PE于MathWorks的产品Matlab和SimuLink间提供了一个双向连接,以指导硬件的设计验证和联合仿真。

这种整合可以分别充分发挥Matlab/SimuLink和ModelSim各自的优势。

1.联合仿真环境Link for ModelSim是一个客户/服务器的车是平台和联合仿真应用,ModelSim在这个仿真环境中所起的作用取决于ModelSim与Matlab还是SimuLink连接,本说明只讲ModelSim与Matlab的连接。

a.ModelSim与Matlab连接当与Matlab相连接时,ModelSim作为客户端,如下图所示:在这个模式中,Matlab服务器等到ModelSim客户端发出的服务请求,当接收到一个请求时,Matlab建立一个通信连接,而且调用一个指定的Matlab函数,这个函数封装了用于计算数据以验证或者使当前在ModelSim中仿真的HDL模型的可视化。

下图显示了在一个测试平台环境中Matlab函数如何与ModelSim进行通信Matlab服务器可以用于多个HDL实体之间的联合仿真,但是你必须为多个HDL实体指定一个通信方式使他们可以相互通信,下图显示了两个ModelSim客户端如何连接到服务器的TCP/IP的4449端口:回到目录2.通信模式在ModelSim和Matlab之间的通信模式有共享内存和网络两种,当你的ModelSim和MatLab运行与同一个系统的时候,可以指定为共享内存方式和网络方式,但共享内存方式更加合适,其也是默认的方式。

AMESim与MATLAB_Simulink联合仿真接口配置

AMESim—MATLAB(64位)联合仿真设置详细步骤说明:现以AMESimR12、MATLAB2014b为例说明,其他版本类似。

1、版本要求2、辅助软件VS2013若要使用 AMESim 与 Simulink 的接口,则需要在本机安装编译器,高版本软件需要高版本的编译器,这里以VS2013为例设置。

一般推荐先安装VS编译器,然后安装 Matlab,最后安装 AMESim的顺序。

若后安装VS编译器,将VS编译器安装目录下如 D:\ Microsoft Visual Studio 12.0 \VC\bin 目录中的nmake.exe 文件和vcvars32.bat 以及D:\Microsoft Visual Studio 12.0\VC\bin\amd64下的vcvars64.bat(64位版本的MATLAB)文件拷贝至 AMESim 安装目录,如D:\AMESim\v1200下。

3、环境变量设置定义Windows 系统环境变量:1)选择“控制面板-系统”或者在“我的电脑”图标上点右键,选择“属性”;2)在弹出的“系统属性”窗口中选择“高级”页,选择“环境变量”;3)用户变量中添加HOME D:\MATLAB D:\MATLAB\R2014bPath D:\ Microsoft Visual Studio 12.0\Common7\Tools; D:\ Microsoft Visual Studio 12.0\VC\bin; D:\Program Files\MATLAB\R2014b\bin; D:\ProgramFiles\MATLAB\R2014b\bin\win644) 在系统变量中添加在Path 环境变量中加入(以分号与其它已经存在的变量值隔开)路径:Matlab_Root(如 D:\Matlab\R2010a)\bin 和Matlab_Root(如D:\Matlab\R2010a)\bin\win32 ,以及%windir%\System32,其中%windir%指的是 Windows 的安装路径,如 C:\WINNTPath D:\Program Files (x86)\Microsoft Visual Studio 10.0; D:\AMESim\v1000; D:\AMESim\v1000\win64;D:\AMESim\v1000\sys\mingw32\bin;D:\AMESim\v1000\s ys\mpich\mpd\bin;D:\AMESim\v1000\sys\cgns;%SystemRoot%\system32;%SystemR oot%;%SystemRoot%\System32\Wbem;D: \MATLAB\R2014b\bin\win64;C:\WINDOWS\system32;C:\WINNT (该处很重要一定要添加,而且一定要包含C:\WINDOWS\system32,不然会有引起很多错误)4、AMESim与MATLAB设置启动AMESim并确认 AMESim 使用的是 MS C++编译器。

关于modelsim和matlab的联合仿真

关于modelsim和matlab的联合仿真一,如何将matlab里面进行算法时所用的数据源放到modelsim里面进行调用。

1,将数据用matlab程序转化为二进制并存储到一个data.dat文件里面,这一步中,二进制的位数与verilog 程序里面的输入端口的位数相同;data.dat文件名任意定,后缀名不变就行。

下面几句fp = fopen('data.dat','w');for i1 = 1:100bin_I = int8_to_bin(Routdata(i1));fprintf(fpi,'%d',bin_I);fprintf(fpi,' ');endfclose(fp);就是将100个数据源中的数据Routdata转化为二进制并存储起来,其中的int8_to_bin是自己定义的8位的整型数据转化为二进制的函数。

2,在verilog里面打开数据文件data.dat并读取里面的数据。

reg [7:0] mem [99:0];//声明一个数组寄存器,位宽为8位,数组长度为100;initial$readmemb("data.dat",mem);//将数据读到数组寄存器中;reg [6:0] cnt;always@(posedge clk or negedge rst)if(!rst)cnt <= 7'b0;elsebegincnt <= cnt 1'b1;inI <= mem[cnt];end这样,inI就作为所设计模块的输入,可以进行modelsim仿真了。

二,如何将modelsim里面的仿真结果输出到matlab进行分析。

1,将modelsim仿真结果写入.txt文件,integer fid;initialfid = $fopen("dataout.txt","w");reg [6:0] cnt;always@(posedge clk or negedge rst)if(!rst)cnt <= 7'b0;elseif(cnt==7'd100)$fclose(fid);elsebegincnt <= cnt 1'b1;$fwrite(fid,"%b",out);end其中,out为所设计模块处理后的输出,以二进制的形式存储到txt文件中。

Modelsim和MATLAB的联合仿真

Modelsim的仿真功能虽然很强大,但是显示结果多为波形文件,当涉及到数字信号处理算法的验证或者考查信号频谱等方面的问题是则略显不足。

MATLAB具有数据可视化功能,可以迅速方便的图形、图像、动画等表述计算结果,帮助数据分析和逻辑思维。

故使用Modelsim和MATLAB对FPGA设计进行联合仿真可以大大加快仿真速度。

本文介绍一种简单的文件读写方式实现Modelsim和MATLAB的联合仿真。

由于Modelsim(及FPGA设计)中常用数据为二进制,故以下以二进制为例。

1、通过MATLAB生成仿真输入数据。

在Modelsim对FPGA设计进行验证仿真时,经常需要输入仿真数据,这些数据可以用FPGA产生,但是如果数据产生过程很复杂的话,需要耗费很大的精力,并且产生的数据的准确性也不能保证。

这时候就可以借助MATLAB,利用MATLAB内部自带的各种函数,产生需要的信号,再经过定点化,就作为FPGA 接收模块的输入信号了。

这样做无疑会节约很多时间和精力。

下面用一个简单的例子说明如何用MATLAB产生的数据用作Modelsim仿真。

例:线性调频信号的产生(4096个14bit数据)f0=(32.4)*1e6;%模拟信号中频fs=(100)*1e6;%采样频率Ts=1/fs;%采样周期BW=0.05e6;%中频信号带宽50KHzTp=4096*Ts;%sample4096pointK=BW/Tp;%带宽时宽比%-------generate input lfm signal---------%t=-Tp/2:Ts:Tp/2-Ts;xs=cos(2*pi*(f0*t+0.5*K*t.^2));%LFM信号表达式fid=fopen('F:\programmer\DDC_test\cordic_test\test5M.txt','w');if(fid==-1)disp('Couldn''t open file test5M.txt for writing');endx=round(xs*(2^13-1));a=quantizer([14,0]);sx=num2bin(a,x);%有符号十进制转二进制for i=1:length(x)b=sx(i,:);fprintf(fid,'%s\n',b);endfclose(fid);将产生的数据以二进制形式写入test5M.txt 文件中,以备使用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Altera仿真库 从Quartus 中提取 仿真库-从 仿真库

3. 从Quartus 中提取

1. 改变工作目录到存放仿真库的目录下 2. 创建新的库 3. 编译库

Altera仿真库 从Quartus 中提取 仿真库-从 仿真库

• 编译库

–对新创建的库进行编译 对新创建的库进行编译——选择源文件: 选择源文件: 对新创建的库进行编译 选择源文件 Quartus安装目录 安装目录\eda\sim_lib\220pack.vhd 安装目录 altera_mf_components.vhd 选择编译余下的6 再选择编译余下的6个文件

ModelSim仿真 仿真

• • • • 设置断点 单步运行 查看当前信号值 从仿真波形回溯源代码

ModelSim的安装 的安装

1. 运行setup,安装程序。选择“Full product”选项 。当询问security key的时候,选择 NO。 当看 见“ License Wizard”对话框时候,选择“close” 。 2. 运行keygen,生成license.dat, 把它拷贝到新建的 keygen license.dat, c:\flexlm 目录中。 3. 设置环境变量: LM_LICENSE_FILE = c:\flexlm\license.dat (选择“我的电脑” 按右键 ,选“属性”,再选“高级”,可以看到环境变 量按钮) 4. 运行ModelSim,OK

Matlab Link ModelSim

MATLAB 连接 连接HDL仿真器 仿真器

MATLAB 连接 连接HDL仿真器 仿真器

• MATLAB test bench function wraps around and communicates with the HDL simulator during a test bench simulation session.

MATLAB连接 连接ModelSim流程例 连接 流程例

在ModelSim仿真过程中, MATLAB 绘 制输出信号

MATLAB连接 连接ModelSim流程例 连接 流程例

• 8 重新仿真

ModelSim: restart 重复步骤7, 输入激励信号,运行仿真。 重复步骤 , 输入激励信号,运行仿真。

Altera仿真库 从Quartus 中提取 仿真库-从 仿真库

• 还可以再编译其他器件系列的库 • 修改ModelSim 安装目录下的 修改 ModelSim.ini文件只读属性为可写,以便 文件只读属性为可写, 文件只读属性为可写 记录仿真库的路径及映射关系

ModelSim用户界面 用户界面

MATLAB连接 连接ModelSim流程例 连接 流程例

• 9 结束仿真

– ModelSim

quit 退出仿真 quit 结束ModelSim

– Matlab

hdldaemon(‘kill’) 关闭连接

Simulink Link ModelSim

Simulink 连接 HDL 仿真器

Simulink 与HDL仿真器协同仿真流程 仿真器协同仿真流程

1. ModelSim

– 建库 – 编译

2. Simulink

– 建模 – 使用/配置协同仿真模块

• Matlab

– 建立连接

3. ModelSim

– 加载仿真器

4. Simulink

– 运行仿真

使用Simulink 协同仿真模块 使用

Simulink 建模

配置协同仿真模块--端口设置 配置协同仿真模块 端口设置

• 仿真库

– IP Core 仿真库

• 如果设计中包含了 如果设计中包含了MegaWizard 生成的 Core 或 生成的IP 直接调用了LPM, 则必须制定Altera 直接调用了LPM, 则必须制定Altera 仿真库

– 器件族仿真库

Altera仿真库 仿真库

添加Altera的仿真库三种方法 为ModelSim SE添加 添加 的仿真库三种方法

vcom <file1>.vhd <file2>.vhd vlog <file1>.v <file2>.v

4. 启动仿真器

vsim top_entity

ModelSim基本 基本 仿真步骤

5. 添加信号到 添加信号到Wave窗 窗 add wave /* 6. 添加激励 运行仿真 添加激励,

force run <time_step> <time_units>

连接ModelSim流程例modsimrand.m 流程例 连接

Matlab启动 server in shared memory mode: ModelSim仿真

hdldaemon

modsimrand_plot.m function [iport,tnext] = modsimrand_plot(oport, tnow, portinfo)

1. hdldaemon('socket',端口号)

in TCP/IP socket mode端口号,0表示由系 端口号, 表示由系 端口号 统分配可用端口

或 2 Hdldaemon

in shared memory mode

MATLAB连接 连接ModelSim流程例 连接 流程例

• 2 从MATLAB环境启动ModelSim vsim 或 vsim('vsimdir','D:\Modeltech_6.1f\win32\')

端口名称与ModelSim 信号命名相同,删除不 合适的端口 对输出端口设采样时间

配置协同仿真模块--端口设置 配置协同仿真模块 端口设置

• 自动填入端口信息:

– 在modelsim中关联:vsimulink 实体名 – 在simulink 协同仿真模块中删除已有端口,点 击 Auto Fill – 删除不必要的端口,如clk(clk信息应在clocks 选项卡中设置)

1. 从ModelSim AE版中复制 版中复制Altera的仿真库 版中复制 的仿真库 – 1安装 安装ModelSim AE版 安装 版 – 2在ModelSim AE的安装目录下的 在 的安装目录下的Altera目录 的安装目录下的 目录 就是所要的仿真库

Altera仿真库 仿真库

2 从Altera 官方网站下载预编译的仿真库 /support/software/do wnload/eda_software/modelsim/msmindex.jsp

ModelSim exe具体安装路径 具体安装路径

MATLAB连接 连接ModelSim流程例 连接 流程例

• 3 设置MATLAB当前目录

例

cd D:\MATLAB\toolbox\edalink\extensions\modelsim\modelsim demos 该目录下有modsimrand_plot.m文件

• 设置MODELSIM当前目录

–例

cd D:\MATLAB\toolbox\edalink\extensions\modelsim\modelsim demos\vhdl\modsimrand 该目录下有VHDL文件

MATLAB连接 连接ModelSim流程例 连接 流程例 •4 执行ModelSim命令

vlib work 创建工作库 vmap work work 映射工作库到物理目录 库到物理目录 vcom modsimrand 选择一个 择一个HDL文件进行编译 文件进行编译 择一个

MATLAB连接 连接ModelSim流程例 连接 流程例

• 5关联HDL设计与MATLAB函数 ,执行ModelSim

ModelSim版本 版本

• ModelSim AE

– Altera OEM 版,功能有限,速度较慢。有厂 功能有限,速度较慢。 家仿真库

• ModelSim PE • ModelSim SE

– 专业版, 性能最强 专业版, 性能最强。

Altera和ModelSim 和

• ModelSim 的版本

– ModelSim AE 要有License 要有 – ModelSim AE Free 发行速度跟不上SE 版和 版和Quartus 的 发行速度跟不上 速度 – ModelSim SE 不带FPGA/CPLD厂家的仿真库 不带 厂家的仿真库

ModelSim版本 版本

• 如用于Matlab/Simulink协同仿真

matlabtb modsimrand mfunc modsimrand_plot -rising /modsimrand/clk -socket portnum

仿真

仿真结果可视化

用ModelSim 仿真例

仿真数据来自ModelSim, 由Matlab绘图 仿真数据来自 绘图

MATLAB连接 连接ModelSim流程例 连接 流程例 1. 建立连接通道 MATLAB

MATLAB连接 连接ModelSim流程例 连接 流程例

• 7执行Vsim命令,输入激励信号,运行仿真。 输入激励信号, 输入激励信号 运行仿真。 例

force /modsimrand/clk 0 0 ns, 1 5 ns -repeat 10 ns force /modsimrand/clk_en 1 force /modsimrand/reset 1 0, 0 50 ns run 80000

• 选用ModelSim 6.1~6.3

• 如选用ModelSim AE

– 可以用 相应 相应ModelSim Se的 License. 例如 例如: 的 最新版本的ModelSim AE 6.4 可以使用 最新版本的 ModelSim Se 6.4的License 的

Altera的仿真库 的仿真库