ModelSim作布局布线后仿真的库问题

Modelsim常见问题

Modelsim 常见问题

Q1:设计中用到厂商提供的IP时,编译时出现“(vopt-3473) Component instance "XXXX" is not bound.”

A1:编译时,需要把所需的Libray添加到编译命令中,如“vsim -L C:/Modeltech_6.2b/xilinx_lib/XilinxCoreLib ......”。

Q2:vhdl和verilog混合仿真时,vhdl和verilog代码中会调用同一个组件,但是他们分别来自不同的library,如unisim和unisim_ver,它们相互并不通用,及verilog不能调用unisim_ver的组件,会造成组件找到却没办法绑定的错误,如:“Port 'Q' not found in the connected module”?

A2:当仿真时,由于vhdl代码中会指定从那个库文件里面提取,而verilog代码中没有,所以使用vsim命令时,把verilog所需的库放在第一个,而后放vhdl 所需的库,这样,verilog会从unisim_ver代码开始查询组件。

Q3:"ERROR: ../<project>/<module.v>: Unresolved reference to 'glbl' in 'glbl.GSR'" A3:在仿真工程中添加glbl.v文件(一般在~/ise/verilog/src/glbl.v,同理Quartus),把testbench.v和glbl.v同时选中后进行仿真,即vsim -t 1ps -L unisims_ver work.glbl work.tb。

荐)ModelSim SE仿真Altera库的一些问题 常见仿真错误 问题 合集

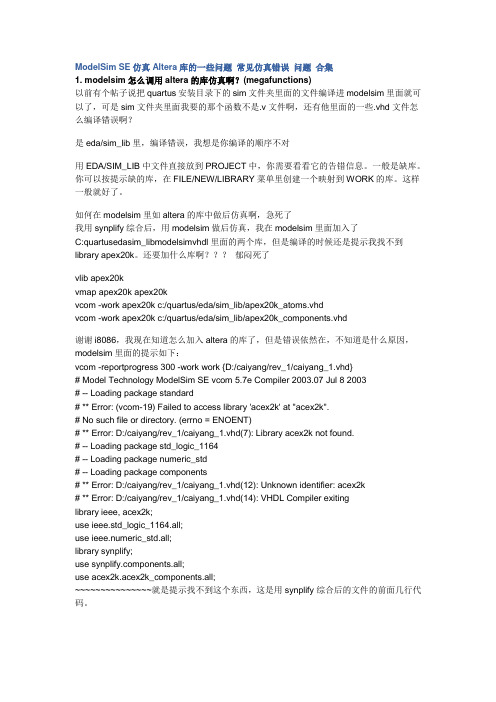

荐)ModelSim SE仿真Altera库的一些问题常见仿真错误问题合集1. modelsim怎么调用altera的库仿真啊?(megafunctions)以前有个帖子说把quartus安装目录下的sim文件夹里面的文件编译进modelsim里面就可以了,可是sim文件夹里面我要的那个函数不是.v文件啊,还有他里面的一些.vhd文件怎么编译错误啊?是eda/sim_lib里,编译错误,我想是你编译的顺序不对用EDA/SIM_LIB中文件直接放到PROJECT中,你需要看看它的告错信息。

一般是缺库。

你可以按提示缺的库,在FILE/NEW/LIBRARY菜单里创建一个映射到WORK的库。

这样一般就好了。

如何在modelsim里如altera的库中做后仿真啊,急死了我用synplify综合后,用modelsim做后仿真,我在modelsim里面加入了C:quartusedasim_libmodelsimvhdl里面的两个库,但是编译的时候还是提示我找不到library apex20k。

还要加什么库啊???郁闷死了vlib apex20kvmap apex20k apex20kvcom -work apex20k c:/quartus/eda/sim_lib/apex20k_atoms.vhdvcom -work apex20k c:/quartus/eda/sim_lib/apex20k_components.vhd谢谢i8086,我现在知道怎么加入altera的库了,但是错误依然在,不知道是什么原因,modelsim里面的提示如下:vcom -reportprogress 300 -work work {D:/caiyang/rev_1/caiyang_1.vhd}# Model Technology ModelSim SE vcom 5.7e Compiler 2003.07 Jul 8 2003# -- Loading package standard# ** Error: (vcom-19) Failed to access library 'acex2k' at "acex2k".# No such file or directory. (errno = ENOENT)# ** Error: D:/caiyang/rev_1/caiyang_1.vhd(7): Library acex2k not found.# -- Loading package std_logic_1164# -- Loading package numeric_std# -- Loading package components# ** Error: D:/caiyang/rev_1/caiyang_1.vhd(12): Unknown identifier: acex2k# ** Error: D:/caiyang/rev_1/caiyang_1.vhd(14): VHDL Compiler exitinglibrary ieee, acex2k;use ieee.std_logic_1164.all;use ieee.numeric_std.all;library synplify;use ponents.all;use acex2k.acex2k_components.all;~~~~~~~~~~~~~~~就是提示找不到这个东西,这是用synplify综合后的文件的前面几行代码。

modelsim仿真小结

Modelsim仿真小结Modelsim的基本仿真流程大致分以下几个步骤:建库、编译工程、前后仿真、调试等。

Modelsim仿真既可以在modelsim界面操作,也可以用do文件实现,这里结合学习的教程、网上看到的资料,和实际遇到的一些问题,分别做一整理小结。

1.建库建库包括Altera库和Xilinx库,同时都包括Verilog和VHDL。

这里只建了Verilog库,VHDL 和Verilog步骤相同。

对于Altera库主要包括lpm元件库、Mega_Function库atera_mf、altera原语库altera_primitive和各器件系列模型库。

前三种是调用altera模块的必备库,第四种是进行综合后功能仿真和布线后时序仿真需要的库,和器件系列有关,只选对应系列即可。

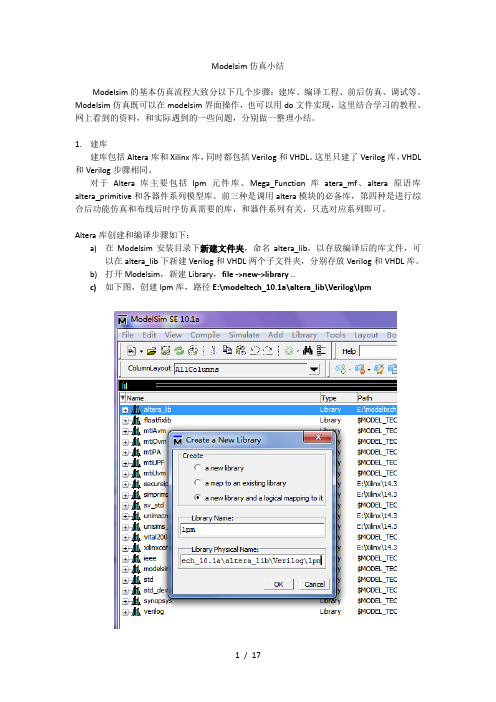

Altera库创建和编译步骤如下:a)在Modelsim安装目录下新建文件夹,命名altera_lib,以存放编译后的库文件,可以在altera_lib下新建Verilog和VHDL两个子文件夹,分别存放Verilog和VHDL库。

b)打开Modelsim,新建Library,file ->new->library ..c)如下图,创建lpm库,路径E:\modeltech_10.1a\altera_lib\Verilog\lpmd)添加库文件,并编译,compile -> compile …,出现compile source files窗口,library指定到lpm下,查找围,选quartus安装目录下…eda\sim_lib目录里的仿真原型文件:220model.v ,点c ompile ,点done。

到此,lpm库建立完毕。

e)同理,建立altera_mf库添加altera_mf.v ,建立primitive库添加altera_primitive.v建立各系列的模型库,命名可用系列名加_ver“xxx_ver”,也可随意吧,添加各系列的xxx_atoms.v。

Modelsim使用常见问题及解决办法

Modelsim使用常见问题及解决办法在ISE启动modelsim时遇到问题1。

我在ISE中启动modelsim时出现了下面的错误Loading work.tb_ic1_func# ** Error: (vsim-19) Failed to access library 'xilinxcorelib_ver' at "xilinxcorelib_ver".# No such file or directory. (errno = ENOENT)# ** Error: (vsim-19) Failed to access library 'unisims_ver' at "unisims_ver". # No such file or directory. (errno = ENOENT)# Loading work.fifoctlr_ic_v2# ** Error: (vsim-19) Failed to access library 'xilinxcorelib_ver' at "xilinxcorelib_ver".# No such file or directory. (errno = ENOENT)# ** Error: (vsim-19) Failed to access library 'unisims_ver' at "unisims_ver". # No such file or directory. (errno = ENOENT)# ** Error: (vsim-3033) fifoctlr_ic_v2.v(126): Instantiation of 'BUFGP' failed. The design unit was not found.是什么原因?“点到仿真模式,在source里面选中你建立工程选择的芯片,然后看Processes,点开,有个compile HDL simulation library,运行一下就OK了”2.ISE用modelsim仿真提示:# ** Error: (vish-4014) No objects found matching '*'.结果仿真时老是报错:# ** Error: (vish-4014) No objects found matching '*'.# Error in macro ./test_top_tb.fdo line 10# (vish-4014) No objects found matching '*'.# while executing# "add wave *"解决办法,改modelsim.ini文件中的一个参数:VoptFlow = 0# ** Error: (vish-4014) No objects found matching 'XXXX'.在之前的设计里有一个信号XX, 并且保持在wave.do文件里现在这个信号在你的设计你被去掉了,modelsim仍然调用旧的wave.do,找不到对应的信号XX,就报错误这个错误可以忽略3.当对IP核修改后,用Modelsim仿真显示:No entity is bound for inst 或CE is not in the entity。

modelsim后仿真详解

modelsim后仿真想很多人跟我一样,被ModelSim的后仿真搞的头晕脑胀。

为了这个问题,我在网上找了很多的资料,但发现这些资料往往说的不明白。

一些步骤被作者有意无意地省略掉,这常常给读者造成不必要的麻烦,所以我决定写下这一篇文章,把这3天我努力的结果拿出来,与大家分享。

首先,我把我用到的软件说明一下。

如果你发现根据我的操作,你还是解决不了ModelSim后仿真的问题,那就可能是软件版本的问题。

1, ModelSim Se 6.1b2, Synplify Pro 7.5.13, ISE 5.2i (这个是老了点)4, WindowsXP(这个应该没有多大的关系)还有就是我使用的是verilog,我想VHDL的方法与verilog是差不多的,最多也就是在建库方面有点差别而已。

下面的这些方法,是我这3天搞出来的。

当然也参考了一些文章。

如果谁有更方便的方法,欢迎指出来。

我的邮箱是vf1983cs@。

有空大家多交流。

一、为modelsim生成3个库。

首先,介绍一下这三个库。

Simprim_ver:用于布局布线后的仿真。

Unisim_ver :如果要做综合后的仿真,还要编译这个库。

Xilinxcorelib_ver:如果设计中调用了CoreGen产生的核,则还需要编译这个库。

我们要为modelsim生成的是标准库。

所谓的标准库就是modelsim运行后,会自动加载的库。

不过这方面我还不是很肯定。

因为我在后仿真时,还是要为仿真指定库的路径,不然modelsim找不到。

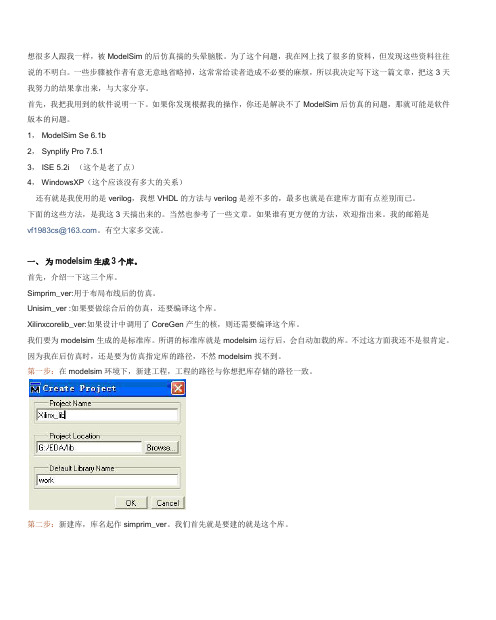

第一步:在modelsim环境下,新建工程,工程的路径与你想把库存储的路径一致。

第二步:新建库,库名起作simprim_ver。

我们首先就是要建的就是这个库。

第三步:在modelsim的命令栏上,打下如下命令:vlog -work simprim_ver d:/Xilinx/verilog/src/simprims/*.v其中的d:/Xilinx是我的Xilinx的安装路径,你把这个改成你的就行了。

使用Modelsim完成相关仿真过程问题汇总

使用Modelsim仿真Altera FPGA工程(包括IP核)步骤以及问题汇总前提:计算机上已经安装QuartusII和Modelsim通用版,并且均已破解。

环境说明:所用的软件版本,QuartusII为9.0,Modelsim为6.5c。

本测试仅在WIN XP SP3上测试,对于VISTA/WIN7/LIN或者其他平台没做过测试。

但其他平台或者其他版本的过程应该都差不多。

其他:感谢teamo版主的破解和编译教程,以及后期对我的热心指导。

如果各位对整个步骤还有什么问题的华可以直接和我联系,我的论坛ID是lanphon,邮箱是lanphon@。

一、Altera库的编译(本部分基本上全部抄袭teamo版主的教程,懒得写了)1) 先到C:\modeltech_6.5目录下找到文件"modelsim.ini",将其属性改为可写(右键‐>属性)。

2) 启动modelsim se,选择【file】‐>【new】‐>【library】命令,在弹出的【create a newlibrary】窗口中将选项【create】设置为【a new library and a logical mapping to it】,在【libryr name】和【library library】窗口中将选项【create】设置为【a new library and a logical mapping to it】,在【libryr name】和【library physical name】中键入所要创建库名字,如Altera ,此时在主窗口中已多了一个Altera 项。

注:这个过程实质上想当于在modelsim 主窗口中的脚本区域中输入了vlib和vmap命令。

3) 在workspace中的library中选中你健入的库名Altera,在主菜单中选【compile】→【compile…】命令。

modelsim仿真问题_xp

modelsim仿真问题_xp1、MODELSIM仿真提示already declared in this scope解决方法:在定义这个信号前其它模块接口信号中调用了这个信号,modelsim仿真报错,通过把信号定义挪到调用模块前面问题解决。

2、modelsim中,Instantiation of 'dffeas' failed. The design unit was not found.** Error: (vsim-3033) E:/pro/verilog_prj_example/simulation/modelsim/tb_sdrtest.v(2 4): Instantiation of 'print_task' failed. The design unit was not found.两种方法;报告3、Error: Can't compile duplicate declarations of entity "ram" into library "work"Error: Instance could be entity "ram" in file ram.v E rror: Instance could be entity "ram" in file ram.bdf解决办法:将.bdf文件的名字改掉,不能和.v文件的名字相同。

4、Quartus中仿真时出现no simulation input file assignment specify 对话框最好保证工程名、主模块、仿真文件的名字都一样。

5、9.17.2014下载波形文件仿真错误Error: Run Generate Functional Simulation Netlist (quartus_map yumen2_mk--generate_functional_sim_netlist) to generate functional simulation netlist for top level entity "yumen2_mk" before running the Simulator (quartus_sim)解决方法:原因是在功能仿真时候没有建立一个网表,网表的作用本人不是很清楚,只能说是功能仿真的一个必要步骤吧。

想很多人跟我一样,被ModelSim的后仿真搞的头晕脑胀

想很多人跟我一样,被ModelSim的后仿真搞的头晕脑胀。

为了这个问题,我在网上找了很多的资料,但发现这些资料往往说的不明白。

一些步骤被作者有意无意地省略掉,这常常给读者造成不必要的麻烦,所以我决定写下这一篇文章,把这3天我努力的结果拿出来,与大家分享。

首先,我把我用到的软件说明一下。

如果你发现根据我的操作,你还是解决不了ModelSim后仿真的问题,那就可能是软件版本的问题。

1, ModelSim Se 6.1b2, Synplify Pro 7.5.13, ISE 5.2i (这个是老了点)4, WindowsXP(这个应该没有多大的关系)还有就是我使用的是verilog,我想VHDL的方法与verilog是差不多的,最多也就是在建库方面有点差别而已。

下面的这些方法,是我这3天搞出来的。

当然也参考了一些文章。

如果谁有更方便的方法,欢迎指出来。

我的邮箱是****************。

有空大家多交流。

一、为modelsim生成3个库。

首先,介绍一下这三个库。

Simprim_ver:用于布局布线后的仿真。

Unisim_ver :如果要做综合后的仿真,还要编译这个库。

Xilinxcorelib_ver:如果设计中调用了CoreGen产生的核,则还需要编译这个库。

我们要为modelsim生成的是标准库。

所谓的标准库就是modelsim运行后,会自动加载的库。

不过这方面我还不是很肯定。

因为我在后仿真时,还是要为仿真指定库的路径,不然modelsim找不到。

第一步:在modelsim环境下,新建工程,工程的路径与你想把库存储的路径一致。

第二步:新建库,库名起作simprim_ver。

我们首先就是要建的就是这个库。

第三步:在modelsim的命令栏上,打下如下命令:vlog -work simprim_ver d:/Xilinx/verilog/src/simprims/*.v其中的d:/Xilinx是我的Xilinx的安装路径,你把这个改成你的就行了。

ModelSim的前后仿真(Quartus)

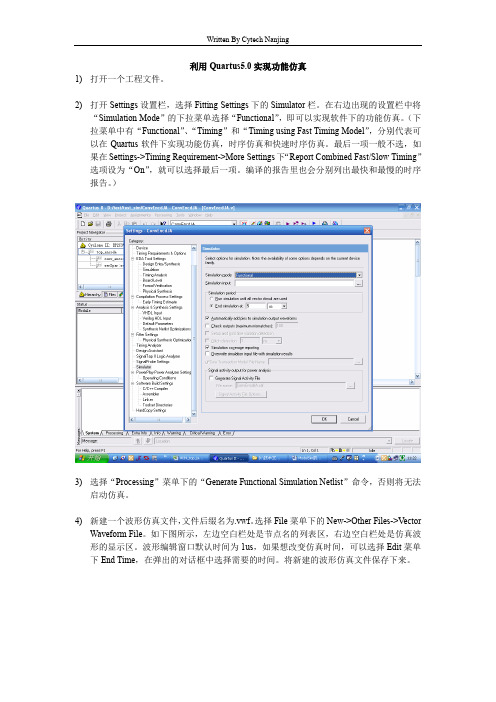

利用Quartus5.0实现功能仿真1)打开一个工程文件。

2)打开Settings设置栏,选择Fitting Settings下的Simulator栏。

在右边出现的设置栏中将“Simulation Mode”的下拉菜单选择“Functional”,即可以实现软件下的功能仿真。

(下拉菜单中有“Functional”、“Timing”和“Timing using Fast Timing Model”,分别代表可以在Quartus软件下实现功能仿真,时序仿真和快速时序仿真。

最后一项一般不选,如果在Settings->Timing Requirement->More Settings下“Report Combined Fast/Slow Timing”选项设为“On”,就可以选择最后一项。

编译的报告里也会分别列出最快和最慢的时序报告。

)3)选择“Processing”菜单下的“Generate Functional Simulation Netlist”命令,否则将无法启动仿真。

4)新建一个波形仿真文件,文件后缀名为.vwf。

选择File菜单下的New->Other Files->VectorWaveform File。

如下图所示,左边空白栏处是节点名的列表区,右边空白栏处是仿真波形的显示区。

波形编辑窗口默认时间为1us,如果想改变仿真时间,可以选择Edit菜单下End Time,在弹出的对话框中选择需要的时间。

将新建的波形仿真文件保存下来。

5)将需要仿真的信号加入波形编辑窗口。

在列表区任一位置双击或者点击右键选择“InsertNode or Bus…”,弹出的对话框点击“Node Finder”按钮。

在“Node Finder”界面中点击“List”按钮,有关信号的列表会出现在界面的左边,双击需要观察的信号加入至界面右边。

如果工程中用到了很多信号,在左边列表中也会显示很多(Named编辑框默认的是*通配符),可以在Named编辑框中添加需要的信号名称实现模糊查找。

使用modelsin对quartus II仿真时遇到问题的解决方法

1、FFT core可以设置成两种不同的引擎结构,四输出(Quad——output)和单输出(signal output),对于要求转换时间尽量小的应用,四输出的是最佳的结构,对于要求资源尽量小的应用,单输出的引擎结构比较合适,为了增加吞吐量,可以采用并行引擎结构。

FFT core支持的数据流:FFT core支持三种I/O数据流结构,连续(streaming)、缓冲突发(buffered burst)、突发(burst)。

连续I/o数据流允许处理连续输入数据,输出连续复数数据流,而不中断输入和输出数据;缓冲突发结构于连续相比,需要更少的存储资源,但是这是以减少平均吞吐量为代价的;突发数据流的操作于缓冲突发的方法基本上一致,但是突发方式需要更少的存储资源,这也是以降低吞吐量为代价的、。

2、用modelsim对fft模块进行仿真的时候出现此类问题的解决方法:** Error: (vsim-3033) E:/Quartus II projects/fft_1024_t/fft_1024_ip.v(92): Instantiation of 'asj_fft_sglstream_fft_130' failed. The design unit was not found.出现这种情况,第一可能是quartus破解不完整,导致有些库已经器件不能够使用,重新破解,在破解的时候有时候可能有好几个网卡,则选择前两个网卡号对license.dat进行破解。

在完整破解的时候,在仿真的时候需要加进去.vo文件以及测试文件,顶层文件,同时将生成fft核的时候产生.hex,.txt文件,在进行仿真的时候需要将其放到所建的modelsim工程文件夹下面。

第二种情况就是在不同版本的quartus上建立了ip核,比如说在9.0上建立的文件,在8.0上进行综合编译,就会出现这样的问题。

解决方法就是在现有的版本上重新建一个fft核之后进行仿真,应该就可以解决问题了。

使用modelsin对quartus II仿真时遇到问题的解决方法

1、FFT core可以设置成两种不同的引擎结构,四输出(Quad——output)和单输出(signal output),对于要求转换时间尽量小的应用,四输出的是最佳的结构,对于要求资源尽量小的应用,单输出的引擎结构比较合适,为了增加吞吐量,可以采用并行引擎结构。

FFT core支持的数据流:FFT core支持三种I/O数据流结构,连续(streaming)、缓冲突发(buffered burst)、突发(burst)。

连续I/o数据流允许处理连续输入数据,输出连续复数数据流,而不中断输入和输出数据;缓冲突发结构于连续相比,需要更少的存储资源,但是这是以减少平均吞吐量为代价的;突发数据流的操作于缓冲突发的方法基本上一致,但是突发方式需要更少的存储资源,这也是以降低吞吐量为代价的、。

2、用modelsim对fft模块进行仿真的时候出现此类问题的解决方法:** Error: (vsim-3033) E:/Quartus II projects/fft_1024_t/fft_1024_ip.v(92): Instantiation of 'asj_fft_sglstream_fft_130' failed. The design unit was not found.出现这种情况,第一可能是quartus破解不完整,导致有些库已经器件不能够使用,重新破解,在破解的时候有时候可能有好几个网卡,则选择前两个网卡号对license.dat进行破解。

在完整破解的时候,在仿真的时候需要加进去.vo文件以及测试文件,顶层文件,同时将生成fft核的时候产生.hex,.txt文件,在进行仿真的时候需要将其放到所建的modelsim工程文件夹下面。

第二种情况就是在不同版本的quartus上建立了ip核,比如说在9.0上建立的文件,在8.0上进行综合编译,就会出现这样的问题。

解决方法就是在现有的版本上重新建一个fft核之后进行仿真,应该就可以解决问题了。

有关modelsim的问题汇总

问题一:编译xilinx仿真库在网上搜了无数帖子,结合自己数小时的实践,终于搞定了Xilinx仿真库。

测试环境:Windows XP3,Xilinx ISE Suite 10.1,ModelSim SE 6.5c使用ISE自带的库生成工具是最方便的方法。

首先打开ISE,在Edit->Preferences...->ISE General 的Intergrated Tools 的Model Tech Simulator中指定Modelsim.exe的实际安装路径。

(在这里我的路径是D:\Work\modeltech_6.5c\win32\modelsim.exe,请根据自己的实际情况更改)。

OK以后退出ISE。

然后到ModelSim安装目录下找到ModelSim.ini文件,右键将其只读属性去掉,确定。

按下WIN+R,输入compxlibgui后回车,这其实就是自带的工具Simulation Library Compilation Wizard。

点击Select simulator,选中ModelSim。

检查路径正确了以后选Next。

再Next,建议再Next,或者根据自己的实际需要选择FPGA/CPLD的具体型号。

继续Next,在Map only to existing pre-compiled libraries前打上勾,在Output Directory for modelsim.ini file using mapped libraries中选择modelsim安装根目录modelsim.ini所在的路径,这一步很重要。

再点击Next就开始编译了。

最后把ModelSim.ini文件的只读属性改回去,万事OK……问题二:Hello all,Whenever I need to look at a filter output (or any DSP core), I used to define a real signal and assign it to what I want to examine, roughly something like this:dac_real_out <= hex2real(dac_holder, 12.0);where dac_holder is a std_logic_vector. It is much easier to look at an analogue signal waveform instead of tracing hex values word by word.This used to work quite alright using ModelSim XE edition. Now for some reason, it seems I can't get it to compile my design---I get the following error:# ** Error: (vcom-42) Unsupported ModelSim library format for "work". (Format: 3)My first question is: can I go around it as I've never encountered this before.My second one is: if not, is there anyway I can make ISE simulator do the same thing? apparently I can't add this real signal to my waveform editor and presumably ISE doesn't support it.Would appreciate any input on this.Manny wrote:> This used to work quite alright using ModelSim XE edition. Now for > some reason, it seems I can't get it to compile my design---I get the > following error:> # ** Error: (vcom-42) Unsupported ModelSim library format for "work". > (Format: 3)You can't *elaborate* (vsim) your design becausethe compiled work directory does not match the simulatoryou are using. Delete it and recompile (vcom)For modelsim, that is something like:vdel -allvlib workvmap work workvcom <source files>I like to write script like thisto archive with the design.> is there anyway I can make ISE simulator do> the same thing? apparently I can't add this real signal to my waveform > editor and presumably ISE doesn't support it.I expect that is true.You are better off with a real hdl simulator in any case.问题3:使用verilog进行描述,经过编译之后,在仿真过程中发现object中无项目,最终无波形输出。

ModelSim常见错误原因及解决

1.常见错误:Failed to find INSTANCE ...,问题出在下面所示的第2步或第4步。

正确处理步骤:(1)Quartus中编译测试码欲调用的顶层模块(设模块名:xxx),设置EDA tool 的simulation 工具,如verilog ,以产生xxx.vo文件及xxx_v.sdo延时文件;(2)打开modelsim,新建工程,添加xxx.vo文件、测试用激励波形文件testbench.v、所用器件的网表文件(以cyclone为例:$Quartus\eda\sim_lib\cyclone_atoms.v)。

全部编译。

!!:确认testbench.v中不包含顶层模块xxx代码。

(3)xxx_v.sdo复制到modelsim工程目录。

(4)最后,建立仿真配置文件:在workspace的project页中右键单击,选simulation configuration,如下图于是,workspace中得到simulation 1。

按下图设置:注意,上面的框中添加xxx_v.sdo,下面的文本框中设置作用域,格式为:\testbench模块名\xxx的实例名。

(5)`timescale 影响仿真结果显示效果。

=================例===================[1]//文件count4.vmodule count4(out,reset,clk);output[3:0] out;input reset, clk;reg[3:0] out;always @(posedge clk)beginif (reset)out <= 0;elseout <= out + 1;endendmodule[2]//测试文件count_tp.v`timescale 1ns/1nsmodule count_tp;reg clk,reset;wire[3:0] out;parameter DELY = 100;count4 mycount(out,reset,clk);always #(DELY/2) clk = ~clk;initialbeginclk = 0; reset = 0;#DELY reset = 1;#DELY reset = 0;#(DELY*20) $finish;endinitial $monitor($time,,,"clk=%d reset=%d out=%d",clk,reset,out); endmodule[3]所用器件:cyclone[4]结果:明显产生了时延p.s.-----------------------网上有朋友指出勾选SDF中的两个选项,将原来的警告禁止,将原来的错误变为警告, 可以成功地进行反标注并运行仿真,但这样做并没有解决实际问题,只能产生功能仿真,没有得到带时延的时序仿真2.** Error: D:/ModelSim_6.5/ModelSimnear "'t": Illegal base specifier in numeric constant.syntax error, unexpected "BASE", expecting "class"错误原因:不是’timescale 而是`timescale,那个是键盘左上角的点,不是一撇。

Modelsim-仿真方法总结

Modelsim 仿真方法总结Modeling 仿真工具是Model公司开发的。

它支持Verilog、VHDL以及他们的混合仿真.Modelsim各版本的使用方法大体一致,Modelsim仿真主要分为前仿真和后仿真。

下面来具体介绍modelsim的仿真方法,涉及quartus—modelsim联合(使用)仿真的差异会特别提示。

前仿真与后仿真说明1。

1 前仿真前仿真也称为功能仿真、行为仿真.旨在验证电路的功能是否符合设计要求,其特点是不考虑延迟(包括门延迟与线延迟),主要验证电路与理想情况是否一致。

前仿真需要用到RTL级代码(由源代码经过综合后产生)与Testbench。

1。

2)后仿真后仿真也称为时序仿真或者布局布线仿真。

是指在电路已经映射到特定的工艺环境以后,综合考虑门延迟与线延迟的影响,验证电路在一定的时序条件下是否存在时序违规以及能否满足设计构想的过程。

需要用到的文件是——从布局布线结果中抽象出来的门级网表、testbench和后缀名为sdo或者sdf的标准时延文件。

注:扩展名为sdo和sdf的标准时延文件包含门延迟与实际布线延迟,能较好的反应芯片的实际工作情况。

二)modelsim仿真主要有以下几个步骤:(1)建立库并映射库到物理目录;(2)编译源代码(包括Testbench);(3)执行仿真;解释:①库:modelsim中有两类仿真库.一种是工作库,默认名为work;另一种是资源库。

Work库中存放当前工程下所有已经编译过的文件,所以编译前一定要建立一个work 库.资源库存放work库中已经编译文件所要调用的资源,这样的资源可能有很多,它们被存放在不同的资源库内。

(例如要想对综合在cyclone芯片中的设计做后仿真,就需要有一个名为cyclone_ver的资源库.)映射库用于将已经预编译好的文件所在目录映射为一个modelsim可识别的库。

(此即是为仿真库建立一个逻辑映像的行为过程,后面会提到,在modelsim中新建库时,create a new library and a logical mapping to it或a map to an existing libraryd的提示) 上述三个步骤是大的框架,前仿真和后仿真均是按照这个框架进行的,建立modelsim工程对前后仿真来说都不是必须的.下面分别介绍每一步的操作。

modelsim使用常见问题及解决办法集锦③

modelsim使⽤常见问题及解决办法集锦③四、You selected Modelsim-Altera as Simulation Software in EDA ToolSettings,however……You selected ModelSim-Altera as Simulation Software in EDA Tool Settings,however NativeLink found ModelSim in the pata – correct path or change EDA Tool Settings and try again.问题原因该⼯程设置的仿真⼯具名称与在Quartus II软件中指定的该软件路径不匹配。

例如,本来设置的仿真⼯具是modelsim–altera,结果在Quartus II软件的modelsim-altera路径下设定的是Tools下设置的是modelsim-se的路径,导致软件版本不匹配⽽报错。

设置的仿真⼯具为modelsim-alteraModelsim-altera路径却指向了modelsim-se版本。

解决⽅法1、如果你电脑装的是modelsim-se版本,请按照如下图所⽰的设置进⾏⼯程和⼯具路径设置:2、如果你的电脑装的是modelsim-altera版本,请按照如下图所⽰的设置进⾏⼯程和⼯具路径设置:五、Unable to checkout a license问题原因使⽤了⾮免费版本的Modelsim软件,却没有获得软件使⽤许可证解决⽅法⽅法1:使⽤免费版本的modelsim软件,如modelsim altera stater edition。

⽅法2:购买软件许可证。

⽅法3:破解modelsim软件,破解⽅法见如下链接(altera收费版和se版本破解思路相同,破解⼯具通⽤):modelsim-win64-10.1c 下载、安装、破解全攻略(出处: 中国电⼦技术论坛)获得许可后最好重启Quartus II软件六、Error loading design问题原因提⽰信息中提⽰没有Verilog的仿真许可证,表明是没有获得软件使⽤许可。

利用ModelSim进行的功能仿真,综合后仿真,时序仿真

利用ModelSim进行的功能仿真,综合后仿真,时序仿真功能仿真,就是在理想状态下(不考虑延迟),验证电路的功能是否符合设计的要求。

功能仿真需要:1.TestBench或者其他形式的输入激励2.设计代码(HDL源程序)3.调用器件的模块定义(供应商提供,如FIFO,RAM等等)值得一提的是,可以在ModelSim直接编写TestBench,使用View->Source->Show language templates.综合后仿真(门级仿真),实际上就是将对综合后的门级网表进行仿真,只考虑门延迟,而没有加入时延文件。

在功能仿真之后检验综合的结果是否满足功能要求。

综合后仿真需要:1.综合后的门级网表,注意这里变成了*.vo文件,而不是原来功能仿真中所需要的HD L源代码.2.测试激励3.元件库Altera的仿真库位置为*:\altera\quartus\eda\sim_lib所谓时序仿真,就是在综合后仿真的基础上加上时延文件(sdf文件),综合考虑了路径延迟和门延迟的情况,验证电路是否存在时序违规。

时序仿真需要:1.综合后的门级网表,注意这里变成了*.vo文件,而不是原来功能仿真中所需要的HD L源代码.2.测试激励3.元件库Altera的仿真库位置为*:\altera\quartus\eda\sim_lib4.较门级仿真还需要具有包含时延信息的反标记文件*.sdf可以有两种方法实现门级仿真,或时序仿真。

1.工程编译成功后,自动启用ModelSim来运行门级仿真,前提是要在Quartus II的Options中设置好ModelSim的路径(和有些参考PDF上说的环境变量好像无关,至少我用的Quartus II 9.0 Web Edti on是这样的)具体方法是,进入Quartus9.0->Tools->Options,在Categroy里选中General下的EDA Tool Options,在ModelSim右边的Location of Executable中双击来改变路径,就并且在工程中设置了自动启动ModelSim,就可以自动启用了。

ModelSim SE仿真Altera库的一些问题 常见仿真错误 问题 合集

ModelSim SE仿真Altera库的一些问题常见仿真错误问题合集1. modelsim怎么调用altera的库仿真啊?(megafunctions)以前有个帖子说把quartus安装目录下的sim文件夹里面的文件编译进modelsim里面就可以了,可是sim文件夹里面我要的那个函数不是.v文件啊,还有他里面的一些.vhd文件怎么编译错误啊?是eda/sim_lib里,编译错误,我想是你编译的顺序不对用EDA/SIM_LIB中文件直接放到PROJECT中,你需要看看它的告错信息。

一般是缺库。

你可以按提示缺的库,在FILE/NEW/LIBRARY菜单里创建一个映射到WORK的库。

这样一般就好了。

如何在modelsim里如altera的库中做后仿真啊,急死了我用synplify综合后,用modelsim做后仿真,我在modelsim里面加入了C:quartusedasim_libmodelsimvhdl里面的两个库,但是编译的时候还是提示我找不到library apex20k。

还要加什么库啊???郁闷死了vlib apex20kvmap apex20k apex20kvcom -work apex20k c:/quartus/eda/sim_lib/apex20k_atoms.vhdvcom -work apex20k c:/quartus/eda/sim_lib/apex20k_components.vhd谢谢i8086,我现在知道怎么加入altera的库了,但是错误依然在,不知道是什么原因,modelsim里面的提示如下:vcom -reportprogress 300 -work work {D:/caiyang/rev_1/caiyang_1.vhd}# Model Technology ModelSim SE vcom 5.7e Compiler 2003.07 Jul 8 2003# -- Loading package standard# ** Error: (vcom-19) Failed to access library 'acex2k' at "acex2k".# No such file or directory. (errno = ENOENT)# ** Error: D:/caiyang/rev_1/caiyang_1.vhd(7): Library acex2k not found.# -- Loading package std_logic_1164# -- Loading package numeric_std# -- Loading package components# ** Error: D:/caiyang/rev_1/caiyang_1.vhd(12): Unknown identifier: acex2k# ** Error: D:/caiyang/rev_1/caiyang_1.vhd(14): VHDL Compiler exitinglibrary ieee, acex2k;use ieee.std_logic_1164.all;use ieee.numeric_std.all;library synplify;use ponents.all;use acex2k.acex2k_components.all;~~~~~~~~~~~~~~~就是提示找不到这个东西,这是用synplify综合后的文件的前面几行代码。

modelsim下创建Altera仿真库的问题汇总

ModelSim SE中Altera仿真库的添加在ModelSim中进行仿真需要加入Quartus提供的仿真库,原因是下面三个方面:·Quartus不支持Testbench;·调用了megafunction或者lpm库之类的Altera的函数;·时序仿真要在Modelsim下做仿真。

下面以Altera器件为例,介绍如何在ModelSim中加入Altera的仿真库,Quartus II软件中自带有Altera的仿真库,只要把它拿到ModelSim中去编译一下就可以了,具体步骤如下:1.设置仿真库路径打开ModelSim安装目录(我用的是ModelSim SE 6.5版本,安装在D:/ModelSim_6.5b目录下),新建文件夹altera,我们就在该目录下存放预编译的各种Altera库。

启动ModelSim SE 6.5,在主窗口执行【File】/【Change Directory】命令将路径转到altera 文件夹。

或在命令行中执行cd D:/ModelSim_6.5b/altera。

2.新建库Quartus II中提供的仿真库文件存放的路径是.../altera/91/quartus/eda/sim_lib,每个库文件提供了两种形式:.v(V erilog)格式和.vhd(VHDL)格式两种,根据你所用的语言选择使用。

用于编译资源库的文件有220model.v,220model.vhd,220pack.vhd,altera_mf.v,altera_mf.vhd,altera_mf_components.vhd,altera_primitives.v,altera_primitives.vhd,altera_primitives_components.vhd文件。

网上的很多教程都是把这些文件一起编译,这样适用于V erilog和VHDL混合仿真,但如果只用一种语言,如V erilog则完全没必要全部编译。

Modelsim使用常见问题及解决办法

Modelsim使用常见问题及解决办法在ISE启动modelsim时遇到问题1。

我在ISE中启动modelsim时出现了下面的错误Loading work.tb_ic1_func# ** Error: (vsim-19) Failed to access library 'xilinxcorelib_ver' at "xilinxcorelib_ver".# No such file or directory. (errno = ENOENT)# ** Error: (vsim-19) Failed to access library 'unisims_ver' at "unisims_ver". # No such file or directory. (errno = ENOENT)# Loading work.fifoctlr_ic_v2# ** Error: (vsim-19) Failed to access library 'xilinxcorelib_ver' at "xilinxcorelib_ver".# No such file or directory. (errno = ENOENT)# ** Error: (vsim-19) Failed to access library 'unisims_ver' at "unisims_ver". # No such file or directory. (errno = ENOENT)# ** Error: (vsim-3033) fifoctlr_ic_v2.v(126): Instantiation of 'BUFGP' failed. The design unit was not found.是什么原因?“点到仿真模式,在source里面选中你建立工程选择的芯片,然后看Processes,点开,有个compile HDL simulation library,运行一下就OK了”2.ISE用modelsim仿真提示:# ** Error: (vish-4014) No objects found matching '*'.结果仿真时老是报错:# ** Error: (vish-4014) No objects found matching '*'.# Error in macro ./test_top_tb.fdo line 10# (vish-4014) No objects found matching '*'.# while executing# "add wave *"解决办法,改modelsim.ini文件中的一个参数:VoptFlow = 0# ** Error: (vish-4014) No objects found matching 'XXXX'.在之前的设计里有一个信号XX, 并且保持在wave.do文件里现在这个信号在你的设计你被去掉了,modelsim仍然调用旧的wave.do,找不到对应的信号XX,就报错误这个错误可以忽略3.当对IP核修改后,用Modelsim仿真显示:No entity is bound for inst 或CE is not in the entity。

Modelsim仿真PLL遇到的问题

Modelsim仿真PLL遇到的问题Modelsim仿真PLL遇到的问题今天在用Modelsim做一个后仿真的时候,发现PLL的没有输出,在设定不同的测试时钟频率的时候,出现一下三种情况:(1)当输入时钟周期小于在例化PLL时选择的输入时钟周期时,在运行仿真时,会出现以下警告信息:Warning : Input clock freq. is under VCO range. Cyclone III PLL may lose lock(2)当输入时钟周期大于在例化PLL时选择的输入时钟周期时,在运行仿真时,会出现以下警告信息:Warning : Input clock freq. is over VCO range. Cyclone III PLL may lose lock这上面这两种情况下,PLL都不会正常工作。

如果出现上面第一种情况,可以将输入测试时钟的周期设置大一些。

如果出现第二种情况,可以将输入测试时钟的周期设置小一些。

(3)当输入时钟周期等于在例化PLL时选择的输入时钟周期时,在运行仿真时,会出现以下信息:Note : Cyclone III PLL locked to incoming clock这有这种情况下PLL才能正常工作根据以上这三种情况,我判断应该是在编译后生成的.vo文件中,包含了PLL的设置信息,如PLL的输入频率。

但是我也发现比较困惑的一点就是输入测试时钟的频率和例化PLL时设置的输入时钟频率也不一定非要相等,PLL才能工作。

不知道这是什么原因。

但是也并不是只要将测试时钟的频率设定为与PLL的输入时钟完全相同时就一定可以正常工作,例如我例化的PLL 的输入时钟频率为400MHz(从器件手册上看,Cyclone III 的PLL输入是支持这么高的频率的),在测试时我把输入测试时钟的频率设置为2.5ns,但是PLL没有输出。

当我改为5ns的时候就有输出了。

另外,在进行前仿真是,也发现了同样的问题,即如果PLL的输入时钟频率不合适那么PLL将不能够工作,只不过在PLL不能正常工作的时候,Modelsim没有任何提醒,只有在正常工作时,才出现Note : Cyclone III PLL locked to incoming clock。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ModelSim作布局布线后仿真的库问题Modelsim是目前最流行的应用最广泛的FPGA仿真器,是Mentor Graphics的子公司Model T echnology开发的。

因为Modelsim好学易用,调试方便,仿真速度快,功能强大,所以很多芯片厂商的开发系统都OEM Mentor Graphics公司的Modelsim仿真器,包括Xilinx,Alter a,Lattice和Actel等。

Modelsim是一个单内核仿真器,同一个内核可以进行VHDL仿真、Verilog仿真和VHDL/Verilog混合仿真;支持所有的VHDL和Verilog标准;采用直接编译技术(Direct-Compiled),大大提高了HDL编译和仿真速度。

Modelsim支持三个层次的仿真:RTL仿真、综合后仿真和布局布线后仿真。

为了加快仿真速度,一般情况下设计中调用的库都是已经进行编译过的,然后对设计进行仿真,此时仿真器直接调用库中已经编译过的单元,而不是再次对设计中的单元模块进行编译。

所以如果要对设计进行综合后仿真和布局布线后仿真,必须先对设计中调用的库进行编译处理。

这也是本文的重点内容。

因为每个厂商的库不一样,而且同一个厂商,不同的器件库就有可能不同,所以下面就目前国内比较常用的几个公司的芯片的库问题分别进行探讨。

1.Xilinx公司的器件:其库的处理方式有两种,一种是在Xilinx的网站上,我们可以下载到压缩文件xilinx_lib_4.zip,解压缩后有一个xilinx_lib_4.tcl(将来的版本可能会升级)。

单独运行Modelsim,然后在工具菜单中有一项是执行宏(这里Modelsim5.5 和5.6、5.7有一些差异,不过在5.5中仍可以找到执行宏Execute Macro),运行xilinx_lib_4.tcl后可以看到。

你可以根据你的厂商软件版本选择,指定Xilinx 的安装路径,在Install Path中指定你编译后的数据将要放的目录位置(可以是任何一个目录,最好是设计者数据盘中的某个目录,因为库编译一次就可以了,重新安装软件不需要重新编译库)。

对于Xilinx作布局布线后仿真只需要simprim库即可;如果要作综合后仿真,就需要编译Unisim库;如果设计中调用了CoreGen产生的核就需要编译CoreGen库。

这应该根据设计者的具体情况进行选择。

如果编译完了后,在Modelsim中库会自动变为标准库(注意:Xilinx提供的早期脚本文件作不到这一点)。

所谓标准库,也就是说这个库会和IEEE这些库一样,当Modelsim启动时,这些库会自动加载,里面的单元在VHDL代码中可以随意调用。

比如:在布局布线后的VHDL 文件中大家可以看到Library simprim这样的语句。

当然也可以自己手动改变这些库的性质,只用修改在Modelsim安装路径下的Modelsim.ini文件即可。

比如:修改后的Modelsim.ini 可以看到为[Library]std = $MODEL_TECH/../stdieee = $MODEL_TECH/../ieeeverilog = $MODEL_TECH/../verilogstd_developerskit = $MODEL_TECH/../std_developerskitsynopsys = $MODEL_TECH/../synopsysmodelsim_lib = $MODEL_TECH/../modelsim_libsimprim = D:/test/test/simprimunisim = D:/test/test/unisimlogiblox = D:/test/test/logibloxsimprims_ver = D:/test/test/simprims_verunisims_ver = D:/test/test/unisims_verxilinxcorelib = D:/test/test/xilinxcorelibxilinxcorelib_ver = D:/test/test/xilinxcorelib_verlpm = d:/test/test/lpm…可以看到修改后的文件中simprim库和IEEE等标准库处于同等的位置。

如果关于这些库的行不加到这个文件中,那么每做一个项目的时候,设计者都要建立一个库,然后把这个库和编译后的目录映射好。

比如:在Modelsim中用命令vlib simprimvmap simprim D:/test/test/simprim在一个项目中设置的库对其他项目是无效的,所以如果你经常用一些库,就可以把这些库设置成标准库。

另外一种编译库的方法更本质一些,上面这种方法是厂商做一个脚本文件方便大家对库进行处理。

事实上,我们可以手工处理这些库。

在Xilinx的ISE安装目录下,比如:D:/xili nx/vhdl/src和D:/xilinx/Verilog/src下都有这些库源文件;simprim库的源文件就在…/src/simprims目录下,CoreGen库的源文件就在…/src/XilinxCoreLib下等。

在Modelsim的命令窗口运行下面的命令即可:vlib simprimvmap simprim d:/test/test/simprim (路径可以自己任意指定)vcom –work simprim $XILINX/vhdl/src/simprims/simprim_Vcomponents.vhdvcom –work simprim $XILINX/vhdl/src/simprims/simprim_Vpackage.vhdvcom –work simprim $XILINX/vhdl/src/simprims/simprim_VITAL.vhd(注意:编译顺序不能颠倒),Unisim库如下所示:vlib unisimvmap unisim D:/test/test/unisimvcom -work unisim $XILINX/vhdl/src/unisims/unisim_VCOMP.vhdvcom -work unisim $XILINX/vhdl/src/unisims/unisim_VPKG.vhdvcom -work unisim $XILINX/vhdl/src/unisims/unisim_VITAL.vhdvcom -work unisim $XILINX/vhdl/src/unisims/unisim_VCFG4K.vhd如果是Verilog语言,可以进行同样的处理。

不过必须注意一定要编译glbl.v文件。

如果要了解更详细的信息,可以参考相关文献。

库编译后就可以手工修改安装目标下的Modelsim.ini文件。

修改后的文件如前所述即可。

2.Altera公司的器件:对于Altera公司,其MaxplusII软件能开发的器件的库的名字是alt_vtl,仿真模型在maxp lus2/vhdl87/vital或者maxplus2/vhdl93/vital下面可以找到。

如果是Quartus,则库的名字不再用alt_vtl。

该公司不同的器件库名字是不一样的,库名如下:如果是lpm库,要编译的文件是220model.vhd和220pack.vhd,在安装目录下可以搜索的到。

比如:…quartus/eda/sim_lib/关于lpm库设置过程是这样的,进入MODELSIM,创建一个库,例如:vlib lpmvmap lpm <…/myalteralib/lpm>(自己指定绝对路径,或者用菜单创建)vcom –work lpm <…/sim_lib/220pack.vhd> (自己指定绝对路径,或者用菜单编译)vcom –work lpm <…/sim_lib/220model.vhd> (自己指定绝对路径,或者用菜单编译)现在可以到Modelsim的安装目录,编辑modelsim.ini。

[Library]std = $MODEL_TECH/../stdieee = $MODEL_TECH/../ieeeverilog = $MODEL_TECH/../verilogstd_developerskit = $MODEL_TECH/../std_developerskitsynopsys = $MODEL_TECH/../synopsysmodelsim_lib = $MODEL_TECH/../modelsim_liblpm = <…/myalteralib/lpm>(一定要和自己刚才创建的lpm库目录一致)此时,即可在Modelsim的library窗口中看到有这个库了。

其他的库同理可以这么作。

下面举例apex20k库为例:运行Modelsim,创建库apex20k,vlib apex20kvmap apex20k <…/myalteralib/apex20k>vcom –work apex20k <…/eda/sim_lib/apex20k_atoms.vhd>vcom –work apex20k <…/eda/sim_lib/apex20k_componenets.vhd>然后修改modelsim.ini文件即可。

3.Actel公司的器件:因为大多数设计者使用Actel公司器件的原因是其反熔丝特性,这些芯片是一次编程的,所以布局布线后仿真显的更加重要。

安装Actel公司的Designer后其库的原文件位置是:VHDL 的VITAL Library: <Drive>:/Actel/ Designer_R1-2001/ lib/vtl/95Verilog Library: <Drive>:/Actel/ Designer_R1-2001/lib/vlog此处以VHDL为例进行库编译说明。

对应于不同的器件系列其库名字分别是act1, act2, ac t3, a3200dx, a40mx, a42mx, a54sx,a54sxa, ex and a500k等。

V erilog的库名稍微有所不同,库名分别是act1, act2, act3, 3200dx, 40mx, 42mx, 54sx, 54sxa, ex and a500k等。

源文件分别和库名相对应,很容易看出。

下面以act2库为例进行说明。

vlib act2vmap act2 d:/test/test/act2vcom –93 –work act2 <Drive>:/Actel/ Designer_R1-2001/ lib/vtl/95/act2.vhd然后对Modelsim安装目录下的Modelsim.INI文件进行修改即可。