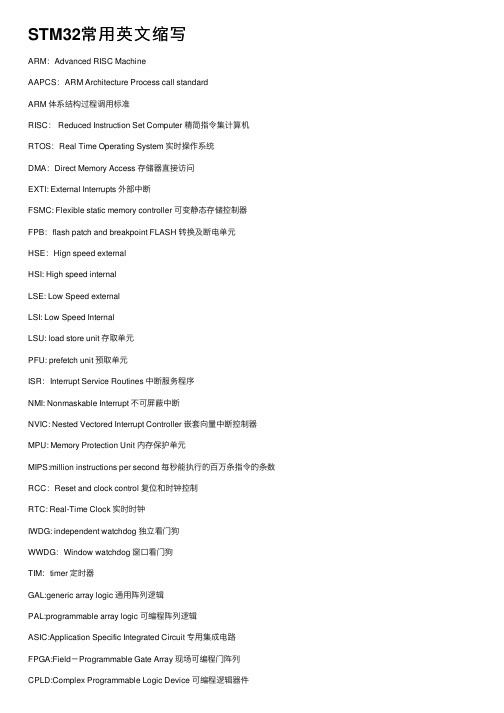

Stm32常见英文缩写

stm32常用英文词汇

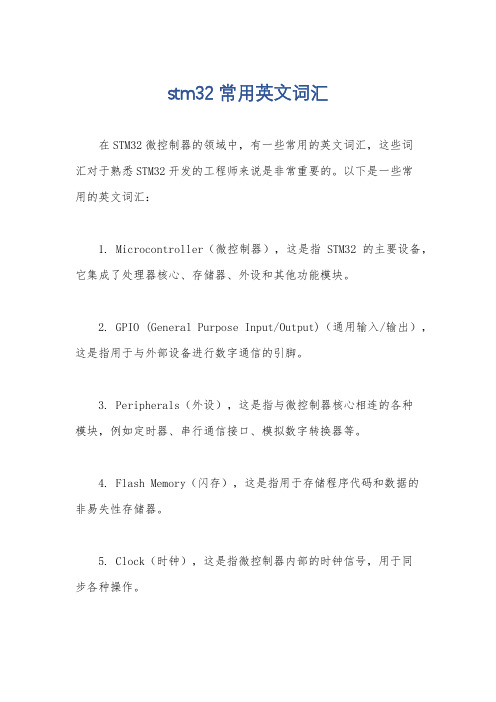

stm32常用英文词汇在STM32微控制器的领域中,有一些常用的英文词汇,这些词汇对于熟悉STM32开发的工程师来说是非常重要的。

以下是一些常用的英文词汇:1. Microcontroller(微控制器),这是指STM32的主要设备,它集成了处理器核心、存储器、外设和其他功能模块。

2. GPIO (General Purpose Input/Output)(通用输入/输出),这是指用于与外部设备进行数字通信的引脚。

3. Peripherals(外设),这是指与微控制器核心相连的各种模块,例如定时器、串行通信接口、模拟数字转换器等。

4. Flash Memory(闪存),这是指用于存储程序代码和数据的非易失性存储器。

5. Clock(时钟),这是指微控制器内部的时钟信号,用于同步各种操作。

6. Interrupt(中断),这是指微控制器在发生特定事件时暂停当前执行的程序,转而执行特定的中断服务程序。

7. DMA (Direct Memory Access)(直接存储器访问),这是指一种数据传输方式,可以在不干扰处理器的情况下直接在外设和存储器之间传输数据。

8. Bootloader(引导加载程序),这是指用于启动系统并加载应用程序的特殊程序。

9. IDE (Integrated Development Environment)(集成开发环境),这是指用于编写、编译和调试STM32应用程序的软件工具。

10. Firmware(固件),这是指存储在微控制器中的程序代码和数据,用于控制设备的操作。

这些词汇是在STM32开发中经常会遇到的,了解它们的含义对于理解和使用STM32微控制器是非常重要的。

希望这些信息能够对你有所帮助。

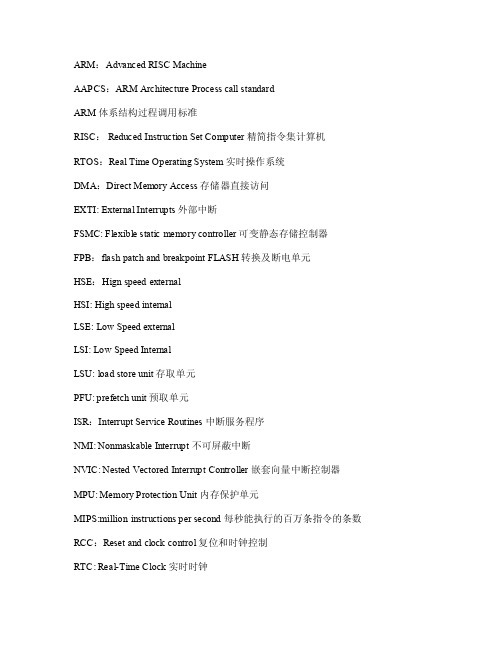

STM32常用英文缩写

ARM:Ad vance d RIS C Mac hineAAPC S:ARM Arch itect ure P roces s cal l sta ndardARM体系结构过程调用标准RI SC:R educe d Ins truct ion S et Co mpute r 精简指令集计算机RTO S:Rea l Tim e Ope ratin g Sys tem 实时操作系统DMA:Dire ct Me moryAcces s 存储器直接访问EXTI: Ext ernal Inte rrupt s 外部中断FS MC: F lexib le st aticmemor y con troll er 可变静态存储控制器F PB:fl ash p atchand b reakp ointFLASH转换及断电单元HSE:H ign s peedexter nalHSI:Highspeed inte rnalLSE: LowSpeed exte rnalLSI: LowSpeed Inte rnalLSU: load stor e uni t 存取单元PF U: pr efetc h uni t 预取单元IS R:Int errup t Ser viceRouti nes 中断服务程序NMI: Non maska ble I nterr upt 不可屏蔽中断NVI C: Ne stedVecto red I nterr upt C ontro ller嵌套向量中断控制器MPU: Memo ry Pr otect ion U nit 内存保护单元MIP S:mil lioninstr uctio ns pe r sec ond 每秒能执行的百万条指令的条数RCC:R esetand c lockcontr ol 复位和时钟控制RTC: Rea l-Tim e Clo ck 实时时钟I WDG:indep enden t wat chdog独立看门狗WW DG:Wi ndowwatch dog 窗口看门狗TIM:timer定时器GAL:gener ic ar ray l ogic通用阵列逻辑PA L:pro gramm ablearray logi c 可编程阵列逻辑ASIC:Appl icati on Sp ecifi c Int egrat ed Ci rcuit专用集成电路F PGA:F ield-Progr ammab le Ga te Ar ray 现场可编程门阵列C PLD:C omple x Pro gramm ableLogic Devi ce 可编程逻辑器件端口AFIO:alte rnate func tionIO 复用 IO 端口GP IO:ge neral purp ose i nput/outpu t 通用IO 端口IOP(A-G):IO p ort A - IO port G (例如:IOP A:IOportA)C AN:Co ntrol ler a rea n etwor k 控制器局域网FLITF:TheFlash memo ry in terfa ce 闪存存储器接口I2C: Int er-in tegra ted c ircui t 微集成电路I IS:i ntegr ate i nterf ace o f sou nd 集成音频接口JTAG:join t tes t act ion g roup联合测试行动小组SPI:S erial Peri phera l Int erfac e 串行外围设备接口 SDIO: SDI/OUART: Univ ersal Sync hr./A synch. Rec eiver Tran smitt er 通用异步接收/发送装置USB: Univ ersal Seri al Bu s 通用串行总线寄存器相关CPS P: Cu rrent Prog ram S tatus Regi ster当前程序状态寄存器SPSP: sav ed pr ogram stat us re giste r 程序状态备份寄存器CS R:clo ck co ntrol/stat us re giste r 时钟控制状态寄存器LR: lin k reg ister链接寄存器SP: sta ck po inter堆栈指针MSP: mai n sta ck po inter主堆栈指针PS P:pro cessstack poin ter在S TM32的固件库中定义了三个结构体与这三个寄存器组相对应,这三个结构体与ARM手册中寄存器的对应关系如下:一、N VIC寄存器组STM32的固件库中有如下定义:type def s truct{vu32ISER[2]; u32RESER VED0[30];vu32 ICE R[2];u32 RSE RVED1[30];vu32 IS PR[2];u32 RE SERVE D2[30];vu32ICPR[2]; u32RESER VED3[30];vu32 IAB R[2];u32 RES ERVED4[62];v u32 I PR[11];}NVIC_TypeD ef;它们对应ARM手册中的名称为ISE R = I nterr upt S et-En ableRegis tersICER= Int errup t Cle ar-En ableRegis tersISPR= Int errup t Set-Pend ing R egist erIC PR =Inter ruptClear-Pend ing R egist erIA BR =Activ e Bit Regi sterIPR = Inte rrupt Prio rityRegis ters每个寄存器有240位,以Inter ruptSet-E nable Regi sters说明,IS ER[0]对应中断源0~31,ISER[1]对应中断源32~63,ST M32只有60个中断源,所以没有ISER[2:7]。

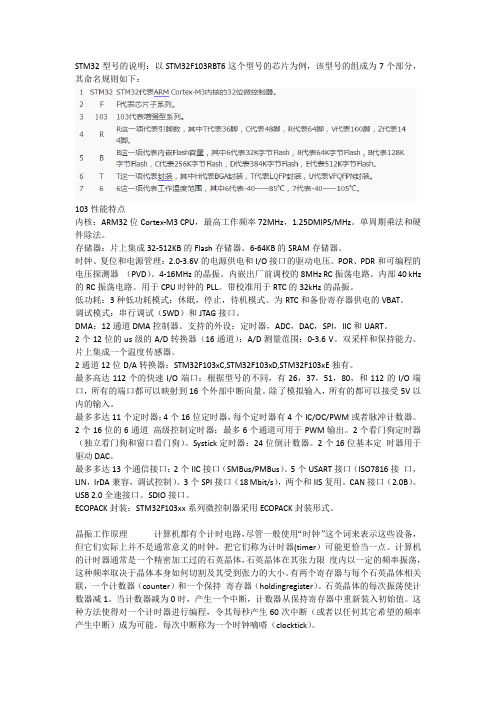

stm32 命名规则

stm32 命名规则

STM32是一款非常流行的嵌入式系统开发板,它的命名规则如下:

1. STM32的命名规则遵循一定的规律,其中“STM”代表意大利半导体公司STMicroelectronics,而“32”表示该系列芯片采用了ARM Cortex-M3或M4内核。

2. 在STM32系列中,每个型号都有一个特定的字母表示其性能等级。

例如,F表示高性能、L表示低功耗、C表示连接器等。

3. 在型号名称的末尾,通常还会添加一些数字来表示不同版本或不同

封装方式。

例如,STM32F103C8T6中,“103”代表该芯片为第一

代产品,“8”表示其内存容量为64KB,“T6”则代表其封装方式为LQFP-48。

4. 对于某些特殊用途的芯片,如USB控制器和以太网控制器等,则会在型号名称中添加相应的字母以区分。

例如,STM32F407VGT6中,“V”代表其具有USB OTG功能,“G”则代表其集成了以太网

MAC控制器。

总之,STM32系列芯片的命名规则十分详细和精确,在选购和使用时需要根据具体需求进行细致分析和比较。

STM32SPI详解

STM32SPI详解1、SPI简介SPI 规定了两个 SPI 设备之间通信必须由主设备 (Master) 来控制次设备 (Slave). ⼀个 Master 设备可以通过提供 Clock 以及对 Slave 设备进⾏⽚选 (Slave Select) 来控制多个 Slave 设备, SPI 协议还规定 Slave 设备的 Clock 由 Master 设备通过 SCK 管脚提供给 Slave 设备, Slave 设备本⾝不能产⽣或控制 Clock, 没有 Clock 则 Slave 设备不能正常⼯作。

2、SPI特点2.1、SPI控制⽅式采⽤主-从模式(Master-Slave) 的控制⽅式。

SPI 规定了两个 SPI 设备之间通信必须由主设备 (Master) 来控制次设备 (Slave). ⼀个 Master 设备可以通过提供 Clock 以及对 Slave 设备进⾏⽚选 (Slave Select) 来控制多个 Slave 设备, SPI 协议还规定 Slave 设备的 Clock 由 Master 设备通过 SCK 管脚提供给 Slave 设备, Slave 设备本⾝不能产⽣或控制 Clock, 没有 Clock 则 Slave 设备不能正常⼯作。

2.2、SPI传输⽅式采⽤同步⽅式(Synchronous)传输数据Master 设备会根据将要交换的数据来产⽣相应的时钟脉冲(Clock Pulse), 时钟脉冲组成了时钟信号(Clock Signal) , 时钟信号通过时钟极性(CPOL) 和时钟相位 (CPHA) 控制着两个 SPI 设备间何时数据交换以及何时对接收到的数据进⾏采样, 来保证数据在两个设备之间是同步传输的。

2.3、SPI数据交换SPI数据交换框图上图只是对 SPI 设备间通信的⼀个简单的描述, 下⾯就来解释⼀下图中所⽰的⼏个组件(Module):SSPBUF,Synchronous Serial Port Buffer, 泛指 SPI 设备⾥⾯的内部缓冲区, ⼀般在物理上是以 FIFO 的形式, 保存传输过程中的临时数据; SSPSR, Synchronous Serial Port Register, 泛指 SPI 设备⾥⾯的移位寄存器(Shift Regitser), 它的作⽤是根据设置好的数据位宽(bit-width) 把数据移⼊或者移出 SSPBUF;Controller, 泛指 SPI 设备⾥⾯的控制寄存器, 可以通过配置它们来设置 SPI 总线的传输模式。

stm32f103c8t6各个字母含义例题

1. S - Single- 作为STM32F103C8T6中的一员,S代表Single,意味着这是一款单片机,是一种单一芯片解决方案。

2. T - Cortex-M3- 这款单片机采用了Cortex-M3内核,该内核是由ARM(Advanced RISC Machines)公司推出的低功耗、高性能的32位处理器核心。

3. M - Microcontroller- M代表微控制器(Microcontroller),指的是这款芯片的主要功能是作为微控制器来使用。

它集成了处理器、存储器和各种输入/输出接口,用于控制各种电子设备。

4. 32- 32代表这款单片机是32位的,相比传统的8位和16位微控制器,32位微控制器具有更高的性能和更大的内存容量。

5. F - Family- F代表Family,表示这款单片机属于STM32系列产品中的一员,STM32系列产品是由意法半导体(STMicroelectronics)公司推出的32位MCU产品线。

6. 103- 这个数字代表这款芯片的具体型号或者版本,STM32F103C8T6是STM32F103系列中的具体型号。

7. C8- C8代表这款芯片的具体型号,可能与其功能、引脚数或者封装有关。

8. T6- T6则代表芯片的封装类型,可能是指这款芯片的封装类型或其它特定规格。

总结起来,STM32F103C8T6代表着一款单片机产品,采用了Cortex-M3内核,属于STM32系列产品中的一员,是一款32位微控制器,具有高性能和丰富的外设接口,适合用于各种嵌入式系统的设计和开发。

在我的个人观点和理解方面,STM32F103C8T6作为一款功能强大、灵活多样的单片机产品,具有广泛的应用前景。

其32位处理器和丰富的外设接口,使其在工业控制、汽车电子、智能家居等领域都有着很大的发展潜力。

作为创客和电子爱好者,利用STM32F103C8T6进行嵌入式系统的设计和开发,也是一项有趣且具有挑战性的工作。

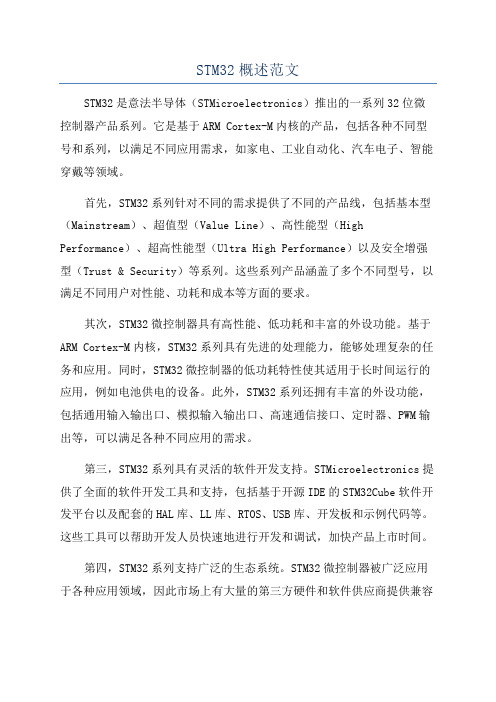

STM32概述范文

STM32概述范文STM32是意法半导体(STMicroelectronics)推出的一系列32位微控制器产品系列。

它是基于ARM Cortex-M内核的产品,包括各种不同型号和系列,以满足不同应用需求,如家电、工业自动化、汽车电子、智能穿戴等领域。

首先,STM32系列针对不同的需求提供了不同的产品线,包括基本型(Mainstream)、超值型(Value Line)、高性能型(High Performance)、超高性能型(Ultra High Performance)以及安全增强型(Trust & Security)等系列。

这些系列产品涵盖了多个不同型号,以满足不同用户对性能、功耗和成本等方面的要求。

其次,STM32微控制器具有高性能、低功耗和丰富的外设功能。

基于ARM Cortex-M内核,STM32系列具有先进的处理能力,能够处理复杂的任务和应用。

同时,STM32微控制器的低功耗特性使其适用于长时间运行的应用,例如电池供电的设备。

此外,STM32系列还拥有丰富的外设功能,包括通用输入输出口、模拟输入输出口、高速通信接口、定时器、PWM输出等,可以满足各种不同应用的需求。

第三,STM32系列具有灵活的软件开发支持。

STMicroelectronics提供了全面的软件开发工具和支持,包括基于开源IDE的STM32Cube软件开发平台以及配套的HAL库、LL库、RTOS、USB库、开发板和示例代码等。

这些工具可以帮助开发人员快速地进行开发和调试,加快产品上市时间。

第四,STM32系列支持广泛的生态系统。

STM32微控制器被广泛应用于各种应用领域,因此市场上有大量的第三方硬件和软件供应商提供兼容的产品和解决方案。

这使得开发人员能够更加便捷地选择合适的硬件和软件组件,并加快产品的开发进度。

此外,STM32系列还支持丰富的安全功能。

安全是现代嵌入式系统设计中的一个重要考虑因素,尤其是在物联网和智能设备应用中。

单片机英文缩写全称及中文名称(整理)(二)2024

单片机英文缩写全称及中文名称(整理)(二)引言:单片机作为一种重要的嵌入式系统,被广泛应用于各个领域。

在学习和使用单片机时,了解其英文缩写全称及中文名称是非常重要的。

本文整理了单片机的英文缩写全称及中文名称,旨在帮助读者更好地理解和应用单片机技术。

正文:一、常见的单片机英文缩写全称及其中文名称:1. MCU:Microcontroller Unit,中文名称为“微控制器单元”。

微控制器单元是一种集成了中央处理器(CPU)、存储器、输入/输出(I/O)接口以及外设控制器的单片机。

2. SOC:System-on-a-Chip,中文名称为“片上系统”。

片上系统是一种将微处理器、外设和其他功能集成在一颗芯片上的单片机。

3. ARM:Advanced RISC Machines,中文名称为“高级精简指令集机器”。

高级精简指令集机器是一种32位的复杂指令集(CISC)微处理器架构,广泛应用于单片机和嵌入式系统。

4. DSP:Digital Signal Processor,中文名称为“数字信号处理器”。

数字信号处理器是一种专用的微处理器,用于高效地处理数字信号,常用于音频、视频、通信和测控领域。

5. FPGA:Field-Programmable Gate Array,中文名称为“现场可编程门阵列”。

现场可编程门阵列是一种可被用户重新配置和重新编程的集成电路,常用于硬件逻辑设计和数字信号处理。

二、单片机英文缩写全称及中文名称的应用领域:1. 工业控制领域:- PLC:Programmable Logic Controller,可编程逻辑控制器,用于工业自动化控制系统。

- DCS:Distributed Control System,分布式控制系统,用于工业过程控制和监控。

2. 通信领域:- GSM:Global System for Mobile Communications,全球移动通信系统,用于移动通信。

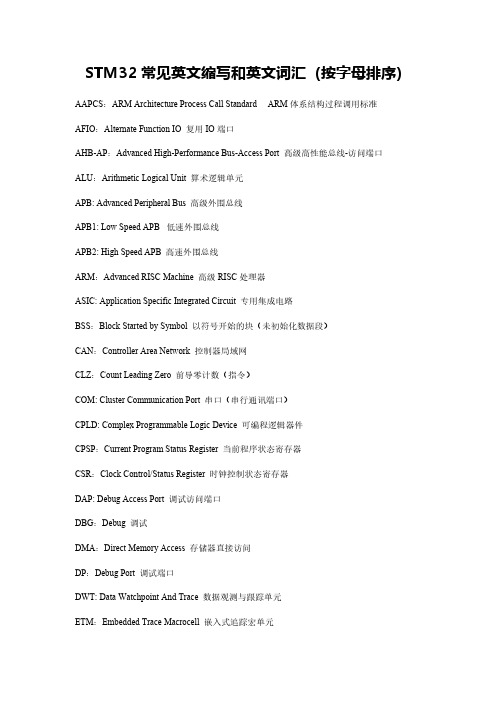

STM32嵌入式常见英文缩写和词汇

STM32常见英文缩写和英文词汇(按字母排序)AAPCS:ARM Architecture Process Call Standard ARM体系结构过程调用标准AFIO:Alternate Function IO 复用IO端口AHB-AP:Advanced High-Performance Bus-Access Port 高级高性能总线-访问端口ALU:Arithmetic Logical Unit 算术逻辑单元APB: Advanced Peripheral Bus 高级外围总线APB1: Low Speed APB 低速外围总线APB2: High Speed APB 高速外围总线ARM:Advanced RISC Machine 高级RISC处理器ASIC: Application Specific Integrated Circuit 专用集成电路BSS:Block Started by Symbol 以符号开始的块(未初始化数据段)CAN:Controller Area Network 控制器局域网CLZ:Count Leading Zero 前导零计数(指令)COM: Cluster Communication Port 串口(串行通讯端口)CPLD: Complex Programmable Logic Device 可编程逻辑器件CPSP:Current Program Status Register 当前程序状态寄存器CSR:Clock Control/Status Register 时钟控制状态寄存器DAP: Debug Access Port 调试访问端口DBG:Debug 调试DMA:Direct Memory Access 存储器直接访问DP:Debug Port 调试端口DWT: Data Watchpoint And Trace 数据观测与跟踪单元ETM:Embedded Trace Macrocell 嵌入式追踪宏单元EXTI: External Interrupts 外部中断FA:Full Ascending 满栈递增FD:Full Desending 满栈递减EA:Empty Ascending 空栈递增ED:Empty Desending 空栈递减FIQ:Fast Interrupt Request 快速中断请求FLITF:The Flash Memory Interface 闪存存储器接口FPB:Flash Patch And Breakpoint 闪存补丁及断点FPGA: Field Programmable Gate Array 现场可编程门阵列FSMC: Flexible Static Memory Controller 可变静态存储控制器GAL: Generic Array Logic 通用阵列逻辑GPIO:General Purpose Input/Output 通用IO端口HSE:High Speed External 高速外部HSI: High Speed Internal 高速内部I2C:Inter-Integrated Circuit 内置集成电路ICE:In-Circuit Emulator 在线仿真器IDE:Integrated Development Environment 集成开发环境IIS:Integrated Interface Of Sound 集成音频接口IRQ:Interrupt Request 中断请求ISR:Interrupt Service Routines 中断服务程序ITM: Instrumentation Trace Macrocell 测量跟踪宏单元IWDG: Independent Watchdog 独立看门狗JTAG:Joint Test Action Group 联合测试行动小组JTAG-DP:JTAG Debug Port JTAG 调试端口LR:Link Register 链接寄存器LSE: Low Speed External 低速外部LSI: Low Speed Internal 低速内部LSU: Load Store Unit 存取单元MIPS: Million Instructions Per Second 每秒能执行的百万级指令的条数MPU: Memory Protection Unit 内存保护单元MSP: Main Stack Pointer 主堆栈指针NMI: Non Maskable Interrupt 不可屏蔽中断NVIC: Nested Vectored Interrupt Controller 嵌套向量中断控制器PAL: Programmable Array Logic 可编程阵列逻辑PC:Program Counter 程序计数器PFU: Pre-Fetch Unit 预取单元PPB:Private Peripheral Bus 专用外设总线PSP:Process Stack Pointer 进程堆栈指针RCC:Reset And Clock Control 复位和时钟控制RISC:Reduced Instruction Set Computer 精简指令集计算机RO: Read Only 只读RTC: Real-Time Clock 实时时钟RTOS:Real Time Operating System 实时操作系统RW: Read Write 读写SDIO: Secure Digital I/O 安全数字输入输出SIMD:Single Instruction Multiple Data单指令多数据流SP:Stack Pointer 堆栈指针SPI:Serial Peripheral Interface 串行外设接口SPSR:Saved Program Status Register 程序状态保存寄存器SW:Software 软件SW-DP: Serial Wire Debug Port 串行线调试端口SWI:Software Interrupt 软中断SWJ-DP: Serial Wire JTAG Debug Port 串行线-JTAG调试端口TAP:Test Access Port 测试访问端口TIM:Timer 定时器TP: Trace Port 跟踪端口TPIU:Trace Port Interface Unit 跟踪端口接口单元USART: Universal Synchr./Asynch. Receiver/Transmitter 通用同步/异步收发器USB: Universal Serial Bus 通用串行总线VFP:Vector Floating Point 矢量浮点运算WWDG:Window Watchdog 窗口看门狗ZI: Zero Initial 零初始化STM32常见英文词汇(按字母排序)Access 访问Arbitration 仲裁Assembler 汇编器Banked 分组Big Endian 大端存储模式Binutils 连接器Bit-Band Alias 位段别名Bit-Band Region 位段区域Bit-Banding 位段(技术)Buffer 缓存Bus Matrix 总线矩阵Bus Splitter 总线分割Ceramic 陶瓷Comments 注释Context Switch 任务切换Decode 译码Directive 伪操作Disassembly 反汇编Execute 执行Fetch 取指Handler 处理者Heap 堆Instructions 指令Late-Arriving 迟到Latency 延时Literal Pool 数据缓冲池Little Endian 小端存储模式Load 加载Loader 装载器Optimization 优化Perform 执行Pre-Emption 抢占Prefetch 预读/预取指Prescaler 预分频器Process 进程/过程Pseudo-Instruction 伪指令Resonator 共振器Stack 栈Store 存储Tail-Chaining 尾链Task Switch 任务切换Thread 线程。

单片机缩写的英文全称及中文名称(一)

单片机缩写的英文全称及中文名称(一)引言概述:单片机(Microcontroller)是一种集成了中央处理器(CPU)、存储器和输入输出接口等功能的微型计算机系统。

它具有体积小、功耗低、功能强大等特点,广泛应用于电子设备控制、嵌入式系统等领域。

本文将介绍一些常用单片机的英文全称及中文名称,为读者更好地理解和应用单片机系统提供帮助。

正文:大点1: AVR(Advanced Virtual RISC)系列单片机- ATmega328P: 一款常用的AVR单片机,其特点包括8位RISC结构、32KB闪存、2KB SRAM等。

中文名称为“高级虚拟RISC系列单片机328P”。

- ATmega16: 另一款常见的AVR单片机,其特点包括8位RISC结构、16KB闪存、1KB SRAM等。

中文名称为“高级虚拟RISC系列单片机16”。

- ATtiny85: 一款小型的AVR单片机,特点包括8位RISC结构、8KB闪存、512B SRAM等。

中文名称为“高级虚拟RISC系列微型单片机85”。

大点2: PIC(Peripheral Interface Controller)系列单片机- PIC16F877A: 一款常用的PIC单片机,其特点包括8位RISC 结构、14KB闪存、368B SRAM等。

中文名称为“外围接口控制器系列单片机16F877A”。

- PIC18F452: 另一款常见的PIC单片机,其特点包括8位RISC 结构、32KB闪存、1536B SRAM等。

中文名称为“外围接口控制器系列单片机18F452”。

- PIC12F675: 一款小型的PIC单片机,特点包括8位RISC结构、1KB闪存、64B RAM等。

中文名称为“外围接口控制器系列微型单片机12F675”。

大点3: STM32(STMicroelectronics 32-bit)系列单片机- STM32F103C8T6:一款常用的STM32单片机,其特点包括32位ARM Cortex-M3核心、64KB闪存、20KB SRAM等。

STM32嵌入式开发常见缩写

ARM:Advanced RISC MachineAAPCS:ARM Architecture Process call standard ARM体系结构过程调用标准DMA:Direct Memory Access 存储器直接访问EXTI: External Interrupts 外部中断FSMC: Flexible static memory controller 可变静态存储控制器FPB:flash patch and breakpoint FLASH 转换及断电单元HSE:Hign speed externalHSI: High speed internalLSE: Low Speed externalLSI: Low Speed InternalLSU: load store unit 存取单元PFU:prefetch unit 预取单元ISR:Interrupt Service Routines 中断服务程序NMI:Nonmaskable Interrupt 不可屏蔽中断NVIC: Nested Vectored Interrupt Controller 嵌套向量中断控制器MPU: Memory Protection Unit 内存保护单元MIPS:million instructions per second 每秒能执行的百万条指令的条数RCC:Reset and clock control 复位和时钟控制RTC: Real-Time Clock 实时时钟RISC:Reduced Instruction Set Computer 精简指令集计算机RTOS:Real Time Operating System 实时操作系统IWDG: independent watchdog 独立看门狗WWDG:Window watchdog 窗口看门狗TIM:timer 定时器TIM1:高級控制定時器GAL:generic array logic 通用阵列逻辑PAL:programmable array logic 可编程阵列逻辑ASIC:Application Specific Integrated Circuit 专用集成电路FPGA:Field-Programmable Gate Array 现场可编程门阵列CPLD:Complex Programmable Logic Device 可编程逻辑器件端口AFIO:alternate function IO 复用IO端口GPIO:general purpose input/output 通用IO端口IOP(A-G):IO port A - IO port G (例如:IOPA:IO port A)CAN:Controller area network 控制器局域网FLITF:The Flash memory interface 闪存存储器接口I2C:Inter-integrated circuit 微集成电路IIS:integrate interface of sound 集成音频接口JTAG:joint test action group 联合测试行动小组,調試接口SPI:Serial Peripheral Interface 串行外围设备接口SDIO: SD I/OUART: Universal Synchr./Asynch. Receiver Transmitter 通用异步接收/发送装置,串口USB: Universal Serial Bus 通用串行总线寄存器相关CPSP:Current Program Status Register 当前程序状态寄存器SPSP:saved program status register 程序状态备份寄存器CSR:clock control/status register 时钟控制状态寄存器LR:link register 链接寄存器SP:stack pointer 堆栈指针MSP: main stack pointer 主堆栈指针PSP:process stack pointer 进程堆栈指针PC:program counter 程序计数器调试相关ICE:in circuit emulator 在线仿真ICE: Breaker 嵌入式在线仿真单元DBG:debug 调试IDE:integrated development environment 集成开发环境DWT: data watchpoint and trace 数据观测与跟踪单元ITM: instrumentation trace macrocell 测量跟踪单元ETM:embedded trace macrocell 嵌入式追踪宏单元TPIU:trace port interface unit 跟踪端口接口单元TAP:test access port 测试访问端口DAP: debug access prot 调试访问端口TP: trace port 跟踪端口DP:debug port 调试端口SWJ-DP: serial wire JTAG debug port 串行-JTAG 调试接口SW-DP: serial wire debug port 串行调试接口JTAG-DP:JTAG debug port JTAG 调试接口系统类IRQ:interrupt request 中断请求FIQ:fast interrupt request 快速中断请求SW:software 软件SWI:software interrupt 软中断RO:read only 只读(部分)RW:read write 读写(部分)ZI:zero initial 零初始化(部分)BSS:Block Started by Symbol 以符号开始的块(未初始化数据段)总线Bus Matrix总线矩阵Bus Splitter 总线分割AHB-AP:advanced High-preformance Bus-access port APB:advanced peripheral busAPB1: low speed APB APB2: high speed APBPPB:Private Peripheral Bus 专用外设总线杂类ALU:Arithmetic Logical Unit 算术逻辑单元CLZ:count leading zero 前导零计数(指令)SIMD:single instruction stream multiple data stream单指令流,多数据流VFP:vector floating point 矢量浮点运算词汇/词组Big Endian 大端存储模式Little Endian 小端存储模式context switch 任务切换(上下文切换)(CPU 寄存器内容的切换)task switch 任务切换literal pool 数据缓冲池词汇类/单词arbitration 仲裁access 访问assembler 汇编器disassembly 反汇编binutils 连接器bit-banding 位段(技术)bit-band alias 位段别名bit-band region 位段区域banked 分组buffer 缓存/ceramic 陶瓷fetch 取指decode 译码execute 执行Harvard 哈佛(架构)handler 处理者heap 堆stack 栈latency 延时load (LDR) 加载(存储器内容加载到寄存器Rn)store (STR) 存储(寄存器Rn内容存储到存储器)Loader 装载器optimization 优化process 进程/过程thread 线程prescaler 预分频器prefetch 预读/预取指perform 执行pre-emption 抢占tail-chaining 尾链late-arriving 迟到resonator 共振器指令相关instructions 指令pseudo-instruction 伪指令directive 伪操作comments 注释FA full ascending 满栈递增(方式)EA empty ascending 空栈递增(方式)FD full desending 满栈递减(方式)ED empty desending 空栈递减(方式)。

Stm32常见英文缩写(Stm32iscommonlyabbreviatedinEnglish)

Stm32常见英文缩写(Stm32 is commonly abbreviated in English)Embedded common English abbreviations and English vocabulary (in the collection)Author: the author of the English abbreviation and English vocabulary in EnglishThis article is a supplement to the original, reproduced please indicate the sourceThis article is linked to:/s/blog_574d08530100hzo2 (the disabled wing angel summed up well, thanks for his sharing)English abbreviationsARM: Advanced RISC MachineAAPCS: ARM Architecture Process call standardThe ARM architecture process calls standardRISC: Reduced Instruction Set Computer to simplify Instruction Set ComputerRTOS: Real Time Operating SystemDMA: Direct Memory Access Memory is accessed directly EXTI: External Interrupts External InterruptsFSMC: Flexible static memory controller variable static storage controllerFPB: flash patch and breakpoint flash conversion and power failure unitsHSE: Hign speed externalHSI: High speed internalThe LSE: Low Speed externalLSI: Low Speed InternalLSU: load store unit access unitPFU: prefetch unit prefetch unitISR: Interrupt Service Routines Interrupt Service RoutinesNMI: Nonmaskable Interrupt cannot be blockedNVIC: Nested Vectored Interrupt Controller Nested vector Interrupt ControllerMPU: Memory Protection Unit Memory Protection UnitMIPS: million instructions per second of the million instructions per secondRCC: Reset and clock control Reset and clock controlRTC: real-time ClockIWDG: independent watchdog independent watchdogWWDG: Window watchdog Window watchdogTIM: timerGAL: generic array logic common array logicPAL: programmable logic programmable array logicASIC: Application Specific Integrated Circuit special Integrated CircuitFPGA: field-gate Array Field Programmable Gate ArrayCPLD: Complex programmed Logic Device Programmable Logic DeviceportAFIO: alternate function IO multiplexing IO portGPIO: general purpose input/output generic IO portIOP (a-g) : IO port a-io port G (for example: IOPA: IO port A)CAN: Controller area network Controller LANFLITF: The Flash memory interface Flash memory interfaceI2C: inter-integrated circuit microintegrated circuitIIS: integrate interface of sound with audio interfaceJTAG: joint test action groupSPI: Serial Peripheral Interface SDIO: SD I/OUART: Universal Synchr. / Asynch. Receiver Transmitter Universal asynchronous Receiver/TransmitterUSB: Universal Serial Bus Universal Serial BusRegister correlationCPSP: Current Program Status Register Current Program Status RegisterSPSP: saved program status register program status backup registerCSR: clock control/status register clock controls the status registerLR: link register link registerSP: stack pointer pointerMSP: main stack pointer to main stack pointerPSP: process stack pointer process stack pointerPC: program counter program counterdebugICE: in circuit emulator online simulationICE Breaker embedded online simulation unitDBG: debug debugIDE: integrated development environment integration development environmentDWT: data watchpoint and trace data observation and tracking unitITM: instrumentation trace macrocell measurement tracking unitETM: embedded trace macrocell embedded tracking macro unitTPIU: trace port interface unit tracking port interface unitTAP: the test access port test access portDAP: debug access prot debug access portTP: trace port trace portDP: debug port debug portSwj-dp: serial wire JTAG debug port serial - JTAG debugging interfaceSw-dp: serial wire debug portSerial debugging interfaceJtag-dp: JTAG debug portJTAG debugging interfaceThe system classIRQ: interrupt request interrupt requestFIQ: fast interrupt request quickly interrupts the requestSW: software software: software interrupt soft interruptRO: read only read only (part)RW: read write (part)ZI: zero initial zero initialization (part)BSS: Block Started by Symbol Block (uninitialized data segment)The busBus Matrix Bus MatrixBus Splitter Bus divisionAHB - AP: advanced High - preformance bus-access port APB: advanced peripheral busAPB1: low speed APBAPB2: high speed APBPPB: Private Peripheral BusmiscellaneousALU: the Logical Unit Arithmetic logic UnitCLZ: count leading zero leading zero counting (instruction)SIMD: single instruction stream multiple data stream single instruction stream, multi-data streamVFP: vector floating point vector floating point operation Words/phrasesBig EndianLarge - end storage modeLittle Endian small end storage modeContext switch task switching (context switching) (switching between CPU register content)Task switch task switchLiteral pool data buffer poolWords/wordsArbitration by the arbitrationThe access to visitAssembler assemblerDisassembly disassemblyBinutils connectorBit - banding segment (technology)Bit-band alias segment aliasBit - band region regionBanked groupingThe buffer cache /Ceramic pottery and porcelainTake the fetch refers toDecode decodingThe execute performHarvard Harvard (architecture)Handler handlerHeap heapStack stackLatency time delayLoad (LDR) load (memory content loaded to register Rn) Store (STR) storage (register Rn content stored in memory) Loader LoaderOptimization optimizationProcess process/processThread the threadPrescaler predividerPrefetch prefetch/prefetch meansPerform performThe pre - emption preemptionTail - chaining tail chainNewest - arriving lateResonator cavityInstructions relatedInstructions instructionsThe pseudo - instruction directiveDirective pseudo operationComments commentsFA full ascending ascending (mode)EA empty ascending stack increment (method) FD full desending is regressiveED empty desending stack decrement (method)translation1. The number of wait states for a read operation programmed on - the - flyDynamic Settings (programmed on - the - fly) reads the number of wait statesRefer to the articleReference: 1. BSS /view/453125.htm? Fr = ala0_1BSS is the uninitialized data segment produced by the Unix linker. The other sections are the "text" segments containing the program code and the "data" section containing the initialized data. Variables in the BSS section have no value but name and size. This name was later used by many files, including PE. The "start block" refers to where the compiler handles uninitialized data. The BSS section does not include any data, but simply maintains the start and end addresses so that the memory area can be effectively zero at run time. The BSS section does not exist in the application's binary image file.In the sections of memory management architecture (such as Intel's 80 x86 systems) BSS, (Block Started by Symbol segment), often referred to as used to store global uninitialized variables in the program of a memory area, generally during initialization BSS section will be reset. The BSS section is a static memory allocation, which is where the program zeroes at the start.For example, after the completion of programs such as C language, the global variables that have been initialized are saved in the.data segment. The uninitialized global variables are saved in the.bss section.Both the text and data sections are in the executable (in the embedded system typically solidified in the mirror file), which is loaded from the executable file; The BSS section is not in the executable file and is initialized by the system.2. ISR reference: /view/32247? fromTaglist3. The DMA reference: /view/32471.htm? Fr = ala0_1In the case of DMA transfers, the DMA controller is directly in charge of the bus, so there is a bus control transfer problem. Before DMA transfers, the CPU takes control of the bus to the DMA controller, and after the DMA transfer, the DMA controller should immediately return the bus control back to the CPU.A full DMA transfer process must go through the following four steps.1. The DMA requests the CPU to initialize the DMA controller and issue the operation command to the I/O interface, and the I/O interface requests the DMA request.2. The DMA response DMA controller discriminated the optimal level and shielding for DMA requests, and the bus request wasmade to the bus decision logic. The bus control can be released when the CPU executes the current bus cycle. At this point, the bus decision logic output bus should answer, indicating that the DMA has responded, and the I/O interface is notified by the DMA controller to start the DMA transfer.3. After the DMA controller receives the bus control, the CPU immediately hangs up or executes only the internal operation, and the DMA controller outputs the read and write command, and directly controls the DMA transfer with the I/O interface.4. The DMA controller will release the bus control and issue an end signal to the I/O interface after completion of the specified batch data transfer. When the I/O interface received signal after the end of the stop work I/O devices on one hand, on the other hand to the CPU interrupt request, make the CPU never step in the state of the liberation, and perform a check of the DMA transfer operation is code. Finally, the original program is carried out with the result and state of this operation.DMA transfer way, therefore, no CPU control transmission directly, nor as reserved interrupt handling the scene and the scene of the recovery process, through the hardware for the RAM and I/O devices open a direct send data access, has greatly improve the CPU's efficiency.。

STM32第一章

32位基于ARM微控制器STM32F101xx与STM32F103xx 固件函数库介绍本手册介绍了32 位基于ARM微控制器STM32F101xx与STM32F103xx的固件函数库。

该函数库是一个固件函数包,它由程序、数据结构和宏组成,包括了微控制器所有外设的性能特征。

该函数库还包括每一个外设的驱动描述和应用实例。

通过使用本固件函数库,无需深入掌握细节,用户也可以轻松应用每一个外设。

因此,使用本固态函数库可以大大减少用户的程序编写时间,进而降低开发成本。

每个外设驱动都由一组函数组成,这组函数覆盖了该外设所有功能。

每个器件的开发都由一个通用API (application programming interface 应用编程界面)驱动,API 对该驱动程序的结构,函数和参数名称都进行了标准化。

所有的驱动源代码都符合“Strict ANSI-C”标准(项目于范例文件符合扩充ANSI-C标准)。

我们已经把驱动源代码文档化,他们同时兼容MISRA-C 2004 标准(根据需要,我们可以提供兼容矩阵)。

由于整个固态函数库按照“Strict ANSI-C”标准编写,它不受不同开发环境的影响。

仅对话启动文件取决于开发环境该固态函数库通过校验所有库函数的输入值来实现实时错误检测。

该动态校验提高了软件的鲁棒性。

实时检测适合于用户应用程序的开发和调试。

但这会增加了成本,可以在最终应用程序代码中移去,以优化代码大小和执行速度。

想要了解更多细节,请参阅Section 2.5。

因为该固件库是通用的,并且包括了所有外设的功能,所以应用程序代码的大小和执行速度可能不是最优的。

对大多数应用程序来说,用户可以直接使用之,对于那些在代码大小和执行速度方面有严格要求的应用程序,该固件库驱动程序可以作为如何设置外设的一份参考资料,根据实际需求对其进行调整此份固件库用户手册的整体架构如下:… 定义,文档约定和固态函数库规则。

… 固态函数库概述(包的内容,库的架构),安装指南,库使用实例。

STM32嵌入式常见英文缩写和词汇

STM32常见英文缩写和英文词汇(按字母排序)AAPCS:ARM Architecture Process Call Standard ARM体系结构过程调用标准AFIO:Alternate Function IO 复用IO端口AHB-AP:Advanced High-Performance Bus-Access Port 高级高性能总线-访问端口ALU:Arithmetic Logical Unit 算术逻辑单元APB: Advanced Peripheral Bus 高级外围总线APB1: Low Speed APB 低速外围总线APB2: High Speed APB 高速外围总线ARM:Advanced RISC Machine 高级RISC处理器ASIC: Application Specific Integrated Circuit 专用集成电路BSS:Block Started by Symbol 以符号开始的块(未初始化数据段)CAN:Controller Area Network 控制器局域网CLZ:Count Leading Zero 前导零计数(指令)COM: Cluster Communication Port 串口(串行通讯端口)CPLD: Complex Programmable Logic Device 可编程逻辑器件CPSP:Current Program Status Register 当前程序状态寄存器CSR:Clock Control/Status Register 时钟控制状态寄存器DAP: Debug Access Port 调试访问端口DBG:Debug 调试DMA:Direct Memory Access 存储器直接访问DP:Debug Port 调试端口DWT: Data Watchpoint And Trace 数据观测与跟踪单元ETM:Embedded Trace Macrocell 嵌入式追踪宏单元EXTI: External Interrupts 外部中断FA:Full Ascending 满栈递增FD:Full Desending 满栈递减EA:Empty Ascending 空栈递增ED:Empty Desending 空栈递减FIQ:Fast Interrupt Request 快速中断请求FLITF:The Flash Memory Interface 闪存存储器接口FPB:Flash Patch And Breakpoint 闪存补丁及断点FPGA: Field Programmable Gate Array 现场可编程门阵列FSMC: Flexible Static Memory Controller 可变静态存储控制器GAL: Generic Array Logic 通用阵列逻辑GPIO:General Purpose Input/Output 通用IO端口HSE:High Speed External 高速外部HSI: High Speed Internal 高速内部I2C:Inter-Integrated Circuit 内置集成电路ICE:In-Circuit Emulator 在线仿真器IDE:Integrated Development Environment 集成开发环境IIS:Integrated Interface Of Sound 集成音频接口IRQ:Interrupt Request 中断请求ISR:Interrupt Service Routines 中断服务程序ITM: Instrumentation Trace Macrocell 测量跟踪宏单元IWDG: Independent Watchdog 独立看门狗JTAG:Joint Test Action Group 联合测试行动小组JTAG-DP:JTAG Debug Port JTAG 调试端口LR:Link Register 链接寄存器LSE: Low Speed External 低速外部LSI: Low Speed Internal 低速内部LSU: Load Store Unit 存取单元MIPS: Million Instructions Per Second 每秒能执行的百万级指令的条数MPU: Memory Protection Unit 内存保护单元MSP: Main Stack Pointer 主堆栈指针NMI: Non Maskable Interrupt 不可屏蔽中断NVIC: Nested Vectored Interrupt Controller 嵌套向量中断控制器PAL: Programmable Array Logic 可编程阵列逻辑PC:Program Counter 程序计数器PFU: Pre-Fetch Unit 预取单元PPB:Private Peripheral Bus 专用外设总线PSP:Process Stack Pointer 进程堆栈指针RCC:Reset And Clock Control 复位和时钟控制RISC:Reduced Instruction Set Computer 精简指令集计算机RO: Read Only 只读RTC: Real-Time Clock 实时时钟RTOS:Real Time Operating System 实时操作系统RW: Read Write 读写SDIO: Secure Digital I/O 安全数字输入输出SIMD:Single Instruction Multiple Data单指令多数据流SP:Stack Pointer 堆栈指针SPI:Serial Peripheral Interface 串行外设接口SPSR:Saved Program Status Register 程序状态保存寄存器SW:Software 软件SW-DP: Serial Wire Debug Port 串行线调试端口SWI:Software Interrupt 软中断SWJ-DP: Serial Wire JTAG Debug Port 串行线-JTAG调试端口TAP:Test Access Port 测试访问端口TIM:Timer 定时器TP: Trace Port 跟踪端口TPIU:Trace Port Interface Unit 跟踪端口接口单元USART: Universal Synchr./Asynch. Receiver/Transmitter 通用同步/异步收发器USB: Universal Serial Bus 通用串行总线VFP:Vector Floating Point 矢量浮点运算WWDG:Window Watchdog 窗口看门狗ZI: Zero Initial 零初始化STM32常见英文词汇(按字母排序)Access 访问Arbitration 仲裁Assembler 汇编器Banked 分组Big Endian 大端存储模式Binutils 连接器Bit-Band Alias 位段别名Bit-Band Region 位段区域Bit-Banding 位段(技术)Buffer 缓存Bus Matrix 总线矩阵Bus Splitter 总线分割Ceramic 陶瓷Comments 注释Context Switch 任务切换Decode 译码Directive 伪操作Disassembly 反汇编Execute 执行Fetch 取指Handler 处理者Heap 堆Instructions 指令Late-Arriving 迟到Latency 延时Literal Pool 数据缓冲池Little Endian 小端存储模式Load 加载Loader 装载器Optimization 优化Perform 执行Pre-Emption 抢占Prefetch 预读/预取指Prescaler 预分频器Process 进程/过程Pseudo-Instruction 伪指令Resonator 共振器Stack 栈Store 存储Tail-Chaining 尾链Task Switch 任务切换Thread 线程。

stm32f429igt6命名规则

stm32f429igt6命名规则STM32F429IGT6是一款高性能、低功耗的32位微控制器,属于STM32F4系列产品。

在STM32F429IGT6的命名规则中,包含了一些特定的标识,以提供关于器件的重要信息。

下面将详细介绍STM32F429IGT6的命名规则,以及每个标识所代表的含义。

1. STM32:代表STMicroelectronics(意法半导体)公司推出的32位微控制器产品系列。

2. F:代表芯片系列。

F系列是STM32系列中的一部分,主要用于高性能应用。

3. 429:代表器件系列。

429是指STM32F4系列中的一个型号,具有较高的计算能力和内存容量。

4. I:代表封装类型。

在STM32F429IGT6的命名中,I代表LQFP 封装,通常用于表面安装的应用。

5. G:代表工作温度范围。

G代表通常工作温度范围为-40°C至+85°C。

6. T:代表器件特性。

T代表器件具有扩展温度范围的工作能力,即通常工作温度范围为-40°C至+105°C。

7. 6:代表存储容量。

6代表该型号具有512KB的闪存容量。

通过以上几个标识的组合,STM32F429IGT6的命名规则就形成了。

这种命名规则的设计主要是为了提供与器件相关的重要信息,使用户能够更好地了解器件的特性和能力。

除了上述的命名规则外,STM32F429IGT6还有一些其他的标识和功能,如下所示:1.高性能:STM32F429IGT6采用Cortex-M4内核,具有较高的计算能力和工作频率,使其能够处理复杂的应用程序。

2.多种外设:STM32F429IGT6集成了丰富的外设,如多个串行通信接口、USB接口、PWM控制器、定时器和ADC等,使其能够满足多种应用需求。

3.低功耗:STM32F429IGT6采用静态功耗优化设计,具有较低的工作电流和待机电流,从而节省能源。

4. 512KB闪存:STM32F429IGT6具备512KB的闪存容量,用于存储应用程序和数据,使其能够处理较大规模的应用。

单片机英文缩写全称及中文名称整理(一)2024

单片机英文缩写全称及中文名称整理(一)引言概述:本文整理了单片机英文缩写全称及中文名称,旨在帮助读者更好地理解和应用单片机技术。

单片机是一种集成电路,具有微处理器核心、存储器和输入输出接口等功能模块,被广泛应用于各种电子设备和控制系统中。

下面将从五个大点出发,详细介绍单片机英文缩写的全称和中文名称。

正文内容:1. MCU(Microcontroller)- 嵌入式微控制器- CPU (Central Processing Unit) - 中央处理器- ROM (Read-Only Memory) - 只读存储器- RAM (Random Access Memory) - 随机存储器- I/O (Input/Output) - 输入输出- ADC (Analog-to-Digital Converter) - 模数转换器- UART (Universal Asynchronous Receiver-Transmitter) - 通用异步收发器- I2C (Inter-Integrated Circuit) - 集成电路之间的串行通信接口- SPI (Serial Peripheral Interface) - 串行外围设备接口- PWM (Pulse Width Modulation) - 脉宽调制2. EEPROM (Electrically Erasable Programmable Read-Only Memory) - 可擦写可编程只读存储器- GPIO (General Purpose Input/Output) - 通用输入输出- CAN (Controller Area Network) - 控制器局域网络- USB (Universal Serial Bus) - 通用串行总线- RTC (Real-Time Clock) - 实时时钟- DMA (Direct Memory Access) - 直接内存访问- ISP (In-System Programming) - 系统内编程- WDT (Watchdog Timer) - 看门狗定时器- POR (Power-On Reset) - 上电复位- LVD (Low Voltage Detection) - 低电压检测3. A/D (Analog-to-Digital) - 模数转换- D/A (Digital-to-Analog) - 数模转换- IDE (Integrated Development Environment) - 集成开发环境- MCU Core (Microcontroller Core) - 单片机核心- RISC (Reduced Instruction Set Computer) - 精简指令集电脑- CISC (Complex Instruction Set Computer) - 复杂指令集电脑- BCD (Binary-Coded Decimal) - 二进制编码十进制- OS (Operating System) - 操作系统- ISP (In-System Programming) - 系统内编程- FPGA (Field-Programmable Gate Array) - 现场可编程门阵列4. GPIO (General Purpose Input/Output) - 通用输入输出- ADC (Analog-to-Digital Converter) - 模数转换器- PWM (Pulse Width Modulation) - 脉宽调制- SPI (Serial Peripheral Interface) - 串行外围设备接口- I2C (Inter-Integrated Circuit) - 集成电路之间的串行通信接口- UART (Universal Asynchronous Receiver-Transmitter) - 通用异步收发器- RTC (Real-Time Clock) - 实时时钟- WDT (Watchdog Timer) - 看门狗定时器- INT (Interrupt) - 中断- PIN (Pin Number) - 引脚编号5. IDE (Integrated Development Environment) - 集成开发环境- SDK (Software Development Kit) - 软件开发工具包- CMSIS (Cortex Microcontroller Software Interface Standard) - 嵌入式MCU软件接口标准- HAL (Hardware Abstraction Layer) - 硬件抽象层- SPL (Standard Peripheral Library) - 标准外设库- RTOS (Real-Time Operating System) - 实时操作系统- API (Application Programming Interface) - 应用程序编程接口- GCC (GNU Compiler Collection) - GNU编译器集合- ICSP (In-Circuit Serial Programming) - 系统内串行编程- IAP (In-Application Programming) - 系统内应用编程- ISR (Interrupt Service Routine) - 中断服务子程序总结:以上是关于单片机英文缩写全称及中文名称的整理,本文列举了部分常见的缩写及名称,可以帮助读者更好地理解和运用单片机技术。

stm32全称是什么

stm32全称是什么stm32全称是意法半导体32位系列微控制器芯片。

ST即意法半导体(STMicroelectronics)。

意法半导体(STMicroelectronics)集团于1987年6月成立,是由意大利的SGS 微电子公司和法国Thomson 半导体公司合并而成。

1998年5月,SGS-THOMSON Microelectronics 将公司名称改为意法半导体有限公司,意法半导体是世界最大的半导体公司之一。

从成立之初至今,ST 的增长速度超过了半导体工业的整体增长速度。

自1999年起,ST 始终是世界十大半导体公司之一。

据最新的工业统计数据,意法半导体(STMicroelectronics)是全球第五大半导体厂商,在很多市场居世界领先水平。

例如,意法半导体是世界第一大专用模拟芯片和电源转换芯片制造商,世界第一大工业半导体和机顶盒芯片供应商,而且在分立器件、手机相机模块和车用集成电路领域居世界前列。

意法半导体(STMicroelectronics)整个集团共有员工近50000 名,拥有16 个先进的研发机构、39 个设计和应用中心、15 主要制造厂,并在36 个国家设有78 个销售办事处。

公司总部设在瑞士日内瓦,同时也是欧洲区以及新兴市场的总部;公司的美国总部设在德克萨斯州达拉斯市的卡罗顿;亚太区总部设在新加坡;日本的业务则以东京为总部;中国区总部设在上海,负责香港、大陆和台湾三个地区的业务。

意法半导体(ST)公司成立于1987年,是意大利SGS半导体公司和法国汤姆逊半导体合并后的新企业,从成立之初至今,ST的增长速度超过了半导体工业的整体增长速度。

自1999年起,ST始终是世界十大半导体公司之一。

整个集团共有员工近50,000名,拥有16个先进的研发机构、39个设计和应用中心、15主要制造厂,并在36个国家设有78个销售办事处。

公司总部设在瑞士日内瓦,同时也是欧洲区以及新兴市场的总部;公司的美国总部设在德克萨斯州达拉斯市的卡罗顿;亚太区总部设在新加坡;日本的业务则以东京为总部;大中国区总部设在上海,负责香港、大陆和台湾三个地区的业务。

STM32学习笔记(5):通用定时器PWM输出

STM32学习笔记(5):通用定时器PWM输出1.TIMER输出PWM基本概念脉冲宽度调制(PWM),是英文“Pulse Width Modulation”的缩写,简称脉宽调制,是利用微处理器的数字输出来对模拟电路进行控制的一种非常有效的技术。

简单一点,就是对脉冲宽度的控制。

一般用来控制步进电机的速度等等。

STM32的定时器除了TIM6和TIM7之外,其他的定时器都可以用来产生PWM 输出,其中高级定时器TIM1和TIM8可以同时产生7路的PWM输出,而通用定时器也能同时产生4路的PWM输出。

1.1PWM输出模式STM32的PWM输出有两种模式,模式1和模式2,由TIMx_CCMRx寄存器中的OCxM位确定的(“110”为模式1,“111”为模式2)。

模式1和模式2的区别如下:110:PWM模式1-在向上计数时,一旦TIMx_CNT<TIMx_CCR1时通道1为有效电平,否则为无效电平;在向下计数时,一旦TIMx_CNT>TIMx_CCR1时通道1为无效电平(OC1REF=0),否则为有效电平(OC1REF=1)。

111:PWM模式2-在向上计数时,一旦TIMx_CNT<TIMx_CCR1时通道1为无效电平,否则为有效电平;在向下计数时,一旦TIMx_CNT>TIMx_CCR1时通道1为有效电平,否则为无效电平。

由此看来,模式1和模式2正好互补,互为相反,所以在运用起来差别也并不太大。

而从计数模式上来看,PWM也和TIMx在作定时器时一样,也有向上计数模式、向下计数模式和中心对齐模式,关于3种模式的具体资料,可以查看《STM32参考手册》的“14.3.9 PWM模式”一节,在此就不详细赘述了。

1.2PWM输出管脚PWM的输出管脚是确定好的,具体的引脚功能可以查看《STM32参考手册》的“8.3.7定时器复用功能重映射”一节。

在此需要强调的是,不同的TIMx有分配不同的引脚,但是考虑到管脚复用功能,STM32提出了一个重映像的概念,就是说通过设置某一些相关的寄存器,来使得在其他非原始指定的管脚上也能输出PWM。

STM32学习重点spi剖析

一、SPI简介SPI 是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。

是Motorola首先在其MC68HCXX系列处理器上定义的。

SPI接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议,STM32也有SPI接口。

SPI接口一般使用4条线:MISO 主设备数据输入,从设备数据输出。

MOSI 主设备数据输出,从设备数据输入。

SCLK时钟信号,由主设备产生。

CS从设备片选信号,由主设备控制。

SPI主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。

SPI总线四种工作方式SPI 模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。

时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。

SPI主模块和与之通信的外设备时钟相位和极性应该一致。

不同时钟相位下的总线数据传输时序见下图:二、STM32的SPI介绍STM32的SPI功能很强大,SPI时钟最多可以到18Mhz,支持DMA,可以配置为SPI协议或者I2S协议。

本节,我们将利用STM32的SPI来读取外部SPI FLASH芯片(W25X16),这节,我们使用STM32的SPI1的主模式,STM32的主模式配置步骤如下:1)配置相关引脚的复用功能,使能SPI1时钟。

详解STM32命名规则

STM32型号的说明:以STM32F103RBT6这个型号的芯片为例,该型号的组成为7个部分,其命名规则如下:103性能特点内核:ARM32位Cortex-M3 CPU,最高工作频率72MHz,1.25DMIPS/MHz。

单周期乘法和硬件除法。

存储器:片上集成32-512KB的Flash存储器。

6-64KB的SRAM存储器。

时钟、复位和电源管理:2.0-3.6V的电源供电和I/O接口的驱动电压。

POR、PDR和可编程的电压探测器(PVD)。

4-16MHz的晶振。

内嵌出厂前调校的8MHz RC振荡电路。

内部40 kHz 的RC振荡电路。

用于CPU时钟的PLL。

带校准用于RTC的32kHz的晶振。

低功耗:3种低功耗模式:休眠,停止,待机模式。

为RTC和备份寄存器供电的VBAT。

调试模式:串行调试(SWD)和JTAG接口。

DMA:12通道DMA控制器。

支持的外设:定时器,ADC,DAC,SPI,IIC和UART。

2个12位的us级的A/D转换器(16通道):A/D测量范围:0-3.6 V。

双采样和保持能力。

片上集成一个温度传感器。

2通道12位D/A转换器:STM32F103xC,STM32F103xD,STM32F103xE独有。

最多高达112个的快速I/O端口:根据型号的不同,有26,37,51,80,和112的I/O端口,所有的端口都可以映射到16个外部中断向量。

除了模拟输入,所有的都可以接受5V以内的输入。

最多多达11个定时器:4个16位定时器,每个定时器有4个IC/OC/PWM或者脉冲计数器。

2个16位的6通道高级控制定时器:最多6个通道可用于PWM输出。

2个看门狗定时器(独立看门狗和窗口看门狗)。

Systick定时器:24位倒计数器。

2个16位基本定时器用于驱动DAC。

最多多达13个通信接口:2个IIC接口(SMBus/PMBus)。

5个USART接口(ISO7816接口,LIN,IrDA兼容,调试控制)。

STM32常用英文缩写

STM32常⽤英⽂缩写ARM:Advanced RISC MachineAAPCS:ARM Architecture Process call standardARM 体系结构过程调⽤标准RISC: Reduced Instruction Set Computer 精简指令集计算机RTOS:Real Time Operating System 实时操作系统DMA:Direct Memory Access 存储器直接访问EXTI: External Interrupts 外部中断FSMC: Flexible static memory controller 可变静态存储控制器FPB:flash patch and breakpoint FLASH 转换及断电单元HSE:Hign speed externalHSI: High speed internalLSE: Low Speed externalLSI: Low Speed InternalLSU: load store unit 存取单元PFU: prefetch unit 预取单元ISR:Interrupt Service Routines 中断服务程序NMI: Nonmaskable Interrupt 不可屏蔽中断NVIC: Nested Vectored Interrupt Controller 嵌套向量中断控制器MPU: Memory Protection Unit 内存保护单元MIPS:million instructions per second 每秒能执⾏的百万条指令的条数RCC:Reset and clock control 复位和时钟控制RTC: Real-Time Clock 实时时钟IWDG: independent watchdog 独⽴看门狗WWDG:Window watchdog 窗⼝看门狗TIM:timer 定时器GAL:generic array logic 通⽤阵列逻辑PAL:programmable array logic 可编程阵列逻辑ASIC:Application Specific Integrated Circuit 专⽤集成电路FPGA:Field-Programmable Gate Array 现场可编程门阵列CPLD:Complex Programmable Logic Device 可编程逻辑器件端⼝AFIO:alternate function IO 复⽤ IO 端⼝GPIO:general purpose input/output 通⽤ IO 端⼝IOP(A-G):IO port A - IO port G (例如:IOPA:IO port A)CAN:Controller area network 控制器局域⽹FLITF:The Flash memory interface 闪存存储器接⼝I2C: Inter-integrated circuit 微集成电路IIS: integrate interface of sound 集成⾳频接⼝JTAG:joint test action group 联合测试⾏动⼩组SPI:Serial Peripheral Interface 串⾏外围设备接⼝ SDIO: SD I/OUART: Universal Synchr./Asynch. Receiver Transmitter 通⽤异步接收/发送装置USB: Universal Serial Bus 通⽤串⾏总线寄存器相关CPSP: Current Program Status Register 当前程序状态寄存器SPSP: saved program status register 程序状态备份寄存器CSR:clock control/status register 时钟控制状态寄存器LR: link register 链接寄存器SP: stack pointer 堆栈指针MSP: main stack pointer 主堆栈指针PSP:process stack pointer在STM32的固件库中定义了三个结构体与这三个寄存器组相对应,这三个结构体与ARM⼿册中寄存器的对应关系如下:⼀、NVIC寄存器组STM32的固件库中有如下定义:typedef struct{vu32 ISER[2];u32 RESERVED0[30];vu32 ICER[2];u32 RSERVED1[30];vu32 ISPR[2];u32 RESERVED2[30];vu32 ICPR[2];u32 RESERVED3[30];vu32 IABR[2];u32 RESERVED4[62];vu32 IPR[11];} NVIC_TypeDef;它们对应ARM⼿册中的名称为ISER = Interrupt Set-Enable RegistersICER = Interrupt Clear-Enable RegistersISPR = Interrupt Set-Pending RegisterICPR = Interrupt Clear-Pending RegisterIABR = Active Bit RegisterIPR = Interrupt Priority Registers每个寄存器有240位,以Interrupt Set-Enable Registers说明,ISER[0]对应中断源0~31,ISER[1]对应中断源32~63,STM32只有60个中断源,所以没有ISER[2:7]。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

UART: Universal Synchr./Asynch. Receiver Transmitter 通用异步接收/发送装置

USB: Universal Serial Bus 通用串行总线

ITM: instrumentation trace macrocell 测量跟踪单元

ETM: embedded trace macrocell 嵌入式追踪宏单元

TPIU:trace port interface unit 跟踪端口接口单元

TAP: test access port 测试访问端口

FPB:flash patch and breakpoint FLASH 转换及断电单元

HSE:Hign speed external

HSI: High speed internal

LSE: Low Speed external

LSI: Low Speed Internal

RTOS:Real Time Operating System 实时操作系统

DMA:Direct Memory Access 存储器直接访问

EXTI: External Interrupts 外部中断

FSMC: Flexible static memory controller 可变静态存储控制器

英文缩写

ARM:Advanced RISC Machine

AAPCS:ARM Architecture Process call standard

ARM 体系结构过程调用标准

RISC: Reduced Instruction Set Computer 精简指令集计算机

嵌入式常见英文缩写和英文词汇(搜集中)

原文地址: 作者: 原文地址:嵌入式常见英文缩写和英文词汇(搜集中)作者:残翅天使 作者

本文是在原创上作补充,转载请注明出处

本文链接:/s/blog_574d08530100hzo2 (残翅天使归纳得很好,感谢他的分享)

串行调试接口

JTAG-DP:JTAG debug port

JTAG 调试接口

系统类

IRQ: interrupt request 中断请求

FIQ: fast interrupt request 快速中断请求

SW:software 软件

参考文章

1.BSS 的参考:/view/453125.htm?fr=ala0_1

BSS 是 Unix 链接器产生的未初始化数据段。 其他的段分别是包含程序代码的“text”段和包含 已初始化数据的“data”段。BSS 段的变量只有名称和大小却没有值。此名后来被许多文件格 式使用,包括 PE。“以符号开始的块”指的是编译器处理未初始化数据的地方。BSS 节不包 含任何数据,只是简单的维护开始和结束的地址,以便内存区能在运行时被有效地清零。 BSS 节在应用程序的二进制映象文件中并不存在。

DAP: debug access prot 调试访问端口

TP: trace port 跟踪端口

DP:debug port 调试端口

SWJ-DP: serial wire JTAG debug port 串行-JTAG 调试接口

SW-DP: serial wire debug port

调试相关

ICE:in circuit emulator 在线仿真

ICE Breaker 嵌入式在线仿真单元

DBG:debug 调试

IDE:integrated development environment 集成开发环境

DWT: data watchpoint and trace 数据观测与跟踪单元

IWDG: independent watchdog 独立看门狗

WWDG:Window watchdog 窗口看门狗

TIM:timer 定时器

GAL:generic array logic 通用阵列逻辑

PAL:programmable array logic 可编程阵列逻辑

寄存器相关

CPSP: Current Program Status Register 当前程序状态寄存器

SPSP: saved program status register 程序状态备份寄存器

CSR:clock control/status register 时钟控制状态寄存器

总线

Bus Matrix 总线矩阵

Bus Splitter 总线分割

AHB-AP:advanced High-preformance Bus-access port

APB:advanced peripheral busAPB1: low speed APB

LSU: load store unit 存取单元

PFU: prefetch unit 预取单元

ISR:Interrupt Service Routines 中断服务程序

NMI: Nonmaskable Interrupt 不可屏蔽中断

NVIC: Nested Vectored Interrupt Controller 嵌套向量中断控制器

FLITF:The Flash memory interface 闪存存储器接口

I2C: Inter-integrated circuit 微集成电路

IIS: integrate interface of sound 集成音频接口

JTAG:joint test action group 联合测试行动小组

端口

AFIO:alternate function IO 复用 IO 端口

GPIO:general purpose input/output 通用 IO 端口

IOP(A-G):IO port A - IO port G (例如:IOPA:IO port A)

CAN:Controller area network 控制器局域网

thread 线程

prescaler 预分频器

prefetch 预读/预取指

perform 执行

pre-emption 抢占

tail-chaining 尾链

late-arriving 迟到

resonator 共振器

指令相关

SWI: software interrupt 软中断

RO:read only 只读(部分)

RW:read write 读写(部分)

ZI:zero initial 零初始化(部分)

BSS:Block Started by l 以符号开始的块(未初始化数据段)

VFP: vector floating point 矢量浮点运算

词汇/词组

Big Endian

大端存储模式

Little Endian 小端存储模式

context switch 任务切换(上下文切换)(CPU 寄存器内容的切换)

task switch 任务切换

比如,在 C 语言之类的程序编译完成之后,已初始化的全局变量保存在.data 段中,未 初始化的全局变量保存在.bss 段中。

literal pool 数据缓冲池

词汇类/单词

arbitration 仲裁

access 访问

assembler 汇编器

disassembly 反汇编

binutils 连接器

bit-banding 位段(技术)

bit-band alias 位段别名

stack 栈

latency 延时

load (LDR) 加载(存储器内容加载到寄存器 Rn)

store (STR) 存储(寄存器 Rn 内容存储到存储器)

Loader 装载器

optimization 优化

process 进程/过程

在采用段式内存管理的架构中 (比如 intel 的 80x86 系统)bss 段 , (Block Started by Symbol segment)通常是指用来存放程序中未初始化的全局变量的一块内存区域,一般在初始化时 bss 段部分将会清零。bss 段属于静态内存分配,即程序一开始就将其清零了。

instructions 指令

pseudo-instruction 伪指令

directive 伪操作

comments 注释

FA full ascending 满栈递增(方式)

EA empty ascending 空栈递增(方式)

FD full desending 满栈递减(方式)

ED empty desending 空栈递减(方式)

翻译

1.number of wait states for a read operation programmed on-the-fly

动态设置(programmed on-the-fly)的读操作的等待状态数目

LR: link register 链接寄存器

SP: stack pointer 堆栈指针

MSP: main stack pointer 主堆栈指针

PSP:process stack pointer 进程堆栈指针

PC: program counter 程序计数器

bit-band region 位段区域

banked 分组

buffer 缓存/

ceramic 陶瓷

fetch 取指

decode 译码

execute 执行