基于verilog的边沿检测电路

X450Verilog参考例程-逻辑分析仪DIY

笔记19 DIY逻辑分析仪一、背景知识逻辑分析仪是一种类似于示波器的波形测试设备,它可以监测硬件电路工作时的逻辑电平(高或低),存储后用图形的方式直观地表达出来,主要是方便用户在数字电路的调试中观察输出的逻辑电平值。

逻辑分析仪是电路开发中不可缺少的设备,通过它,可以迅速地定位错误,解决问题,达到事半功倍的效果。

如图6.1所示,一个逻辑分析的基本功能架构主要包括数据采样、触发控制、数据存储和现实控制四大部分。

图6.1 逻辑分析仪功能框图逻辑分析仪是利用时钟从测试设备上采集和显示数字信号的仪器,主要作用是时序判定。

由于逻辑分析仪不像示波器那样有许多电压等级,通常只显示两个电压(逻辑0和1)。

因此,设定了参考电压后,逻辑分析仪将被测信号通过比较器进行判定,高于参考电压者逻辑为1,低于参考电压者为逻辑0,在逻辑1与逻辑0之间形成数字波形。

整体而言,逻辑分析仪测量被测信号时,并不会显示出电压值,只是简单的显示逻辑1或者逻辑0的差别。

如果要测量电压就一定需要使用示波器。

除了电压值的显示不同外,逻辑分析仪与示波器的另一个差别在于通道数量。

一般的示波器只有2个通道或4个通道,而逻辑分析仪可以拥有从16个通道、32个通道、64个通道和上百个通道数不等,因此逻辑分析仪具备同时进行多通道测试的优势,更适合于对总线式信号的调试。

根据硬件设备设计上的差异,目前市面上逻辑分析仪大致上可分为独立式(或单机型)逻辑分析仪和需结合电脑的卡式虚拟逻辑分析仪。

独立式逻辑分析仪是将所有的测试软件、运算管理元件以及整合在一台仪器之中;卡式虚拟逻辑分析仪则需要搭配电脑一起使用,显示屏也与主机分开。

就整体规格而言,独立式逻辑分析仪已发展到相当高标准的产品,例如采样率可达8GHz、通道数可扩充到300个通道以上,存储深度相对也高,独立式逻辑分析仪价格昂贵,一般用户很少用得起。

基于计算机接口的卡式虚拟逻辑分析仪,以较小的成本提供了相应的性能,但是卡式虚拟逻辑分析仪也有很大缺点,它需要配备电脑才能使用,尤其数字测试中,工程师往往会陷入一堆PCB板中,采用旋转按钮的仪器要比在屏幕上移动鼠标更加方便。

集成电路边界扫描测试中的电路网表结构分析

集成电路边界扫描测试中的电路网表结构分析集成电路边界扫描测试(Boundary Scan Testing,BST)是一种广泛应用于VLSI设计和制造中的测试技术。

BST是一种将测试功能集成到复杂的芯片设计中的方法,它可以诊断集成电路中的任何一个缺陷,从而提高产品的质量和性能。

BST采用的核心技术是边界扫描技术(Boundary Scan),用于测试芯片的连接性、可编程逻辑器件(Programmable Logic Devices,PLD)和电路的故障诊断。

在BST中,电路网表结构分析是非常关键的一个步骤。

电路网表结构指的是VLSI集成电路中各个模块相互连接的电路线路结构,也就是电路的物理连接方式。

电路网表结构分析的主要目的是找出部分设计错误和模块之间的错误连接,以确保VLSI集成电路在边界扫描测试过程中能够被正确地测试。

电路网表结构分析需要一些专门的工具和软件来实现。

首先,我们需要对VLSI集成电路进行仿真和验证,确定其运行正确。

然后,需要将电路分解成多个模块和其相应的边界扫描单元(Boundary Scan Cells)。

Boundary Scan Cells是一种可设置逻辑器件,可以被串联到某个端口上,常常与电路网表结构密切相关。

在电路网表结构分析的过程中,我们需要同时验证电路网表结构和单元测试。

我们可以通过检查边界扫描链上的信号线路和寄存器电路是否正确来检测电路网表结构错误。

如果有任何电路连接错误,那么边界扫描测试将无法在这些错误地连接的边界扫描单元上进行正确测试,从而导致电路测试失败。

电路网表结构分析在VLSI设计过程中非常重要,它可以帮助我们找出设计中的错误和潜在的问题,最终确保集成电路在真正的测试前可以顺利进行边界扫描测试,从而提高产品的质量和性能。

在今后的VLSI设计工作中,电路网表结构分析将继续发挥重要作用,帮助人们设计出更加合理、优秀的电路设计。

verilog计数器设计原理

Verilog计数器设计原理1. 介绍计数器是一种常见的数字电路,用于计算和记录事件的数量。

在数字系统中,计数器通常用于生成时钟信号、控制状态机、实现频率分频等应用。

Verilog是一种硬件描述语言,可以用于设计和仿真数字电路。

本文将详细介绍与Verilog计数器设计相关的基本原理。

2. 计数器的基本概念计数器是一种能够在输入脉冲信号的作用下进行累加或递减操作的数字电路。

它通常由触发器和逻辑门组成,触发器用于存储和传递数据,逻辑门用于控制触发器的工作状态。

2.1 同步计数器同步计数器是通过时钟信号来同步各个触发器的状态转换,以实现数据的累加或递减操作。

它包含一个时钟输入端(CLK)和一个复位输入端(RST)。

2.1.1 同步正向计数器同步正向计数器是最简单的同步计数器之一,它能够在每个上升沿时钟信号到达时进行累加操作。

2.1.1.1 原理同步正向计数器由多个触发器和逻辑门组成,其中每个触发器都有一个时钟输入端和一个复位输入端。

当时钟信号的上升沿到达时,触发器的状态将根据输入信号进行更新。

具体的原理如下:1.初始化:将计数器的初始值设置为0。

2.时钟边沿检测:当时钟信号的上升沿到达时,进入下一步操作。

3.累加操作:根据触发器的当前状态进行累加操作。

如果触发器为0,则变为1;如果触发器为1,则变为0。

4.检测溢出:如果最高位触发器由1变为0,则表示计数溢出,需要将其他低位触发器进行进位操作。

2.1.1.2 Verilog代码示例以下是一个4位同步正向计数器的Verilog代码示例:module synchronous_counter(input wire clk,input wire rst,output wire [3:0] count);reg [3:0] count;always @(posedge clk or posedge rst)beginif (rst)count <= 4'b0000;elsecount <= count + 1;endendmodule2.1.2 同步递减计数器同步递减计数器是同步正向计数器的一种扩展,它能够在每个上升沿时钟信号到达时进行递减操作。

《数字电子技术与接口技术试验教程》课件第5章

第5章 基于HDL的时序逻辑电路实验

图5-2 边沿D触发器的仿真结果

9

第5章 基于HDL的时序逻辑电路实验 (2) 边沿D触发器的VHDL源代码如下:

--Behavioral D Flip-Flop with Clock Enable and Asynchronous Reset

entity Dflipflop is Port (D,clk,rst,ce : in STD_LOGIC; Q : out STD_LOGIC);

architecture Behavioral of DFF is begin

process(clk, rst,D) begin

if (CLK'event and CLK='1') then if rst ='1' then Q <= '0'; else Q<=D; end if;

end if; end process; end Behavioral;

end if; end process; end Behavioral;

13

第5章 基于HDL的时序逻辑电路实验

(3) 带有置位和清零端的边沿D触发器的约束文件规定

如下:

#Basys2约束文件: NET "clk" LOC ="B8"; //时钟

#Basys2约束文件: NET "clk" LOC ="B8"; //时钟

end Dflipflop;

architecture Behavioral of Dflipflop is begin

process(clk, rst,D,ce)

脉冲边沿检测电路原理

优点

具有记忆功能,能够保持输出状态;对输入脉冲的幅度和 宽度要求较低。

应用场景

适用于需要记忆脉冲边沿状态的场合,如电机控制、遥控 开关等。

集成电路型

工作原理 优点 缺点

应用场景

集成电路型脉冲边沿检测电路采用专门的集成电路芯片实现脉 冲边沿检测功能,具有高度的集成化和智能化。

功能强大,性能稳定;易于实现复杂逻辑功能;体积小,重量 轻。

电源和偏置电路

为各级电路提供稳定的工作电压和偏置电流,确保电路 正常工作。

03 常见脉冲边沿检测电路类 型

单稳态触发器型

工作原理

单稳态触发器型脉冲边沿检测电路利用单稳态触发器的特性,在输入 脉冲的上升沿或下降沿触发时产生一定宽度的输出脉冲。

优点

电路结构简单,易于实现;输出脉冲宽度可调,适应性强。

可靠性

衡量电路在长时间工作过程中的稳定性和可靠性,包括温漂、时漂等参数的变化情况,应足够高 以保证长期稳定的性能表现。

06 脉冲边沿检测电路应用实 例分析

在数字系统中的应用

时钟同步

在数字系统中,脉冲边沿检测电路可用于实 现精确的时钟同步,确保各个数字模块在统 一的时钟信号下正常工作。

数据传输

通过检测脉冲信号的边沿变化,可以实现数字信号 的高速、准确传输,提高数据传输的效率和可靠性 。

可靠性。

智能化阶段

近年来,随着人工智能和机器学 习技术的发展,脉冲边沿检测电 路开始向智能化方向发展,通过 算法优化和自适应调整来提高检

测精度和响应速度。

02 脉冲边沿检测电路基本原 理

脉冲信号特性

01

02

03

脉冲幅度表示脉冲信号电压或来自流 的最大值,决定了信号的 强度。

基于FPGA的抖动及消抖的方法

基于FPGA的抖动及消抖的方法抖动的产生通常的按键所用开关为机械弹性开关,当机械触点断开、闭合时,由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。

因而在闭合及断开的瞬间均伴随有一连串的抖动,为了不产生这种现象而作的措施就是按键消抖。

抖动时间抖动时间的长短由按键的机械特性决定,一般为5ms~10ms。

这是一个很重要的时间参数,在很多场合都要用到按键稳定闭合时间的长短则是由操作人员的按键动作决定的,一般为零点几秒至数秒。

键抖动会引起一次按键被误读多次。

为确保FPGA对键的一次闭合仅作一次处理,必须去除键抖动。

在键闭合稳定时读取键的状态,并且必须判别到键释放稳定后再作处理。

FPGA内实现消抖的方法在FPGA内实现按键消抖的方法多种多样,但是最简单的是采用移位寄存器的方法进行消抖。

因为移位寄存器的方法不需要对时钟进行分频,也不需要进行延时等复杂操作,即可实现对按键边沿的检测。

假设未按下时键值=1.1、在无键按下时,移位寄存器samp[7:0]始终采集到高电平,即samp[7:0]=8b1111_1111;2、当键按下时,samp[7:0]将采集到低电平,数据的变化方式为samp[7:0]=8b1111_1110--8b1111_1100--8b1111_1000-- ........8b0000_0000;samp[7:0]=8b1111_ 1110即为按键下降沿。

3、当松开按键时,samp[7:0]将重新采集到高电平,数据变化方式为samp[7:0]=8b0000_0001--8b0000_0011-- ........--8b1111_1111;当samp[7:0]=8b0111_1111时,即为按键上升沿。

参考Verilog代码//模块名:EdgeDetect,边沿检测//button:按键,无键按下时为高电平//clk:10M时钟//rst:复位按钮,低电平有效//rise:检测到上升沿,高电平有效,宽度为1个clk//fall:检测到下降沿,高电平有效,宽度为1个clkmodule EdgeDetect(input clk,input rst,input button,output reg rise,output reg fall);。

verilog基本电路设计(包括:时钟域同步、无缝切换、异步fifo、去抖滤波))

Verilog基本电路设计(包括:时钟域同步、无缝切换、异步FIFO、去抖滤波))Verilog基本电路设计共包括四部分:单bit跨时钟域同步时钟无缝切换异步FIFO去抖滤波Verilog基本电路设计之一: 单bit跨时钟域同步(帖子链接:/thread-605419-1-1.html)看到坛子里不少朋友,对于基本数字电路存在这样那样的疑惑,本人决定开贴,介绍数字电路最常见的模块单元,希望给初学者带来帮助,也欢迎大佬们前来拍砖。

如果想要做数字设计,下面这些电路是一定会碰到的,也是所有大型IP,SOC设计必不可少的基础,主要包括异步信号的同步处理,同步FIFO,异步FIFO,时钟无缝切换,信号滤波debounce等等,后面会根据大家反馈情况再介绍新电路。

首先介绍异步信号的跨时钟域同步问题。

一般分为单bit的控制信号同步,以及多bit的数据信号同步。

多bit的信号同步会使用异步FIFO完成,而单bit的信号同步,又是时钟无缝切换电路以及异步FIFO电路的设计基础,这里先介绍单bit信号同步处理。

clka域下的信号signal_a,向异步的clkb域传递时,会产生亚稳态问题。

所有的亚稳态,归根结底就是setup/hold时间不满足导致。

在同一个时钟域下的信号,综合以及布线工具可以在data路径或者clock路径上插入buffer使得每一个DFF的setup/hold时间都满足;但是当signal_a在clkb域下使用时,由于clka与clkb异步,它们的相位关系不确定,那么在clkb的时钟沿到来时,无法确定signal_a此时是否处于稳定无变化状态,也即setup/hold时间无法确定,从而产生亚稳态。

这种异步信号在前后端流程里面是无法做时序分析的,也就是静态时序分析里常说的false_path。

消除亚稳态,就是采用多级DFF来采样来自另一个时钟域的信号,级数越多,同步过来的信号越稳定。

对于频率很高的设计,建议至少用三级DFF,而两级DFF同步则是所有异步信号处理的最基本要求。

verilog判断上升沿的方法

verilog判断上升沿的方法在 Verilog 中判断上升沿的方法有多种。

以下是其中两种常用方法的介绍:方法一:使用边沿检测器要判断信号的上升沿,可以使用边沿检测器模块。

边沿检测器将输入信号与其之前的状态进行比较,当输入信号从低电平变为高电平时,输出产生一个上升沿脉冲。

以下是一个示例代码片段:```module EdgeDetector (input wire clk,input wire sig,output wire posedge);reg sig_prev = 0;always @(posedge clk) beginsig_prev <= sig;posedge <= (sig && !sig_prev);endendmodule```在上述示例中,输入信号 `sig` 和时钟信号 `clk` 都采用 `wire` 类型声明。

`sig_prev` 为上一个时刻的信号值,使用 `reg` 类型存储,并在时钟上升沿触发时进行更新。

`posedge` 为输出信号,当边沿检测到输入信号 `sig` 由低电平变为高电平时,输出一个脉冲。

方法二:使用组合逻辑Verilog 中也可以使用组合逻辑来判断上升沿。

以下是一个使用组合逻辑实现的示例代码片段:```module RisingEdgeDetector (input wire clk,input wire sig,output wire posedge);wire sig_prev = ~sig;assign posedge = (sig && sig_prev);endmodule```在上述示例中,`sig_prev` 通过对输入信号 `sig` 取反得到,用于表示上一个时刻的信号状态。

`posedge` 是一个输出信号,使用 `assign` 语句通过逻辑运算判断输入信号 `sig` 是否为高电平,并且上一个时刻的信号 `sig_prev` 为低电平。

边沿检测电路设计verilog

边沿检测电路设计verilogAbstract边沿检测电路(edge detection circuit)是个常⽤的基本电路。

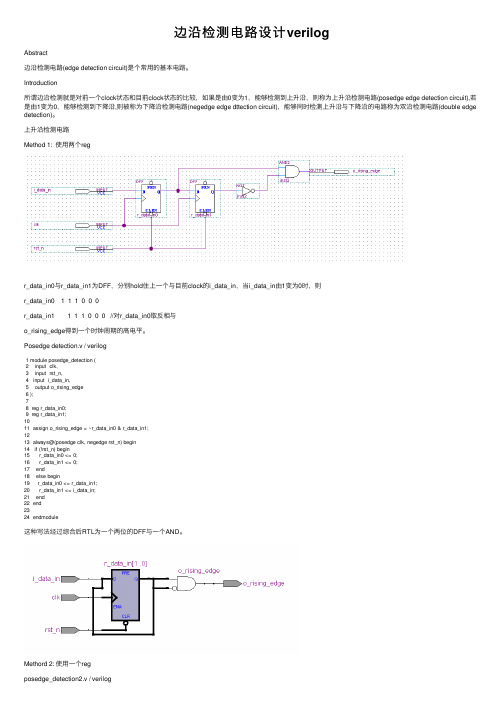

Introduction所谓边沿检测就是对前⼀个clock状态和⽬前clock状态的⽐较,如果是由0变为1,能够检测到上升沿,则称为上升沿检测电路(posedge edge detection circuit),若是由1变为0,能够检测到下降沿,则被称为下降沿检测电路(negedge edge dttection circuit),能够同时检测上升沿与下降沿的电路称为双沿检测电路(double edge detection)。

上升沿检测电路Method 1: 使⽤两个regr_data_in0与r_data_in1为DFF,分别hold住上⼀个与⽬前clock的i_data_in,当i_data_in由1变为0时,则r_data_in0 1 1 1 0 0 0r_data_in1 1 1 1 0 0 0 //对r_data_in0取反相与o_rising_edge得到⼀个时钟周期的⾼电平。

Posedge detection.v / verilog1 module posedge_detection (2 input clk,3 input rst_n,4 input i_data_in,5 output o_rising_edge6 );78 reg r_data_in0;9 reg r_data_in1;1011 assign o_rising_edge = ~r_data_in0 & r_data_in1;1213 always@(posedge clk, negedge rst_n) begin14 if (!rst_n) begin15 r_data_in0 <= 0;16 r_data_in1 <= 0;17 end18 else begin19 r_data_in0 <= r_data_in1;20 r_data_in1 <= i_data_in;21 end22 end2324 endmodule这种写法经过综合后RTL为⼀个两位的DFF与⼀个AND。

下降沿检测电路时序设计verilog hdl描述

下降沿检测电路时序设计verilog hdl描述下降沿检测电路是数字电路中常见的一种,主要用于检测输入信号的下降沿,并输出对应的信号。

本文将分别介绍下降沿检测电路的功能和设计思路,以及其Verilog HDL描述。

一、下降沿检测电路的功能下降沿检测电路主要用于检测输入信号的下降沿,并输出相应的信号。

下降沿指的是信号的电平从高电平突然降落至低电平的过程。

下降沿检测电路可以用于许多应用场合,例如在计时电路中,可以通过检测下降沿实现计数器的计数;在触发电路中,可以通过检测下降沿实现触发器的触发。

二、下降沿检测电路的设计思路下降沿检测电路通常采用触发器和异或门两种基本电路组成。

触发器负责记录输入信号的电平状态,异或门负责检测输入信号的电平变化,进而输出检测结果。

具体来说,下降沿检测电路的设计思路可以分为以下几个步骤:1、确定输入信号的接口。

输入信号的接口应包括输入信号的名称和输入信号的位宽。

一般来说,输入信号的位宽取决于信号的采样精度和采样速率。

2、确定输出信号的接口。

输出信号的接口应包括输出信号的名称和输出信号的位宽。

通常情况下,输出信号只需要一个比特位,表示输入信号是否发生了下降沿。

3、设计触发器。

触发器可采用D触发器或JK触发器实现。

触发器的输入端连接输入信号,输出端连接异或门的一个输入端口。

4、设计异或门。

异或门有两个输入端口,分别连接触发器输出和输入信号。

当输入信号发生电平变化时,异或门输出高电平。

5、组合触发器和异或门。

将触发器和异或门组合在一起,构成下降沿检测电路。

电路的输出连接到输出信号。

三、下降沿检测电路的Verilog HDL描述下降沿检测电路的Verilog HDL描述如下:```module falling_edge_detection(input clk, input signal_in, output signal_out);wire pre_trigger;DFF pre_trigger_d(signal_in, clk, pre_trigger);assign signal_out = pre_trigger ^ signal_in;endmodule```模块名称为falling_edge_detection。

verilog状态跳变检测方法

verilog状态跳变检测方法在Verilog中,你可以使用时钟边缘检测的方法来检测状态跳变。

一种常见的方法是使用触发器(Flip-Flop)或寄存器(Register)来实现。

下面是一个简单的例子,展示如何使用触发器来检测状态跳变:```verilogmodule state_detector (input wire clk, // 输入时钟信号input wire reset, // 输入复位信号input wire current_state, // 输入当前状态output reg next_state // 输出下一个状态);reg previous_state; // 寄存器,用于存储上一个状态always (posedge clk or posedge reset) beginif (reset) beginnext_state <= 0; // 复位时,将下一个状态设置为0previous_state <= 0; // 同时将上一个状态也设置为0end else begin// 检测状态跳变if (current_state != previous_state) beginnext_state <= ~previous_state; // 状态跳变时,取反上一个状态作为下一个状态end else beginnext_state <= previous_state; // 状态未跳变时,保持上一个状态作为下一个状态endprevious_state <= current_state; // 更新上一个状态为当前状态 endendendmodule```在上面的代码中,我们使用了一个触发器(`previous_state`)来存储上一个状态。

在时钟上升沿时,我们比较当前状态和上一个状态,如果它们不相等,则表示发生了状态跳变。

根据需要,你可以根据状态跳变的规则来设置下一个状态的值。

verilog and用法

verilog and用法Verilog是一种硬件描述语言,被广泛用于数字电路设计和验证。

它是一种基于模块化的设计语言,具有在ASIC和FPGA等数字电路实现中的广泛应用。

Verilog分为两种版本:Verilog 1995和Verilog 2001。

其中Verilog 2001包括了SystemVerilog,这是一种可扩展的语言,包含了更多的特性。

Verilog由三个部分组成:模块声明、语句和表达式。

一个Verilog模块声明由关键字module和模块名组成。

模块名在整个设计中必须是唯一的。

模块中定义了一些输入和输出端口,它们在设计中被用来传递信息。

Verilog语句类似于其他编程语言中的语句,包括赋值语句、条件语句和循环语句。

Verilog表达式定义了一些逻辑运算,包括与、或、非和异或等。

Verilog的应用非常广泛,它可以用于设计各种数字电路,包括处理器、存储器、芯片组、FPGA和ASIC等。

Verilog还被用于模拟器和验证器中,用于验证设计的正确性和功能。

在数字电路设计中,Verilog可以帮助工程师快速建立模块和子模块,并进行有效的模块级和系统级仿真。

它还可以生成Verilog网表,这是一种逻辑门等级的电路表示方法,可用于后续的FPGA实现。

Verilog中的and是逻辑与操作符,用于将两个逻辑值进行求和。

当两个逻辑值都为1时,结果为1;否则结果为0。

and操作符可以用于两个逻辑值之间或两个逻辑向量之间,以及其它数据类型之间。

例如:wire a, b, c;assign c = a & b;在这个例子中,a、b和c都是逻辑向量。

and操作符将a和b的值进行与操作,并分配给c。

在使用Verilog进行数字电路设计和验证时,常常需要和一些工具和技术配合使用。

仿真工具可以实现电路的模拟和验证,RTL综合工具可以将Verilog设计语言转换为硬件描述语言,FPGA工具可以将Verilog网表烧录到FPGA设备等。

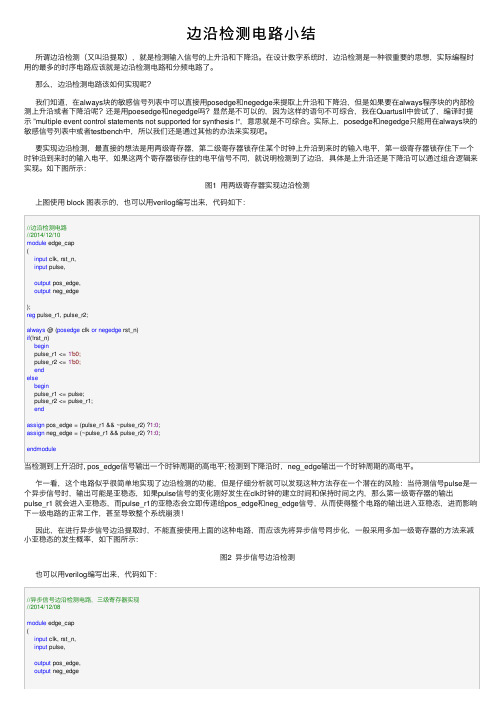

边沿检测电路小结

边沿检测电路⼩结所谓边沿检测(⼜叫沿提取),就是检测输⼊信号的上升沿和下降沿。

在设计数字系统时,边沿检测是⼀种很重要的思想,实际编程时⽤的最多的时序电路应该就是边沿检测电路和分频电路了。

那么,边沿检测电路该如何实现呢?我们知道,在always块的敏感信号列表中可以直接⽤posedge和negedge来提取上升沿和下降沿,但是如果要在always程序块的内部检测上升沿或者下降沿呢?还是⽤poesedge和negedge吗?显然是不可以的,因为这样的语句不可综合,我在QuartusII中尝试了,编译时提⽰ ”multiple event control statements not supported for synthesis !“,意思就是不可综合。

实际上,posedge和negedge只能⽤在always块的敏感信号列表中或者testbench中,所以我们还是通过其他的办法来实现吧。

要实现边沿检测,最直接的想法是⽤两级寄存器,第⼆级寄存器锁存住某个时钟上升沿到来时的输⼊电平,第⼀级寄存器锁存住下⼀个时钟沿到来时的输⼊电平,如果这两个寄存器锁存住的电平信号不同,就说明检测到了边沿,具体是上升沿还是下降沿可以通过组合逻辑来实现。

如下图所⽰:图1 ⽤两级寄存器实现边沿检测上图使⽤ block 图表⽰的,也可以⽤verilog编写出来,代码如下://边沿检测电路//2014/12/10module edge_cap(input clk, rst_n,input pulse,output pos_edge,output neg_edge);reg pulse_r1, pulse_r2;always @ (posedge clk or negedge rst_n)if(!rst_n)beginpulse_r1 <= 1'b0;pulse_r2 <= 1'b0;endelsebeginpulse_r1 <= pulse;pulse_r2 <= pulse_r1;endassign pos_edge = (pulse_r1 && ~pulse_r2) ?1:0;assign neg_edge = (~pulse_r1 && pulse_r2) ?1:0;endmodule当检测到上升沿时, pos_edge信号输出⼀个时钟周期的⾼电平; 检测到下降沿时,neg_edge输出⼀个时钟周期的⾼电平。

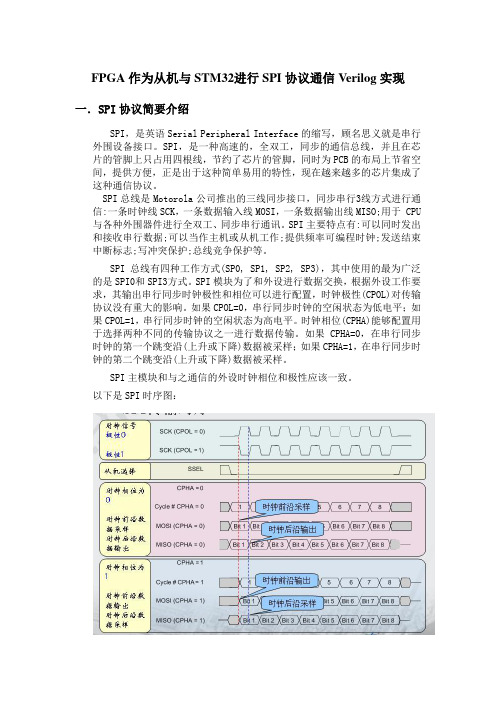

Verilog实现FPGA作为从机与STM32进行SPI协议通信

FPGA作为从机与STM32进行SPI协议通信Verilog实现一.SPI协议简要介绍SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接口。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

SPI总线是Motorola公司推出的三线同步接口,同步串行3线方式进行通信:一条时钟线SCK,一条数据输入线MOSI,一条数据输出线MISO;用于 CPU 与各种外围器件进行全双工、同步串行通讯。

SPI主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。

SPI总线有四种工作方式(SP0, SP1, SP2, SP3),其中使用的最为广泛的是SPI0和SPI3方式。

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。

时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

如果 CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。

SPI主模块和与之通信的外设时钟相位和极性应该一致。

以下是SPI时序图:主要讲解一下广泛使用的两种方式设置:SPI0方式:CPOL=0,CPHA=0;SCK空闲状态为低电平,第一个跳变沿(上升沿)采样数据,无论对Master还是Slaver都是如此。

SPI3方式:CPOL=1,CPHA=1;SCK空闲状态为高电平,第二个跳变沿(上升沿采样数据,无论对Master还是Slaver都是如此。

基于FPGA的SSI通信模块设计

基于FPGA的SSI通信模块设计李文涛;李瑞刚【摘要】为了实现SSI协议的从机与上位机的实时通信,设计基于FPGA工业数据采集用的SSI接口模块.利用LM2596稳压芯片及其外围电路设计电源,利用ADuM1201数字隔离芯片设计隔离电路,并通过MAX491实现差分信号转换;软件设计利用Verilog HDL硬件描述语言完成.该模块具有同步时钟发生器和独立供电电源,可独立工作,成本低且效率高.测试结果验证了方案的可行性和可靠性.%Designing FPGA industrial data collection-based SSI(synchronous serial interface)module was im-plemented,including applying LM2596 voltage regulator and its peripheral circuit to the power supply design and employing ADuM1201 digital isolation chip to design isolation circuit and having MAX491 based to accom-plish differential signal conversion as well as making use of Verilog HDL(hardware description language)to design softwares.The module has synchronous clock generator and independent power supply and it can work alone along with low cost and high efficiency.Test results prove both feasibility and reliability of this scheme.【期刊名称】《化工自动化及仪表》【年(卷),期】2018(045)004【总页数】5页(P324-328)【关键词】SSI通信模块;FPGA;Verilog;HDL语言【作者】李文涛;李瑞刚【作者单位】内蒙古科技大学信息工程学院;内蒙古科技大学信息工程学院【正文语种】中文【中图分类】TH862+.7同步串行接口(SSI)是一种串行通信协议,通常微控制单元(MCU)、数字信号处理器(DSP)以及其他一些工控机不提供SSI接口,S7-300 PLC中提供了接收SSI信号的模块SM338,但实时性不好,并且用PLC作为上位机增加了系统的一次性成本和维护成本,从某种角度来说限制了SSI协议类型传感器的发展[1,2]。

verilog检测上升沿和下降沿的一种方法

verilog检测上升沿和下降沿的⼀种⽅法各位好,有个问题像⼤家请教⼀下,检测上升沿和下降沿的 ,当检测到上升沿时out 输出1,检测到下降沿时out 输出0,⽤的以下的代码,但是⽤逻辑分析仪查看波形如下,out 输出1延迟了两个时钟周期20ns,请问下有没有好的代码⽅法让这个延迟时间短⼀点,测量了别⼈的延迟只有5ns1. reg sig_in0;2. reg sig_in1;3.4. wire rising_edge;5. wire falling_edge;6.7. assign rising_edge = ~sig_in0 & sig_in1;8. assign falling_edge = sig_in0 & ~sig_in1;9.10. always@(posedge clk) begin11. sig_in0 <= sig_in1;12. sig_in1 <= mcu_sig_3 ;13. end14.15. always @(posedge clk) begin16. if( falling_edge_3)17. out <= 0;18. else if(rising_edge_3)19. out <= 1;20. end21.复制代码你的⽐较⽅法不对,这种边沿检测法,⽤的是时序电路,最⼩时间当然是1个时钟周期,你说的5ns,估计是组合逻辑的延时吧,这是不能⽐较的。

⽐如always @(posedge mcu_sig_3 or negedge rst_n)beginif(!rst_n)out <= 0;elseout <= 1;end这个从判断mcu_sig_3上升沿,到out输出,就快,⼏ns⽽已,就是⼀个选择器的输出延时⽽已。

但这种⽅法没有意思,FPGA设计的边沿判断,都是采⽤2级寄存器打拍的⽅法,只要系统设计合理,不在乎那两个时钟周期。

verilog 脉冲信号转电平信号

Verilog脉冲信号转电平信号是数字电路设计中的一个重要问题,本文将就这一主题展开讨论。

本文将首先介绍Verilog语言中脉冲信号和电平信号的概念和特点。

将介绍脉冲信号转换为电平信号的方法和技巧,并给出具体的Verilog代码示例。

将对脉冲信号和电平信号的应用进行简要说明。

1. 脉冲信号和电平信号的概念和特点Verilog语言中,脉冲信号通常用于表示短暂的信号变化,它可以是一个时钟信号的上升沿或下降沿,也可以是一个短暂的触发信号。

脉冲信号的特点是持续时间较短,一般只能维持一个时钟周期。

电平信号则是指信号在一段时间内保持稳定的高电平或低电平。

电平信号的特点是持续时间较长,可以跨越多个时钟周期。

2. 脉冲信号转换为电平信号的方法和技巧在数字电路设计中,经常需要将脉冲信号转换为电平信号,以满足具体的电路需求。

脉冲信号转换为电平信号的方法和技巧有多种,下面将介绍其中的几种常用方法。

2.1 时钟边沿检测时钟边沿检测是一种常用的脉冲信号转换为电平信号的方法。

在Verilog中,可以使用posedge或negedge关键字来检测信号的上升沿或下降沿。

当检测到上升沿或下降沿时,就可以生成相应的电平信号。

```verilogalways (posedge clk)begin// 生成电平信号的操作end```2.2 脉冲宽度控制通过控制脉冲信号的宽度,可以实现脉冲信号转换为电平信号。

在Verilog中,可以使用计数器或状态机来控制脉冲信号的宽度。

当脉冲信号的宽度达到一定值时,就可以生成相应的电平信号。

```verilogreg [7:0] count;always (posedge clk)beginif (pulse)begincount <= count + 1;if (count == 8)begincount <= 0;endendend```2.3 硬件触发器硬件触发器是一种专门用于脉冲信号转换为电平信号的电路。

verilog edge 用法

verilog edge 用法Verilog中的边沿触发器(edge-triggered)是一种常用的硬件描述语言,用于在特定信号的上升沿或下降沿上触发操作。

边沿触发器在数字电路设计中起着至关重要的作用,因为它们可以捕获信号的变化,并在特定时刻执行相应的操作。

在Verilog中,边沿触发器通常使用“posedge”和“negedge”关键字来表示上升沿和下降沿。

例如,下面是一个简单的Verilog模块,演示了边沿触发器的用法:verilog.module edge_trigger(。

input wire clk,。

input wire reset,。

input wire data,。

output reg q.);always @(posedge clk or negedge reset) begin.if (reset == 1'b0) begin.q <= 1'b0;end else begin.q <= data;end.end.endmodule.在这个例子中,当时钟信号(clk)的上升沿到来时,如果复位信号(reset)为低电平(0),则输出信号q被置为低电平(0)。

否则,输出信号q被赋值为输入信号data的值。

边沿触发器的用法不仅限于上面的例子,它们还可以用于实现时序逻辑、状态机和其他复杂的数字电路。

在实际的数字电路设计中,合理地使用边沿触发器可以帮助设计者实现高性能、低功耗的电路。

总之,Verilog中的边沿触发器是数字电路设计中不可或缺的重要组成部分,熟练掌握其用法对于数字电路设计者来说至关重要。

希望本文对您有所帮助,谢谢阅读!。

上升沿检测电路设计(分析“信号”文档)共8张PPT

module d_test (d,clk,dout);

input d,clk;

output dout;

wire dout;

wire reg

d_dly1_n; d_dly1;

assign连续赋值语句的变量定义为wire

reg

d_dly2;

always@(posedge clk)

Always过程赋值语句的变量定义为reg

电子信息工程技术专业教学资源库

Electronic information teaching resource

FPGA/CPLD应用技术

深圳职业技术学院

温国忠、余菲、曾启明、赵杰、刘俐、王毅峰

电子信息工程技术 专业课程

项目化ign of rising edge detection circuit

w检ir测e 到输入信号do的ut上; 升沿,输出一个高电平脉C冲LK

assign d_dly1_n=~din_dly;

input

d,clk;

reg

d_dly2;

Q din_dly

din_dly_n D

Q din_dly2_n

clk

CLK

dout

深圳职业技术学院 电子信息工程专业资源库

Page 5

Verilog HDL代码设计

设计任务分析 电路设计

代码设计 功能仿真

设计任务分析

设计任务

采用时钟检测输入信号d上升沿,当检测到输入信号d由低电平变成高电平 ( 01 )时,产生一个高电平脉冲,完成Verilog HDL设计与仿真

clk d

dout

时钟信号

输入信号

检测到输入信号的上升沿,输出一个高电平脉冲

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

在时序逻辑电路中,少不了“沿”。

always块敏感信号中可以通过关键字posedge和negedge来提取信号的上升沿和下降沿。

但是如果在程序块内部需要某个信号的上升沿或者下降沿、或者对于按钮触发的模块,由于按钮按下的持续时间很长,相当于一个电平信号,而不是脉冲信号,这时就需要边沿检测电路将其处理成单时钟周期宽度的脉冲信号。

下面介绍几种基于verilog的边沿检测电路。

(软件平台为quartus11.1,ModelSim-Altera 10.0)

方法1:

①Verilog源码

module detecEdge (clk,rst_n,din,pos_clk,neg_clk,doub_clk);

input clk,rst_n,din;

output pos_clk,neg_clk,doub_clk;

reg ctl_this, ctl_last;

always @(posedge clk or negedge rst_n) //同步复位(注意与异步复位的区别)

begin

if(!rst_n) //低有效

begin

ctl_this <= 0;

ctl_last <= 0;

end

else begin //注意非阻塞赋值的作用

ctl_this <= din; //din的当前时钟值

ctl_last <= ctl_this; //din的前一个时钟值

end

end

//assign pos_clk = (ctl_last == 0 && ctl_this == 1)? 1:0; //上升沿检测

//assign neg_clk = (ctl_last == 1 && ctl_this == 0)? 1:0; //下降沿检测

assign pos_clk = ctl_this & (!ctl_last); //上升沿检测

assign neg_clk = ctl_last & (!ctl_this); //下降沿检测

assign doub_clk = ctl_last ^ ctl_this; //双边沿检测

endmodule

②RTL综合图

③消耗资源

④Modelsim仿真

testbench源码:

`timescale 1ns/1ps

module testbench;

reg clk, rst_n, din;

wire pos_clk, neg_clk, doub_clk;

//调用detecEdge模块

detecEdge inst(

.clk(clk),

.rst_n(rst_n),

.din(din),

.pos_clk(pos_clk),

.neg_clk(neg_clk),

.doub_clk(doub_clk)

);

initial //输入信号初始化

begin

rst_n = 0;

clk = 0;

din = 0;

#50;

rst_n = 1;

end

always #100 din = ~din; //输入激励

always #5 clk = ~clk; //系统时钟endmodule

仿真波形:

由仿真结果知,当din上升沿到来时,pos_clk输出一个脉冲信号(宽度为1个clk),同理,当din下降沿到来时,neg_clk输出一个脉冲信号,doub_clk在din的上升沿和下降沿都输出脉冲信号。

方法2:

①Verilog源码

module detecEdge(clk,rst_n,din,pos_clk,neg_clk,doub_clk);

input clk;

input rst_n;

input din;

output pos_clk;

output neg_clk;

output doub_clk;

reg [2:0] ctl_r; //din状态寄存器

always @(posedge clk or negedge rst_n) //注意异步复位与同步复位

if(!rst_n) //低有效

begin

ctl_r <= 3'b000;

end

else begin

ctl_r <= {ctl_r[1:0], din};

end

assign pos_clk = (!ctl_r[2]) & ctl_r[1]; //上升沿检测

assign neg_clk = (!ctl_r[1]) & ctl_r[2]; //下降沿检测

assign doub_clk = ctl_r[2] ^ ctl_r[1]; //双边沿检测

endmodule

或者:

module detecEdge(clk,rst_n,din,pos_clk,neg_clk,doub_clk);

input clk;

input rst_n;

input din;

output pos_clk;

output neg_clk;

output doub_clk;

reg ctl_r0, ctl_r1, ctl_r2;

always @(posedge clk or negedge rst_n)

if(!rst_n) //低有效

begin

ctl_r0 <= 1'b0;

ctl_r1 <= 1'b0;

ctl_r2 <= 1'b0;

end

else

begin

ctl_r0 <= din;

ctl_r1 <= ctl_r0;

ctl_r2 <= ctl_r1;

end

assign pos_ clk = (!ctl_r2) & ctl _r1;

assign neg_ clk = (!ctl_r1) & ctl_r2;

assign doub_clk = ctl_r1 ^ ctl_r2;

②RTL综合图

③消耗资源

④modelsim仿真

testbench源码:

`timescale 1ns/1ps

module testbench;

reg clk, rst_n, din;

wire pos_clk, neg_clk, doub_clk;

//调用detecEdge模块

detecEdge inst(

.clk(clk),

.rst_n(rst_n),

.din(din),

.pos_clk(pos_clk),

.neg_clk(neg_clk),

.doub_clk(doub_clk)

);

initial //输入信号初始化

begin

rst_n = 0;

clk = 0;

din = 0;

#50;

rst_n = 1;

end

always #100 din = ~din; //输入激励

always #5 clk = ~clk; //系统时钟

endmodule

仿真波形:

注意与方法1的仿真波形的区别。

(方法2延迟了1个时钟周期)。