脉冲边沿检测电路.

脉冲信号正常与否的判断(附全部verilog源码)

1. 讲废话最近闲得蛋疼,翻阅了一下以前的项目笔记,想起去年折腾的一个小玩意儿。

记得当时是由于项目需要,boss找到我,说主板上有一个单片机,会发出heartbeat信号(就是MCU 等一些芯片的心跳信号,只要芯片活着,就会一直发送固定频率的脉冲出去,如果芯片挂了,heartbeat就一直为0或1),能不能用CPLD判断这个信号是否处于正常状态?(说白了,也就是判断单片机是否还活着)。

于是着手研究了一下这个heartbeat信号,用示波器测了一下,是一个标准的脉冲,频率为1HZ,占空比为50%,捯饬了两个小时,给出的解决方案是:每3s钟,计算一次上升沿的个数,如果此数值等于0,则heartbeat信号异常(用0表示),否则heartbeat信号正常(用1表示)。

把这个问题和方案贴出来,一是觉得实用性比较强,以前也没有看到有人做过,二是此解决方案对于其他同类问题有启发作用,只要弄懂此个案,其他问题也会触类旁通,易于解决。

现在给出方案的verilog源码,供大家研究,代码已通过项目验证,可靠好用。

2. 晒干货ps. 带★号处可根据需要进行修改./*********************************************************************** *******************Author: Bob LiuE-mail:*************************Device: LCMX0256C-3T100CTool: Diamond 1.1Function:判断脉冲输入信号是否正常Version: 2012-1-11 v1.0************************************************************************ ******************/module pulse_in_status (input CLK, // 基准时钟,50Minput pulse_in, // 被测脉冲output reg pulse_in_status // 指示被测脉冲正常与否,1表示正常,0异常);reg [1 :0] temp; // 电平值寄存器reg [31:0] CNT,CNT2;reg [3 :0] pos_edge; // 上升沿个数parameter delay = 50_000;always @ (posedge CLK)begin//================================================== ============//检测被测脉冲的边沿(带消抖)//================================================== ============if(CNT==5*delay) // ★延时5ms,此延时时间应大于脉冲抖动时间(一般为ms级),小于被测脉冲的半个时钟周期begintemp[0] <= pulse_in; // 保存pulse_in信号的当前状态值CNT <= 0 ;endelsebegintemp[1] <= temp[0]; // 保存pulse_in信号的前一状态值CNT <= CNT+1 ;end//================================================== ============//检测被测脉冲3s之内的上升沿个数,此数值等于0,则表示被测脉冲异常,否则为正常//================================================== ============if(CNT2==3000*delay) // ★3s之内判断上升沿个数,如果依然为0,说明pulse_in 脉冲信号异常,否则正常.beginif(pos_edge==0)beginpulse_in_status <= 0; // pulse_in脉冲信号异常CNT2 <= 0; //复位计时寄存器endelsebeginpulse_in_status <= 1; // pulse_in脉冲信号正常CNT2 <= 0; //复位计时寄存器pos_edge <= 0; //清空上升沿个数寄存器endendelsebeginCNT2 <= CNT2+1; //计时if(temp==2'b01) // 如果检测到pulse_in的一个上升沿,上升沿个数计数器pos_edge加1beginpos_edge <= pos_edge+1;endendendendmodule3. 扯犊子以上源码,可适用于不同频率脉冲信号的判断,占空比不是关键点,如果你的脉冲信号是10HZ(占空比任意),即时钟周期为0.1s,那么你可以判断0.3s内脉冲的个数,从而判别此脉冲输入是否正常,只需修改代码中带★号的地方即可。

一种高速低抖动四相位时钟电路的设计

一种高速低抖动四相位时钟电路的设计崔伟;张铁良;杨松【摘要】超高速A/D转换器对精准的时钟电路提出严格要求,时钟抖动是影响其精度的重要因素.文章在分析时钟抖动对A/D转换器的影响后,介绍了一种适用于GHz的低抖动四相位时钟电路.电路采用时钟恢复电路、四相位分布网络和相位校正电路,得到占空比稳定、相位误差小的四相位时钟.采用0.18μm CMOS工艺实现,电路仿真表明,四相位输出时钟抖动102 fs,占空比调整范围30%~70%,功耗**********.【期刊名称】《电子元件与材料》【年(卷),期】2019(038)001【总页数】6页(P67-71,77)【关键词】高速时钟;时钟抖动;多相位;时钟恢复;模数转换器;CMOS【作者】崔伟;张铁良;杨松【作者单位】北京微电子技术研究所, 北京 100076;北京微电子技术研究所, 北京100076;北京微电子技术研究所, 北京 100076【正文语种】中文【中图分类】TN432A/D转换器 (Analog to Digital Converter,ADC)是模拟系统与数字系统接口的关键部件,广泛应用于工业、民用、雷达等领域。

转换器的发展使采样速率不断提升,在超高速A/D转换器中,广泛采用多通道时间交织技术来提高整体采样率,其必须严格按照时间序列进行信号采样和数模转换,因而对时钟电路提出严格要求。

随着工艺技术的提升,时钟的上升、下降时间在整个时钟周期中所占的比例不断增大,占空比失调问题越发严重[1]。

此外,时钟抖动直接影响A/D转换器的信噪比(Signal Noise Ratio,SNR)等参数指标[2]。

目前,有多种方法可以实现低抖动高速时钟电路,包括基于延迟锁相环技术的时钟电路[3-4],基于连续时间积分器的时钟电路[5]和基于脉宽控制环路的时钟电路[6-7],它们各有特点,适用于不同类型的A/D转换器。

本文提出的高速低抖动四相位时钟电路,应用于时间交织ADC,为ADC采样保持电路提供精准的高速四相位时钟。

脉冲边沿检测

脉冲边缘检测法:Reg[2:0] key_rst; //用来保存按键的值Reg[2:0] key_rst_r; //用来保存key_rst的值always @(posedge clk or negedge rst)beginif(!rst)key_rst<=3’b111;elsekey_rst<={key1,key2,key3};//将三个按键的值都赋给key_rstendalways @ (posedge clk or negedge rst)beginif(!rst) key_rst_r<=3’b111;elsekey_rst_r<=key_rst;endwire[2:0] key_an;assign key_an=key_rst_r&(~key_rst);//实现了记录由低电平按下的目的到此就可以判断有按键按下或有抖动。

这两个是那一个到此还不确定。

Reg[2:0] low_sw;Reg[2:0] low_sw_r;Reg[19:0] cnt;always @(posedge clk or negedge rst)beginif(!rst) cnt<=20’d0;else if(key_an) cnt<=20’d0;else cnt<=cnt+1’b1;endalways @(posedge clk or negedge clk)beginif(!rst) low_sw<=3’b111;else if(cnt==20’hfffff)low_sw<={key1,key2,key3};endalways @(posedge clk or negedge rst)beginif(!rst) low_sw_r<=3’b111;elselow_sw_r<=low_sw;endwire[2:0] led_ctrlassign led_ctrl=low_sw_r&(~low_sw);到此就可以判断是按键按下还是抖动了,如果led_ctrl=1那就是按键按下了,如果led_ctrl=0,则是抖动。

脉冲电路设计

脉冲电路脉冲电路的基本知识在数字电路中分别以高电平和低电平表示1状态和0状态。

此时电信号的波形是非正弦波。

通常,就把一切既非直流又非正弦交流的电压或电流统称为脉冲。

图Z1601表示出几种常见的脉冲波形,它们既可有规律地重复出现,也可以偶尔出现一次。

脉冲波形多种多样,表征它们特性的参数也不尽相同,这里,仅以图Z1602所示的矩形脉冲为例,介绍脉冲波形的主要参数。

(1)脉冲幅度Vm--脉冲电压或电流的最大值。

脉冲电压幅度的单位为V、mV,脉冲电流幅度的单位为A、mA。

(2)脉冲前沿上升时间tr--脉冲前沿从0.1Vm上升到0.9Vm所需要的时间。

单位为ms、μs、ns。

(3)脉冲后沿下降时间tf--脉冲后沿从0.9Vm下降到0.1Vm所需要的时间。

单位为:ms、μs、ns。

(4)脉冲宽度tk--从脉冲前沿上升到0.5Vm处开始,到脉冲下降到0.5Vm处为止的一段时间。

单位为:s、ms、μs或ns。

(5)脉冲周期T--周期性重复的脉冲序列中,两相邻脉冲重复出现的间隔时间。

单位为:s、ms、μs。

(6)脉冲重复频率--脉冲周期的倒数,即f =1/T,表示单位时间内脉冲重复出现的次数,单位为Hz、kHz、MHz。

(7)占空比tk/T--脉冲宽度与脉冲周期的比值,亦称占空系数。

对电路来说,有个阻抗匹配问题,只有当阻抗匹配时,输出效果才最好,否则,有可能导致负载力不足,导致一旦外加电路,就会把电压拉下了,建议后面加一级运放增大负载能力交流电源的零交越脉冲电路设计时间:2012-04-25 14:58:04 来源:作者:本设计中的电路可生成一个交流电源的零交越脉冲,并提供电气绝缘。

输出脉冲的下降沿出现在零交越点前约200μs。

使用这个电路可以安全地停止一个可控硅栅极的触发,使之有时间正常地关断。

只有当主电压约为0V时,电路才产生短脉冲,因此在230V、50Hz输入下只耗电200mW。

电路为电容C1充电,直至达到22V齐纳二极管D3的上限(图1与参考文献1)。

脉冲信号检波电路设计

脉冲信号检波电路设计

单片机自带A/D采样高频脉冲信号的检波电路。

该电路是基于AD8310芯片的检波电路设计,经过多级检波,将脉冲信号频率降低,从而达到降低采样成本的目的。

关键词:高频;脉冲信号;检波电路

引言

对于脉冲信号,频率高达上百兆赫兹,脉冲沿较陡,一般的采样芯片无法直接对其进行采样处理,而采用高采样率芯片直接对脉冲信号进行采集则成本较高。

因此,目前工业上常用的处理方法是对脉冲信号进行检波降频处理。

1常用方法论证及比较

1.1二极管分立元件检波

二极管分立元件检波方法主要由二极管,电容器,电阻构成。

其特点为设计简单,成本低,线性度差,温度稳定性低。

1.2对数放大器检波

对数放大器检波方法主要由对数放大器和二极管组成。

采用级联放大器输出端加二极管整流电路,将脉冲信号或者其它交流信号转换为直流电压。

其特点为元器件多,对高频信号效果差,线性度和温度稳定性较二极管分立元件检波稍好。

1.3专用检波芯片检波

目前检波芯片主要分为功率检波和对数检波两种。

芯片内部分为检波和。

脉冲边沿检测电路原理

优点

具有记忆功能,能够保持输出状态;对输入脉冲的幅度和 宽度要求较低。

应用场景

适用于需要记忆脉冲边沿状态的场合,如电机控制、遥控 开关等。

集成电路型

工作原理 优点 缺点

应用场景

集成电路型脉冲边沿检测电路采用专门的集成电路芯片实现脉 冲边沿检测功能,具有高度的集成化和智能化。

功能强大,性能稳定;易于实现复杂逻辑功能;体积小,重量 轻。

电源和偏置电路

为各级电路提供稳定的工作电压和偏置电流,确保电路 正常工作。

03 常见脉冲边沿检测电路类 型

单稳态触发器型

工作原理

单稳态触发器型脉冲边沿检测电路利用单稳态触发器的特性,在输入 脉冲的上升沿或下降沿触发时产生一定宽度的输出脉冲。

优点

电路结构简单,易于实现;输出脉冲宽度可调,适应性强。

可靠性

衡量电路在长时间工作过程中的稳定性和可靠性,包括温漂、时漂等参数的变化情况,应足够高 以保证长期稳定的性能表现。

06 脉冲边沿检测电路应用实 例分析

在数字系统中的应用

时钟同步

在数字系统中,脉冲边沿检测电路可用于实 现精确的时钟同步,确保各个数字模块在统 一的时钟信号下正常工作。

数据传输

通过检测脉冲信号的边沿变化,可以实现数字信号 的高速、准确传输,提高数据传输的效率和可靠性 。

可靠性。

智能化阶段

近年来,随着人工智能和机器学 习技术的发展,脉冲边沿检测电 路开始向智能化方向发展,通过 算法优化和自适应调整来提高检

测精度和响应速度。

02 脉冲边沿检测电路基本原 理

脉冲信号特性

01

02

03

脉冲幅度表示脉冲信号电压或来自流 的最大值,决定了信号的 强度。

FPGA_跨时钟域介绍

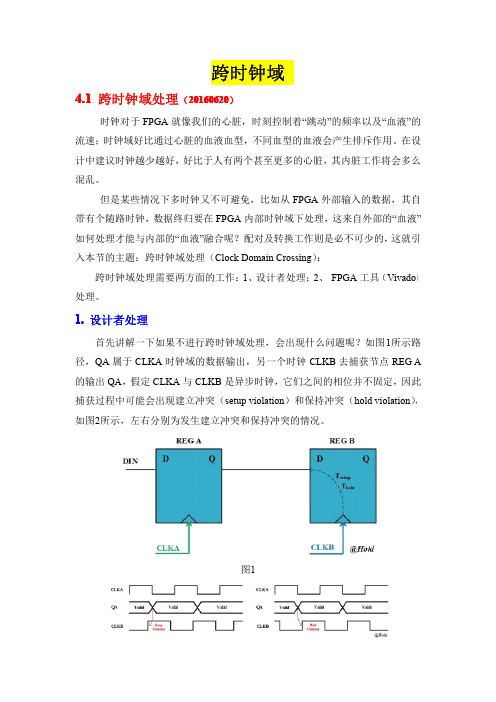

跨时钟域4.1跨时钟域处理(20160620)时钟对于FPGA就像我们的心脏,时刻控制着“跳动”的频率以及“血液”的流速;时钟域好比通过心脏的血液血型,不同血型的血液会产生排斥作用。

在设计中建议时钟越少越好,好比于人有两个甚至更多的心脏,其内脏工作将会多么混乱。

但是某些情况下多时钟又不可避免,比如从FPGA外部输入的数据,其自带有个随路时钟,数据终归要在FPGA内部时钟域下处理,这来自外部的“血液”如何处理才能与内部的“血液”融合呢?配对及转换工作则是必不可少的,这就引入本节的主题:跨时钟域处理(Clock Domain Crossing):跨时钟域处理需要两方面的工作:1、设计者处理;2、FPGA工具(Vivado)处理。

1.设计者处理首先讲解一下如果不进行跨时钟域处理,会出现什么问题呢?如图1所示路径,QA属于CLKA时钟域的数据输出,另一个时钟CLKB去捕获节点REG A 的输出QA,假定CLKA与CLKB是异步时钟,它们之间的相位并不固定,因此捕获过程中可能会出现建立冲突(setup violation)和保持冲突(hold violation),如图2所示,左右分别为发生建立冲突和保持冲突的情况。

图1图2当冲突出现时(我感觉整个人都不好了),会发生什么事情呢?在发生建立冲突或者保持冲突,捕获节点(REG B)会处于一个不定的状态,正常的状态是高电平或者低电平,而此时的状态停留在高电平和低电平的中间,无效的电平X,称这个状态为亚稳态。

如图3所示,捕获节点输出保持在亚稳态,可能在整个时钟周期内都保持在亚稳态,由于不正确的状态,其后连接的逻辑在功能实现上就会出现问题,比如一个判断信号上升沿的逻辑,通常判断D==HIGH&&D_PREV==LOW(D为信号当前电平状态,D_PREV为信号上个时钟的电平状态)是否成立,而发生亚稳态时则D_PREV==X,这个上升沿将会错过。

因此,加入跨时钟域处理设计是必须的。

FPGA_跨时钟域

跨时钟域4.1跨时钟域处理(20160620)时钟对于FPGA就像我们的心脏,时刻控制着“跳动”的频率以及“血液”的流速;时钟域好比通过心脏的血液血型,不同血型的血液会产生排斥作用。

在设计中建议时钟越少越好,好比于人有两个甚至更多的心脏,其内脏工作将会多么混乱。

但是某些情况下多时钟又不可避免,比如从FPGA外部输入的数据,其自带有个随路时钟,数据终归要在FPGA内部时钟域下处理,这来自外部的“血液”如何处理才能与内部的“血液”融合呢?配对及转换工作则是必不可少的,这就引入本节的主题:跨时钟域处理(Clock Domain Crossing):跨时钟域处理需要两方面的工作:1、设计者处理;2、FPGA工具(Vivado)处理。

1.设计者处理首先讲解一下如果不进行跨时钟域处理,会出现什么问题呢?如图1所示路径,QA属于CLKA时钟域的数据输出,另一个时钟CLKB去捕获节点REG A 的输出QA,假定CLKA与CLKB是异步时钟,它们之间的相位并不固定,因此捕获过程中可能会出现建立冲突(setup violation)和保持冲突(hold violation),如图2所示,左右分别为发生建立冲突和保持冲突的情况。

图1图2当冲突出现时(我感觉整个人都不好了),会发生什么事情呢?在发生建立冲突或者保持冲突,捕获节点(REG B)会处于一个不定的状态,正常的状态是高电平或者低电平,而此时的状态停留在高电平和低电平的中间,无效的电平X,称这个状态为亚稳态。

如图3所示,捕获节点输出保持在亚稳态,可能在整个时钟周期内都保持在亚稳态,由于不正确的状态,其后连接的逻辑在功能实现上就会出现问题,比如一个判断信号上升沿的逻辑,通常判断D==HIGH&&D_PREV==LOW(D为信号当前电平状态,D_PREV为信号上个时钟的电平状态)是否成立,而发生亚稳态时则D_PREV==X,这个上升沿将会错过。

因此,加入跨时钟域处理设计是必须的。

脉冲电路PPT课件

三极管由截止转变为饱和导通所需的时 间称为开启时间,即在基区逐渐积累电荷, 使电流由小变大所需时间。由饱和导通转变 为截止所需的时间称为关闭时间,即在基区 通过中和逐渐清除电荷,使电流逐渐变小所 需时间。

通常关闭时间比开启时间要长很多倍, 这主要是射极输入的载流子在基区中积累电 荷比基区中载流子中和这些电荷要快得多, 普通开关管的开启时间约为10~30ns,关闭 时间约为100~200ns,高频管的开关速度比 普通开关管慢得多。对于生物电脉冲,它的 前沿约为数毫秒,也可以用高频管代替开关 管。

第二节 晶体管反相器

一. 晶体三极管的开关特性 晶体三极管不仅有放大作用,而且还有开关作用。在

脉冲数字电路中就是利用三极管的开关作用。 由其特性曲线知,当基极电流Ib≤0时,晶体管工作在

截止区。此时集电极电流Ic≈0,晶体管的发射结和集电结 均处于反向偏置,相当于开关断开。当Ib由零逐渐上升时, 晶体管的工作状态由截止区进入放大区,一旦Ib继续上升 达到临界饱和电流Ibs时,三极管处于临界饱和状态,如再 增大Ib,使Ib>Ibs,三极管进入饱和区。此时集射极电压 Uce接近于零,Ib基本上失去了对Ic的控制能力,相当于开 关接通。

体管饱和程度加深,输出信号 Uo仍然为零。如果充电的时 间常数(R1+rbe)C小于脉冲宽 度,电容C在正脉冲持续期间 (输入高电平)得到完全充电, 其电压(左正右负)接近于输入 脉冲的幅度电压Um。当输入 脉冲下降时,电容C开始放电, 迫使基极电位下降到-Um,三 极管截止,输出信号 Uo上升 到接近于Ec。

电平渐移,对信号

放大、变换和计数等会 造成困难。为了克服这 个缺点,对电路进行改 造,在电阻R上并联一 个二极管 D。

输入波形 输出波形

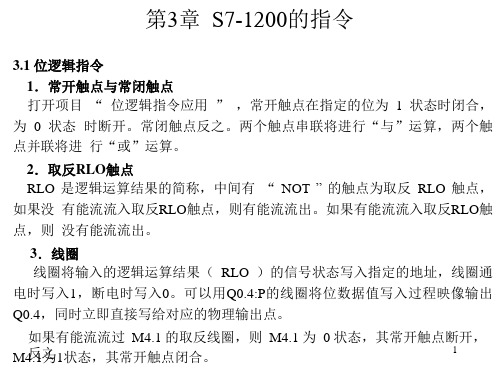

S7-1200-PLC编程及应用第三版--ppt课件-第3章

8.在信号边沿置位操作数的指令 中间有 P 的线圈是 “ 在信号上升沿置位操作数 ” 指令,仅在流进该线圈 的能流 的上升沿,该指令的输出位M6.1为1状态。其他情况下M6.1均为0状态, M6.2 为保存P线圈输入端的RLO的边沿存储位。 中间有 N 的线圈是 “ 在信号下降沿置位操作数 ” 指令,仅在流进该线圈 的能流 的下降沿,该指令的输出位M6.3为1状态。其他情况下M6.3均为0状态, M6.4 为边沿存储位。 上述两条线圈格式的指令对能流是畅通无阻的,这两条指令可以放置在程序 段的中间或最右边。在运行时改变I0.7的状态,可以使M6.6置位和复位。

2Leabharlann 5.置位位域指令与复位位域指令 “ 置位位域 ” 指令 SET_BF 将指定的地址开始的连续的若干个位地址置位, “ 复 位位域”指令RESET_BF将指定的地址开始的连续的若干个位地址复位。

7.扫描操作数信号边沿的指令 中间有P的触点的名称为 “ 扫描操作数的信号上升沿”,在I0.6 的上升沿, 该触 点接通一个扫描周期。M4.3为边沿存储位,用来存储上一次扫描循环时 I0.6的 状态。通过比较I0.6前后两次循环的状态,来检测信号的边沿。边沿存 储位的 地址只能在程序中使用一次。不能用代码块的临时局部数据或I/O变量 来作边 沿存储位。 中间有 N 的触点的名称为 “ 扫描操作数的信号下降沿 ” ,在 M4.4 的下降 RES沿E,T_BF的线圈“通电”一个扫描周期。该触点下面的M4.5为边沿存储位。

12

3.关断延时定时器指令 关断延时定时器( TOF )用于将 Q 输出的复位操作延时 PT 指定的一段时间 IN输入电路接通时,输出Q为1状态,当前时间被清零。在IN的下降沿开始定 时,ET从0逐渐增大。ET等于预设值时,输出Q变为0状态,当前时间保持不 变,直到IN输入电路接通(见波形A)。关断延时定时器可以用于设备停机 后 的延时。 如果 ET 未达到 PT 预设的值, IN 输入信号就变为 1 状态, ET 被清 0 , 输出 Q 保 持1状态不变(见波形B)。复位线圈RT通电时,如果IN输入信号 为0状态, 则定时器被复位,当前时间被清零,输出Q变为0状态(见波形C)。 如果复 位时IN输入信号为1状态,则复位信号不起作用(见波形D)。

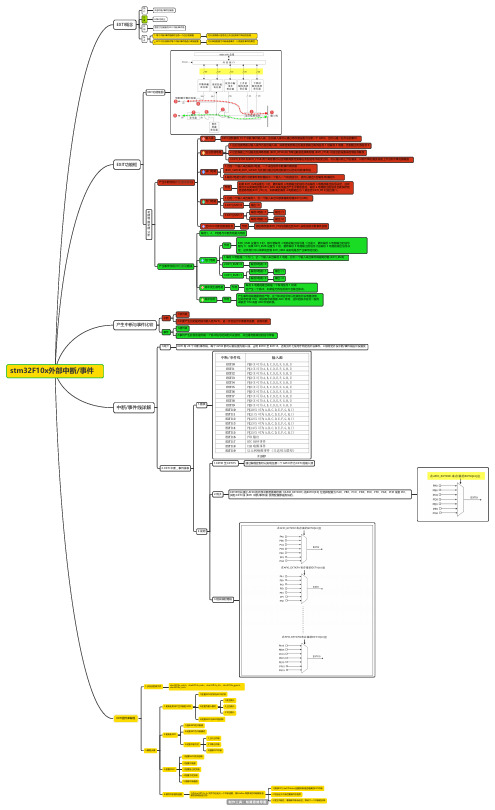

事件EXTI思维导图

1.在stm32f10x_it.c文件中自定义一个中断函数,用#define 将原来的中断服务函 数名改成自定义的

1.使用EXTI_GetITStatus()函数判断是否是真的EXTI中断 2.写自定义中断后要操作的程序 3.发生中

作用

产生事件的线路最终的产物,这个脉冲信号可以给其他外设电路使用, 比如定时器 TIM、模拟数字转换器 ADC 等等,这样的脉冲信号一般用 来触发 TIM 或者 ADC开始转换。

产生中断与事件比较

中断 事件

1.软件级 2.中断产生目的是把信号输入到NVIC,进一步会运行中断服务函数,实现功能 1.硬件级 2.事件产生的目的是传输一个脉冲信号给其他外设使用,并且是电路级别的信号传输

析

产生事件流程(绿色虚线)路线

作用

EXTI_EMR 设置为 0 时,那不管编号 3 电路的输出信号是 1 还是 0,最终编号 6 电路输出的信号 都为 0;如果 EXTI_EMR 设置为 1 时,最终编号 6 电路输出的信号才由编号 3 电路的输出信号决 定,这样我们可以简单的控制 EXTI_EMR 来实现是否产生事件的目的。

2.例子

EXTI0可以通过 AFIO 的外部中断配置寄存器 1(AFIO_EXTICR1) 的EXTI0[3:0] 位选择配置为 PA0、PB0、PC0、PD0、PE0、PF0、PG0、PH0 或者 PI0, 其他 EXTI 线 (EXTI 中断/事件线) 使用配置都是类似的。

2.说明

3.相关映射路线

或门电路

1.它的一个输入来自编号2电路,一个来自软件中断事件寄存器 (EXTI_SWIER),EXTI_SWIER 允许我们通过程序控制就可以启动中断/事件线

2.编号2电路与软件中断事件寄存器其中一个输入一个有效信号1,就可以输出1给编号4和编号6

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基础知识

Q

Q

G1 >1

>1 G2

R

S

J 1J

Q

C1

K 1K

Q

CP

RS 00 01 10 11

Q n+1 Qn

1

0 不用

功能 保持 置1 置0 不许

JK 00 01 10 11

Q n+1 Qn

0

1 Qn

功能 保持 置0 置1 翻转

电路工作原理

+5V

复位开关 脉冲输入

IC1a

RD

1J C1

Q1 10

5 >1 4 6

IC2b

LED1 LED2

元件和器件

1Y 1 1A 2 1B 3 2Y 4 2A 5 2B 6 GND 7

14 VCC

>1

13 4Y

>1 12 4B

11 4A

>1

10 3Y

>1 9 3B

8 3A

74LS02 四2输入或非门

1CP 1 1RD 2 1K 3 VCC 4 2CP 5 2RD 6 2J 7

1K= Biblioteka 保持J K Q = 1 翻转

IC2a 0 LED1

>1

IC2c

RD 1J

>1

C1

1K

IC1b

Q2

10

>1

IC2b 01

LED2

当第一个脉冲是上升沿… 其后的脉冲不再改变RS触发器状态

电路工作原理

+5V

复位开关 脉冲输入

IC1a RD

1J

C1 Q1 10

1K

= 0 保持

J K Q = 1 翻转

IC2a 01

>1

LED1

IC2c

RD 1J

>1

C1

1K

IC1b

当第一个脉冲是下降沿…

Q2

10

>1

IC2b 0

LED2

其后的脉冲不再改变RS触发器状态

引脚安排

复位开关

脉冲输入

+5V

IC1a RD

1J C1 Q1 1K 13

RD

12 >1 13 11

1J C1

Q2

1K

8

IC1b

IC2a 2

>1 1 3

脉冲边沿检测电路

一、实验目的 二、基础知识 三、电路及工作原理 四、元件和器件 五、引脚安排 六、样板

实验目的:

1. 熟悉基本RS触发器的功能; 2. 熟悉TTL集成或非门74LS02的使用方法; 3. 熟悉TTL集成JK触发器74LS73的使用方法; 4.了解一种检测脉冲第一个边沿跳变方向的方法。

74LS73

14 1J 13 1Q 12 1Q 11 GND 10 2K 9 2Q 8 2Q

双下降沿JK触发器

Y AB

参见P176、177

脉冲信号由实 验面板上的信 号提供