debussy和modelsim协同仿真(VHDL)

基于modelsim和debussy的批处理仿真

基于modelsim和debussy的批处理仿真本文将会叙述采用批处理的方法进行modelsim结合debussy仿真调试。

目的在于提高仿真效率。

该流程只适用于FPGA的前仿真,使用verilog文件以及测试文件。

如此操作有以下几个优点:1、虽然开始的时候需要稍作准备,但等你完成了一次仿真后,以后只需要略微修改一下就可以直接应用到其他工程里边去。

相对于采用用modelsim的界面操作,省去了很多例如创建工程、添加仿真文件、进行编译、进行仿真等等节省了宝贵的工作时间。

当然可以提高工作效率。

2、文件管理非常清楚。

所有的verilog文件都放在一个文件夹,所有仿真需要的文件以及仿真结果都放在另外一个文件里边,而且仿真后的文件也相对于使用modelsim界面操作仿真结果要少。

3、还有就是,因为没有界面操作,仿真速度会快很多,特别是采用modelsim进行稍微大的仿真的时候,这时候采用这种方法的优势就更加明显了。

以下是进行仿真前的准备工作第一步:安装modelsim、debussy软件以及编译相应的仿真库,如何安装以及破解,网络上有很多的资料说明,在这里就不详细说了。

对于仿真库的编译,也有很多的方法,可以参考文章《modelsim添加仿真库方法》by Craftor。

许多工程师也在自己的博客写过或转载过相似的库编译的方法。

这些都是我进行批处理仿真前已经做好了。

我的软件都是装在D盘分别是:D:\modeltech_6.5e和D:\Novas\Debussy第二步:创建do文件。

如下(行号不需要):1、vlib work2、vlog-f vfile.f-incr3、vsim-L xilinxcorelib_ver-L unisims_ver-L simprims_ver-L uni9000_ver-L unisims_ver-pli novas_fli.dll-lib work tuner_iic_tb4、run40ms5、exit然后保存为sim.do解析:1表示创建仿真工作库,也就是将你编译文件之后的文件存在这个work文件夹下。

VHDL仿真,Verilog_HDL仿真入门--ModelSim使用简介

VHDL仿真,Verilog_HDL仿真入门--ModelSim使用简介VHDL仿真,Verilog HDL仿真入门--ModelSim使用简介学硬件描述语言当然得实践,就得用软件仿真。

入门其实就是讲下仿真软件怎么用,是很简单的一件事,但是对于刚学的人来说可能有点无从下手。

我之前就有点迷茫,所以写这个入门当自己的笔记,也希望能给自学的新手有所帮助。

仿真VHDL和Verilog HDL并没有什么区别,一般的软件两种语言也都支持,仿真的步骤和方法也都是一样的。

常用的软件有Model Sim和Quartus II。

Quartus II功能很强大!实际的工作经常用它,它提供了功能仿真和时序仿真两种方式,但是作为学习HDL 并不方便,因为它compile编译的时候很慢,对于复杂的逻辑更是要很长时间。

好的一点是,Quartus II编译后可以清楚的看到它使用了芯片的多少资源,各信号不同的延时等等。

另外,Quartus II编译后也可以调用第三方的仿真工具,如Model Sim进行仿真。

而Model Sim只完成逻辑功能的仿真,并不考虑具体使用什么器件,学习HDL 或者设计逻辑的时候compile一次所用的时间很短,便于调试找出逻辑的错误。

所以初学仿真推荐使用Model Sim。

本文也只讲下用Model Sim仿真逻辑的方法。

以下部分基本是参照软件帮助简写的,只是原来是英文的而且说的比较繁琐一些,也更详细内容更多。

详见Model Sim菜单Help--SE PDFDocumentation--tutorial。

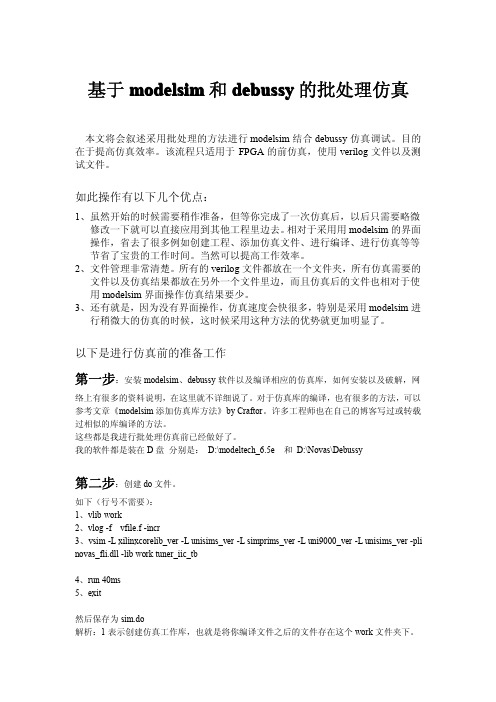

仿真有两种方法。

一种是Basic Simulation,就是直接建立库,然后编译源文件。

另一种是通过建立Project来仿真,建立Project时软件会为它建立一个库,然后的仿真是一样的。

Basic Simulation的流程图如下预览:下面详细写一个例子的步骤1. 建立库。

选择菜单File>New>Library。

如何使用debussy与modelsim做co-simulation(soc)(verilog)(vhdl)(debussy)(modelsim)

如何使用Debussy與ModelSim做Co-Simulation (SOC) (Verilog) (VHDL) (Debussy) (ModelSim) Abstract本文介紹如何使用Debussy與ModelSim做Co-Simulation,並使用Verilog、VHDL以及Verilog搭配VHDL交叉一起simulation。

Introduction使用環境:Debussy v9 + ModelSim SE我之前一直使用Debussy + NC-Verilog做simulation,Debussy (Verdi)可以說是HDL的Source Insight,是trace與debug的神兵利器,NC-Verilog也是Verilog simulator中速度最快的,可是最近因工作需要,拿到的一包code卻是用Verilog寫RTL,用VHDL寫testbench,所以必須2種語言一起做simulation,我在NC-Verilog一直無法成功讓兩種語言一起simulation。

ModelSim雖然支援Verilog + VHDL co-simulation,但用慣Debussy的我還是無法忘懷其方便的trace code方式,所以若能讓ModelSim也能dump出Debussy所需要的fsdb檔案,這樣就太完美了。

接下來會分4個方式討論與testbench皆使用Verilog與testbench皆使用VHDL使用VHDL,testbench使用Verilog使用Verilog,testbench使用VHDL與testbench皆使用VerilogStep 1:設定ModeSim使用Verilog PLI (因為testbench使用Verilog)將C:\Novas\Debussy\share\PLI\modelsim_pli\WINNT\複製到C:\\win32\下修改C:\\,將Veriuser部分修改成如下所示:; List of dynamically loaded objects for Verilog PLI applications; Veriuser =; use by verilogVeriuser =; use by vhdl; Veriuser =复制代码是個read only檔,要修改前記得修改其屬性才能存檔。

Debussy是一个VerilogVHDL调试工具

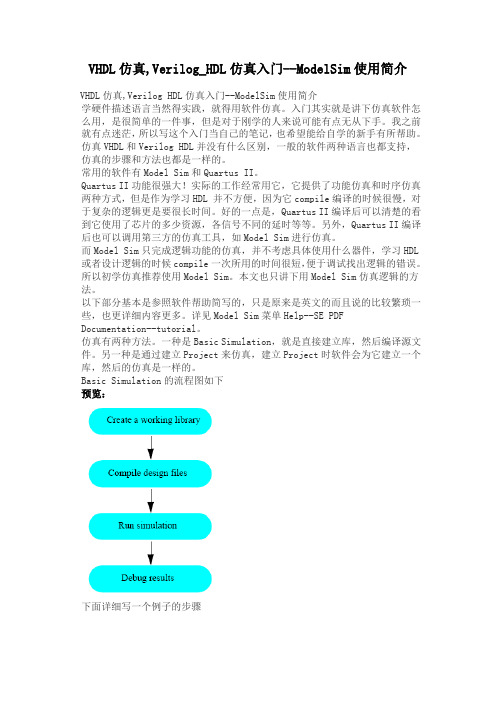

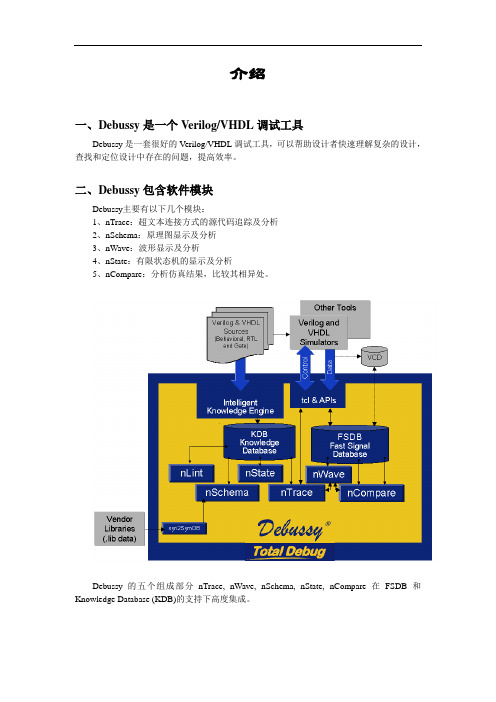

介绍一、Debussy是一个Verilog/VHDL调试工具Debussy是一套很好的Verilog/VHDL调试工具,可以帮助设计者快速理解复杂的设计,查找和定位设计中存在的问题,提高效率。

二、Debussy包含软件模块Debussy主要有以下几个模块:1、nTrace:超文本连接方式的源代码追踪及分析2、nSchema:原理图显示及分析3、nWave:波形显示及分析4、nState:有限状态机的显示及分析5、nCompare:分析仿真结果,比较其相异处。

Debussy的五个组成部分nTrace, nWave, nSchema, nState, nCompare在FSDB和Knowledge Database (KDB)的支持下高度集成。

三、Debussy功能Debussy直接编译Verilog/VHDL源代码,并且采用了预综合技术识别电路的单元,可以生成原理图。

在导入仿真结果后,可以用Active Annotation在源代码、原理图、状态图上动态显示变量的仿真值。

Debussy的输入为:Verilog/VHDL或混合语言源代码,仿真波形文件,SDF支持的波形格式:vcd,fsdb,模拟波形文件(PowerMill,TimeMill,Avant! Star-Sim,SmartSpice)支持的仿真器:VCS,Verilog-XL,NC-verilog,NC-VHDL,Modelsim,Leapfrog,Ploaris。

操作一、启动1. 启动%debussy启动debussy时,弹出一个nTrace窗口,包含三个子窗口:a、左边是Hierarchical Browser窗口,用来显示设计的层次(design hierachy)。

b、右边是Source Code window,显示源代码。

跟踪信号的驱动、负载。

c、底下是Message window(消息窗口),用来报告操作的结果。

2.导入设计File->Import DesignDebussy提供了两种导入设计的方法:A、从设计源文件直接导入B、从库导入(先将源文件编译成库)Note: 可以用命令的方式直接启动debussy并导入设计文件,即在命令行上列出所有的选项和源文件,或者把这些选项和源文件写到一个文件中,用-f选项指定这个文件。

debussy和modelsim协同仿真(VHDL)

debussy和modelsim协同仿真(VHDL)1、编辑modelsim根目录下的modelsim.ini文件,将; Veriuser = veriuser.sl 更换为Veriuser = novas_fli.dll。

2、将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas_fli.dll 拷贝至C:\Modeltech_6.1d\win32中3、将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas.vhd拷贝至工程所在目录4、打开modelsim,在工程所在目录新建一个novas的LIB,然后编译novas.vhd文件。

5、在testbentch中增加library novas;use novas.pkg.all;6、在testbentch中添加debussy_debug:processbeginfsdbDumpfile("**.fsdb");fsdbDumpvars(0,"顶层文件名(有testbench的话即为testbench名)");wait;end process debussy_debug;7、编译整个工程,然后仿真8、打开debussy, import design加载文件,设置好顶层文件,打开nWARE,加入信号即可为了更加方便的使用DEBUSSY,我们可以编写DO文件来达到这一目的:1、先新建dc16_tca目录。

比如在E:/WORK/TEMP里新建该目录,把源程序都放在dc16_tca/soure里头。

2、编写tca.do文件:下面是以TCA为例说明一下这个步骤:tca.do:#start#建立并编译novas库vlib novasvmap novas novasvcom -work novas D:/WORK/temp/dc16_TCA/source/novas.vhd#建立并编译work库vlib workvcom -work work d:/work/temp/dc16_tca/source/dc16_constant_def.vhdvcom -work work d:/work/temp/dc16_tca/source/dc16_tca.vhdvcom -work work d:/work/temp/dc16_tca/source/dc16_tca_tb.vhdvsim dc16_tca_tb#仿真运行时间run 10000usquit#end3、然后在dos界面先进入到dc16_tca目录里,比如E:/WORK/TEMP/dc16_tca然后再输入>c:\modeltech_6.1b\win32/vsim -c -do tca.do这里假设modelsim装在C盘个人感觉modelsim的仿真速度用DO文件的方式比用modelsim的GUI方式要快很多。

Debussy是一个VerilogVHDL调试工具

介绍一、Debussy是一个Verilog/VHDL调试工具Debussy是一套很好的Verilog/VHDL调试工具,可以帮助设计者快速理解复杂的设计,查找和定位设计中存在的问题,提高效率。

二、Debussy包含软件模块Debussy主要有以下几个模块:1、nTrace:超文本连接方式的源代码追踪及分析2、nSchema:原理图显示及分析3、nWave:波形显示及分析4、nState:有限状态机的显示及分析5、nCompare:分析仿真结果,比较其相异处。

Debussy的五个组成部分nTrace, nWave, nSchema, nState, nCompare在FSDB和Knowledge Database (KDB)的支持下高度集成。

三、Debussy功能Debussy直接编译Verilog/VHDL源代码,并且采用了预综合技术识别电路的单元,可以生成原理图。

在导入仿真结果后,可以用Active Annotation在源代码、原理图、状态图上动态显示变量的仿真值。

Debussy的输入为:Verilog/VHDL或混合语言源代码,仿真波形文件,SDF支持的波形格式:vcd,fsdb,模拟波形文件(PowerMill,TimeMill,Avant! Star-Sim,SmartSpice)支持的仿真器:VCS,Verilog-XL,NC-verilog,NC-VHDL,Modelsim,Leapfrog,Ploaris。

操作一、启动1. 启动%debussy启动debussy时,弹出一个nTrace窗口,包含三个子窗口:a、左边是Hierarchical Browser窗口,用来显示设计的层次(design hierachy)。

b、右边是Source Code window,显示源代码。

跟踪信号的驱动、负载。

c、底下是Message window(消息窗口),用来报告操作的结果。

2.导入设计File->Import DesignDebussy提供了两种导入设计的方法:A、从设计源文件直接导入B、从库导入(先将源文件编译成库)Note: 可以用命令的方式直接启动debussy并导入设计文件,即在命令行上列出所有的选项和源文件,或者把这些选项和源文件写到一个文件中,用-f选项指定这个文件。

EDK工程ModelSim仿真流程

EDK工程ModelSim仿真流程前期准备:1.已经安装软件工具:Xilinx ISE 11.1ModelSim 6.5Debussy5.4v92.EDK和ModelSim6.5联合仿真库设置完毕3.EDK和ModelSim6.5可以生成”.FSDB”文件,供Debussy波形查看器观察波形以参加电子设计竞赛的H.264工程为例,进行仿真演示。

1.首先确保工程simulation文件夹下没有文件。

2.如果有文件,要通过如下方式清除,不能直接删除。

3.清除后,点击Simulation Generate Simulation HDLFiles,重新生成工程仿真的库文件。

Console控制台显示生成了Simulation ModelSimulation文件夹下生成了一堆文件。

4.在Simulation文件夹下,找到“system_tb.v”文件,打开,添加如下语句initial begin$dumpfile("aa.fsdb");$dumpvars;end以便仿真时,生成fsdb文件。

5.返回XPS界面,选择Simulation->Launch HDL Simulator,通过这种方式,打开了ModelSim6.5软件6.打开了ModelSim6.5软件,如下图所示7.打开Simulation文件夹中的system_setup.do文件,该文件中存放了系统生成的仿真脚本语句。

8.返回ModelSim6.5,在命令行下先输入“do system.do”命令。

9.输入如下命令“vsim -novopt -t ps D:/modeltech_6.5/win32/novas.dll -Lxilinxcorelib_ver -L secureip -L unisims_ver +notimingchecks system_tb glbl”理由(复制system_setup.do文件中第二条脚本语句”vsim -novopt -t ps -L xilinxcorelib_ver -L secureip -L unisims_ver +notimingchecks system_tb glbl”,注意到要仿真生成fsdb波形文件,所以在ps和-L前添加一条新的语句”D:/modeltech_6.5/win32/novas.dll”,要链接这个“novas.dll”动态链接文件。

FPGA开发-使用modelsim和debussy做rtl仿真

1 引言

做 ASIC 或者 FPGA 设计中,选择合适的软件工具,对工作的开展有很大的帮助,一杆 利器,绝对可以使工作事半功倍。在 Windows 环境下做 rtl 开发(Verilog/VHDL),modelsim 是主流的仿真工具。Modelsim 虽然仿真速度快,功能强大。但是在调试查看波形时,便利 性远比不上 debussy。 或许大家对 debussy 有些陌生, 但是说到 linux 下被广泛使用的 verdi, 应该熟悉。Debussy 就是 verdi 的 Windows 版本,都是思源科技 NOVAS 开发的波形调试工 具,具有相同的源码。Debussy 和 verdi 具有相同的操作界面,熟悉 verdi 的工程师,使用 debussy 很容易上手。

图 6 Debussy 导入设计

4.

选中”From File”选项卡,然后在左下方的窗口中,按路径依次双击文件夹并打开, 找到 nv_lab1.f 的位置, 这时右下侧窗口显示出 nv_lab.f 文件, 双击该文件, 把 nv_lab.f 添加到了 Design Files 列表中,如图 7。然后点击 OK 按钮,则在 Debussy 中打开 了 lab1 的设计。

图 8 Debussy 中打开波形窗口

图 9 打开的波形窗口

6.

在波形窗口菜单栏,点击 File Open,在弹出的对话框中按路径找到 sim_top.fsdb 文件,双击,打开波性文件,如图 10 所示。

图 10 找到并打开波性文件

7.

查看信号波形。如图 11 所示,切换到 debussy 主界面,通过左边的导航栏,找到 想查看的文件并双击打开, 在文件中选中需要观察的信号, 可以按住鼠标左键拖动, 选中多个新号,选中后按 ctrl+w 键,把信号添加到波形窗口中。

matlab和modelsim联合仿真(一)

基于VerilogHDL语言的FPGA设计课程作业学院:电子工程学院专业班级:集电11级3班姓名:朱潮勇学号:05116079作业题目:Matlab和modelsim联合仿真(一)完成日期:2013年11月20日一、设计要求 (2)二、规范说明 (2)三、顶层设计结构图 (2)四、模块详细设计 (3)1 功能说明 (3)2 端口定义 (3)3 设计激励代码 (3)4 matlab代码 (5)5 仿真结果 (6)五、结论和问题: (8)六、补充:..................................................................................................... 错误!未定义书签。

一、设计要求虽然Modelsim的功能非常强大,仿真的波形可以以多种形式进行显示,但是当涉及到数字信号处理的算法的仿真验证的时候,则显得有点不足。

而进行数字信号处理是Matlab 的强项,不但有大量的关于数字信号处理的函数,而且图形显示功能也很强大,所以在做数字信号处理算法的FPGA验证的时候借助Matlab会大大加快算法验证的速度。

关于matlab与modelsim联合仿真有两种,一是以matlab或者modelsim分别产生数据,保存为文本的形式在给modelsim或matlab来调用。

这是一种间接的联合仿真的方式。

二是用matlab的link for modelsim的功能,将两者联合。

后者的联合仿真功能更加强大。

此次实验将进行第一种联合仿真。

分为两个例子。

第一个例子说明如何用Matlab产生的数据用作Modelsim仿真。

第二个例子说明如何用modelsim产生数据用作matlab进行分析。

二、规范说明1. Matlab产生数据用作Modelsim仿真首先利用matlab产生一个周期256点8bit的正弦波数据,然后以16进制形式写入sin.txt文件,然后将产生的sin.txt文件复制到Modelsim的工程下,在Verilog文件中先定义一个8bit X 256数组,然后通过$readmemh命令,将文件中的数据读入2. Matlab对Modelsim仿真生成的数据进行分析Matlab对Modelsim仿真生成数据的处理也是通过文件读写实现的。

VHDLQuartusII调用Modelsim进行仿真

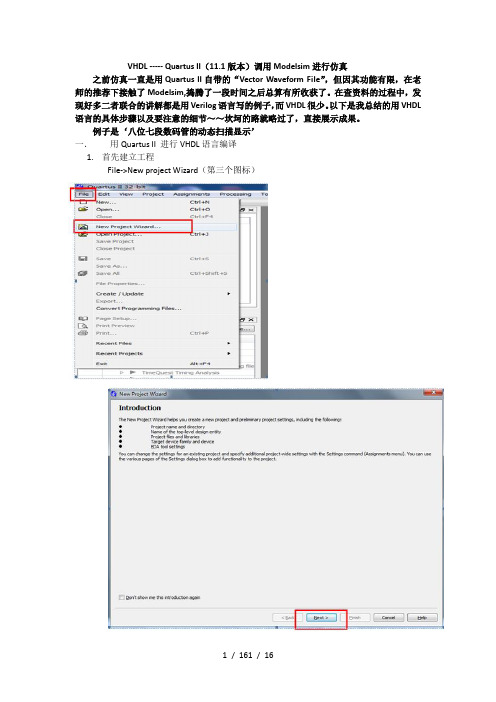

VHDL ----- Quartus II(11.1版本)调用Modelsim进行仿真之前仿真一直是用Quartus II自带的“Vector Waveform File”,但因其功能有限,在老师的推荐下接触了Modelsim,捣腾了一段时间之后总算有所收获了。

在查资料的过程中,发现好多二者联合的讲解都是用Verilog语言写的例子,而VHDL很少。

以下是我总结的用VHDL 语言的具体步骤以及要注意的细节~~坎坷的路就略过了,直接展示成果。

例子是‘八位七段数码管的动态扫描显示’一.用Quartus II 进行VHDL语言编译1.首先建立工程File->New project Wizard(第三个图标)填入所建工程的目录以及名称,注意稍后的源程序中实体名必须和这里的名称相同。

填好后单击finish,然后单击yes。

2.新建VHDL源程序文件File->New->VHDL File->OK将程序写进去(这里只讲步骤,不讲源程序的写法)注意:程序中的实体名必须和之前建工程时所命名的文件名相同!然后保存一下,不用改动,直接单击保存。

3.编译快捷键按钮在界面中上方的红色倒三角,显示编译成功之后关闭编译报告。

4.设备设置具体的实验器件根据提供的实验板设定Assignment->Device4.引脚分配Assignment->Pin Planner在Location下的方格中填入对应的硬件引脚,也是根据实验板而定6.引脚分配好之后再次编译一下,使分配的引脚起作用。

一、调用Modelsim1、设置仿真工具为Modelsim-alteraTool->Options->EDA Tool Options,在Modelsim-Altera后面的地址改为Modelsim-Altera.exe在你电脑中的位置,然后点击OK。

2、写TestBench文件,这里使用Quartus II生成的模板Processing->start->Start TestBench Template Writer,显示成功后关闭生成报告。

VHDL--QuartusII调用Modelsim进行仿真..doc

VHDL —— Quartus 11(11.1版本调用Modelsim进行仿真之前仿真一直是用Quartus II自带的“ Vector Waveform File但因其功能有限, 在老师的推荐下接触了Modelsim,捣腾了一段时间之后总算有所收获了。

在查资料的过程中,发现好多二者联合的讲解都是用Verilog语言写的例子,而VHDL很少。

以下是我总结的用VHDL语言的具体步骤以及要注意的细节~~坎坷的路就略过了,直接展示成果。

例子是八位七段数码管的动态扫描显示’一.用Quartus II进行VHDL语言编译1. 首先建立工程File->New project Wizard(第三个图标IntroductionT»w WUartf hctw OMt* ■ new preyed preAwurr prwfM rdj^rvg the <oi> i —Cf New Pt eel WLurdDirectory, Nd ok?, f op I eve! t fit Hy [ 1 ol 5JWwt • fw B^grtany »«ClDr 簞 2 *W prqgKl?U r'^Ww FMhag 厚叫<™« 电「申mjrdjQ口»**#1 4 ** e* tw >a^4r-*l *rtir r g W p轉W TIM « *» «*"*«** *B«C*r ・W enfliv*M»W ** 華«*h^ru填入所建工程的目录以及名称,注意稍后的源程序中实体名必须和这里的名称相同。

填好后单击finish撚后单击yes。

新建VHDL源程序文件File->New->VHDL File->OK将程序写进去(这里只讲步骤,不讲源程序的写法电|脚弧{} ts ts e 代%处处 » n 创1鑼a l =*二二imlibrary ieee;use ieee .std_logic_1164.all;use ieee.std_logic_unsigned.all; □ entity hexx is日 port (clk:xn std_logic;―时神信号输入key:in std_logic_vector (3 downto 0) ;■-四位信号若入 ag : out std^logic^vector (6 downto 0);―7段值号辕出 • sei:out std_logic_vector (2 downto 0)) ;-■数码管送择 end;22 sel<«ql; end if;1C 11 12□ architecture a of hexx is 曰begnn□process (elk)variable ql :std logic vector (2 downto 0):■R 000R ; 1€ n19 2C 21 曰曰卜beginif elk*event and clk«thenif ql-w lll H then ql:"000”; else qls-ql*1!*; end if ; 24电i nend process; 细(} tFS / ® 口创圖2 I r = we 789 10library ieee;use ieee.std IoqIc 1164.all;use ieee.5td_logic_unaignedeall: Bentity hexx is曰 port (clk:in std_logic;一时神(8号辐入key: m std logic tor (3 downto 0) ;一Qfifll 号输入sg:ouc std_logic_vector (6 downs 0); -」段(B 号•出 sellout scd_logxc_vector (2 downto 0));■■数冯苣送择 end; 11 Barchitectuxe a of hexx is 12 Qtegin三曰卜曰□process (cllc)variable ql:std_lo^ic —vector (2 downto 0): beginif elk 'event and clJc**!* then If ql —ill- then ql : —000": else •000- end if ; sel<*ql; end if; end process;-HD —曰 6 7 8 2 2 2 ••X•■“ ■八1 2 3 q注意:程序中的实体名必须和之前建工程时所命名的文件名相同!然后保存一下,不用改动,直接单击保存。

Modelsim仿真方法总结

Modelsim仿真方法总结第一篇:Modelsim 仿真方法总结Modelsim 仿真方法总结Modeling 仿真工具是Model公司开发的。

它支持Verilog、VHDL以及他们的混合仿真。

Modelsim各版本的使用方法大体一致,Modelsim仿真主要分为前仿真和后仿真。

下面来具体介绍modelsim 的仿真方法,涉及quartus-modelsim联合(使用)仿真的差异会特别提示。

前仿真与后仿真说明 1.1 前仿真前仿真也称为功能仿真、行为仿真。

旨在验证电路的功能是否符合设计要求,其特点是不考虑延迟(包括门延迟与线延迟),主要验证电路与理想情况是否一致。

前仿真需要用到RTL级代码(由源代码经过综合后产生)与T estbench。

1.2)后仿真后仿真也称为时序仿真或者布局布线仿真。

是指在电路已经映射到特定的工艺环境以后,综合考虑门延迟与线延迟的影响,验证电路在一定的时序条件下是否存在时序违规以及能否满足设计构想的过程。

需要用到的文件是——从布局布线结果中抽象出来的门级网表、testbench和后缀名为sdo或者sdf的标准时延文件。

注:扩展名为sdo和sdf的标准时延文件包含门延迟与实际布线延迟,能较好的反应芯片的实际工作情况。

二)modelsim仿真主要有以下几个步骤:(1)建立库并映射库到物理目录;(2)编译源代码(包括Testbench);(3)执行仿真;解释:①库:modelsim中有两类仿真库。

一种是工作库,默认名为work;另一种是资源库。

Work库中存放当前工程下所有已经编译过的文件,所以编译前一定要建立一个work库。

资源库存放work库中已经编译文件所要调用的资源,这样的资源可能有很多,它们被存放在不同的资源库内。

(例如要想对综合在cyclone芯片中的设计做后仿真,就需要有一个名为cyclone_ver的资源库。

)映射库用于将已经预编译好的文件所在目录映射为一个modelsim可识别的库。

Modelsim与debussy在FPGA仿真和debug中的应用

Modelsim与debussy在FPGA仿真和debug中的应⽤仿真是FPGA设计中的⼀个⾮常重要的环节,但很多朋友在做FPGA设计的过程中,却并没有意识到仿真的作⽤,也没有⼀个好的仿真流程来保证仿真验证的效果。

我们做仿真的⽬的是要通过仿真找到设计中潜在的问题并解决之,这就需要⼀个debug 的过程。

在这篇⽂章中,会讨论⼀下我对FPGA设计中仿真验证和debug的看法,也介绍⼀下modelsim+Debussy在仿真和debug中的应⽤流程。

记得在学校的时候,搭硬件系统要⽤到FPGA。

那时候没有任何FPGA设计的经验,也没有好的设计流程可以参考。

在做设计的时候,基本上是很随意的去写代码,很少顾及到甚⾄很基本的设计原则。

代码写好后,尽管有验证代码正确性的意识,但并没有成熟可靠的⽅法可以使⽤,基本上就是画⼀些简单的波形作为激励信号,通过开发软件⾃带的仿真⼯具,⼤概看⼀下输出的波形是不是正确。

这样做存在很多问题。

⾸先测试覆盖率⾮常的低,激励信号不可能做的很复杂,不可能涵盖所有需要验证的设计环节;再者就是要看被测设计的输出波形来检验设计是否正确,这样就需要⼤量的时间,效率很低。

在发现设计有问题的时候,检查设计代码,也⽤很原始的⼿段,⼀⾏⼀⾏的去查看,没有意识到或者说根本就不知道有⼯具软件可以来做trace。

更通常的验证⽅法就是在FPGA程序写好以后,综合出来,烧录到实际的系统中,在系统上直接验证。

但这种做法,效率低下且有问题的话,很难debug。

另外⽐较糟糕的是很难发现⼀些⽐较特殊的问题。

后来在公司的时候,做IC设计,公司有⽐较成熟和完善的设计流程。

主要⽤NC来做仿真,⽤debussy来做debug。

成熟和完善的设计流程带来的就是⽐较⾼的仿真的效率和⽐较⾼的覆盖率,我们在debug的时候,基于⽐较好的流程和⽅法,效率也⽐较⾼。

数年⼯作下来,让我建⽴起了⼀个基本的仿真验证的概念,这个时候,再回头看当初做FPGA设计的时候所遇到的问题,感触颇深。

debussy使用

前期问题解决方案1.altera后仿真问题系统内有宏模块库的仿真:需要添加库文件,路径\altera\80\quartus\eda\sim_lib220model.v :带有用户原语类型的Quartus自带的IP核的库文件altera_mf.v:Quartus自带的IP核的库文件cycloneii_atoms.v:相应系列的器件库,这个和你选择的器件有关,这一点一定要注意,如果你选择CycloneIII,那就选择III代的,不然会编译不通过,因为你在新建项目的时候已经确立了选用芯片的型号。

布局布线后仿真:首先在新建工程时要选择Modelsim作为仿真工具,在quartus II中编译后,在工程文件夹中生成一个:\simulation\modelsim文件夹,其中包括*.vo是仿真网表文件,可以用来代替设计文件*_modelsim.xrf是Quartus编译生成的信息文件;*_v.sdo是工程延时的文件将*.vo和*_v.sdo添加在工程中。

注意:后仿真可以不加载altera_mf.v,因为*.vo中包含了构造信息和参数。

总结:RTL级前仿真,如果有宏模块库必须加载altera_mf.v,不需要cycloneii_atoms.v 综合布局布线后仿真,必须对cycloneii_atoms.v进行编译,altera_mf.v和*.vo 任选一个即可。

2.debuss波形输入问题Debussy 介绍Debussy 是NOVAS Software, Inc(思源科技)发展的HDL Debug & Analy sis tool,这套软体主要不是用来跑模拟或看波形,它最强大的功能是:能够在HDL source code、schematic diagram、waveform、state bubble diagram 之间,即时做trace,协助工程师debug。

可能您会觉的:只要有simulator如ModelSim就可以做debug了,我何必再学这套软体呢? 其实Debussy v5.0以后的新版本,还提供了nLint -- check coding style & synthesizable,这蛮有用的,可以协助工程师了解如何写好co ding style,并养成习惯。

怎样使用Debussy+ModelSim快速查看前仿真波形

怎样使用Debussy+ModelSim快速查看前仿真波形作者:未知 时间:2010-06-18 08:22:23 来自:网络转载引子:ModelSim是HDL仿真软件,Debussy是波形查看软件;搭配使用,相当爽。

此处所谓快速查看前仿真波形仅为抛砖引玉,大家不要拘泥于此。

两款软件的功能都很强大,请自行研究。

注:本篇博文的软件环境为:Debussy 5.3v9 + Modelsim SE 6.5配置篇1 安装、和谐软件。

略。

2 拷贝文件..\Novas\Debussy\share\PLI\modelsim_pli\WINNT\novas.dll至文件夹..\modeltech_6.5\win32。

3 取消文件..\modeltech_6.5\modelsim.ini的只读属性后,打开。

找到view sourceprint?1; Veriuser = veriuser.sl替换为view sourceprint?1Veriuser = novas.dll保存;关闭;设为只读。

配置完,以后就一劳永逸了。

实战篇此处以一简单分频器为例。

文件地图如下:view sourceprint?1│ rtl.f2│ run.bat3│ sim.do4│5└─rtl6 clk_rst.v7 divider.v8 divider_tb.v1 编写欲仿真的HDL文件:RTL级代码+Testbench代码。

保存在文件夹rtl中。

(1)divider.v // RTL级代码模块view sourceprint?01`timescale1ns/10ps0203module divider(05 input i_rst_n,0607 output o_clk08);0910parameter U_DLY = 1;1112// log2(5) = 2.3219 <= 313reg[2:0] cnt_p; // 上升沿计数子1415// 5位上升沿计数器: 0 ~ 416// 4 = 5 - 117always@ (posedge i_clk, negedge i_rst_n)18begin19 if(!i_rst_n)20 cnt_p <= 0;21 else22 begin23 if(cnt_p == 4)24 cnt_p <= 0;25 else26 cnt_p <= #U_DLY cnt_p + 1'b1;27 end28end2930// log2(5) = 2.3219 <= 331reg[2:0] cnt_n; // 下降沿计数子3233// 5位下降沿计数器: 0 ~ 434// 4 = 5 - 135always@ (negedge i_clk, negedge i_rst_n)36begin37 if(!i_rst_n)39 else40 begin41 if(cnt_n == 4)42 cnt_n <= 0;43 else44 cnt_n <= #U_DLY cnt_n + 1'b1;45 end46end474849reg o_clk_p; // 上升沿时钟输出寄存器 5051// 输出上升沿时钟52// 0 ~ 2 ↑-> 153// (2+1) ~ 4 ↑-> 054// 2 = 5>>155// 4 = 5 - 156always@ (posedge i_clk, negedge i_rst_n)57begin58 if(!i_rst_n)59 o_clk_p <= 0;60 else61 begin62 if(cnt_p <= 2) // 2 = 5>>163 o_clk_p <= 1;64 else65 o_clk_p <= 0;66 end67end6869reg o_clk_n; // 下降沿时钟输出寄存器 7071// 输出下降沿时钟73// (2+1) ~ 4 ↓-> 074// 2 = 5>>175// 4 = 5 - 176always@ (negedge i_clk, negedge i_rst_n)77begin78 if(!i_rst_n)79 o_clk_n <= 0;80 else81 begin82 if(cnt_n <= 2) // 2 = 5>>183 o_clk_n <= 1;84 else85 o_clk_n <= 0;86 end87end8889assign o_clk = o_clk_n & o_clk_p; // 按位与(作用:掩码) 9091endmodule(2)clk_rst.v // Testbench的时钟及复位模块view sourceprint?01`timescale1ns/10ps0203module clk_rst(04 output reg i_clk,05 output reg i_rst_n06);0708parameter CLK_PERIOD = 20;09parameter MULT_RATIO = 10;10parameter RESET_TIME = MULT_RATIO * CLK_PERIOD + 1;1112initial13begin14 i_rst_n <= 1'b0;15 #RESET_TIME i_rst_n <= 1'b1;16end1718initial19begin20 i_clk <= 1'b0;21 forever22 #(CLK_PERIOD / 2) i_clk <= ~i_clk;23end2425endmodule把时钟及复位单独剥出来,便于移植到其他平台。

对于vhdl和modelsimse的理解

对于vhdl和modelsimse的理解modelsim 是一套功能强大的功能仿真软件,modelsim可以支持硬件描述语言vhdl 和verilog hdl 而且支持二者混合仿真,modelsim又分为se 与pe 我们用的se主要针对asic及高层fpga设计者使用其功能bipe要强大主要功能包含波形比较,高级数据流窗口,性能分析级高级代码覆盖率分析,支持vhdl,verilog hdl及混合仿真常用的一些vhdl开发软件一、max+plus2 软件说明altera公司的集成开发软件,但目前altera公司已停止开发max+plus2 专向quartus2平台二、quartus2 软件说明altera公司的集成开发软件,适合大规模fpga开发。

三、ise 软件说明xillinx公司的集成开发软件四、modelsim 软件说明mentor公司的子公司model tech出品的vhdl 和verilog hdl 仿真软件,使用比较复杂。

五、active hdl 软件说明aldec公司出品的vhdl和verilog hdl f 仿真软件,人机见面比较好使用简单。

以上为比较主流的vhdl开发软件还有debussy system generator等开发软件。

对vhdl语言的一些感受:综合这些天对vhdl语言的学习有以下一些总结:vhdl是一种硬件描述语言,有3类基本描述语句:顺序描述语句、并行描述语句、属性描述语句。

顺序描述语句只能出现在进程、过程、块、子程序中,例如if,case,等语句。

并行语句同时执行不因变成顺序而影响执行先后vhdl能并行处理的信号有:进程语句(process)端口映射语句(port map),generic等属性描述语句一般可以用来获取一般数值的邻值,极限值。

modelsim使用入门(VHDL_

modelsim使用实例(VHDL)标签: modelsim仿真testbench FPGA看了几天的modelsim以及如何在quartusII中调用,浏览了N个网页,尝试了N次,......终于初步完成。

下面是入门部分介绍。

modelsim是专业的仿真软件,仿真运行速度比同类的其他仿真软件都要快很多。

Quartus 自己都不再做仿真器了,普遍使用modelsim,自有其缘由。

这里用的是modelsim-altera(6.6d)版本,与quartus II 11.0搭配。

据说Altera公司推出的Quartus软件不同版本对应不同的modelsim,相互之间不兼容。

某些功能齐全的modelsim版本可以进行两种语言的混合编程, modelsim-altera只能支持一种语言进行编程(VHDL或者Verilog选其一)。

1、新建工程打开modelsim-->file-->new-->project 新建工程,输入工程名,文件存放路径后(不可直接放在某盘下,必须放入文件夹中),进入下一步。

在主体窗口下方出现project标签。

见下图。

2、新建文件--create new file:输入名称div10,选择语言VHDL --关闭对话框新的工程文件将会在工程窗口出现。

3、写入源程序(VHDL)双击div10.vhd,打开文本编辑器。

实例代码如下(一个十分频的VHDL源代码):library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity div10 is --实体要与工程名相同 port(clk :in std_logic;div :out std_logic );end div10;architecture behav of div10 issignal temp :std_logic:='0';signal count :std_logic_vector(2 downto 0):="000";beginprocess(clk)beginif(clk'event and clk='1') thenif(count="100") thencount<=(others=>'0');temp<=not temp;elsecount<=count+1;end if;end if;end process;div<=temp;end behav;4、写testbenchmodelsim单独使用时需要自己写testbench,输入时钟,给测试电路加以激励源以驱动电路。

ModelSim,synplify,ISE后仿真流程

ModelSim,synplify,ISE后仿真流程首先,我把我用到的软件说明一下。

如果你发现根据我的操作,你还是解决不了ModelSim 后仿真的问题,那就可能是软件版本的问题。

1, ModelSim Se 6.1b2, Synplify Pro 7.5.13, ISE 5.2i (这个是老了点)4, WindowsXP(这个应该没有多大的关系)还有就是我使用的是verilog,我想VHDL的方法与verilog是差不多的,最多也就是在建库方面有点差别而已。

下面的这些方法,是我这3天搞出来的。

当然也参考了一些文章。

如果谁有更方便的方法,欢迎指出来。

我的邮箱是vf1983cs@。

有空大家多交流。

一、为modelsim生成3个库。

首先,介绍一下这三个库。

Simprim_ver:用于布局布线后的仿真。

Unisim_ver :如果要做综合后的仿真,还要编译这个库。

Xilinxcorelib_ver:如果设计中调用了CoreGen产生的核,则还需要编译这个库。

我们要为modelsim生成的是标准库。

所谓的标准库就是modelsim运行后,会自动加载的库。

不过这方面我还不是很肯定。

因为我在后仿真时,还是要为仿真指定库的路径,不然modelsim找不到。

第一步:在modelsim环境下,新建工程,工程的路径与你想把库存储的路径一致。

第二步:新建库,库名起作simprim_ver。

我们首先就是要建的就是这个库。

第三步:在modelsim的命令栏上,打下如下命令:vlog -work simprim_ver d:/Xilinx/verilog/src/simprims/*.v其中的d:/Xilinx是我的Xilinx的安装路径,你把这个改成你的就行了。

以下凡是要根据自己系统环境改变的内容,我都会用绿色标出,并加一个下划线。

编译完之后,你会发现你的工程文件夹下出现了一个simprim文件夹,里面又有很多个文件夹。

如何使用debussy与modelsim做co-simulation(soc)(verilog)(v

如何使用D e b u s s y与M o d e l S i m做C o-S i m u l a t i o n(S O C)(V e r i l o g)(V H D L)(D e b u s s y)(M o d e l S i m)-CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN如何使用Debussy与ModelSim做Co-Simulation(SOC) (Verilog) (VHDL) (Debussy) (ModelSim)Abstract本文介绍如何使用Debussy与ModelSim做Co-Simulation,并使用Verilog、VHDL以及Verilog搭配VHDL交叉一起simulation。

Introduction使用环境:Debussy 5.4 v9 + ModelSim SE 6.3e我之前一直使用Debussy + NC-Verilog做simulation,Debussy (Verdi)可以说是HDL的Source Insight,是trace与debug的神兵利器,NC-Verilog也是Verilog simulator中速度最快的,可是最近因工作需要,拿到的一包code却是用Verilog写RTL,用VHDL写testbench,所以必须2种语言一起做simulation,我在NC-Verilog一直无法成功让两种语言一起simulation。

ModelSim虽然支援Verilog + VHDL co-simulation,但用惯Debussy的我还是无法忘怀其方便的trace code方式,所以若能让ModelSim也能dump出Debussy所需要的fsdb档案,这样就太完美了。

接下来会分4个方式讨论1.RTL与testbench皆使用Verilog2.RTL与testbench皆使用VHDL3.RTL使用VHDL,testbench使用Verilog4.RTL使用Verilog,testbench使用VHDL1.RTL与testbench皆使用VerilogStep 1:设定ModeSim使用Verilog PLI (因为testbench使用Verilog)将C:\Novas\Debussy\share\PLI\modelsim_pli\WINNT\novas.dll复制到C:\Modeltech_6.3e\win32\下修改C:\Modeltech_6.3e\modelsim.ini,将Veriuser部分修改成如下所示:; List of dynamically loaded objects for Verilog PLI applications; Veriuser = veriuser.sl; use by verilogVeriuser = novas.dll; use by vhdl; Veriuser = novas_fli.dll复制代码modelsim.ini是个read only档,要修改前记得修改其属性才能存档。

基于ModelSim的VHDL仿真技术研究与应用

基于ModelSim的VHDL仿真技术研究与应用作者:陈志刚来源:《电脑知识与技术》2019年第31期摘要:电子产品设计人员希望电子器件有更小的功耗、更强的功能、更低的价格,这就要求将更多的功能集成到单一的芯片。

随着计算机技术的快速发展,电子系统设计过程中广泛使用VHDL语言,首先利用VHDL完成电子产品的系统设计,再通过EDA软件对VHDL程序进行编译,产生SDF文件,ModelSim通过调用SDF文件,使用Testbench生成相应的测试激励。

以24进制计数为例,应用联合仿真,有效解决不同种类激励源的产生、验证自动化、平台移植等问题。

关键詞:ModelSim;QuartusII;Testbench;联合仿真中图分类号:TP391 文献标识码:A文章编号:1009-3044(2019)31-0286-021概述ModelSim是工业界广泛使用的仿真软件,由Me.or Graph-ics公司开发。

可以独立完成硬件描述语言代码的功能仿真,还能结合FPGA/CPLD开发软件进行时序仿真,得到包含信号传输时序的结果。

同时可以对System c、c语言进行调试与仿真,设计过程中可以采取许多灵活的手段来完成设计工作,大多数FP-GA/CPLD供应商软件都提供与ModelSim的接口。

Altera 公司的FPGA/CPLD器件的集成度小到300门,大到超过1000万门,可以用来设计、集成现有的大多数逻辑器件,直到实现单片系统,而且其开发系统简单易学、功能强大,学校计划执行非常好,占据了国内大量的市场,很多学校和公司都使用Ahera公司的产品进行设计和开发。

QuartuslI适合通过画波形图做初级的仿真,但从Quartusl110.0起不再提供对波形仿真的支挣”。

本文使用QuartusII13与ModelSim10软件进行联合仿真,通过高电平异步复位24进制计数器的设计说明二者联合仿真的方法。

224进制计数器的VHDL设计目前,常用的HDL硬件描述语言主要有VHDL和VerilogHDL,其中VerilogHDL语言具有简捷、高效、易学易用、功能强大等特点,适用于RTL级和门电路级的描述;VHDL语言主要用于描述数字系统的结构、行为、功能和接口。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1、编辑modelsim根目录下的modelsim.ini文件,将; Veriuser = veriuser.sl 更换为Veriuser = novas_fli.dll。

2、将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas_fli.dll 拷贝至

C:\Modeltech_6.1d\win32中

3、将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas.vhd拷贝至工程所在目录

4、打开modelsim,在工程所在目录新建一个novas的LIB,然后编译novas.vhd文件。

5、在testbentch中增加library novas;use novas.pkg.all;

6、在testbentch中添加

debussy_debug:process

begin

fsdbDumpfile("**.fsdb");

fsdbDumpvars(0,"顶层文件名(有testbench的话即为testbench名)");

wait;

end process debussy_debug;

7、编译整个工程,然后仿真

8、打开debussy, import design加载文件,设置好顶层文件,打开nWARE,加入信号即可为了更加方便的使用DEBUSSY,我们可以编写DO文件来达到这一目的:

1、先新建dc16_tca目录。

比如在E:/WORK/TEMP里新建该目录,把源程序都放在

dc16_tca/soure里头。

2、编写tca.do文件:

下面是以TCA为例说明一下这个步骤:

tca.do:

#start

#建立并编译novas库

vlib novas

vmap novas novas

vcom -work novas D:/WORK/temp/dc16_TCA/source/novas.vhd

#建立并编译work库

vlib work

vcom -work work d:/work/temp/dc16_tca/source/dc16_constant_def.vhd

vcom -work work d:/work/temp/dc16_tca/source/dc16_tca.vhd

vcom -work work d:/work/temp/dc16_tca/source/dc16_tca_tb.vhd

vsim dc16_tca_tb

#仿真运行时间

run 10000us

quit

#end

3、然后在dos界面先进入到dc16_tca目录里,比如E:/WORK/TEMP/dc16_tca

然后再输入>c:\modeltech_6.1b\win32/vsim -c -do tca.do

这里假设modelsim装在C盘

个人感觉modelsim的仿真速度用DO文件的方式比用modelsim的GUI方式要快很多。

而且每次只要输入一次命令就可以产生.FSDB文件,真的不错。

各位可以体会一下。

4、打开debussy再打开nWARE加入*.*.fedb文件即可看到波形大功告成!!。