线性稳压器件(Linear Regulators):工作原理及补偿

线性稳压器的工作原理及应用

线性稳压器的工作原理及应用第一个需要考虑的因素便是确定预期输出电压。

最为简单的线性稳压器拥有一个固定的输出电压范围,其由和图 1 所示R1/R2 网络相类似的内部连接确定。

可调稳压器可能会有四个引脚:Vin、Vout、接地引脚和调节引脚。

调节引脚是用来调节电压设置电阻。

图1 基本的线性稳压器三端可调稳压器的输出电压如图2 所示图2 三端可调稳压器并由下列关系式设定:1.25 V 为电压参考值。

分子和分母均除以R1 可以得出:这就是本系列第一篇文章(第 1 部分最基本的构建块运算放大器)中所建立起来的非反相运算放大器(op amp) 传输函数。

我们通常用输入电源电压(线性)或输出电流需求(负载)改变时其保持规定输出电压的表现来衡量稳压器的动态性能,即对静态变化和瞬态变化的响应。

我们通常是在最大负载电流下规定线性调整率(line regulation),而负载调整率的规定则可能是在一个或多个线性电压条件下完成的。

当输入未得到调节时,可能会存在一定叠加于DC 之上的电源线频率AC,即输入纹波,应从输出中将其去除。

另一个动态性能变量是输出噪声。

通过增加稳压器输出端的滤波器电容一般可以降低输入纹波和输出噪声,但是会延长瞬态恢复时间。

线性稳压器的运行依赖于一个内部增益级。

为了防止该增益级出现振荡,通常会需要一个最小输出滤波器电容(请参见图 1 中的C2)。

一个输入滤波器电容(请参见图 1 中的C1)将有助于稳压器服务于瞬态负载,尤其是在稳压器远离电源时更需要这样一个输入滤波器电容。

许多稳压器都不容许存在反向电压。

如果输出电容被充电至输出电压,同时输入短路至接地,那么稳压器将出现反向电压,并且在所有电路获得放电以前稳压器都会锁闭在某种未知状态中。

这种故障状态可能会引起稳压器自毁。

为。

线性稳压器原理

线性稳压器原理线性稳压器是一种常见的电子元件,它在电路中起着稳定输出电压的作用。

其工作原理是通过将输入电压进行稳定,以确保输出电压始终保持在设定的数值范围内。

在本文中,我们将深入探讨线性稳压器的原理,以及其在电子电路中的应用。

首先,让我们来了解一下线性稳压器的基本结构。

线性稳压器通常由三个主要部分组成,输入端、控制电路和输出端。

输入端接收来自电源的不稳定电压,控制电路对输入电压进行稳定处理,最终输出端提供稳定的电压给负载使用。

控制电路中通常包含一个参考电压源和一个误差放大器,用于对输入电压进行比较和调节,以确保输出电压的稳定性。

其次,让我们来详细了解线性稳压器的工作原理。

当输入电压发生变化时,控制电路会通过负反馈机制对输出电压进行调节,以使其保持在设定的稳定数值范围内。

这种负反馈机制可以有效地抑制输入电压的波动,从而确保输出电压的稳定性。

此外,线性稳压器还通过将多余的电压转化为热量的方式来实现稳压,这也是其常见的缺点之一,因为这会导致功耗增加和效率降低。

接下来,让我们来探讨线性稳压器在电子电路中的应用。

线性稳压器广泛应用于各种电子设备中,如电源适配器、电池充电器、稳压电源等。

在这些应用中,线性稳压器可以提供稳定的电压输出,以确保电子设备的正常运行。

此外,线性稳压器还常用于模拟电路中,因为其输出电压稳定性较高,能够满足对电压精度要求较高的应用场景。

总结一下,线性稳压器是一种常见的电子元件,其工作原理是通过负反馈机制对输入电压进行稳定处理,以确保输出电压的稳定性。

在电子电路中,线性稳压器广泛应用于各种电子设备中,能够提供稳定的电压输出,满足不同应用场景的需求。

然而,线性稳压器也存在一些缺点,如功耗增加和效率降低,因此在实际应用中需要综合考虑其优缺点,选择合适的稳压器类型。

通过本文的介绍,相信读者对线性稳压器的原理和应用有了更深入的了解。

在实际应用中,我们需要根据具体的需求和场景选择合适的线性稳压器,以确保电子设备的正常运行和稳定性能。

电子电路中线性稳压器的作用及原理解析

电子电路中线性稳压器的作用及原理解析线性稳压器是广泛应用于电子电路中的一种电源管理器件,其作用主要是将不稳定的直流电源(输入)转换为稳定的输出电压,并且输出电压与负载电流几乎无关。

线性稳压器能够提供相对稳定、纹波较小的电源电压给电路中的各个组件使用,从而保证了电子设备、家用电器、计算机等的正常运行。

一、线性稳压器的基本工作原理线性稳压器的基本工作原理是将输入电压经过调节电路进行调整,并去除掉噪声,然后再传递到稳定电压的输出端口。

其中,调节电路通常由参考电压源和误差放大器两部分组成。

参考电压源提供一个固定的参考电压,误差放大器输出一个误差电压,通过对这两个信号的比较,产生一个控制信号来调节晶体管或调节管的导通状态,使得输出电压保持稳定。

具体来说,在线性稳压器中,调节管的导通状态决定了输出电压与输入电压之间的电压差,而误差放大器就是基于这种电压差来产生误差信号的放大器。

如果输出电压低于设定的标准电压值,如果调节器被要求提高电压,则控制电压将导致晶体管或调节管导通的时间更长,输出电压就会增加。

反之,如果输出电压高于标准电压值,则减小导通时间,输出电压就会减少。

二、线性稳压器的特点线性稳压器具有以下几个特点:线性稳压器能够提供稳定、纹波小的电源电压,能够满足各种电路对电源质量的要求。

线性稳压器的输出电流几乎不受负载电流的影响,因此稳定性高。

线性稳压器具有较低的输出电阻和噪声,使得其在一些对信噪比要求较高的应用场景下得到广泛应用。

线性稳压器调节方便,可靠性高,适用于大多数功率要求不高的电子电路。

线性稳压器的成本较低,相对于其他电源管理器件来说,具有较高的性价比。

虽然线性稳压器有很多优点,但是也存在一些缺点,如功率消耗大、效率低、温升大等。

因此,在一些需要低噪声、低纹波、高效率、高稳定性的场合,可以考虑采用其他类型的电源管理器件。

三、常见的线性稳压器常见的线性稳压器有78xx系列、79xx系列和LM317。

line regulation test原理

line regulation test原理

线性稳压器(Linear Regulator)是一种电源管理器件,用于提供稳定的输出电压。

线性稳压器的线性调节测试(Line Regulation Test)是为了验证其在输入电压变化时输出电压的稳定性。

该测试通常通过改变输入电压,然后测量输出电压的变化来进行。

线性稳压器的原理是通过将输入电压通过一个可变阻抗调节元件(通常是晶体管)来维持输出电压的稳定。

在线性调节测试中,通常保持负载电流不变,改变输入电压,并观察输出电压的变化。

测试步骤包括:

1. 设定初始条件:将负载电流设定为所需值,输入电压设定为额定值。

2. 改变输入电压:通过增加或减小输入电压的方式,改变线性稳压器的输入。

这可以模拟输入电源的波动或变化。

3. 测量输出电压:在改变输入电压后,测量输出电压的变化。

这样可以确定线性稳压器对输入电压变化的响应。

4. 记录结果:记录不同输入电压下的输出电压值,并计算输出电压与输入电压之间的差异。

这个差异即为线性调节的指标。

线性调节测试的结果通常以百分比或毫伏数表示,表示输出电压相对于输入电压的变化程度。

线性稳压器的线性调节性能越好,输出电压在不同输入电压下的变化就越小,表现为更好的线性调节性能。

这对于保持电子系统中各个部分的稳定性非常重要,尤其是在输入电源变化较大的环境中。

线性稳压器

线性稳压器线性稳压器(LinearRegulator)使用在其线性区域内运行的晶体管或FET,从应用的输入电压中减去超额的电压,产生经过调整的输出电压。

其产品均采纳小型封装,具有杰出的性能,而且供给热过载保护、安全限流等增值特性,关断模式还能大幅降低功耗。

目录原理特点比较原理线性稳压器的突出优点是具有最低的本钱,最低的噪声和最低的静态电流。

它的外围器件也很少,通常只有一两个旁路电容。

新型线性稳压器可实现以下指标:30μV输出噪声、60dBPSRR、6μA静态电流及100mV的压差。

线性稳压器能够实现这些特性的重要原因在于内部调整管采纳了P沟道场效应管,而不是通常线性稳压器中的PNP晶体管。

P沟道的场效应管不需要基极电流驱动,所以大大降低了器件自身的电流;另一方面,在采纳PNP管的结构中,为了防止PNP晶体管进入饱和状态降低输出本领,必须保证较大的输入输出压差;而P沟道场效应管的压差大概等于输出电流与其导通电阻的乘积,微小的导通电阻使其压差特别低。

当系统中输入电压和输出电压接近时,线性稳压器是最好的选择,可实现很高的效率。

所以在将锂离子电池电压转换为3V电压的应用中大多选用线性稳压器,尽管电池最后放电能量的百分之十没有使用,但是线性稳压器依旧能够在低噪声结构中供给较长的电池寿命。

特点所谓的抗短路本领要求,是指在相关料子的短路条件下,稳压器不损坏。

稳压器的抗短路本领包含经受短路的耐热本领和经受短路的动稳定本领两个方面。

压差和接地电流值定了后就可确定稳压器适用的设备类型。

五大主流线性稳压器每个都具有不同的旁路元件(passelement和独特性能,电压差和接地电流值重要由线性稳压器的旁路元件(passelement确定。

分别适合不同的设备使用。

即使没有输出电容也相当稳定,它比较适合电压差较高的设备使用,规范NPN稳压器的优点是具有约等于PNP晶体管基极电流的稳定接地电流。

但较高的压差使得这种稳压器不适合很多嵌入式设备使用。

线性稳压器的工作原理

线性稳压器的工作原理线性稳压器是一种电子设备,主要用于电源系统中,将不稳定的输入电压转化为稳定的输出电压。

其工作原理是通过使用负反馈控制技术,将不稳定的输入电压调整并稳定到设定的输出电压。

以下是线性稳压器的工作原理的详细解释。

在开始解释之前,需要先了解两个概念:基准电压和误差放大器。

基准电压是一个与输入电压无关的准确值,用来设定输出电压的期望值。

误差放大器是一个负反馈放大器,用于监测输出电压并与基准电压进行比较,产生一个反馈信号。

工作原理如下:1.输入电压通过输入电压端进入线性稳压器。

这个电压通常会有一定的波动,可能会受到电网电压的变化、负载的变化等因素的影响。

2.输入电压经过输入电压端进入制动器。

制动器中的一个电阻网络会将输入电压调整到与基准电压相匹配的水平。

3.调整后的电压通过制动器进入误差放大器。

误差放大器监测输出电压与基准电压之间的差异。

如果输出电压低于期望值,误差放大器会产生一个较大的正反馈信号。

相反,如果输出电压高于期望值,误差放大器会产生一个较大的负反馈信号。

4.误差放大器输出的反馈信号通过负载电流,通过一个驱动电路传递给制动器。

这个反馈信号会告诉制动器调整电阻网络的程度,以调整输出电压。

5.制动器根据误差放大器的反馈信号,调整电阻网络的电阻值。

如果输出电压低于期望值,制动器会减小电阻值,增加输出电压。

相反,如果输出电压高于期望值,制动器会增加电阻值,降低输出电压。

6.输出电压从制动器经过输出电压端输出给负载。

这个输出电压是根据误差放大器的调整和制动器的调整来稳定到期望值的。

值得注意的是,线性稳压器通过使用一个线性的调整器(制动器)将不稳定的输入电压调整为稳定的输出电压,因此整个过程会有一定的功耗。

功耗的大小与输入输出电压差以及负载电流有关。

因此,在选择线性稳压器时,需要综合考虑功耗、热效应和电源效率等因素。

总结而言,线性稳压器通过负反馈控制技术,利用误差放大器监测输出电压与基准电压之间的差异,并通过制动器调整输入电压,从而实现将不稳定的输入电压转化为稳定的输出电压的功能。

线性稳压器的工作原理及比较

线性稳压器的工作原理及比较一、线性稳压器的工作原理线性稳压器是一种电子元件,用于将输入电压稳定在一个固定的输出电压上。

它通过调整电路中的阻抗来实现电压的稳定。

线性稳压器的工作原理可以分为三个主要步骤:输入电压的采样、误差放大和反馈控制。

1. 输入电压采样:线性稳压器首先对输入电压进行采样,以获取实际电压值。

这通常通过一个电阻分压网络来实现,其中一个电阻连接到输入电压,另一个电阻连接到地。

2. 误差放大:采样后的电压与参考电压进行比较,产生一个误差信号。

这个误差信号被放大器放大,以便能够控制输出电压。

3. 反馈控制:放大后的误差信号通过一个反馈回路传送给稳压器的控制端。

这个信号与稳压器内部的参考电压进行比较,产生一个控制信号。

稳压器根据控制信号调整输出电压,使其保持在一个稳定的水平上。

二、线性稳压器的比较线性稳压器有很多不同的类型,每种类型都有其特点和适用范围。

以下是几种常见的线性稳压器及其比较:1. 简单线性稳压器(Series Linear Regulator,简称SLR):简单线性稳压器是最基本的线性稳压器类型,由一个功率晶体管和一个反馈电路组成。

它的工作原理简单,成本低廉,但效率相对较低。

它适用于低功率应用,如模拟电路和传感器。

2. 低压差线性稳压器(Low Dropout Regulator,简称LDO):低压差线性稳压器是一种特殊的线性稳压器,它能够在输入电压与输出电压之间保持很小的压差。

这意味着它可以在输入电压接近输出电压的情况下正常工作,提供更高的效率。

LDO适用于需要较高输出电流和较低输入电压的应用。

3. 开关稳压器(Switching Regulator):开关稳压器是一种比较先进的稳压器类型,它通过开关元件(如晶体管)来控制电路中的能量流动。

开关稳压器的效率较高,能够提供更大的输出功率。

然而,它的设计和调试相对复杂,成本也较高。

开关稳压器适用于高功率和高效率要求的应用,如电源管理和电动车辆。

线性稳压器原理与补偿理论(中文)LinearRegulatorsTheoryofOperation

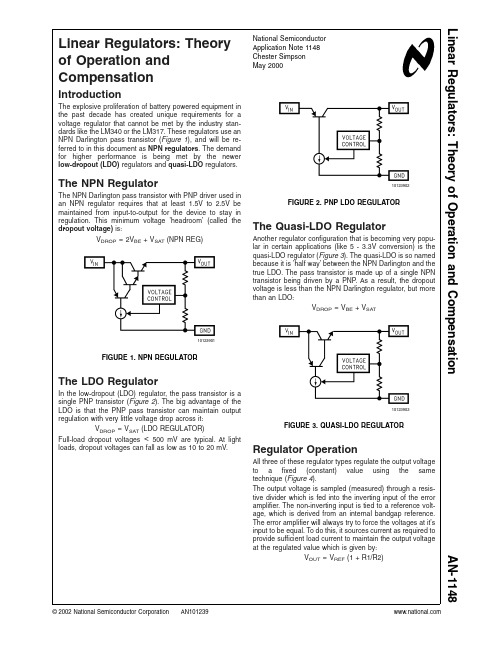

低压差稳压器工作原理低压差稳压器工作原理随着便携式设备(电池供电)在过去十年间的快速增长,象原来的业界标准LM340 和LM317 这样的稳压器件已经无法满足新的需要。

这些稳压器使用NPN 达林顿管,在本文中称其为NPN 稳压器(NPN regulators)。

预期更高性能的稳压器件已经由新型的低压差(Low-dropout)稳压器(LDO)和准LDO稳压器(quasi-LDO)实现了。

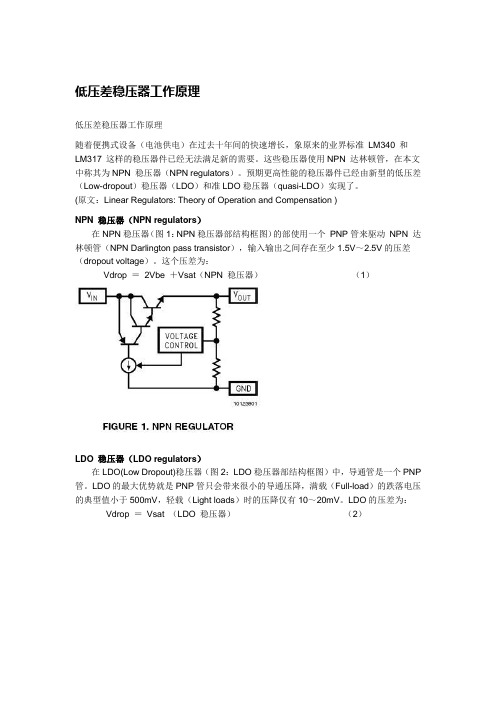

(原文:Linear Regulators: Theory of Operation and Compensation )NPN 稳压器(NPN regulators)在NPN稳压器(图1:NPN稳压器部结构框图)的部使用一个PNP管来驱动NPN 达林顿管(NPN Darlington pass transistor),输入输出之间存在至少1.5V~2.5V的压差(dropout voltage)。

这个压差为:Vdrop =2Vbe +Vsat(NPN 稳压器)(1)LDO 稳压器(LDO regulators)在LDO(Low Dropout)稳压器(图2:LDO稳压器部结构框图)中,导通管是一个PNP 管。

LDO的最大优势就是PNP管只会带来很小的导通压降,满载(Full-load)的跌落电压的典型值小于500mV,轻载(Light loads)时的压降仅有10~20mV。

LDO的压差为:Vdrop =Vsat (LDO 稳压器)(2)准LDO 稳压器(Quasi-LDO regulators)准LDO(Quasi-LDO)稳压器(图3:准LDO 稳压器部结构框图)已经广泛应用于某些场合,例如:5V到3.3V 转换器。

准LDO介于NPN 稳压器和LDO 稳压器之间而得名,导通管是由单个PNP 管来驱动单个NPN 管。

因此,它的跌落压降介于NPN稳压器和LDO之间:Vdrop =Vbe +Vsat (3)稳压器的工作原理(Regulator Operation)所有的稳压器,都利用了相同的技术实现输出电压的稳定(图4:稳压器工作原理图)。

线性稳压电路原理

线性稳压电路原理

线性稳压电路是一种常用的电路,用于将输入电压稳定成输出电压。

其基本原理是利用稳压元件(如稳压二极管、稳压三极管等)的特性,通过负反馈调节,使输出电压保持稳定。

具体来说,线性稳压电路的工作过程如下:

1. 输入电压经过变压器或电源转换电路得到一个合适的直流电压。

2. 输入电压经过滤波电路得到一个平滑的直流电压。

滤波电路一般由电容器和电感器组成,用于去除输入电压中的纹波。

3. 平滑的直流电压进入稳压电路。

稳压电路中,稳压元件连接在负载电路的输出端,起到稳压的作用。

4. 当输入电压发生变化时,稳压电路通过负反馈将这种变化传递给稳压元件,稳压元件的特性使得其阻抗发生变化,以抵消输入电压变化带来的影响,从而保持输出电压稳定。

5. 输出电压经过滤波电路后,供给负载电路使用。

线性稳压电路的特点是简单可靠、稳定性好。

它适用于对输出电压精度要求较高的场合,如通信设备、精密仪器等。

但是,线性稳压电路的效率较低,因为输入电压的降压过程中会有功率损耗,导致能量的浪费。

此外,稳压元件在工作过程中会产生一定的热量,需要进行散热处理。

稳压器的原理

稳压器的原理一、稳压器的定义与作用稳压器是一种电子元件,用于稳定电压或电流的输出。

它可以将不稳定的输入电压或电流转化为稳定输出,有效保护电路中的其他元件,使其正常工作。

稳压器广泛应用于各种电子设备中,如电源供应、通信设备、计算机等。

二、线性稳压器的工作原理线性稳压器是稳压器的一种常见类型,下面将详细介绍线性稳压器的工作原理。

1. 输入滤波与整流输入滤波电路用于去除输入电压中的杂散噪声和电涌,保证稳压器的稳定工作。

整流电路将交流电压转换为直流电压。

2. 调节管调节管是线性稳压器的核心元件,它通过调节输入和输出之间的电压差来稳定输出电压。

调节管的基本工作原理是通过调节电阻来实现电压稳定。

3. 参考电压源参考电压源是提供调节管参考电压的一种电路,通常采用电压比较器、反馈电路等元件组成。

参考电压源可以根据需要输出不同的稳定电压。

4. 调节回路调节回路是稳压器的反馈回路,用于感知输出电压的变化并调节输入电压,使得输出电压保持稳定。

调节回路通常由比较器、反馈电路、放大器等组成。

三、稳压器的优缺点分析稳压器虽然在电子设备中有着广泛的应用,但也存在一些优缺点,下面将进行简要的分析。

1. 优点•稳定输出:稳压器能够将输入电压或电流转化为稳定的输出,确保其他电子元件正常工作。

•低噪声:稳压器的滤波电路能够有效去除杂散噪声,提供干净的电源。

•易于控制:稳压器的输出电压可以通过调节参考电压源来控制,方便实现电压调节。

2. 缺点•低效率:线性稳压器由于通过电阻调节电压,会有一定功耗,效率较低。

•体积较大:线性稳压器的实现通常需要较多的电子元件,体积较大。

•不适用大功率应用:线性稳压器的功率受限,不适用于大功率应用,容易发热。

四、不同类型稳压器的比较除了线性稳压器,还有许多其他类型的稳压器,如开关稳压器、开环反馈稳压器等。

下面将比较不同类型稳压器的特点。

1. 线性稳压器•优点:稳定输出、低噪声、易于控制。

•缺点:低效率、体积较大、不适用大功率应用。

电源管理芯片中稳压器regulator工作原理

电源管理芯片中稳压器regulator工作原理

稳压器(regulator)是电源管理芯片中的一种关键元件,用于将不稳定的输入电压转换为稳定的输出电压。

其工作原理主要由参考电压源、错误放大器和功率输出级三部分构成。

1. 参考电压源:稳压器的参考电压源提供一个稳定的参考电压,通常为固定的电压值。

这个参考电压可以由内部电路产生,也可以由外部提供。

2. 错误放大器:错误放大器主要起到误差检测和调节的作用。

它将输出电压与参考电压进行比较,然后根据误差信号调整控制元件,使输出电压保持在设定的稳定值附近。

3. 功率输出级:功率输出级是稳压器中的功率放大器。

根据错误放大器的控制电压,它调整输出线路的阻抗,以实现输入电压到输出电压的转换。

简单来说,当输入电压发生变化时,稳压器会不断检测输出电压与参考电压之间的差异,并通过调整控制元件来实现输出电压的稳定。

这样可以保证电路中其他部件在稳定电压下正常运行,提高系统的稳定性和可靠性。

线性稳压器的工作原理及比较

线性稳压器的工作原理及比较线性稳压器是一种常见的电子元件,用于稳定直流电源的输出电压。

它通过调整输入电压的大小来保持输出电压的稳定性。

本文将详细介绍线性稳压器的工作原理,并与其他类型的稳压器进行比较。

一、线性稳压器的工作原理线性稳压器的核心部件是三极管。

它通过将输入电压分配给负载和稳压器来实现电压稳定。

下面是线性稳压器的工作原理:1. 输入电压:线性稳压器的输入电压通常来自交流电源或其他电源,它可以是固定的或可调节的。

2. 变压器:输入电压首先通过变压器降压,以适应稳压器的需求。

3. 整流器:变压器输出的交流电压通过整流器转换为直流电压。

4. 滤波器:直流电压通过滤波器去除电压中的脉动。

5. 三极管:滤波后的直流电压输入三极管,三极管通过调整电流来稳定输出电压。

6. 负载:输出电压连接到负载上,以提供所需的电源电压。

7. 反馈回路:线性稳压器中的反馈回路用于检测输出电压,并将信息反馈给三极管,以调整输入电压以保持输出电压的稳定性。

二、线性稳压器与其他稳压器的比较线性稳压器相对于其他类型的稳压器具有一些优点和缺点。

下面是与开关稳压器的比较:1. 效率:线性稳压器的效率较低,因为它通过将多余的电压转化为热量来稳定输出电压。

而开关稳压器通过开关电路来调整输入电压,因此效率较高。

2. 稳定性:线性稳压器的输出电压非常稳定,具有较低的噪声和纹波。

开关稳压器的输出电压可能存在一定的纹波和噪声。

3. 成本:线性稳压器的成本相对较低,因为它的设计相对简单。

开关稳压器的设计更加复杂,因此成本较高。

4. 可靠性:线性稳压器具有较高的可靠性,因为它没有复杂的开关电路。

开关稳压器可能由于开关元件的故障而导致系统失效。

5. 外部组件:线性稳压器不需要额外的外部元件,因为它的设计已经包含了所需的电路。

开关稳压器可能需要外部元件来实现稳定输出电压。

综上所述,线性稳压器是一种常见的稳压器类型,它通过调整输入电压来实现稳定输出电压。

线性稳压器的工作原理及比较

线性稳压器的工作原理及比较

线性稳压器是一种常见的电源稳压器件,其工作原理是通过调整输入电压和输出电压之间的差值来实现稳定输出电压。

具体来说,线性稳压器通过使用一个可变电阻(调节器)来调整输入电压,并将调整后的电压传递给负载,以保持输出电压的稳定。

线性稳压器的比较主要包括以下几个方面:

1. 效率:线性稳压器的效率相对较低,通常在50%到70%之间。

这是因为线性稳压器通过将多余的电压转化为热量来实现稳定输出,因此会有较大的功耗损失。

2. 稳定性:线性稳压器的输出电压稳定性较好,可以在较大负载变化时保持较稳定的输出电压。

然而,由于其工作原理的限制,线性稳压器对输入电压的波动比较敏感,因此对输入电压的稳定性要求较高。

3. 噪声:线性稳压器的输出电压通常具有较低的噪声水平,可以满足对噪声要求较高的应用。

4. 成本:线性稳压器相对于其他稳压器件来说成本较低,因为其结构简单,不需要复杂的控制电路。

总的来说,线性稳压器适用于对输出电压稳定性要求较高、负载变化较大、噪声要求较高的应用场景。

然而,由于其效率较低,对输入电压稳定性要求较高,因此在一些功耗较大、电压波动较大的应用中可能不适用。

regulator工作原理

regulator工作原理Regulator工作原理引言:Regulator是一种常见的电子元件,广泛应用于各种电路中。

它的主要作用是稳定电压或电流,保证电路的正常工作。

本文将详细介绍Regulator的工作原理及其应用。

一、Regulator的基本原理Regulator的工作原理基于负反馈控制的原理。

当输入电压或电流发生变化时,Regulator通过调节输出电压或电流来抵消这种变化,从而实现电路的稳定工作。

二、线性稳压器1. 线性稳压器的工作原理线性稳压器是Regulator的一种常见类型。

它通过在稳压管中产生稳定的参考电压,再通过调节电阻或开关管的导通程度来控制输出电压。

当输出电压高于设定值时,稳压管会减小导通程度,从而降低输出电压;当输出电压低于设定值时,稳压管会增加导通程度,从而提高输出电压。

2. 线性稳压器的特点线性稳压器具有简单、稳定可靠、成本低等特点。

然而,由于稳压管的导通损耗较大,线性稳压器的效率较低。

此外,线性稳压器对输入电压的波动比较敏感,调节速度较慢。

三、开关稳压器1. 开关稳压器的工作原理开关稳压器是另一种常见的Regulator类型。

它通过周期性开关管的导通和截止来控制输出电压。

当输出电压高于设定值时,开关管截止,输出电压降低;当输出电压低于设定值时,开关管导通,输出电压增加。

2. 开关稳压器的特点开关稳压器具有高效率、调节速度快的特点。

开关管的导通损耗较小,因此效率较高。

此外,开关稳压器对输入电压的波动不敏感,能够在较短的时间内调节输出电压。

四、Regulator的应用领域1. 电源系统Regulator在电源系统中起到稳定电压和电流的作用,保证各种电子设备正常工作。

例如,手机充电器中的稳压芯片能够将市电的高压转换为合适的电压给手机充电。

2. 通信设备通信设备对电压和电流的要求比较严格,Regulator在其中起到重要作用。

例如,在基站中,Regulator能够稳定供电,保证信号传输的稳定性和可靠性。

简述稳压器的工作原理和作用

简述稳压器的工作原理和作用一、稳压器的概述稳压器是一种电子电路,用于将不稳定的直流电压转换为稳定的直流电压。

它通常由一个可变电阻和一个固定电阻组成,并通过反馈控制来维持输出电压的恒定。

二、线性稳压器的工作原理线性稳压器是最常见的一种稳压器,它通过将输入电压降低到所需输出电压来实现稳定输出。

具体来说,线性稳压器包括三个主要部分:输入滤波器、调节元件和输出滤波器。

输入滤波器用于过滤输入信号中的高频噪声和杂波。

调节元件通常是一个晶体管或MOSFET,用于调整输入信号以达到所需输出电压。

输出滤波器用于过滤输出信号中的残余噪声。

在线性稳压器中,负载变化会导致输出电压发生变化。

为了解决这个问题,反馈控制回路被引入到线性稳压器中。

当负载发生变化时,反馈回路会检测到这个变化并相应地改变调节元件的状态以保持输出电压稳定。

三、开关稳压器的工作原理开关稳压器是另一种常见的稳压器,它通过周期性地将输入电压切换到输出电路来实现稳定输出。

开关稳压器通常包括一个开关管、一个电感和一个电容。

在工作时,当开关管导通时,电感会储存能量。

当开关管断开时,电容会释放能量并提供给负载使用。

通过改变开关管的导通时间和断开时间,可以调整输出电压的大小。

与线性稳压器相比,开关稳压器具有更高的效率和更小的尺寸。

然而,由于其复杂性和噪声问题,它们不如线性稳压器易于设计和实现。

四、稳压器的应用稳压器广泛应用于各种领域,包括消费类电子、通信、计算机、医疗设备等。

其中最常见的应用是在直流电源中使用它们以提供恒定的输出电压。

此外,在模拟信号处理中也经常使用线性稳压器以提供恒定的参考电平。

在音频放大器中也需要使用高质量的线性稳压器以保证音频信号不受干扰。

总之,稳压器是现代电子电路中不可或缺的组成部分。

它们通过提供稳定的电源以及恒定的参考电平,保证了电路的正常运行和高质量的信号处理。

线性稳压电路工作原理

线性稳压电路工作原理

线性稳压电路是一种常用的电路设计,用于在输入电压有波动的情况下提供稳定的输出电压。

它的工作原理基于负反馈控制,通过不断调整电路的参数,使得输出电压保持在期望的数值范围内。

线性稳压电路通常由三个基本组成部分构成:一个电源输入,一个稳压器和一个负载。

电源输入为稳压器提供电能。

稳压器则根据反馈电路中的反馈信号和参考电压来调整电路的参数,在输入电压波动时调整输出电压以保持稳定。

负载则连接在稳压器的输出端,用于消耗电流和提取所需的电能。

稳压器的核心是一个反馈回路,常见的反馈方式有电压反馈和电流反馈。

电压反馈中,输出电压与参考电压之间的差异被放大并馈回到稳压器中,根据差异的方向进行调整。

电流反馈则是根据输出电流与参考电流之间的差异来进行调整。

无论哪种方式,稳压器都会根据反馈信号调整其电路参数,如改变电阻、电流或者电容值,以降低差异并保持输出电压稳定。

线性稳压电路的工作原理可以通过一个简单的反馈控制回路来理解。

当输入电压波动时,输出电压也会随之变化。

反馈回路通过将部分输出电压馈回到稳压器中,使其能够感知并响应输出电压的变化。

稳压器则通过调整自身的参数来抵消输入电压的变化,以确保输出电压保持在稳定水平。

总的来说,线性稳压电路通过负反馈控制来保持输出电压稳定。

通过调整电路参数以对抗输入电压的变化,它能够在输入电压波动时提供稳定的输出电压,满足各种电子设备的需求。

线性集成稳压电路工作原理

线性集成稳压电路工作原理

用三极管作为调整元件的一种具体稳压电路如图所示

先假设负载电阻RL不变,电网电压升高引起Ui升高,于是 输出电压U0升高。 引起输出电压U0的升高会引发一系列变化: U0↑→Ub2↑→Ube2↑→Ic2↑→Uc2↓→Ub1↓→U0↓可见电 网电压U0升高引起的U0的升高受到了抑制。

线性集成稳压电路工作原理

用三极管作为调整元件的一种具体稳压电路如图所示

同样可以说明电网电压下降引起U0下降是如何受到抑制的。 引起输出电压U0的下降会引发一系列变化: U0↓→Ub2↓→Ube2↓→Ic2↓→Uc2↑→Ub1↑→U0↑,可见 电网电压U0下降引起的U0的下降受到了抑制。

线性集成稳压电路工作原理

的目的。例如,将电位器RD作为调整元 件,让它和负载RL相串联,通过电位器 的不断调节就可以达到稳压的目的,如

图所示。

U0 Ui UD

调节电位器上的压降可以调控负载上的电压。

线性集成稳压电路工作原理

1.2 集成稳压电路工作原理 用电位器实现稳压的原理如下:如果由于某种原因,负载 RL两端的电压U0下降而偏低,则可以将电位器电阻RP1调小, 从而电位器两端压降UD减小,根据式(1),U0便会增加; 反之,当U0过大时,应将电位器电阻RD调大,因此电位器 两端压降UD随之变大,U0就会小下来。

模拟电子技术

线性集成稳压电路工作原理

1.1 交流供电式稳压电源的组成和工作原理 线性集成稳压电路主要用于组成交流供电式稳压电源。 由线性集成稳压电路组成的交流供电式稳压电源如图所示, 它由变压器、整流电路、滤波电路和集成稳压电路组成。

直到目前为止,稳压电源中被集成化的只是稳压电路部分。 滤波部分是一个大容量的电容器,变压器包含大容量电感和 铁心,都还无法集成化,整流电路部分也都没有制作在集成 稳压电路之中。

线性稳压器:工作原理与补偿(英文)

Linear Regulators:Theory of Operation and CompensationIntroductionThe explosive proliferation of battery powered equipment in the past decade has created unique requirements for a voltage regulator that cannot be met by the industry stan-dards like the LM340or the LM317.These regulators use an NPN Darlington pass transistor (Figure 1),and will be re-ferred to in this document as NPN regulators .The demand for higher performance is being met by the newer low-dropout (LDO)regulators and quasi-LDO regulators.The NPN RegulatorThe NPN Darlington pass transistor with PNP driver used in an NPN regulator requires that at least 1.5V to 2.5V be maintained from input-to-output for the device to stay in regulation.This minimum voltage ’headroom’(called the dropout voltage)is:V DROP =2V BE +V SAT (NPN REG)The LDO RegulatorIn the low-dropout (LDO)regulator,the pass transistor is a single PNP transistor (Figure 2).The big advantage of the LDO is that the PNP pass transistor can maintain output regulation with very little voltage drop across it:V DROP =V SAT (LDO REGULATOR)Full-load dropout voltages <500mV are typical.At light loads,dropout voltages can fall as low as 10to 20mV.The Quasi-LDO RegulatorAnother regulator configuration that is becoming very popu-lar in certain applications (like 5-3.3V conversion)is the quasi-LDO regulator (Figure 3).The quasi-LDO is so named because it is ’half way’between the NPN Darlington and the true LDO.The pass transistor is made up of a single NPN transistor being driven by a PNP .As a result,the dropout voltage is less than the NPN Darlington regulator,but more than an LDO:V DROP =V BE +V SATRegulator OperationAll three of these regulator types regulate the output voltage to a fixed (constant)value using the same technique (Figure 4).The output voltage is sampled (measured)through a resis-tive divider which is fed into the inverting input of the error amplifier.The non-inverting input is tied to a reference volt-age,which is derived from an internal bandgap reference.The error amplifier will always try to force the voltages at it’s input to be equal.To do this,it sources current as required to provide sufficient load current to maintain the output voltage at the regulated value which is given by:V OUT =V REF (1+R1/R2)National Semiconductor Application Note 1148Chester Simpson May 2000Linear Regulators:Theory of Operation and CompensationAN-1148©2002National Semiconductor Corporation Regulator Operation(Continued)Performance ComparisonThe primary differences in performance between the NPN,LDO,and quasi-LDO are in the parameters of dropout voltage (previously defined)and ground pin current .For this analysis,we will define ground pin current (I GND )as shown in Figure 4,neglecting the small IC bias currents which also flow to ground.It can be seen that the value of I GND is the load current I L divided by the gain of the pass transistor.The high gain of the Darlington in an NPN regulator means it requires very little drive to source I L ,so it’s ground pin current is very low (typically a few mA).The quasi-LDO also has very good performance,with products like National’s LM1085being able to source more than 3A with less than 10mA of ground pin current.The ground pin current of an LDO is typically much higher.At full load current,PNP beta values of 15-20are not unusual,which means the LDO ground pin current can be as high as 7%of the load current.A big advantage of NPN regulators is that they are uncondi-tionally stable (most require no external capacitors).An LDO does require at least one external capacitor on the output to reduce the loop bandwidth and provide some positive phase shift.Quasi-LDOs typically require some output capacitance,but much less than an LDO and with less restrictive limits on its performance characteristics.Feedback and Loop StabilityAll voltage regulators use a feedback loop to hold the output voltage constant.The feedback signal experiences changes in both gain and phase as it goes through the loop,and the amount of phase shift which has occurred at the unity gain (0dB)frequency determines stability.BODE PLOTSUnderstanding stability requires the use of Bode Plots ,which show the loop gain (in dB )plotted as a function of frequency (Figure 5).Loop gain and associated terms are defined in the next sections.Loop gain can be measured on a network analyzer,which injects a low-level sine wave into the feedback path and then measures the gain response while the frequency of the signal is swept from DC up to the frequency where the gain drops well below 0dB.Bode plots are convenient tools because they contain all the information necessary to determine if a closed-loop system is stable.However,decoding the information contained in a Bode plot requires understanding the key elements:loop gain,phase margin,poles and zeros .LOOP GAINEvery closed-loop system has a characteristic called loop gain .In this analysis of voltage regulators,loop gain will be defined as the magnitude of the voltage gain that the feed-back signal experiences as it travels through the loop.The block diagram of the LDO in Figure 2will be redrawn to illustrate this concept (Figure 6).A transformer is used to inject an AC signal into the feedback path between points ’A’and ’B’.Using this transformer,a small-signal sine wave is used to ’modulate’the feedback signal.The AC voltages at ’A’and ’B’are measured and used to calculate loop gain.The loop gain is defined as the ratio of the two voltages:Loop Gain =V A /V Bit is important to note that the signal starting at the V B point has a phase shift introduced into it as it travels through the loop (eventually arriving at the V A point).The amount of phase shift is critical in determining stability.FEEDBACKFeedback is used in all voltage regulators to hold the output voltage constant.The output voltage is sampled through a resistive divider (Figure 6),and that signal is fed back to one 2Feedback and Loop Stability (Continued)input of the error amplifier.Since the other input of the error amplifier is tied to a reference voltage,the error amplifier will supply current as required to the pass transistor to keep the regulated output at the correct DC voltage.It is important to note that for a stable loop,negative feed-back must be used.Negative feedback(sometimes called degenerative feedback)is opposite in polarity to the source signal(see Figure7).Because it is opposite in polarity with the source,negative feedback will always cause a response by the loop which opposes any change at the output.This means that if the output voltage tries to rise(or fall),the loop will respond to force it back to the nominal value.Positive Feedback occurs when the feedback signal has the same polarity as the source signal.In this case,the loop responds in the same direction as any change which occurs at the output.This is clearly unstable,since it does not cancel out changes in output voltage,but amplifies them. It should be obvious that no one would intentionally design positive feedback into the loop of a linear regulator,but negative feedback becomes positive feedback if it expe-riences a phase shift of180˚.PHASE SHIFTPhase shift is defined as the total amount of phase change (referred to the starting point)that is introduced into the feedback signal as it goes around the loop.Phase shift (expressed in degrees)is most often measured using a network analyzer.Ideal negative feedback is180˚out of phase wit the source(Figure8),so its’starting point’is at−180˚.This’180˚’offsetcan also be seen in Figure7,as the negative feedbackwaveforms are exactly one half cycle shifted with respect toeach other.It can be seen that starting at−180˚,an additional phaseshift of180˚(positive or negative)brings the signal back tozero,which is in phase with the source signal and wouldcause the loop to be unstable.PHASE MARGINPhase margin is defined as the difference(in degrees)between the total phase shift of the feedback signal and−180˚at the frequency where the loop gain is equal to0dB(unity gain).A stable loop typically needs at least20˚ofphase margin.Phase shift and phase margin can be calculated using thepoles and zeros present in the Bode plot.POLESA pole(Figure9)is defined as a point where the slope of thegain curve changes by−20dB/decade(with reference to theslope of the curve prior to the pole).Note that the effect is 3Feedback and Loop Stability(Continued)additive:each additional pole will increase the negative slope by the factor ’n’x (−20dB/decade),where ’n’is the number of additional poles.The phase shift introduced by a single pole is frequency dependent,varying from 0to −90˚(with a phase shift added by a pole (frequency).The most important point is that nearly all of the phase shift added by a pole (or zero)occurs within the frequency range one decade above and one decade below the pole (or zero)frequency.NOTE:a single pole can add only −90˚of total phase shift,so at least two poles are needed to reach −180˚(which is where instability can occur).ZEROSA zero (Figure 10)is defined as a point where the gain changes by +20dB/decade (with respect to the slope prior to the zero).As before,the change in slope is additive with additional zeros.The phase shift introduced by a zero varies from 0to +90˚,with a +45˚shift occurring at the frequency of the zero.The most important thing to observe about a zero is that it is an ’anti-pole’,which is to say its effects on gain and phase are exactly the opposite of a pole.This is why zeros are intentionally added to the feedback loops of LDO regulators:they can cancel out of the effect of one of the poles that would cause instability if left uncom-pensated.BODE PLOT ANALYSISA Bode plot which contains three poles and one zero (Figure 11)will be analyzed for gain and phase margin.The DC gain is assumed to be 80dB,with the first pole occurring at 100Hz.At that frequency,the slope of the gain curve changes to −20dB/decade.The zero at 1kHz changes the slope back to 0dB/decade until the second pole at 10kHz,where the gain curve slope returns to −20dB/decade.The third and final pole at 100kHz changes the gain slope to the final value of −40dB/decade.It can also be seen that the unity-gain (0dB)crossover frequency is 1MHz.The 0dB frequency is sometimes referred to as the loop bandwidth .The plot of the phase shift shows how the various poles and zeros contribute their effect on the feedback signal.To pro-duce this plot,the phase shift at each frequency point was calculated based upon summing the contributions of every pole and zero at that frequency.The phase shift at any frequency ’f’which is caused by a pole frequency located at frequency ’f p ’can be calculated from:Pole Phase Shift =−arctan (f/f p )The phase shift resulting from a zero located at frequency ’f z ’can be found using:Zero Phase Shift =arctan (f/f z )Is this loop stable?To answer that question,we need only the phase shift at 0dB (which is 1MHz in this case).Finding this does not require complex calculations:As stated in the previous sections,a pole or zero contributes nearly its full phase shift in the frequency range one decade above and below the center frequency of the pole (or zero). 4Feedback and Loop Stability (Continued)Therefore,the first two poles and the first zero contributetheir full phase shifts of−180˚to+90˚,respectively,resulting in a net phase shift of−90˚.The final pole is exactly one decade below the0dB ing the formula for Pole Phase Shift,this pole will contribute−84˚of phase shift@1MHz.Added to the−90˚from the two previous poles and the zero,the total phase shift is−174˚(which means the phase margin is6˚).This loop would either oscillate or ring severely.NPN Regulator CompensationThe pass transistor of the NPN regulator(see Figure1)is connected in a circuit configuration known as common col-lector.An important characteristic of all common collector circuits is low output impedance,which means the pole from the power stage that it places in the loop gain occurs at a very high frequency.The NPN regulator uses a technique called dominant pole compensation because it has no inherent low-frequency poles.In this case,a capacitor is built into the IC which places a pole in the loop gain at a low frequency(Figure12). This dominant pole(shown as P1)for a typical NPN regu-lator is set at about100Hz.The100Hz pole causes the gain to decrease at a rate of−20dB/decade until the second pole (P2)which is located at3MHz.At that point,the slope of thegain plot changes to−20dB/decade.The frequency of P2is primarily due to the NPN power transistor and associated drive circuitry,so it is sometimes referred to as the power pole.Since P2occurs at a fre-quency where the loop gain is−10dB,its contribution to phase shift at the0dB frequency(1MHz)will be small.To determine stability,it only requires that the phase margin at the0dB frequency be calculated:The first pole(P1)will contribute−90˚of phase shift,but the second pole(P2)will add only−18˚of negative phase shift@ 1MHz(0dB).This means the total phase shift@0dB is −108˚,which yields a phase margin of72˚(which is very stable).It should also be noted that simple observation would clearly show this loop is stable,since reaching−180˚of phase shift (the point of instability)would require the full contribution of−90˚(each)from both poles,and P2is too high in frequencyto contribute significant phase shift at the0dB frequency(1MHz).LDO Regulator CompensationThe PNP transistor in an LDO regulator(Figure2)is con-nected in a configuration called common emitter,which hasa higher output impedance than the common collector con-figuration in the NPN regulator.This adds an additionallow-frequency pole whose frequency is dependent bothon load resistance and output capacitance.The fre-quency of this pole(which will be designated P L for loadpole)is found from:f(P L)=1/(2πx R LOAD x C OUT)The presence of the frequency-variable load pole P L meansthat the simple dominant pole compensation method used inthe NPN regulator will not work in an LDO unless additionalcompensation is added.To illustrate why this is true,the loopgain of a5V/50mA LDO regulator will be illustrated usingthese assumptions:At maximum load current,the load pole(P L)occurs at afrequency given by:P L=1/(2πx R LOAD x C OUT)=1/(2πx100x10−5)=160Hz.The internal compensation will be assumed to add a fixedpole(P1)at1kHz.A500kHz power pole(which will be designated P PWR)ispresent due to the PNP power transistor and driver.The DC gain is assumed to be80dB.R L=100Ω(which is the value at maximum load current)C OUT=10µF.using the conditions stated above,a Bode plot(Figure13)isdrawn.It is immediately obvious that this loop is not stable:the two poles P L and P1will each contribute−90˚of phaseshift to reach−180˚at the0dB frequency(which is about40kHz in this example).To reduce the negative phase shift(and prevent oscillations),a zero must be added to the loop.A zero can contribute asmuch as+90˚of positive phase shift,which will cancel outthe effects of one of the two low frequency poles. 5LDO Regulator Compensation(Continued)Nearly all monolithic LDO regulators require that this zero beadded to the loop,and they derive it from a characteristicthat is inherent in the output capacitor:equivalent seriesresistance(usually referred to ESR).LDO Compensation Using ESREquivalent series resistance(ESR)is a characteristic that ispresent in every capacitor.It can be modeled electrically asa resistance that is placed in series with the capacitor(Fig-ure14).The ESR of the output capacitor puts a zero in the loop gainwhich can be used to reduce excess negative phase shift.The frequency where the zero occurs is directly related tothe value of the ESR and amount of output capacitance:F ZERO=1/(2πx C OUT x ESR)Using the example in the previous section(Bode plot shownin Figure13),we will assume that the value of C OUT=10µFand the output capacitor ESR=1Ω,which means a zero willoccur at16kHz.Figure15shows how this added zero will change the un-stable plot into a stable one:The bandwidth of the loop is increased so that the0dBcrossover frequency moves form30kHz to100kHz.The zero adds a total of+81˚positive phase shift at100kHz(the0dB frequency).This will reduce the negative phaseshift caused by the poles P L and P1.Since the pole P PWR is located at500kHz,it adds only−11˚of phase shift at100kHz.Summing all poles and zeros,the total phase shift at0dB isnow−110˚.This corresponds to a phase margin of+70˚,which is extremely stable.This illustrates how an output capacitor with the correctvalue of ESR can generate a zero that stabilizes an LDO.ESR and StabilityVirtually all LDO regulators require that the ESR of theoutput capacitor be within a set range to assure regulatorstability.The LDO manufacturer provides a set of curves which definethe boundaries of the stable region,plotted as a function ofload current(Figure16).To explain why these boundaries exist,the effects of low andhigh ESR on phase margin will be illustrated using theexample previously developed.HIGH ESRUsing the examples developed in the previous sections,wewill change the conditions and assume the ESR of the10µFoutput capacitor is increased to20Ω.This will decrease thefrequency of the zero to800Hz(Figure17).Reducing thefrequency of the zero causes the loop bandwidth to increase,moving the0dB crossover frequency from100kHz to2MHz.This increase bandwidth means that the pole P PWR occurs ata gain value of+20dB(compared to−10dB in Figure14).Analyzing the plot(Figure17)for phase margin,it can beassumed that the zero cancels out either P1or P L.Thismeans the loop has a two-pole response with the low fre-quency pole contributing−90˚of phase shift and the highfrequency pole P PWR contributing about−76˚of phase shift. 6ESR and Stability(Continued)Although this appears to leave a phase margin of14˚(which might be stable),bench test data shows that ESR values> 10Ωusually cause instability because of phase shifts con-tributed by other high-frequency poles which are not shown in this simplified model.LOW ESRAn output capacitor with a very low ESR value can cause oscillations for a different reason.Continuing the example developed in the previous section, we will now reduce the ESR of the10µF output capacitor to 50mΩ,increasing the frequency of the zero to320kHz (Figure18).When the plot is analyzed for phase margin,no calculations are required to see that it is unstable.The−90˚phase shift from each of the two poles P1and P L will produce a total phase shift of−180˚at the0dB fre-quency.For this system to be stable,a zero is needed that would provide positive phase shift before the0dB point.However, since the zero is at320kHz,it’s too far out to do any good (and is cancelled out by P PWR).Output Capacitor SelectionSince the output capacitor is the user’s tool for compensat-ing a monolithic LDO regulator,it must be selected verycarefully.Most cases of oscillations in LDO applications arecaused by the ESR of the output capacitor being too high ortoo low.When selecting an output capacitor for an LDO,a solidtantalum capacitor is usually the best choice(except forparts specifically designed for ceramic capacitors like theLP2985).Tests performed on an AVX 4.7µF Tantalumshowed an ESR of1.3Ω@25˚C,a value that is almostperfectly centered in the stable region(Figure16).Also very important,the ESR of the AVX capacitor variedless than2:1over the temperature range of−40˚C to+125˚C.Aluminium electrolytic capacitors are notorious forexhibiting an exponential increase in ESR at cold tempera-tures,and are not suitable for use as an LDO output capaci-tor.It must be noted that large(≥1µF)ceramic capacitorstypically have very low ESR values(<20mΩ),and willcause most LDO regulators to oscillate if connected directlyto the output(except the LP2985).A ceramic capacitor canbe used if some external resistance is added in series with itto increase the effective rge value ceramics alsohave a poor tempco(typically Z5U)which means the capaci-tance will drop in half as the temperature is increased ordecreased to the operating limits.Quasi-LDO CompensationWhen evaluating the quasi-LDO regulator(Figure3)for sta-bility and compensation,it has some of the electrical char-acteristics of both the LDO and NPN regulator.Since thequasi-LDO uses an NPN pass device,it is in thecommon-collector configuration which means it’s output de-vice node(emitter)looks like a relatively low impedance.However,because of the base of the NPN is being drivenfrom a high-impedance PNP current source,the regulatoroutput impedance of a quasi-LDO is not as low as the NPNregulator with an NPN Darlington pass device(but is muchlower than a true LDO which drives the regulator output offthe collector of a PNP).This means that the troublesome power pole of a quasi-LDOis at a lower frequency than the NPN regulator,so somecompensation(output capacitance)is required to make aquasi-LDO stable.Of course,the pole is at a much higherfrequency than the LDO,so the quasi-LDO requires lesscapacitance and the ESR is not as critical.For example,the LM1085quasi-LDO rated for3A of loadcurrent requires only10µF of Tantalum output capacitanceto assure complete stability over all line and load conditions.No ESR graphs are given,since the value of ESR is notcritical as it is in an LDO.Low-ESR Specific LDO’sNational Semiconductor does have LDO regulators like theLP2985and LP2989which are specifically designed to workwith extremely low ESR capacitors like surface-mount ce- 7Low-ESR Specific LDO’s(Continued)ramics.This type of capacitor can have ESR values as low as 5-10m Ω,which will cause most typical LDO regulators to oscillate (as demonstrated in Figure 18.To make the LP2985stable with such low ESR values,an internal zero is built in which takes the place of the ESR zero previously provided by the Tantalum output capacitor.The effect of this is to shift the stable ESR range downward.A typical LDO with no added internal zero might be stable ESR range from about 100m Ωto 5Ω(well suited for Tantalums but not ceramics).The stable range for the LP2985extends down to 3m Ω,and has an upper limit of about 500m Ωso it can be used with ceramics.The reason the upper limit is moved down can be under-stood by referring to Figure 15.As previously stated,the zero is now built into the LDO,so the ESR zero resulting from the output capacitor must stay at a high enough frequency that it does not cause the bandwidth to get too wide where high frequency poles would add enough phase shift to produce oscillations.The FET AdvantageAn LDO regulator can be built using a P-FET as the pass transistor (see Figure 19).To see why using a P-FET LDO would be advantageous,it should be noted that all of the base current required by the power transistor in a PNP LDO (Figure 2)flows out of the ground pin and back to the negative input voltage return.Therefore,this base drive current is drawn from the input supply but does not drive the load,so it generates wasted power that must be dissipated within the LDO regulator:PWR (Base Drive)=V IN X I BASE The amount of base current required to drive the PNP is equal to the load current divided by the beta (gain)of the PNP ,and beta may be as low as 15-20(at rated load current)in some PNP LDO regulators.The wasted power generated by this base drive current is very undesirable (especially in battery-powered applications).Using a P-FET solves this problem,since the Gate drive is very small.Another advantage of the P-FET LDO is that the dropout voltage can be made very small by adjusting the ON-resistance of the FET.For monolithic regulators,FET power transistors typically will give a lower ON-resistance per unit area than bipolar ONP devices.This allows making higher current regulators in smaller packages.LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body,or (b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.National Semiconductor Corporation AmericasEmail:support@National Semiconductor EuropeFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)6995086208English Tel:+44(0)8702402171Français Tel:+33(0)141918790National Semiconductor Asia Pacific Customer Response Group Tel:65-2544466Fax:65-2504466Email:ap.support@National Semiconductor Japan Ltd.Tel:81-3-5639-7560Fax:81-3-5639-7507National does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ǖ ցOQO!V DROP =2V BE +V SAT (NPN REG)MEP!MEP!V DROP =V BE +V SATV OUT =V REF (1+R1/R2)101239011.NPN3. LDO101239022.PNP LDO10123903ӷ 1148Chester Simpson 2000 5ǖ ցAN-1148©2002National Semiconductor Corporation AN101239www āā Ԣ Lj LM340 LM317 Ք ă և NPN DŽ 1DžLj Ԩ NPN ă DŽLDO Dž LDO DŽquasi-LDO Dž ăāā NPN և PNP NPN Lj Lj ԍ 1.5V 2.5V DŽdropout voltage Džă " "DŽ Dž ǖāā DŽ 5V 3.3V Dž LDO DŽ 3Džă LDO NPN LDO Lj PNP NPN ă Lj NPN LDO ǖāā , DŽ , 4Džăāā DŽ DžLj Lj IC և ă ă Lj ԍ ǖāā LDO DŽ Dž Lj PNP DŽ 2DžăLDO PNP LjLDO ǖāāāāāāVdrop ǙVsat DŽLDO Džāā 500mV Lj 10mV 20mV ă!) *!Բհ101239044.101239055. հ6.10123906A N -1148www 2āāNPN LjLDO LDO ՚ DŽ Dž ă ă Ս Lj IGND DŽ 4DžLjժ IC ă LjIGND IL ăāā NPN Lj Lj IL ă IGND Lj ӯ mA ă LDO Lj ӷ LM1085 10mA , 3A ăLjLDO Բ ă LjPNP ˸ ӯ 15ċ20ă LDO ӯ 7%ăāāNPN DŽ Džă LDO և , ց ă ӯ LDO Lj LDO Ljժ ăāā ԍ ă ՎLj DŽ0dB Dž ăāā հ Lj DŽ dB Dž DŽ 5Džă ă, հLj 0dB ăāāհ Ս Lj Ԉ ԿՂ ă Lj Ԉ հ ǖ Lj Ă ăāā Կ ă Lj ă Lj 2 LDO DŽ 6DžăāāՎ "A"Ă"B" ă Վ Lj հ " " ă A ĂB Lj ă Բ ǖLoop Gain ǙVa /Vbāā Lj Vb Lj Lj Va ă ăāā Lj ă DŽ 6DžLjժ Lj Lj ԍ ă!) *101239077. 101239088.AN-11483āā Lj Ղ ă Lj Lj DŽ 7Džăāā Lj Վă Lj Վ DŽ Վ DžLj Վ Lj ăāā ă Lj Վ ă փ Ljփ ՎLj Վ ăāā Ljփ ă 180Ń Lj Վ ăāā Վ DŽ Džă Lj Lj ă 180ŃDŽ 8DžLj lj180Ńă 7 180Ń Lj հ ӷ ăāā Lj lj180Ń Lj 180Ń DŽ DžLj Lj Lj փ ăāā DŽ DžLj 0dBDŽ Dž Lj lj180Ń ă ӯ 20Ń ăāā հ Ă ăāā ԥ ) * lj31eC0 Ԡ Վ DŽ :Džă ;!!) *1012390910123911101239109. /10. /11. հA N -1148www 4āā "n"ġDŽlj20dB/ Ԡ Dž Lj "n" ăāā Lj 0 lj90ŃDŽ Džă DŽ Dž Ԡ ăāā ǖ lj90Ń Lj lj180ŃDŽ փ Džăāā ԥ ( ) +20dB/ Ԡ Վ DŽ 10Džă Lj Վ ăāā 0 LJ90ŃLj LJ45Ń ă " "Lj ăāā1kHz Վ 0dB/ Ԡ Lj 10kHz Վ lj20dB/ Ԡ ăāā 100kHz Վ lj40dB/ Ԡ ăāā 11 DŽ0dB Dž 1MHz ă0dB ԥ ăāā Ă փ ք ă Lj ք Ă ă DŽf Dž Lj ǖāāāā Ǚljarctan(f/fp)DŽf Dž Lj ǖāāāā Ǚarctan(f/fz)āā Ǜ Lj փՂ Lj 0d B DŽ 1MHz Džăāā , ( ) Ԡ ăāā LDO : , փ ց փ ăհāā Ԉ հ DŽ 11Dž ăāā 80dB Lj 100Hz ă Վ lj20dB/ Ԡ ă!) *NPN ցLDO ց1012391212.NPN հ1012391313. ց LDO հAN-1148www 5āā Lj lj180Ń LJ90ŃLj Վ lj90Ńăāā Ԡ 0dB ă Lj lj84Ń DŽ 1MHz Džă lj90Ń Lj և lj174ŃDŽ 6ŃDžă Lj փ ԍ Lj ăāāNPN DŽ 1Dž ă Lj ăāā NPN Lj ց ă և Lj DŽ 12DžăāāNPN P1 Lj ӯ 100Hz ă100Hz lj20dB/ Ԡ , 3MHz DŽP2Džă P2 Lj lj20dB/ Ԡ ăP2 NPN Lj ă LjP2 lj10dB Lj DŽ0dB Dž DŽ1MHz Dž ăāā Lj 0dB ăāā DŽP1Dž lj90Ń Lj DŽP2Dž lj18Ń DŽ1MHz Džă 0dB lj108ŃLj 72ŃLj ăāā , ,lj180Ń DŽփ Dž ! ևlj90Ń , P2 Lj 0dB DŽ1MHz Dž ăāāLDO PNP ă ă ă ԥ Lj P L ă ǖf(PL)Ǚ1/(2̆ġR load ġCout)āā LjLDO փ ց ă ? 5V/50mA LDO :Lj DŽP L Dž :PL Ǚ1/(2̆ġR load ġCout)Ǚ1/(2̆ġ100ġ10-5)Ǚ160Hzāā և ց 1kHz (P1)ă PNP Lj 500kHz DŽP PWR Džăāā 80dB, R L Ǚ100ˮLj Cout Ǚ10uF ăāā հ DŽ 13Džăāā փ ă P L P1 ՚ lj90Ń ă 0dB DŽ 40kHz DžLj lj180Ń DŽ DžLj Ղ ă LJ90Ń LjLDO ց DŽ DžESRց LDOESRESR1012391414. ESR1012391515. ESR LDO1012391616.LDO ESRAN-11486āā Lj LDOă ӯDŽ ESRDž ăāā LDO ESRLj ԍ ăLDOESRDŽ 16DžLj ăāā LjESR ăāā Lj 10uFESR 20ˮă 800HzDŽ 17Džă LjDŽ0dBDž 100kHz 2MHzăP PWR DŽ Բ15Džă 17հ LjP1 PL Ljă lj90Ńlj76Ń P PWR ăāā DŽESRDžԨ ă DŽ 14Džăāā ESR Ljă DŽFzeroDžESR ǖFzeroǙ1/(2̆ġCoutġESR)āā DŽ 13DžLj CoutǙ10uFLj ESRǙ1ˮă 16kHză 15 հ փăāā Lj DŽ0dBDž30kHz 100kHză 100kHzLJ81Ń ă P L P1 ăP pwr 500kHz Lj 100kHz lj11Ńă Ă Lj0dBlj110Ńă LJ70Ń LjăESRLDO ăESR ( )ESRLDO ց·ESR LDO1012391717. ESR հ1012391818. ESR փAN-1148www 7āā 14Ń ( ), Lj ESR ǚ10ˮ Lj DŽ Dž փ ăāā Lj ց LDO Lj Ղ ă Ԩ LDO ESR ăāā LDO Lj DŽ LDO Lj ǖLP2985Džă AVX 4.7uF , 25ņ ESR 1.3ˮLj DŽ 16Džăāā LjAVX ESR lj40ņ LJ125ņ Վ 2:1ă ESR Lj փ LDO ăāāՂ DŽĽ1uF Dž ESR DŽǘ20m ˮDžLj DŽ LP2985 Dž LDO ă ESR ă DŽ Z5U DžLj Ԡ Վ Lj փ ăāā LDO DŽ 3Dž ց Lj LDO NPN ă LDO NPN Lj DŽ Dž ăāā Lj NPN PNP Lj LDO փ NPN NPN ( Բ PNP LDO )ăāā LDO ԲNPN Lj LDO ( )ց ă , ԲLDO Lj LDO Lj ESR փ ăāā Lj LDO LM1085 3A Lj 10uF ă LDO Ղ ESR Lj LDO ESR ăāā ESR Lj փ ă Lj 10uF ESR 50m ˮLj Վ 320kHz DŽ 18Džăāāփ փ ă P1 P L 0dB lj180Ń ă Lj 0dB ց ă Lj 320kHz Lj Lj ց ăāā ӷ LDO LjLP2985 LP2989Lj ESR ă ESRESR LDO( )FET DŽ Dž1012391919.P LDOA N -1148ǖ ցNational Semiconductor Americas Customer Support CenterEmail:new.feedback@ Tel:1-800-272-9959National SemiconductorEurope Customer Support CenterFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)6995086208English Tel:+44(0)8702402171Français Tel:+33(0)141918790National Semiconductor Asia Pacific Customer Support CenterEmail:ap.support@National SemiconductorJapan Customer Support Center Fax:81-3-5639-7507Email:jpn.feedback@ Tel:81-3-5639-7560www Lj ӷ փ փ ă ӷ ԍ Lj փ ăLj ǖ ăӷ Ljփ ӷ Ԣ և ă ǖ1. Ԣ/ ǖDŽa DžԢ ǗDŽb Dž Lj Lj ă2. և Ԣ LjԢ/ Lj Ԣ/ Ҿ և ăӷ Ԉ Ė DŽCSP-9-111C2Džė Ė DŽCSP-9-111S2Džė LjփԈ CSP-9-111S2 " "ă RoHS ă5ċ10m ˮă ESR LDO DŽ 18 Džăāā LP2985 ESR , ESR ă ESR ă և LDO ESR ӯ 100m ˮ-5ˮLj փ ăLP2985 ESR 3M ˮ, 500M ˮLj ăāā ESR Lj 15ă Lj LDO ԥ IC ևă և ESR Ղ Lj փ ă Lj ăāāLDO P-FET DŽP Dž DŽ 19Džăāā P-FET LDO Lj , PNP LDO DŽ 2Dž ժ ă Lj ժ ă LDO ǖāāāāPWR DŽBase Drive DžǙ!Vin ġIbaseāā PNP ˸ DŽPNP Džă PNP LDO ˸ ӯ 15ċ20DŽ Džă փ DŽ DžăP DŽP-FET Dž Lj ăāāP-FET LDO DŽFET Dž ă Lj Բ ă ă。