理解版图的层

版图设计培训资料

✓ calibre

– Spring soft

✓ laker

第一部分:了解版图

4.

版图的设计流程 熟悉所需文件

对电路的了解

版图布局布线

DRC/LVS

GDSII to FAB

技术中心内部资料

工艺厂商提 供:.tf .display Design rule 、DRC LVS 文件、 PDK、ESD文件、金属阻

PMOS

MOS管剖面图

第二部分:版图设计基础

2.1 器件

2.1.1 MOS管

NMOS工艺层立体图

技术中心内部资料

NMOS版图

13

第二部分:版图设计基础

2.1 器件

2.1.1 MOS管 1) NMOS管

✓ 以TSMC,CMOS,N单阱工艺 为例

✓ NMOS管,做在P衬底上,沟道 为P型,源漏为N型

电阻类型

技术中心内部资料

电阻版图

18

第二部分:版图设计基础

2.1器件

2.1.3 电容

1) 电容值计算C=L*W*C0 2) 电容分类:

✓ poly电容 ✓ MIM电容

基于单位面积电容值

✓ MOS电容 源漏接地,基于栅电容, C=W*L*Cox

MIM电容版图

技术中心内部资料

MOS电容版图

19

值文件

8

IC模拟版图设计

第二部分:版图设计基础

1. 认识版图 2. 版图组成两大部件

2.1 器件 2.2 互连

3. 版图编辑器 4. 电路图编辑器 5. 了解工艺厂商

技术中心内部资料

9

第二部分:版图设计基础

1. 认识版图

Poly

模拟集成电路版图设计基础

三、版图与线路图、工艺的关系

• 1、逻辑图(线路图)------版图-----工艺(流片,形成实物产品) • 2、版图决定于线路图,版图必须和线路图完全一一对应,

根据版图提出的线路图,必须完全实现需求的逻辑功能 • 3、版图受工艺的限制,要么按照特征尺寸画版图,

要么对应具体工艺的特征长度,给出每一种情况的具体数值 • 4、版图的两大任务:

4.相关设置

七、如何绘制版图

5.从原理图将器件导入版图 • 待前面基本设置完成之后便可从原理图将器件导入版图中 • 导入后版图中的器件排布位置和原理图中一致 • 有三种方法可以完成导入

七、如何绘制版图

6.连接器件(常用快捷键)

七、如何绘制版图

6.连接器件(常用快捷键)

七、如何绘制版图

7.实际操作

NMOS晶体管的3倍。 • 两种晶体管的长度看似相同,但却不同,我们很难辨别它们的差异; • 对于N阱来说,N+区域实际上是与VDD相连接的,而电路图中没有显

示这一连接关系; • 对于衬底来说,P+区域实际上是与VSS相连接的。而电路图中没有显

示这一连接关系。

七、如何绘制版图

1.需要的软件工具

七、如何绘制版图

光刻胶 Si3 N4

(1)对P型硅片进行氧化, 生成较 薄 的 一 层 Si3N4 , 然 后进 行 光 刻 , 刻出有源区后进行场氧化。

紫外线照射

掩膜版 掩膜版图形

P-Si

Si3 N4

P-Si

Si3 N4

P-Si

SiO2

集成电路工艺基础

P-Si (b)

P-Si (c)

P-Si

N+ (d )

多晶硅 0.5 ~2m

3.1 匹配中心思想 3.2 匹配问题 3.3 如何匹配 3.4 MOS管 3.5 电阻 3.6 电容 3.7 匹配规则

集成电路版图设计

02 集成电路版图设计基础

CHAPTER

电路设计基础

01

模拟电路设计

02

运算放大器

03

比较器

04

触发器

电路设计基础

01

数字电路设计

02

组合逻辑电路

时序逻辑电路

03

04

可编程逻辑电 路

版图设计基础

版图编辑软件 ICEDrawer

版图设计基础

01

Laker

02

P甩 Pro

版图设计规则

03

版图设计基础

管的形状和尺寸等。

案例二:低功耗模拟电路版图设计

总结词

通过优化模拟电路的版图设计,实现低功耗的目的, 以满足便携式电子设备和物联网等领域的需求。

详细描述

低功耗模拟电路版图设计需要考虑模拟电路的性能和 功耗等方面,同时还需要考虑噪声和失真等方面的因 素。为了实现低功耗的设计,需要采用优化的版图设 计方法,如使用低阻抗的走线、优化晶体管的形状和 尺寸等。

3

antenna effect simulation

物理验证基础 01

P/R/O/L/C分析

热学参数分析(T)

03

02

电学参数分析(P/R/O)

电磁兼容性分析(EMC)

04

03 集成电路版图设计技术

CHAPTER

逻辑电路版图设计

逻辑电路

逻辑电路是实现逻辑运算和逻辑控制的电路,分为组合逻 辑电路和时序逻辑电路。在版图设计中,需要考虑到电路 的复杂性、功耗、速度等因素。

提高芯片的可测试性。

可制造性版图设计实践

符合制造规范

遵循制造规范和流程,确保版图设计具有良好的可制 造性。

pcb板各层的含义

pcb板各层的含义1)顶层(Top Layer),也称元件层,主要用来放置元器件,对于比层板和多层板可以用来布线. (2)中间层(Mid Layer),最多可有30层,在多层板中用于布信号线. (3)底层(Bootom Layer),也称焊接层,主要用于布线及焊接,有时也可放置元器件. (4)顶部丝印层(Top Overlayer),用于标注元器件的投影轮廓、元器件的标号、标称值或型号及各种注释字符。

(5)底部丝印层(Bottom Overlayer),与顶部丝印层作用相同,如果各种标注在顶部丝印层都含有,那么在底部丝印层就不需要了。

(6)内部电源接地层(Internal Planes), (7)机械层(Mechanical Layers), (8)阻焊层(Solder Mask-焊接面),有顶部阻焊层(Top solder Mask)和底部阻焊层(Bootom Solder mask)两层,是Protel PCB对应于电路板文件中的焊盘和过孔数据自动生成的板层,主要用于铺设阻焊漆.本板层采用负片输出,所以板层上显示的焊盘和过孔部分代表电路板上不铺阻焊漆的区域,也就是可以进行焊接的部分. (9)防锡膏层(Past Mask-面焊面),有顶部防锡膏层(Top Past Mask)和底部防锡膏层(Bottom Past mask)两层,它是过焊炉时用来对应SMD元件焊点的,也是负片形式输出.板层上显示的焊盘和过孔部分代表电路板上不铺锡膏的区域,也就是不可以进行焊接的部分。

(10)禁止布线层(Keep Ou Layer), (11)多层(MultiLayer) (12)Drill (13)(Connect)(DRC Errors)(Pad holes)(Via Holes)(Visible Grid1)(visible Grid2) 1.solder表示是否阻焊,就是PCB板上是否露铜2.paste是开钢网用的,是否开钢网孔所以画板子时两层都要画,solder是为了PCB板上没有绿油覆盖(露铜),paste上是为了钢网开孔,可以刷上锡膏。

新手学版图—理解版图的层

网站论坛| 旧讨论区stm_em(); //-->最新公告:当前没有任何公告!网站论坛| 加入收藏您现在的位置:纯粹的版图IC Layout >> 文章专栏 >> 物理版图 >> [专题]新手学版图 >> 正文新手学版图—理解版图的层(详细)热新手学版图—理解版图的层(详细)[ 作者:nfmao | 转贴自:本站原创 | 点击数:2143 | 更新时间:2006-8-17 | 文章录入:nfmao ]新手学版图—理解版图的层版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS反相器为例,基本原理很简单,当输入高电平时,NMOS导通,输出端连接到地;当输入端为低电平时,PMOS导通,输出端连接到VDD。

版图的目的就是要以图形的方式形成这两个MOS管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POLY自对准形成MOS管子,输入为POLY,输出为金属连线,连接点为CONTACT。

首先创建新的cell view背景代表P型衬底,材料为Si-100 电阻率约5-10Ωcm,清洗后生长约200 Å氧化层,再以LPCVD(低压化学气相沉积)沉积氮化硅约800A。

Wafer厚度大约为750um,但最后打磨贴片后的厚度大约只有约250um。

(10000A=1um)氧化层的应用大致可分为:屏蔽、遮蔽、场区及局部绝缘、衬垫、缺陷去除、栅介电层、浅沟槽阻挡,厚度依次约为200A、5000A、3000-5000A、100-200A、<1000A、30-120A、100-200A。

氮化物一般较为致密,所以可以用来隔离、阻挡,以及CMP的停止层。

第3章工艺基础及版图的层

第三章 集成电路工艺基础及版图设计

为了是SPICE能够精确地预测电路的复杂工 作过程,我们不仅需要设计规范和初始原理图, 还必须建立相关电路元件的数学描述。

第三章 集成电路工艺基础及版图设计

CMOS反相器的设计

在一定的工艺条件下,反相器的设计,关键是对晶体管的 尺寸(W/L)的设计,并由确定的沟道长度,获得沟道宽度 的具体数值。

多晶硅(Uin)

金属(Uout )

金属(UDD)

(b)

P+

N-Si

N+

P阱

薄 氧 化 层 (栅 氧 化 层 )

图3 - 6 反向器版图及结构剖面图 (a) 版图; (b) 结构剖面图

第三章 集成电路工艺基础及版图设计

硅晶圆 确定晶体管的基底区域 形成并绘制多晶硅栅的图案

确定有源区 为接触孔开孔(对每个互连层都如此操作) 确定互连层(对每个互连层都如此操作)

第三章 集成电路工艺基础及版图设计

3.3.4器件尺寸设计

栅和有源区的重叠确定了器件的尺寸,重叠区之外的区 域对器件的尺寸没有影响。

如何根据电路性能要求设计器件的尺寸?要设计多大的 重叠区?

第三章 集成电路工艺基础及版图设计

两个重要的尺寸参数——晶体管的长度和宽度

就版图而言,晶体管的长度是源极和漏极之间的距 离;就晶体管性能而言,晶体管的长度是电子所必须 移动的距离;就制造而言,晶体管的长度是多晶硅 (多晶)能够可靠制造的最窄可能长度。

第三章 集成电路工艺基础及版图设计

图3 - 5 反向器

第三章 集成电路工艺基础及版图设计

掩膜版1: 用来规定P阱的形状、 大小及位置。 掩膜版2: 用于确定薄氧化层。 掩膜版3: 用来刻蚀多晶硅, 形成多晶硅栅极及 多晶硅互连线。 掩膜版4: 确定需要进行离子注入形成P+的区域。

解析AutoCAD中层的概念

解析AutoCAD中层的概念(基础教研室张霞林)大家学习PhotoShop的时候接触到了层的概念,普遍认为这一章比较难学。

在AutoCAD中也有层的概念,而且非常重要,在CAD中绘制各种图形时,不管繁简与否,都将会使用到层。

图形越复杂,所涉及到的层也越多。

层虽说是AutoCAD中较简单的工具,但也是最有效的工具之一。

切实理解层的概念,合理运用层的各项操作,都将会直接影响图形绘制的质量。

同时,也可使繁琐的工作变得简单而有趣。

AutoCAD的层可以简单而形象地理解为:一层挨一层放置的透明的电子纸。

每层电子纸上都绘制相应的图像,当所有的纸张重叠在一起时就是完整的一幅图了。

比如想绘制房间布局图,我们可以将墙壁绘制在图层1上,电器绘制在图层2上,家具绘制在图层3上,将三个图层全部打开就是最后完整的图形。

要想修改电器部分,可以直接修改,也可以将家具和墙壁所在的图层设为关,即不可见,这样就不会因为修改电器而误修改家具部分了。

我们可以根据需要增加或删除某一层或多个层。

在每一层上,都可以进行图形绘制,能够设置任意的线型与颜色。

在图形的绘制之前,为了便于以后的使用,最好先创建几个层。

层的创建可通过下拉菜单Data,Layers Control完成,也可通过单击工具条Layers实现创建。

创建时,可一次定义一个或多个层名,层名之间应用逗号隔开,每个层名中不能有空格。

层名限于使用标准字母、数字以及连字符(-)、美元符号($)和下划线(_),且层名最长不可以超过31个字符。

当层名重复时将执行前者。

层对于新建的层,其颜色和线型将自动定义为White和CONTINUOUS,状态为打开。

在层的使用过程中,我们可以根据需要设置层的特性。

AutoCAD支持255种颜色选择,线型库中包括了多种待选线型。

选择设置不同的颜色和线型,可以使得屏幕上的图形美观且便于区分。

线型的设置比较简单,只要单击Set Linetype, 即可根据需要设置。

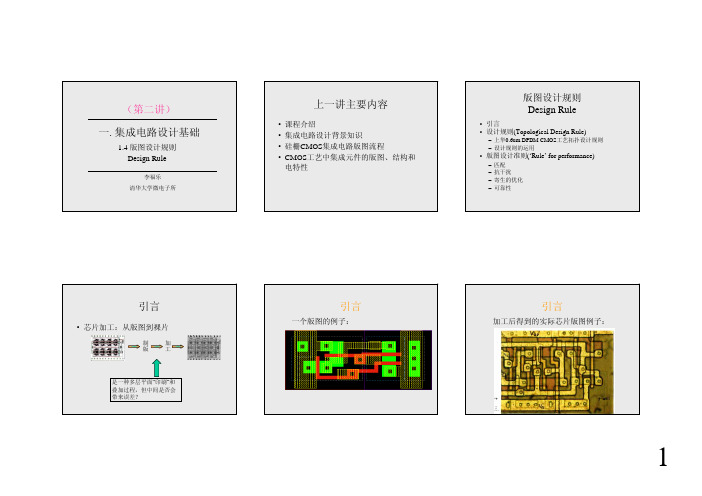

第二讲集成电路版图设计规则

- 1.5mA 最大电流密度

/um

-

- 禁止并行金属线90度拐角,用135

度拐角代替

a

c.2

b

c.1 c.2

设计规则 via

定义为两层金属之 间的连接孔

符号 尺寸

含义

12.a .7*.7 过孔最小面积

12.b 0.8 过孔间距

12.d~f - 接触孔、poly-poly电容和栅 上不能打过孔

12.g 0.4 金属1对过孔的最小覆盖

6.d 6.e 6.f 6.g

尺寸 1.2 1.0 0.5 3.2 1.5 0.8 -

含义 poly2做电容时的最小宽度 poly2做电容时的最小间距 Poly2与有源区的最小间距 做关键电容时的间距 电容底板对顶板的最小覆盖 电容Poly2对接触孔最小覆盖 Poly2不能在有源区上 Poly2不能跨过poly1边沿

– 上华0.6um DPDM CMOS工艺拓扑设计规则 – 设计规则的运用

• 版图设计准则(‘Rule’ for performance)

– 匹配 – 抗干扰 – 寄生的优化 – 可靠性

引言

• 芯片加工:从版图到裸片

制

加

版

工

是一种多层平面“印刷”和 叠加过程,但中间是否会 带来误差?

引言

一个版图的例子:

习)

VDD

15k

OUT IN 80/0.8

又试问NMOS晶体管的漏极面积和周长是多 少?

设计规则的运用

• TASK3:设计一个简单开关电容电路 (练习)

f1 IN

30/0.6 X

f2 OUT

60/0.6 2pF 6/0.6 12/0.6

又试问X点的寄生电容如何计算?

版图重点总结

第一章基本概念(1) ☆☆集成电路:Integrated Circuit ,缩写ICIC是通过一系列特定的加工工艺,将晶体管、二极管等有源器件和电阻、电容、电感等无源器件,按照一定的电路互连,“集成”在一块半导体晶片(如硅或砷化镓)上,封装在一个外壳内,执行特定电路或系统功能的一种器件。

(2)特征尺寸定义为器件中最小线条宽度(对MOS器件而言,通常指器件栅电极所决定的沟道几何长度),也可定义为最小线条宽度与线条间距之和的一半。

(3)就设计方法而言,设计集成电路的方法可以分为三种方式:全定制(Full-Custom Design Approach)半定制(Semi-Custom Design Approach)(标准单元、积木块、门阵列、门海)可编程IC (PLD:Programmable Logic Device)(PROM 、GAL 、PLA、PAL、PLD 、FPGA )(4)☆☆积木块法(BB)与标准单元法(sc)不同之处是:第一,它既不要求每个单元(或称积木块)等高,也不要求等宽。

每个单元可根据最合理的情况单独进行版图设计,因而可获得最佳性能。

设计好的单元存入库中备调用。

第二,它没有统一的布线通道,而是根据需要加以分配。

(5)☆☆门阵列方法与门海方法的比较门阵列方法的设计特点:设计周期短,设计成本低,适合设计适当规模、中等性能、要求设计时间短、数量相对较少的电路。

不足:设计灵活性较低;门利用率低;芯片面积浪费。

门海方法的设计特点:门利用率高,集成密度大,布线灵活,保证布线布通率。

不足:仍有布线通道,增加通道是单元高度的整数倍,布线通道下的晶体管不可用。

(6)集成电路设计:根据电路功能和性能要求,在正确选择系统配置、电路形式、器件结构、工艺方案和设计规则的情况下,尽量减小芯片面积,降低设计成本,缩短设计周期以保证全局优化,设计出满足需求的集成电路。

其最终的输出结果是掩膜版图,通过制版和工艺流片可以得到所需的集成电路。

版图

多晶硅区通常也称为poly,氧化层有时也简称氧。

有源区层包括源区,漏区和沟道。

P选择层(P Select),N选择层(N Select)多晶硅能对掺杂工艺起到掩蔽作用,所以在集成电路制造过程中,由于多晶硅栅极的存在,源区和漏区能自动分开。

画版图及后仿真的步骤:画好原理图⇒在原理图中加入引脚(pin)⇒新建版图(File⇒New ⇒Cell View,弹出Create New File对话框,Tool改为Virtuoso,ok)⇒元件更新到版图中(Tools ⇒Layout XL,Design⇒Gen From Source,弹出Layout Generation Options对话框,选择只生成元件,ok)⇒布局⇒布线⇒跑DRC(Assura→run DRC)⇒跑LVS(Assura→run LVS)⇒提取寄生参数RCX(Assura run RCX)⇒新建版图symbol(From view name选Layout)⇒新建测试原理图,前仿真一样,后仿真时注意setup→environment→弹出environmentoptions 对话框,将改为即在spectre后加av_extracted,别的不变。

布局注意:栅一般同向,排布可参考原理图m:移动,具体操作:单击鼠标左键选中器件,移动器件(注意是移动,鼠标点击一下就放开,不是拖动),到需要放下的位置单击鼠标左键放下器件。

q:改属性,比如改器件属性:点击选中器件,再按q,弹出编辑器件属性对话框Edit Instance Properties注意:Multiplier只能在原理图中设定。

底层模块版图一般画在第一象限,以X,Y轴为边界。

顶层一般以中心点(原点)对称。

底层的版图坐标位置会影响顶层,顶层的不会影响底层。

所以,画好底层版图后一般不要随便移动它。

单显示某一层:选中某一层——NV——window——Redraw(r :刷新屏幕)布线注意:p:画线(是移动,不是拖动,双击结束或按enter结束)p:画线,n:以45度为标准变化,按p后按F3,固定线的宽度,若再选中fixed width,则所有层的线都固定为同一宽度r:画矩形k:标尺shift+k:取消标尺如何确保连对:点击版图中的元件,原理图中对应的元件会显示高亮,如此看其如何对应,若不显示则Layout XL一下。

最新PCB的层的详细解释

最新PCB的层的详细解释Altium Designer中各层的含义mecha nical,机械层keepoutlayer禁止布线层topoverlay顶层丝印层bottomoverlay底层丝印层toppaste,顶层焊盘层bottompaste底层焊盘层topsolder 顶层阻焊层bottomsolder底层阻焊层drillguide,过孔引导层drilldrawing过孔钻孔层multilayer 多层,机械层是定义整个PCB板的外观的,其实我们在说机械层的时候就是指整个PCB板的外形结构。

禁止布线层是定义我们在布电气特性的铜时的边界,也就是说我们先定义了禁止布线层后, 我们在以后的布过程屮,所布的具有电气特性的线是不可能超出禁止布线层的边界.topoverlay和bottomoverlay是定义顶层和底的丝印字符,就是一般我们在PCB板上看到的元件编号和一些字符。

toppaste和bottompaste是顶层底焊盘层,它就是指我们可以看到的露在外面的铜钳,(比如我们在顶层布线层画了一根导线,这根导线我们在PCB 上所看到的只是…根线而已,它是被整个绿油盖住的,但是我们在这根线的位置上的toppaste层上画一个方形,或一个点,所打出来的板上这个方形和这个点就没有绿油了,而是铜辛白。

topsolder和bottomsolder这两个层刚刚和前面两个层相反,可以这样说,这两个层就是要盖绿油的层,multilayer这个层实际上就和机械层差不多了,顾名恩义,这个层就是指PCB板的所有层。

topsolder和bottomsolder这两个层刚刚和前面两个层相反, 可以这样说,这两个层就是要盖绿油的层;因为它是负片输出,所以实际上有solder mask的部分实际效果并不上绿油,而是镀锡,呈银白色!1 Signal layer(信号层)信号层主要用于布置电路板上的导线。

Protel 99 SE提供T 32个信号层,包括Top layer(顶层),Bottom layer(底层)和30 个MidLayer(屮间层)。

用Protel绘制PCB的板层及其其含义

用Protel绘制PCB的板层及其其含义Protel98、Protel99的PCB工作窗口提供了多达32层的绘图平面,通常可以完成16层印制电路板自动布线,用手工布线时甚至可达到20层以上,可以在任何层面上绘图。

Protel98、Protel99把32层的绘图平面加上8个其它辅助层,分成几个不同类型的专用工作层面。

在工作层面对话框中可以根据需要打开或关闭层面,层面名称前若有“√”,就表示该层面是打开的,无“√”表示该层面是关闭的(关闭的层面并非不存在,只是不显示而已),如下图所示。

从图中可见,Protel98、Protel99的绘图平面按照不同的类型而分为几组,其名称和作用如下:一、Signal Layers(信号层)Protel98、Protel99提供了16个信号层:Top (顶层)、Bottom(底层)和Mid1-Mid14(14个中间层)。

信号层就是用来完成印制电路板铜箔走线的布线层。

在设计双面板时,一般只使用Top(顶层)和Bottom(底层)两层,当印制电路板层数超过4层时,就需要使用Mid(中间布线层)。

二、Internal Planes(内部电源/接地层)Protel98、Protel99提供了Plane1-Plane4(4个内部电源/接地层)。

内部电源/接地层主要用于4层以上印制电路板作为电源和接地专用布线层,双面板不需要使用。

三、Mechanical Layers(机械层)机械层一般用来绘制印制电路板的边框(边界),通常只需使用一个机械层。

有Mech1-Mech4(4个机械层)。

四、Drkll Layers(钻孔位置层)共有2层:“Drill Drawing”和“Drill Guide”。

用于绘制钻孔孔径和孔的定位。

五、Solder Mask(阻焊层)共有2层:Top(顶层)和Bottom(底层)。

阻焊层上绘制的时印制电路板上的焊盘和过孔周围的保护区域。

六、Paste Mask(锡膏防护层)共有2层:Top(顶层)和Bottom(底层)。

层的概念

1、“层(Layer) ”的概念与字处理或其它许多软件中为实现图、文、色彩等的嵌套与合成而引入的“层”的概念有所同,Protel的“层”不是虚拟的,而是印刷板材料本身实实在在的各铜箔层。

现今,由于电子线路的元件密集安装。

防干扰和布线等特殊要求,一些较新的电子产品中所用的印刷板不仅有上下两面供走线,在板的中间还设有能被特殊加工的夹层铜箔,例如,现在的计算机主板所用的印板材料多在4层以上。

这些层因加工相对较难而大多用于设置走线较为简单的电源布线层(如软件中的Ground Dever和Power Dever),并常用大面积填充的办法来布线(如软件中的ExternaI P1a11e和Fill)。

上下位置的表面层与中间各层需要连通的地方用软件中提到的所谓“过孔(Via)”来沟通。

有了以上解释,就不难理解“多层焊盘”和“布线层设置”的有关概念了。

举个简单的例子,不少人布线完成,到打印出来时方才发现很多连线的终端都没有焊盘,其实这是自己添加器件库时忽略了“层”的概念,没把自己绘制封装的焊盘特性定义为”多层(Mulii一Layer)的缘故。

要提醒的是,一旦选定了所用印板的层数,务必关闭那些未被使用的层,免得惹事生非走弯路。

2、过孔(Via)为连通各层之间的线路,在各层需要连通的导线的文汇处钻上一个公共孔,这就是过孔。

工艺上在过孔的孔壁圆柱面上用化学沉积的方法镀上一层金属,用以连通中间各层需要连通的铜箔,而过孔的上下两面做成普通的焊盘形状,可直接与上下两面的线路相通,也可不连。

一般而言,设计线路时对过孔的处理有以下原则:(1)尽量少用过孔,一旦选用了过孔,务必处理好它与周边各实体的间隙,特别是容易被忽视的中间各层与过孔不相连的线与过孔的间隙,如果是自动布线,可在“过孔数量最小化” (Via Minimiz8tion)子菜单里选择“on”项来自动解决。

(2)需要的载流量越大,所需的过孔尺寸越大,如电源层和地层与其它层联接所用的过孔就要大一些。

版图初级-理解版图的层(彩图)

新手学版图—理解版图的层(详细)新手学版图—理解版图的层版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS反相器为例,基本原理很简单,当输入高电平时,NMOS导通,输出端连接到地;当输入端为低电平时,PMOS导通,输出端连接到VDD。

版图的目的就是要以图形的方式形成这两个MOS管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POLY自对准形成MOS管子,输入为POLY,输出为金属连线,连接点为CONTACT。

首先创建新的cell view背景代表P型衬底,材料为Si-100 电阻率约5-10Ωcm,清洗后生长约200Å氧化层,再以LPCVD(低压化学气相沉积)沉积氮化硅约800A。

Wafer厚度大约为750um,但最后打磨贴片后的厚度大约只有约250um。

(10000A=1um)氧化层的应用大致可分为:屏蔽、遮蔽、场区及局部绝缘、衬垫、缺陷去除、栅介电层、浅沟槽阻挡,厚度依次约为200A、5000A、3000-5000A、100-200A、<1000A、30-120A、100-200A。

氮化物一般较为致密,所以可以用来隔离、阻挡,以及CMP 的停止层。

涂布光阻、曝光、显影,以氮化物等离子体干法刻蚀去除氮化硅,剥离光阻(以下将省略一些层的去除过程)。

版图Active层将定位出有源区,非有源区将通过LOCOS(硅的局部氧化)生长场氧化层,厚度大约3000-10000A。

不过因该过程存在鸟嘴效应及表面平坦度问题,90年代后已经由STI(淺沟槽绝缘)所取代。

版图P-well层定位P-well区域,在这一区域离子植入B+/225KeV/3x10^13cm^-2。

版图设计基础new

硅芯片上的电子世界--电容

• 电容:一对电极中间夹一层电介质的三明治结构; • 硅芯片上的薄膜电容:

几十微米

上电极:金属或多晶硅 氧化硅电介质 下电极:金属或多晶硅 硅片

• 集成电路中的集成电容

• 金属-金属(多层金属工艺,MIM) • 金属-多晶硅 • 多晶硅-多晶硅(双层多晶硅工艺,PIP)

方块电阻: R=ρL/S=ρL/dW=(ρ/d)L/W R = ρ/d R=R L/W 方块电阻与半导体的掺杂水平和掺杂区的结深有关 对于集成电路来说,方块电阻是基本单位,量纲是Ω/ 只要知道材料的方块电阻,就可以根据所需要的电阻值计算 出电阻的方块数,即电阻条的长度和宽度比 栅极多晶:2-3 Ω/ ;金属:20-100m Ω/ 多晶:20-30 Ω/ ;扩散区:2-200 Ω/

接触孔层和通孔层

• 接触孔包括有源区接触孔(Active Contact)和多晶硅接 触孔(poly contact) • 有源区接触孔用来连接第一层金属和N+或P+区域,在版 图设计中有源区接触孔的形状通常是正方形。 • 应该尽可能多地打接触孔,这是因为接触孔是由金属形成, 存在一定的阻值,假设每个接触孔的阻值是R,多个接触 孔相当于多个并联的电阻

版图设计(物理层设计)

• 版图设计的目标:实现电路正确物理连接,将设计好的 电路映射到硅片上进行生产。芯片面积最小,性能优化 (连线总延迟最小) 集成电路设计的最终目标

• 版图设计的重要性:

电路功能和性能的物理实现;

布局、布线方案决定着芯片正常工作、面积、速度; • 经验很重要。 版图设计包括: 基本元器件版图设计; 布局和布线; 版图检验与分析。

绘图层

• • • • • • • • • • N阱层(N Well) 有源区层(Active) 多晶硅栅层(Poly) P选择层(P Select) N选择层(N Select) 接触孔层(Contact) 通孔层(Via) 金属层(Metal) 文字标注层(Text) 焊盘层(Pad)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

新手学版图—理解版图的层

版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS反相器为例,基本原理很简单,当输入高电平时,NMOS导通,输出端连接到地;当输入端为低电平时,PMOS导通,输出端连接到VDD。

版图的目的就是要以图形的方式形成这两个MOS管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POLY自对准形成MOS管子,输入为POLY,输出为金属连线,连接点为CONTACT。

首先创建新的cell view背景代表P型衬底,材料为Si-100 电阻率约5-10Ωcm,清洗后生长约200Å氧化层,再以LPCVD(低压化学气相沉积)沉积氮化硅约

800A。

Wafer厚度大约为750um,但最后打磨贴片后的厚度大约只有约250um。

(10000A=1um)

氧化层的应用大致可分为:屏蔽、遮蔽、场区及局部绝缘、衬垫、缺陷去除、栅介电层、浅沟槽阻挡,厚度依次约为200A、5000A、3000-5000A、100-200A、<1000A、30-120A、100-200A。

氮化物一般较为致密,所以可以用来隔离、阻挡,以及CMP 的停止层。

涂布光阻、曝光、显影,以氮化物等离子体干法刻蚀去除氮化硅,剥离光阻(以下将省略一些层的去除过程)。

版图Active层将定位出有源区,非有源区将通过LOCOS(硅的局部氧化)生长场氧化层,厚度大约3000-10000A。

不过因该过程存在鸟嘴效应及表面平坦度问题,90年代后已经由STI(淺沟槽绝缘)所取代。

版图P-well层定位P-well区域,在这一区域离子植入B+/225KeV/3x10^13cm^-2。

用版图N-well层定位N-well区域,离子植入P+/600KeV/2x10^13cm^-2。

以

P/250/2x10^12 + P/1200/3x10^13 + 950C,30min,为例最后深度大约2um,方块电阻790ohms。

传统工艺制成的阱区深度约4um左右。

阱区形成后还可能进行阈值调整处理,这一步不需要版图层的参与。

版图Poly层定位poly及gate,不过在形成channel(沟道)之前,必须生长出一层优质的氧化层,这一层的厚度约30-120A,可能实际测量出来只有十几埃。

在这一层上以LPCVD沉积多晶硅约0.5um,并对poly掺杂P/30/5x10^15。

因为多晶硅各向异性所以采用RIE(反应离子刻蚀)方法进行刻蚀。

自对准形成源、漏极,被poly层挡住与active层重叠的下面将会是MOS的沟道,剩下的active 区域将形成源、漏极。

为了抑制热电子或热载流子效应要通过LDD(轻掺杂漏极)首先进行轻掺杂,然后在栅上形成侧墙后再以低能量、高电流来形成源漏区,这样会形成一个梯度。

版图P-imp层决定形成P+型,离子植入B/10/2x10^15,版图N-imp层决定形成N+型,离子植入As/30/3x10^15。

通常该区域的深度在2um左右。

此时器件已经基本形成,之后要为连接作好准备。

在表面濺射一层金属层(比如Ti),在与硅接触的表面反应形成金属硅化物(silicide),在外表面形成TiN。

如果栅、源、漏极都有silicide 俗称为salicide,如果只形成在多晶硅上称为polycide。

表面平坦化处理时,可以通过加热掺杂的BPSG(硼磷硅玻璃)软化流动,或以CMP(化学机械研磨)以达到表面平坦化。

版图contact层定位连接孔,contact光掩膜通常采用Dark形式,即图形区域透光,背景不透光,配合正光阻,光照射的区域可溶化,以此定位出开孔区域。

孔内金属是以MOCVD(金属有机化学气相沉积CVD)形式沉积金属W(钨),再以CMP方式打磨多余的金属。

濺射第一层金属,并以版图metal1层,刻画出金属连线。

覆盖CMP(介电层),以同样的方式开孔(版图via1层),刻画第二层金属(版图metal2层)。

如果是完整的项目还要使用版图pass层开出PAD的位置,并进行钝化处理以PECVD(介质等离子体增强化学气相沉积)沉积氮化硅,以达到保护芯片的目的。

现在各层的作用已经有了说明,接下来将利用实际的作用来举例说明,层与层之间的关系。

1,版图P-well层,N-wel l层在衬底形成各自的阱区,它们之间的关系应该不能相互重叠。

2,因为器件形成在阱中,所以器件的图形必须被阱所覆盖,要么在P-well中,要么在N-well中。

3,P-well与P-well,N-well与N-well是否可以相连,取决于特性是否一致,比如相同的电位。

4,P-imp,N-imp层要比相对的active 大。

否则未覆盖的区域将没有离子植入。

5,因为自对准工艺,在形成channel的地方,poly要横跨过active层。

没有channel 的地方避免接触。

6,contact层必须与metal层或poly层要有接触(在需要连接的地方)。

传统的“钉头”形式需要金属覆盖住contact。