FPGA设计实验指导书(2013)

FPGA实验_简单计算机的设计与调试实验指导书

实验3 简单计算机系统的设计与调试一、实验目的1.掌握利用指令集编写汇编语言程序2.掌握将编好的汇编语言程序翻译成机器码程序3.熟悉各类型指令执行的数据通道4.设计和调试一个8位单周期简单计算机系统二、实验任务1. 编程练习先采用汇编语言格式编写程序,检查程序的思路、流程,在无误情况下,转换成机器码。

程序1 :完成将两个固定数据(如0x96, 0x2A6)进行加、减、与、或、比较运算,将运算结果顺序存放在地址从0x40开始的10个RAM单元中。

程序2:完成将两个固定数据(如0x96, 0x2A6)进行加、减运算,将运算结果顺序显示在数码管上。

两个结果显示之间需加一定延时(软件延时,可以通过给一个寄存器赋初值,对这个寄存器进行减运算,直至结果为0)。

程序3:从键盘输入一个表达式,如:206 - 814= ,通过执行ROM中的程序代码,将运算结果显示在数码管上。

2. 调试简单计算机系统A在实验2任务5简单计算机系统A的ROM中存放编程练习中的程序1,并进行系统的仿真和调试,下载到实验板上进行测试、运行。

3. 设计简单计算机系统B在简单计算机系统A的基础上,增加I/O端口及其映射模块、数码管输出接口,将I/O 端口及其映射模块中的 IO0[7..0]、IO1[7..0]与数码管输出接口的 datainL[7..0]、datainH[7..0]相连,构成简单计算机系统B。

在ROM中存放编程练习中的程序2,并进行系统的仿真和调试,下载到实验板上进行测试、运行。

4. 设计简单计算机系统C在简单计算机系统B的基础上,增加4x4键盘输入接口模块,将I/O端口及其映射模块中IO3[7..0]~IO6[7..0]分别与键盘输入接口模块的srcL[7..0]、srcH[7..0]、dstL[7..0]、dstH[7..0]、, aluop[7..0]相连,构成简单计算机系统C,在ROM中存放编程练习中的程序3,并进行系统的仿真和调试,下载到实验板上进行测试、运行。

实验一FPGA设计流程指导

根据顶层模块中注释语句的提示,创建七段译码器模块的实例。

// 自己设计的代码中用到七段数码管时,需要删除这里的赋值语句

// assign

seven = 8'hFF;

assign seven_sel = 4'b1110; // 仅点亮最低位数码管

// 在下面添加自己设计的代码 decode4_7 decode4_7_inst(

11

数字系统设计与测试

所有在新建工程向导中进行的设置,在工程建立完成后,都可以通过 QuartusII 菜单项进行修改。

江苏大学计算机学院

5

数字系统设计与测试

资源管理区

标题栏 菜单栏 工具栏

编译状态区

工程工作区

信息显示区

图7

2. 设计输入

1) 新建顶层模块

点击菜单项 File-> new…,出现新建源文件对话框如图 8,选择新建一个 Verilog HDL File。 将老师提供的“TOP_FD_III.v”文件内容拷贝到新建 Verilog 文件中,并将模块名命名为顶 层模块名(即新建工程时指定的顶层模块名,以本实验图 2为例,模块名应更改为: seven_seg);保存文件,文件名与模块名相同(本例为:seven_seg.v)。新建的文件默认情况 下会自动加入到工程中。

图2

跳过图 3所示 Add Files 对话框,该对话框设置用来将已存在的设计文件加入到工程中。

图3

江苏大学计算机学院

3

数字系统设计与测试

点击 next,进入 Family & devices settings 对话框,指定 FPGA 器件为Cyclone系列的 EP1C6Q240C8,如图 4。Cyclone 系 列 FPGA 是 Altera 公司最初(2002 年)的低成本 FPGA。 2004 年和 2006 年,Altera 公司又推出了更新的,密度更高的Cyclone II和Cyclone III 系 列 FPGA,进一步巩固它在大批量、低成本应用解决方案中的地位。

FPGA实验指导书

FPGA实验指导书——DE2开发板使用实验昆明理工大学实验一 DE2的顶层默认程序这个实验为用户提供连接分配和顶层Verilog模块,这个模块也是这本手册所有其他实验的基础性模块。

这个实验产生的编程文件是DE2开发板在出货时作为默认载入开发板的编程文件。

本实验将介绍如何编译工程并把生成的编程文件下载到DE2开发板中。

启动开发板(1)将USB线和电源连接到DE2板上。

(2)按下电源开关,这时电源指示灯会被点亮。

(3)你将看到以下现象:●所有的LED灯都闪烁。

●所有七段数码管从0到F循环显示。

●液晶屏显示“Welcome to the Altera DE2 Board”。

●在VGA显示器上显示欢迎信息。

●将开关SW17置OFF,从LINEOUT插座输出1khz正弦波的声音;将开关SW17置ON并将一个MP3播放器的输出接到DE2板的LINE—IN端口,可从耳机里听到MP3播放的音乐。

●若将麦克风接到DE2板的MIC端口上,这样用户的声音可与MP3播放器混合。

Cyclone II中的顶层verilog模块这部分将介绍一个Quartus II工程中所需要的所有组件。

它将让你了解如何使用Quartus II将代码转换成数据流下载的整个设计流程。

按照以下步骤进行:(1)打开Quartus II 软件。

(2)点击File→Open Project ,如图1.1。

(3)在D:\DE2_System_v1.5\DE2_demonstrations\DE2_Default目录下选中DE2_Default.qpf工程文件打开。

(4)在“Project Navigator”工程导航区可查看该工程的层次、包含的所有文件、设计单元等信息。

其中“File”下列出了整个工程包含的所有文件。

双击顶层设计文件DE2_Default.v,可以看到文件的内容和I/O口的声明。

在对每个引脚声明时加上了详细的注释,以便用户更好的明白每个引脚的功能。

FPGA实验指导书

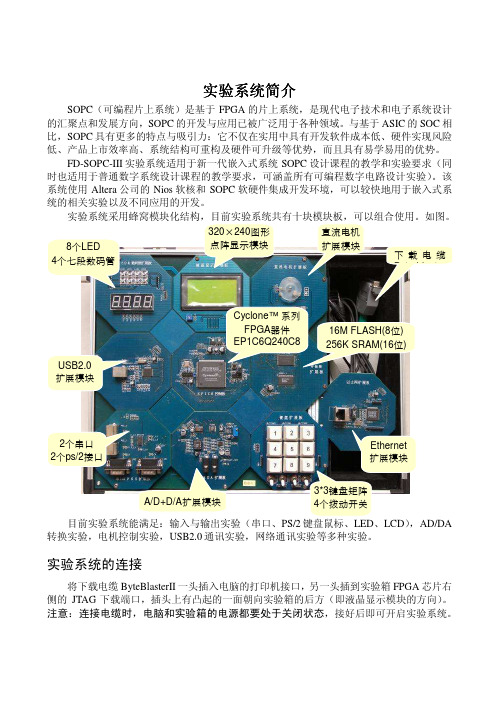

目录第1章FPGA系统 (1)1.1 系统简介 (1)1.2 系统功能特点 (1)1.3 开发平台标准配置 (2)1.4 功能模块介绍 (2)1.4.1 电源 (2)1.4.2 系统时钟 (3)1.4.3 LED灯 (3)1.4.4 8位拨码开关 (3)1.4.5 数码管显示 (4)1.4.6 键盘阵列 (5)1.4.7 独立矩形波信号源 (5)1.4.8 蜂鸣器 (6)第2章基础门电路及触发器 (8)2.1 实验一基本门电路 (8)2.1.1 实验目的 (8)2.1.2 实验内容 (8)2.1.3 实验原理及说明 (8)2.1.4 实验步骤 (8)2.1.5 参考程序及引脚分配 (9)2.2 实验二基本触发器 (10)2.2.1 实验目的 (10)2.2.2 实验内容 (10)2.2.3 实验原理及说明 (10)2.2.4 实验步骤 (10)2.2.5 参考程序及引脚分配 (11)2.3 实验三3-8译码器 (13)2.3.1 实验目的 (13)2.3.2 实验内容 (13)2.3.3 实验原理 (13)2.3.4 实验步骤 (13)2.3.5 参考程序及引脚分配 (14)2.4 实验四8—3编码器 (15)2.4.1 实验目的 (15)2.4.2 实验内容 (15)2.4.3 实验原理 (15)2.4.4 实验步骤 (15)2.4.5 参考程序及引脚分配 (16)2.5 实验五BCD八段显示译码器 (17)2.5.1 实验目的 (17)2.5.2 实验内容 (17)2.5.4 实验步骤 (17)2.5.5 参考程序及引脚分配 (17)2.6 实验六四选一数据选择器 (19)2.6.1 实验目的 (19)2.6.2 实验内容 (19)2.6.3 实验原理及说明 (19)2.6.4 实验步骤 (19)2.6.5 实验参考程序及引脚分配: (20)2.7 实验七数值比较器 (21)2.7.1 实验目的 (21)2.7.2 实验内容 (21)2.7.3 实验原理及说明 (21)2.7.4 实验步骤 (21)2.7.5 参考程序及引脚分配 (22)2.8 实验八4位二进制加法器 (23)2.8.1 实验目的 (23)2.8.2 实验内容 (23)2.8.3 实验原理及说明 (23)2.8.4 实验步骤 (24)2.8.5 参考程序及引脚分配 (24)2.9 实验九4位二进制乘法器 (26)2.9.1 实验目的 (26)2.9.2 实验内容 (26)2.9.3 实验原理及说明 (26)2.9.4 实验步骤 (27)2.9.5 参考程序及引脚分配 (27)第3章逻辑电路 (31)3.1 实验十移位寄存器 (31)3.1.1 实验目的 (31)3.1.2 实验内容 (31)3.1.3 实验原理 (31)3.1.4 实验步骤 (31)3.1.5 参考程序及引脚分配 (31)3.2 实验十一串行并行转换 (33)3.2.1 实验目的 (33)3.2.2 实验内容 (33)3.2.3 实验原理及说明 (33)3.2.4 实验步骤 (34)3.2.5 参考程序及引脚分配 (34)3.3 实验十二单时钟同步可逆计数器 (35)3.3.1 实验目的 (35)3.3.2 实验内容 (35)3.3.3 实验原理及说明 (36)3.3.5 参考程序及引脚分配 (36)3.4 实验十三顺序脉冲发生及其检测 (38)3.4.1 实验目的 (38)3.4.2 实验内容 (38)3.4.3 实验原理及说明 (38)3.4.4 实验步骤 (39)3.4.5 参考程序及引脚分配 (39)3.5 实验十四按键数码管循环左移显示 (41)3.5.1 实验目的 (41)3.5.2 实验内容 (41)3.5.3 实验原理 (41)3.5.4 实验步骤 (42)3.5.5 参考程序和引脚分配 (42)3.6 实验十五电子时钟 (45)3.6.1 实验目的 (45)3.6.2 实验内容 (45)3.6.3 实验原理 (46)3.6.4 实验步骤 (46)3.6.5 参考程序及引脚分配 (46)3.7 实验十六按键控制 (52)3.7.1 实验目的 (52)3.7.2 实验内容 (52)3.7.3 实验原理 (52)3.7.4 实验步骤 (53)3.7.5 参考程序及引脚分配 (53)第4章FPGA综合应用 (60)4.1 实验十七数字密码锁 (60)4.1.1 实验目的 (60)4.1.2 实验内容 (60)4.1.3 实验原理 (60)4.1.4 实验步骤 (61)4.1.5 参考程序及引脚分配 (61)4.2 实验十八智力抢答器 (66)4.2.1 实验目的 (66)4.2.2 实验内容 (66)4.2.3 实验原理及说明 (66)4.2.4 实验步骤 (67)4.2.5 参考程序及引脚分配 (68)4.3 实验十九自动售货机 (74)4.3.1 实验目的 (74)4.3.2 实验内容 (74)4.3.3 实验原理 (74)4.3.4 实验步骤 (75)4.3.5 参考程序和引脚分配 (75)4.4 实验二十数字频率计 (80)4.4.1 实验目的 (80)4.4.2 实验内容 (80)4.4.3 实验原理 (80)4.4.4 实验步骤 (81)4.4.5 参考程序及引脚分配 (81)第1章 FPGA系统1.1系统简介FPGA系统教学开发平台采用国际著名可编程逻辑器件公司Altera 的Cyclone系列5万门芯片为核心,整个平台采用模块化设计,各种模块可以自由组合,同时提供丰富的扩展接口,非常适合于FPGA初学者。

FPGA实验指导书(1)

实验一组合逻辑3-8译码器的设计 .................... 错误!未定义书签。

实验二基于FPGA的数字钟的设计 ................... 错误!未定义书签。

实验三基于NIOS的交通灯实验 .......................... 错误!未定义书签。

实验四静态图像显示 ............................................. 错误!未定义书签。

实验一组合逻辑3-8译码器的设计一、实验目的:1、通过3-8译码器的设计,让学生掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3、初步了解可编程器件设计的全过程。

二、实验步骤:1、打开QuartusII软件。

2、选择路径。

选择File/New Project Wizard,指定工作目录,指定工程和顶层设计实体称;注意:工作目录名不能有中文。

3、添加设计文件。

将设计文件加入工程中。

单击“Next”,如果有已经建立好的VHDL 或者原理图等文件可以在File name中选择路径然后添加,或者选择Add All添加所有可以添加的设计文件(.VHDL ,.Verilog原理图等)。

如果没有直接点击“Next”,等建立好工程后再添加也可,这里我们暂不添加。

4、选择FPGA器件。

Family选择Cyclone II,Available device选EP2C35F484C8,Packge选择Any,Pin Count 选择484,Speed grade选择Any;点击“Next”。

5、选择外部综合器、仿真器和时序分析器。

Quartus II支持外部工具,可通过选中来指定工具的路径。

这里我们不做选择,默认使用Quartus II自带的工具。

6、结束设置。

单击“Next”,弹出“工程设置统计”窗口,上面列出了工程的相关设置情况。

最后单击“Finish”,结束工程设置。

7、建立原理图文件。

电子系统设计实验指导书(FPGA基础篇Vivado版)

实验指导书(FPGA 基础篇 Vivado 版)

东南大学 电子科学 ........................................................................................................................................................... 1

安全使用规范

东南大学 电子科学与工程学院

无论何时,外部电源供电与 USB 两种供电方式只能用其中一种,避免因为电压有所差别而烧坏电路板。 采用电压高于5.5V的任何电源连接器可能造成永久性的损害。 插拔接插件前请关闭电路板总开关,否则易损坏器件。 电路板应在绝缘平台上使用,否则可能引起电路板损坏。 不同编码机制不要混接。 安装设备需防止静电。 液晶显示器件或模块结雾时,不要通电工作,防止电极化学反应,产生断线。 遇到正负极连接时需谨慎,避免接反引起开发板的损坏。 保持电路板的表面清洁。 小心轻放,避免不必要的硬件损伤。

实验目的 ....................................................................................................................................................... 17 实验内容 ....................................................................................................................................................... 17 实验要求 ....................................................................................................................................................... 17 实验步骤 ....................................................................................................................................................... 17 实验结果 ....................................................................................................................................................... 22

《FPGA设计与应用》实验指导书全(Verilog版)

《FPGA设计与应用》实验指导书熊利祥编武汉理工大学华夏学院2011年9月前言一、实验课目的数字电路与系统设计实验课是电子工程类专业教学中重要的实践环节,包括了ISE开发环境基本操作及FPGA的基本原理、基带传输系统的设计、Uart串口控制器电路的设计、PS/2接口的设计、VGA显示接口设计。

要求学生通过实验学会正确使用EDA技术,掌握FPGA器件的开发,熟练使用ISE开发环境,掌握Verilog语言的编程,掌握数字电路和系统的设计。

通过实验,使学生加深对课堂专业教学内容的理解,培养学生理论联系实际的能力,实事求是,严谨的科学作风,使学生通过实验结果,利用所学的理论去分析研究EDA技术。

培养学生使用Basys 2开发板的能力以及运用实验方法解决实际问题的能力。

二、实验要求:1.课前预习①认真阅读实验指导书,了解实验内容;②认真阅读有关实验的理论知识;③读懂程序代码。

2.实验过程①按时到达实验室;②认真听取老师对实验内容及实验要求的讲解;③认真进行实验的每一步,观察程序代码与仿真结果是否相符;④将实验过程中程序代码和仿真结果提交给老师审查;⑤做完实验后,整理实验设备,关闭实验开发板电源、电脑电源后方可离开。

3.实验报告①按要求认真填写实验报告书;②认真分析实验结果;③按时将实验报告交给老师批阅。

三、实验学生守则1.保持室内整洁,不准随地吐痰、不准乱丢杂物、不准大声喧哗、不准吸烟、不准吃东西;2.爱护公务,不得在实验桌及墙壁上书写刻画,不得擅自删除电脑里面的文件;3.安全用电,严禁触及任何带电体的裸露部分,严禁带电接线和拆线;4.任何规章或不按老师要求操作造成仪器设备损坏须论价赔偿。

目录实验一Uart通用串口接口的设计 (4)实验二PS/2接口的设计 (28)实验三VGA显示接口设计 (30)附录一 basys 2开发板资料 (36)实验一 Uart串口控制接口电路的设计一、实验目的1.掌握分频模块的设计方法。

可编程逻辑器件FPGA实验指导书

可编程逻辑器件(FPGA)实验指导书北京航空航天大学电工电子中心2014-10-22目录一、可编程逻辑器件概述 (1)1.1可编程逻辑器件发展及应用意义 (1)1.2可编程逻辑器件FPGA/CPLD结构简介 (1)二、可编程逻辑器件应用实质和编程原则 (6)2.1选择可编程逻辑器件的实质(或目的或目标) (6)2.2可编程逻辑器件设计流程 (6)2.3硬件描述语言分类 (8)三、VHDL程序设计基本结构 (9)3.1实体(ENTITY) (9)3.2结构体(ARCHITECTURE) (11)3.3子程序(FUNCTION PROCEDURE) (12)3.4集合包(PACKAGE) (13)3.5库(LIBRARY) (14)3.6配置(CONGIFURATION) (15)四、VHDL语法和语句简介 (16)4.1数据类型 (16)1、标准数据类型 (16)2、标准逻辑类型 (16)3、用户自定义数据类型 (16)4.2VHDL语言运算符 (17)1、基本运算符 (17)2、关系运算符 (17)3、算术运算符 (17)4、其他运算符 (18)4.3赋值语句 (18)4.4 IF语句 (19)4.5 CASE语句 (20)4.6进程(PROCESS)语句 (21)4.7并行过程调用语句CONCURRENT PROCEDURE CALLS STATEMENT (23)1、并行信号赋值语句 (23)2、条件信号赋值语句 (23)3、选择信号赋值语句 (24)4.8元件例化语句 COMPONENT I NSTANTIATIONS (24)4.9 LOOP语句 (26)4.10跳出循环语句(NEXT、EXIT语句) (27)4.11 RETURN语句 (27)4.12 NULL语句 (28)五、状态机 (29)5.1、状态机类型定义语句 (29)5.2时序电路时钟的表述方法 (31)六、实验篇 (33)6.1、门电路系列实验(任选一个实验) (36)6.2、组合逻辑系列实验(任选一个实验) (36)6.3、触发器系列实验(任选一个实验,规则自已分析确定) (36)6.4、时序逻辑系列实验(任选一个实验,规则自已分析确定) (36)6.5、存储器设计系列实验(任选一个实验,规则自已分析确定) (37)6.6、状态机逻辑系列实验(任选一个实验) (37)6.7、综合系统逻辑系列实验(任选一个实验,规则自已分析确定) (37)七、FPGA实验平台简介 (38)7.1、A LTERA FPGA EP1C6Q240特性 (38)1、Cyclone系列器件特性 (38)2、Cyclone系列器件可选封装和I/O引脚数 (39)3、Cyclone 系列器件I/O Banks布局图 (39)4、Cyclone device IOEs 支持标准接口 (39)5、Cyclone FPGA EP1C6Q240器件特点 (40)6、Cyclone EP1C6(12)Q模块分布图 (40)7、Cyclone EP1C6Q资源分配 (40)8、Cyclone EP1C6240C8引脚布局图 (41)7.2、实验平台硬件接口电路功能 (45)1、电源单元 (46)2、输入单元 (46)3、输出单元 (46)4、接口单元 (47)5、扩展单元 (47)7.3、输入有源信号 (47)1、电源 (47)2、逻辑电平输入信号——8bit DIP 开关×3 (47)3、单脉冲输入信号 (48)4、连续脉冲输入信号 (49)5、4X4键盘输入信号 (50)7.4、显示方式(供输出信号选择不同显示效果) (51)1、LED显示方式 (51)2、七段数码管显示方式 (52)3、米字型数码管显示方式 (53)4、8X8点阵显示方式 (54)5、LCD显示方式 (55)7.5、实验平台FPGA EP1C6Q240C8引脚与负载区各接口电路之间对应关系 (56)7.6、集成开发环境使用 (57)1、文本编辑源程序文件步骤 (58)2、原理图和图表模块编辑步骤 (83)3、混合编辑(自底向上)步骤 (103)4、混合编辑(自顶向下)步骤 (103)一、可编程逻辑器件概述1.1可编程逻辑器件发展及应用意义可编程逻辑器件发展--从PROM(Programmable Read Only Memory)、PLA(Programmable Logic Array)、PAL(Programmable Array Logic)、可重复编程的GAL(Generic Array Logic)、到采用大规模集成电路技术的EPLD(Erasable Programmable Logic Device),直到CPLD(Complex Programmable Logic Device)和FPGA(Field Programmable Gate Array)。

FPGA方向课程设计指导书(2013)

《电子系统设计》方向组方向课程设计指导书电子系统设计方向组编中原工学院电子信息教研室2011年12月1日前言电子信息类基础专业课程主要包括《模拟电子技术》、《数字电子技术》、《微机原理与应用》、《单片机原理与应用》、《信号与系统》、《数字信号处理》、《EDA基础》等。

电子系统设计方向在原有基础课程上增加了《集成电路原理与应用》、《FPGA系统设计与应用》及《锁相技术》等专业课程。

《数字信号处理》是电子信息工程、通信工程专业的一门重要的理论性和实践性都很强的专业必修课,目的是让学生了解数字信号处理的基本理论、基本分析方法、基本算法和基本实现方法。

包括离散时间LSI系统的理论及其时域、频域分析方法,DFT算法,FFT算法,以及IIR、FIR滤波器的结构和设计方法,为后续课程的学习和工作实践打下理论基础。

《集成电路原理与应用》是一门应用性较强的专业课程,是研究模拟和数字集成电路的器件和电路结构、工作原理以及设计方法的学科,本课程应用半导体器件等基础知识,在模拟电子技术与数字电子技术等课程内容的基础上进一步深入学习,目的是培养学生掌握集成电路的设计方法, 培养学生分析、解决电子系统基本问题和能力。

《FPGA系统设计与应用》是一门发展十分迅速、应用非常广泛的前沿交叉学科,由于高密度现场可编程逻辑器件(CPLD/FPGA)和专用集成电路的飞速发展,传统的设计技术已经不适合大规模及超大规模集成电路,FPGA技术正是为了适应现代电子产品设计的要求,吸收多学科最新成果而形成的一门新技术。

课程目的是使学生了解FPGA的内部原理、结构,并学会利用EDA开发工具进行电子系统的设计,以及在信号、通信领域方面的应用。

为了帮助学生深入理解和消化基本理论、进一步提高综合应用能力并且锻炼独立解决问题的能力,我们将《数字信号处理》、《集成电路原理与应用》和《FPGA系统设计与应用》几门课程融合在一起开设的FPGA综合实验课程设计。

计算机组成原理FPGA实验指导书

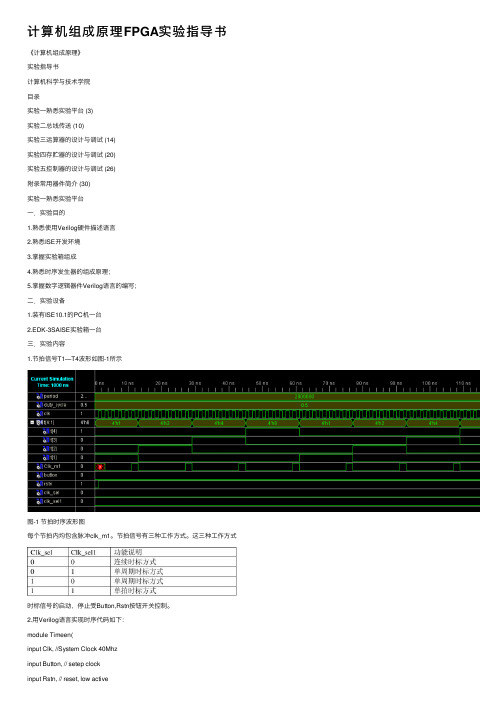

计算机组成原理FPGA实验指导书《计算机组成原理》实验指导书计算机科学与技术学院⽬录实验⼀熟悉实验平台 (3)实验⼆总线传送 (10)实验三运算器的设计与调试 (14)实验四存贮器的设计与调试 (20)实验五控制器的设计与调试 (26)附录常⽤器件简介 (30)实验⼀熟悉实验平台⼀.实验⽬的1.熟悉使⽤Verilog硬件描述语⾔2.熟悉ISE开发环境3.掌握实验箱组成4.熟悉时序发⽣器的组成原理;5.掌握数字逻辑器件Verilog语⾔的编写;⼆.实验设备1.装有ISE10.1的PC机⼀台2.EDK-3SAISE实验箱⼀台三.实验内容1.节拍信号T1—T4波形如图-1所⽰图-1 节拍时序波形图每个节拍内均包含脉冲clk_m1。

节拍信号有三种⼯作⽅式。

这三种⼯作⽅式时标信号的启动,停⽌受Button,Rstn按钮开关控制。

2.⽤Verilog语⾔实现时序代码如下:module Timeen(input Clk, //System Clock 40Mhzinput Button, // setep clockinput Rstn, // reset, low activeinput Clk_sel, // sequence timing or step timing select input Clk_sel1, output [4:1] t, // Display(T1-T4)output M1);wire Clk_m1;wire Clk_i,Clk_ii;wire PB_R;assign M1=Clk_m1;GenClk_i Clk_i_Module (.Clk_s(Clk),.Clk_i(Clk_i),.Rstn(Rstn));GenClk_ii Clk_ii_Module (.PB_R(PB_R),.Clk(Clk),.Clk_ii(Clk_ii));Debouncer Debouner_Module (.Clk_s(Clk),.PB(Button),.PB_state(),.PB_up(PB_R),.PB_down());ClkSel ClkSel_Module (.Clk_s(Clk),.Clk_i(Clk_i),.Clk_ii(Clk_ii),.Clk_m1(Clk_m1),.Clk_sel(Clk_sel),.Clk_sel1(Clk_sel1));Bit1_Display Bit1_Display_Module (.Clk_s(Clk),.Clk_m1(Clk_m1),.T(t),.Rstn(Rstn),.Clk_i(Clk_i));endmodulemodule GenClk_i(input Clk_s,output Clk_i,input Rstn);reg [24:0] Cnt;assign Clk_i= Cnt[24];always@(posedge Clk_s or negedge Rstn) beginif (!Rstn)Cnt<=0;elseCnt <= Cnt + 1;endendmodulemodule GenClk_ii(input PB_R,input Clk,output Clk_ii);reg Clk_o,Clk_o1,Clk_o2;assign Clk_ii=Clk_o2;always@(posedge Clk )beginClk_o<=PB_R;Clk_o1<=Clk_o;Clk_o2<=Clk_o1;endendmodulemodule Debouncer(Clk_s, PB, PB_state, PB_up, PB_down);input Clk_s; // "clk" 时钟信号input PB; // "PB" 有⽑刺的、异步的、低有效的按键信号output PB_state; // 当按键被按下时输出1output PB_down; // 按键被按下的瞬间输出⼀个⾼电平脉冲output PB_up; // 按键被松开的瞬间输出⼀个⾼电平脉冲// ⾸先使⽤两个触发器来同步PB信号reg PB_sync_0;always @(posedge Clk_s)PB_sync_0 <= ~PB; // 翻转PB,使之⾼有效reg PB_sync_1;always @(posedge Clk_s) PB_sync_1 <= PB_sync_0;// 声明⼀个16位的剖?reg [21:0] PB_cnt;// 当按键被按下或松开时,计数?// 当计数器计数溢出时,便认为按键的状态确定。

FPGA实验指导书2

实验四:状态机一、 实验目的1.对有限状态机(FSM)做初步了解。

二、 实验内容1.Gray编码和One-hot编码两种状态机;2.触发器部分和组合逻辑部分结合与分开两种状态机。

三、 实验要求1.对程序中状态和输出稍作修改,在Quartus II 环境下进行时序仿真;2.学会利用状态机编写一个流水灯程序;3.下载至实验板,观察结果。

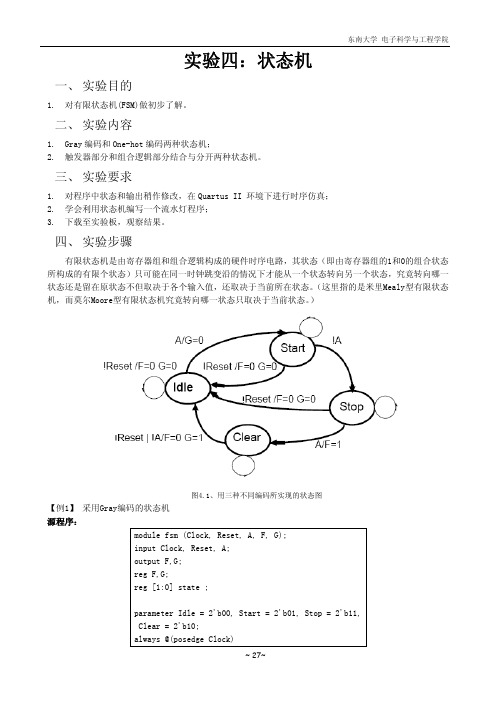

四、 实验步骤有限状态机是由寄存器组和组合逻辑构成的硬件时序电路,其状态(即由寄存器组的1和0的组合状态所构成的有限个状态)只可能在同一时钟跳变沿的情况下才能从一个状态转向另一个状态,究竟转向哪一状态还是留在原状态不但取决于各个输入值,还取决于当前所在状态。

(这里指的是米里Mealy型有限状态机,而莫尔Moore型有限状态机究竟转向哪一状态只取决于当前状态。

)图4.1、用三种不同编码所实现的状态图【例1】 采用Gray编码的状态机源程序:module fsm (Clock, Reset, A, F, G);input Clock, Reset, A;output F,G;reg F,G;reg [1:0] state ;parameter Idle = 2'b00, Start = 2'b01, Stop = 2'b11,Clear = 2'b10;always @(posedge Clock)beginif (!Reset)beginstate <= Idle; F<=0; G<=0;endelse begincase (state)Idle: beginif (A) beginstate <= Start;G<=0;endelse state <= Idle;endStart: beginif (!A) state <= Stop;else state <= Start;endStop: beginif (A) beginstate <= Clear;F <= 1;endelse state <= Stop;endClear: beginif (!A) beginstate <=Idle;F<=0; G<=1;endelse state <= Clear;endendcaseendendendmodule【例2】采用One-hot编码的状态机源程序:module fsm (Clock, Reset, A, F, G);input Clock, Reset, A; output F,G;reg F,G;reg [3:0] state ;parameter Idle = 4'b1000,Start = 4'b0100,Stop = 4'b0010,Clear = 4'b0001;always @(posedge Clock)beginif (!Reset)beginstate <= Idle; F<=0; G<=0;endelsebegincase (state)Idle: beginif (A) beginstate <= Start;G<=0;endelse state <= Idle;endStart: beginif (!A) state <= Stop;else state <= Start;endStop: beginif (A) beginstate <= Clear;F <= 1;endelse state <= Stop;endClear: beginif (!A) beginstate <=Idle;F<=0; G<=1;endelse state <= Clear;enddefault: state <=Idle;endcaseendendendmodule例1中采用Gray编码,例2中采用的是One-hot编码。

电子系统设计实验指导书(FPGA基础篇Vivado版)

东南大学 电子科学与工程学院

安全使用规范

无论何时,外部电源供电与 USB 两种供电方式只能用其中一种,避免因为电压有所差别而烧坏电路板。 采用电压高于5.5V的任何电源连接器可能造成永久性的损害。 插拔接插件前请关闭电路板总开关,否则易损坏器件。 电路板应在绝缘平台上使用,否则可能引起电路板损坏。 不同编码机制不要混接。 安装设备需防止静电。 液晶显示器件或模块结雾时,不要通电工作,防止电极化学反应,产生断线。 遇到正负极连接时需谨慎,避免接反引起开发板的损坏。 保持电路板的表面清洁。 小心轻放,避免不必要的硬件损伤。

2

东南大学 电子科学与工程学院

assign c2=a|b; assign c3=~a; assign c4=~(a&b); assign c5=~(a|b); assign c6=a^b; endmodule 寄存器传输描述方式源程序: module gate(a,b,c1,c2,c3,c4,c5,c6); input a,b; output c1,c2,c3,c4,c5,c6; reg c1,c2,c3,c4,c5,c6; always@(a or b) begin case({a,b}) 2'b00: begin c1<=0;c2<=0;c3<=1;c4<=1;c5<=1;c6<=0; end 2'b01: begin c1<=0;c2<=1;c3<=1;c4<=1;c5<=0;c6<=1; end 2'b10: begin c1<=0;c2<=1;c3<=0;c4<=1;c5<=0;c6<=1; end 2'b11: begin c1<=1;c2<=1;c3<=0;c4<=0;c5<=0;c6<=0; end default: begin c1<=0;c2<=0;c3<=0;c4<=0;c5<=0; c6<=0; end endcase end endmodule (1) 进行语法检查和综合编译。 (2) 编写 testbench,进行时序仿真。

FPGA设计与应用实验指导书-v2

FPGA设计与应用实验指导书实验一Quartus II开发软件入门一、实验目的1. 熟悉Quartus II 开发软件的基本使用方法2. 掌握用VHDL语言设计组合逻辑电路的方法二、实验内容1. 运用Quartus II 开发软件,完成工程创建、代码编写、程序调试、编译仿真等基本操作。

2. 用VHDL语言设计实现一个3-8译码器,并进行功能仿真验证。

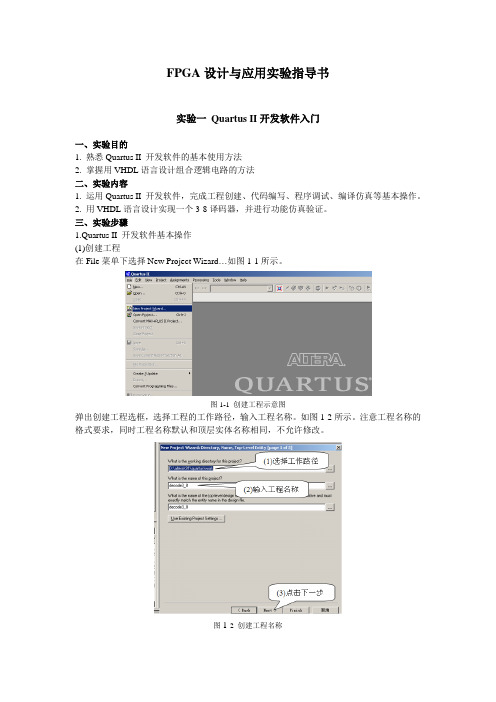

三、实验步骤1.Quartus II 开发软件基本操作(1)创建工程在File菜单下选择New Project Wizard…如图1-1所示。

图1-1 创建工程示意图弹出创建工程选框,选择工程的工作路径,输入工程名称。

如图1-2所示。

注意工程名称的格式要求,同时工程名称默认和顶层实体名称相同,不允许修改。

图1-2 创建工程名称可选择添加已有的程序文件,如图1-3所示。

这里不添加,直接下一步。

图1-3 添加文件选框选择芯片系列和芯片型号,如图1-4所示。

实验中使用的是Altera公司的Cyclone II系列FPGA 芯片,型号为EP2C35F672C6。

如果不进行硬件下载,可直接下一步。

图1-4 芯片参数选框EDA外部工具选框如图1-5所示。

一般选择默认值,直接下一步。

图1-5 EDA外部工具选框完成工程设置后的工程信息如图1-6所示。

图1-6 工程信息选框至此完成工程的创建。

(2)新建VHDL文件在File菜单下选择New选项,如图7所示。

图1-7新建文件示意图点击新建菜单后给出新建文件选框如图1-8所示。

选择VHDL File项创建VHDL文件。

图1-8 新建VHDL文件选框确定后弹出新建VHDL文件编辑窗口如图1-9所示。

可在窗口中编写程序内容并保存,注意文件名称与工程实体名称必须一致。

图1-9 VHDL文件编辑窗口至此完成VHDL文件的创建和VHDL程序的编写。

(3) 程序编译程序编写完成后,选择Processing菜单下的编译工具(Compiler Tool)菜单,如图1-10所示,调出编译工具。

FPGA及其应用实验指导书

FPGA及其应用实验指导书前言近些年来,FPGA技术发展迅速。

一方面,各种大容量、高性能、低功耗的FPGA器件不断推出,使得专用集成电路(ASIC)的生产商感受到空前的竞争压力。

另一方面,出现了许多FPGA设计辅助工具,这些工具大大提高了新型集成电路的设计效率,使更低成本、更短周期的复杂数字系统开发成为可能。

于是一场ASIC与FPGA之争在所难免。

然而FPGA器件具有先天的竞争优势,那就是可以反复编程,在线调试。

FPGA仿真技术正是这场较量的推动引擎之一。

一般来说,FPGA仿真技术就是以计算机为平台,以FPGA仿真软件工具为开发环境,以HDL为设计语言,以FPGA芯片为目标器件,以电子系统设计为应用方向的电子产品自动化设计过程。

设计者只需编写硬件描述语言代码,然后选择目标器件,在集成开发环境里进行编译,仿真,综合,最后在线下载调试。

整个过程,大部分工作由FPGA设计软件完成。

全球许多著名的可编程器件提供商都推出了自己的集成开发工具软件,如Altera公司的QuartusⅡ软件;Xilinx公司的ISE软件等。

这些软件的推出,极大地促进了集算法设计、芯片编程、电路板设计于一体的新型电子系统技术的发展。

另外,在以SOC芯片为目标器件的电子系统设计要求下,可编程器件的内部开始集成高速的处理器硬核、处理器软核、DSP模块、大量的存储资源、高速的串行收发模块、系统时钟管理器、多标准的I/O接口模块,亦使得设计者更加得心应手,新一轮的数字革命由此引发。

FPGA技术是一门实践性很强的学科,要培养出具有竞争力的一流IC设计人才,动手能力是关键。

只有通过理论学习,加上现场实验,在使用软件编程加硬件调试的过程中真正获得锻炼,增长技能。

UP2实验系统采用灵活结构,可方便进行基于CPLD/FPGA芯片的实验开发,并易于升级,符合当前高校在此方面对人才培养的要求。

我们相信,只要学生扎扎实实完成本实验系统的所有实验,并在此基础上利用现有硬件资源开发出新的数字应用系统,学生的潜力会得到最大程度的发挥,对FPGA技术的学习也会有质的飞跃,从而为推动我国数字系统设计技术的发展做出更大的贡献。

FPGA实验仪指导书(1~3章加附录)

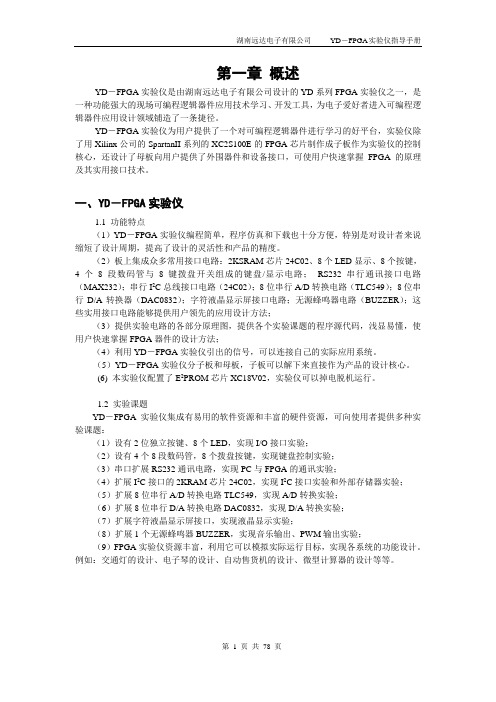

第一章概述YD-FPGA实验仪是由湖南远达电子有限公司设计的YD系列FPGA实验仪之一,是一种功能强大的现场可编程逻辑器件应用技术学习、开发工具,为电子爱好者进入可编程逻辑器件应用设计领域铺造了一条捷径。

YD-FPGA实验仪为用户提供了一个对可编程逻辑器件进行学习的好平台,实验仪除了用Xilinx公司的SpartanII系列的XC2S100E的FPGA芯片制作成子板作为实验仪的控制核心,还设计了母板向用户提供了外围器件和设备接口,可使用户快速掌握FPGA的原理及其实用接口技术。

一、YD-FPGA实验仪1.1 功能特点(1)YD-FPGA实验仪编程简单,程序仿真和下载也十分方便,特别是对设计者来说缩短了设计周期,提高了设计的灵活性和产品的精度。

(2)板上集成众多常用接口电路:2KSRAM芯片24C02、8个LED显示、8个按键,4个8段数码管与8键拨盘开关组成的键盘/显示电路;RS232串行通讯接口电路(MAX232);串行I2C总线接口电路(24C02);8位串行A/D转换电路(TLC549);8位串行D/A转换器(DAC0832);字符液晶显示屏接口电路;无源蜂鸣器电路(BUZZER);这些实用接口电路能够提供用户领先的应用设计方法;(3)提供实验电路的各部分原理图,提供各个实验课题的程序源代码,浅显易懂,使用户快速掌握FPGA器件的设计方法;(4)利用YD-FPGA实验仪引出的信号,可以连接自己的实际应用系统。

(5)YD-FPGA实验仪分子板和母板,子板可以解下来直接作为产品的设计核心。

(6) 本实验仪配置了E2PROM芯片XC18V02,实验仪可以掉电脱机运行。

1.2 实验课题YD-FPGA实验仪集成有易用的软件资源和丰富的硬件资源,可向使用者提供多种实验课题:(1)设有2位独立按键、8个LED,实现I/O接口实验;(2)设有4个8段数码管,8个拨盘按键,实现键盘控制实验;(3)串口扩展RS232通讯电路,实现PC与FPGA的通讯实验;(4)扩展I2C接口的2KRAM芯片24C02,实现I2C接口实验和外部存储器实验;(5)扩展8位串行A/D转换电路TLC549,实现A/D转换实验;(6)扩展8位串行D/A转换电路DAC0832,实现D/A转换实验;(7)扩展字符液晶显示屏接口,实现液晶显示实验;(8)扩展1个无源蜂鸣器BUZZER,实现音乐输出、PWM输出实验;(9)FPGA实验仪资源丰富,利用它可以模拟实际运行目标,实现各系统的功能设计。

FPGA实验指导书

图2-10利用一位全加器设计四位全加器

图2-14利用Pin/Location/Chip进行I/O锁定(1)

以s0的锁定为例介绍跳出界面的各部分功能,如下图所示:

图2-15利用Pin/Location/Chip进行I/O锁定(2)

Node Name框的使用:该框中输入将要锁定的I/O的名称如S0,如果需要查询输入、输出等类型,可以单击Search按扭,跳出的对话框如下图所示。

2)注意学习软件与动手练习相配合,只有多动手设计与调试才能真正掌握设计思想与设计方法。

3)多参考相关的书籍或MAX+PLUSⅡ的帮助系统。

4)在学习过程中要与数字电路、计算机语言等课程进行比较,找出相同点与不同点,进行比较、类比地学习。

5)概念的区分与使用:

器件与符号:如在数字电路中7400为一个器件,在MAX+PLUSⅡ中器件一般被CPLD/FPGA器件专用,而MAX+PLUSⅡ中调用的中小规模的器件都称为符号。本文中有时出于习惯,也会在该使用“符号”的地方而使用“器件”名称,因此在碰到像“器件”、“符号”这样的词,一定要注意上下文的联系。

在Chip Resource组框中选择合适的类型,如本例s0选择Pin单选扭,并在输入框中输入104,表示s0被锁定到特定CPLD器件的104号管脚。点击ADD按扭即可完成操作。

图2-7鼠标双击空白处后的编辑界面

3.MAX+USⅡ的符号库

2013版实验指导书DOC

目录实验一、QUARTUS II的基本应用及简单组合逻辑设计 (1)实验二、计数器设计 (3)实验三、跑马灯控制电路设计 (6)实验四、8位乘法器的实现 (8)实验五、数字钟的设计 (10)实验六、8人抢答器设计 (12)实验一、QUARTUS II的基本应用及简单组合逻辑设计一、实验前准备本实验例子使用独立扩展下载板EP1K10_30_50_100QC208(芯片为EP1K100QC208或者芯片为EP1K30TC144)。

EDAPRO/240H实验仪主板的VCCINT跳线器右跳设定为3.3V;EDAPRO/240H实验仪主板的VCCIO跳线器组中“VCCIO3.3V”应短接,其余VCCIO均断开;独立扩展下载板“EP1K10_30_50_100QC208”的VCCINT跳线器组设定为2.5V;独立扩展下载板“EP1K10_30_50_100QC208”的VCCIO跳线器组设定为3.3V。

二、实验目的1、熟悉Quartus II的菜单、元件库、功能模块及基本应用操作;2、熟悉Quartus II的Verilog HDL文本方式及原理图方式设计实现流程。

3、学习使用JTAG接口下载逻辑电路到可编程逻辑器件并能调试到正常工作。

4、熟悉数字电路集成设计的过程。

三、实验内容1、用Verilog HDL文本方式设计带使能控制的3-8译码器;三、实验原理1、3-8译码器:译码器是把输入的数码解出其对应的数码,译码器有N个二进制选择线,那么最多可译码转换成2N个数据。

当一个译码器有N条输入线及M条输出线时,则称为N×M的译码器。

3×8译码器是依此而来。

3×8译码器真值表如下表所示:四、实验步骤新建设计文件夹(不可用中文)-》新建设计文件-》输入设计项目(原理图/Verilog HDL 文本代码)-》存盘(注意原理图/文本取名)-》将设计项目设置成Project-》选择目标器件-》启动编译-》建立仿真波形文件-》仿真测试和波形分析-》引脚锁定并编译-》编程下载/配置-》硬件测试五、硬件测试说明1、把译码器的输入接到拨码开关,使能控制端接按键,输出端接8个LED灯,通过拨码开关改变输入的逻辑电平变化来观察LED输出情况,验证3×8译码器的工作状态。

FPGA实验指导

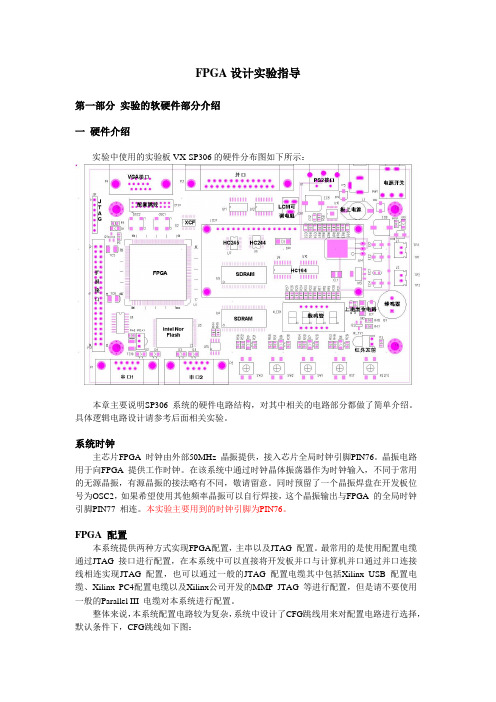

FPGA设计实验指导第一部分实验的软硬件部分介绍一硬件介绍实验中使用的实验板VX-SP306的硬件分布图如下所示:本章主要说明SP306 系统的硬件电路结构,对其中相关的电路部分都做了简单介绍。

具体逻辑电路设计请参考后面相关实验。

系统时钟主芯片FPGA 时钟由外部50MHz 晶振提供,接入芯片全局时钟引脚PIN76。

晶振电路用于向FPGA 提供工作时钟。

在该系统中通过时钟晶体振荡器作为时钟输入,不同于常用的无源晶振,有源晶振的接法略有不同,敬请留意。

同时预留了一个晶振焊盘在开发板位号为OSC2,如果希望使用其他频率晶振可以自行焊接,这个晶振输出与FPGA 的全局时钟引脚PIN77 相连。

本实验主要用到的时钟引脚为PIN76。

FPGA 配置本系统提供两种方式实现FPGA配置,主串以及JTAG 配置。

最常用的是使用配置电缆通过JTAG 接口进行配置,在本系统中可以直接将开发板并口与计算机并口通过并口连接线相连实现JTAG 配置,也可以通过一般的JTAG 配置电缆其中包括Xilinx USB 配置电缆、Xilinx PC4配置电缆以及Xilinx公司开发的MMP_JTAG 等进行配置,但是请不要使用一般的Parallel III 电缆对本系统进行配置。

整体来说,本系统配置电路较为复杂,系统中设计了CFG跳线用来对配置电路进行选择,默认条件下,CFG跳线如下图:从左边开始的前四组跳线用来连接板上并口JTAG 电路与FPGA 的JTAG 电路;在这种情况下,FPGA 工作在主串模式。

对开发板加电后,FPGA 将从XCF02S 中读取配置数据对自己进行配置。

如果需要开发自己的示例程序并下载到板上进行测试,需要将CFG跳线做如下调整,在这种情况下,FPGA 工作在JTAG 模式,这时可以对FPGA中写入新的数据,写入的数据在FPGA掉电后将需要重新进行配置。

(注意在后面的实验中CFG跳线都接成这种模式)本系统还提供通过平台FLASH进行(Platform Flash In-System Programmable Configuration PROMs )对FPGA进行配置,配置模式为主串模式,在这个配置模式中FPGA 从FLASH(XCF) 中读取数据对自己进行配置。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《FPGA设计》实验指导书安全操作注意事项1、接插下载电缆前,请务必关闭实验箱开关,避免损坏下载电缆或实验箱器件。

2、操作过程中应防止静电。

3、保持实验箱和电路板的表面清洁。

4、小心轻放,避免不必要的硬件损伤或者人身受伤。

实验箱简介实验一简单组合逻辑设计一、实验目的和任务1、熟习Quartus II软件的使用;2、掌握用原理图输入法和硬件描述语言(Verilog HDL)两种方法来设计逻辑电路;3、通过电路的仿真及验证,进一步了解4选1数据选择器的功能;二、实验内容1、用原理图输入法来设计4选1数据选择器参照按图1-1所示来编辑完成4选1数据选择器的原理图输入,其中a、b、c、d 为数据输入端,sel[1]、sel[0]为控制输入端,q为4选1数据输出端。

存盘仿真后,观察仿真波形,以验证数据选择器的功能。

图1-1 4选1数据选择器原理图2、用Verilog HDL硬件描述语言来设计4选1数据选择器用QuartusII中的文本编辑器,编辑输入4选1数据选择器源程序:module m41( a, b, c, d, sel, q);input a,b,c,d;input [1:0]sel;output q;reg q;always @( sel)case(sel)2’b00: q=a;2’b01: q=b;2’b11: q=d; endcase endmodule程序中的a 、b 、c 、d 依然为数据输入端,sel[1]、sel[0]为控制输入端,q 为4选1数据输出端。

同样存盘后进行仿真,并观察仿真波形,以验证数据选择器的功能。

三、实验仪器、设备及材料电脑、EDA 软件、实验箱、下载电缆。

四、实验原理4选1数据选择器的原理框图及真值表如图1-2及表1-1所示,sel[1:0]可能出现四种组合情况: 00 01 10 11,它分别对应选通四个不同的数据输入a 、b 、c 、d ,从q 端输出。

结合以前所学数字电路的知识,可由真值表得出利用“与非门”实现的逻辑电路,进而可用QuartusII 原理图输入方法,设计出该4选1数据选择器;如应用EDA 技术所学的Verilog HDL 硬件描述语言来描述该电路功能,即可设计出该4选1数据选择器的源程序。

图1-2 4选1数据选择器的原理框图q Sel[1]输出选择输入0a 01b 00c 11d1Sel[0]表1-1 真值表五、重点、难点da b c件描述语言(Verilog HDL)两种方法来设计该逻辑电路。

其难点是要仿真出4选1数据选择器的波形,然后通过观测仿真波形,来验证该数据选择器的功能。

六、实验步骤(一)原理图输入法的设计步骤:(1)进入Windows 操作系统,双击Quartus II图标,启动软件。

1、单击File \ New Project Wizard菜单,输入文件名路径与设计项目的名字mux41,点击finish, 完成设计项目建立。

点击Assignment \ Device菜单,选择器件(本设计选用cyclone 系列的EP1C12Q240C8)。

2、启动菜单File \ New,选择Block Diagram/Schematic File,点OK,启动原理图编辑器。

画出图1-1(具体方法见后面说明)。

默认存盘名为mux41,保存。

(2)设计的输入1. 在原理图空白处双击,会出现元件选择对话框,在name处输入元件名,点OK完成元件放置。

依次放置4个三输入端与门(and3)、1个四输入端或门(or4),2个非门(not)器件、及6个输入端(input)、1个输入端(output)在原理图上;2. 添加连线到器件的管脚上把鼠标移到元件引脚附近,则鼠标光标自动由箭头变为十字,按住鼠标右键拖动,即可画出连线,参照图1连好相应元件的输入、输出脚。

3.保存原理图单击保存按钮。

原理图文件出现在红色箭头所指的地方。

(3)编译点击菜单栏上红色箭头所指的工具图标,完成编译。

图1-3 编译编译没有错误可以进行仿真。

点击 File \ New菜单。

选择other files中的vector waveform file。

画出输入波形,执行仿真命令,启动仿真并观察仿真波形,进行设计电路的功能验证。

点击开始仿真图1-4 新建波形文件的选择对话框(二)用Verilog HDL语言完成的设计步骤:(1)、运行Quartus II软件,先建立一个新的项目。

;(2)、启动File \ New菜单命令(如图1-5)(3)、选择verilog hdl file,点击OK后,键入上面“二、实验内容”中的程序。

(4)、以默认文件名和路径保存。

(5)参照原理图输入设计进行仿真,并观察仿真波形,以验证所设计电路的功能。

七、实验报告要求1. 对于原理图设计要求有设计过程。

2. 详细论述实验步骤。

八、实验注意事项1. 使用原理图设计时,其文件名[mux41.gdf]要与仿真的波形文件名[mux41.vwf]相同,只是文件的后缀不同;使用Verilog HDL语言设计时,其文件名(m4_1.V)要与模块名[module m4_1( a, b, c, d, sel, q);]相同,且仿真的波形文件名[m4_1.vwf]也要相同。

2. 用原理图输入法和Verilog HDL语言两种方法所做的设计,一定要建两个不同的工程,最好放在不同的目录中,且目录名不要出现中文字符。

3.在Waveform Editor仿真时,应先在菜单选项的Edit/ Grid Size…中所弹出的对话框中将Grid Size:改为1.0us;并菜单选项的Edit/ End Time…中所弹出的对话框中将Grid Size改为100.0us,以方便观察、理解仿真得到的波形。

九、思考题1. 如何用设计好的4选1数据选择器,来实现8选1数据选择器的设计(用原理图输入法来设计),试给出设计与仿真的结果。

2.谈谈使用原理图输入法和Verilog HDL语言设计两种方法的优劣心得。

实验二组合逻辑电路设计一、实验目的1、继续学习Verilog HDL基本语法;2、巩固Quartus II环境下的Verilog HDL编程设计的基础二、主要仪器设备EDA实验系统1台PC机三、实验内容1、设计一个四线至二线编码器,其真值表如下:表2.1 四线至二线编码器的真值表2、设计一个2位信号的比较器,该比较器的电路符号如图2.1所示。

图2.1 比较器电路符号引脚说明:A、B皆为二位信号;CLK为时钟脉冲输入;RST为清除控制信号。

AGTB:当A>B时,其值为1,否则为0;AEQB:当A=B时,其值为1,否则为0;ALTB:当A<B时,其值为1,否则为0;3、设计一个八位全加器。

四、实验报告根据以上实验内容写出实验报告,包括程序设计,软件编译,管脚分配,硬件测试结果等内容。

实验三一般计数器的设计及ModelSim 仿真测试一、实验目的1、掌握一般计数器的设计方法;2、了解ModelSim 仿真测试方法。

二、主要仪器设备EDA实验系统1台PC机三、实验内容1、设计一个8421BCD十进制计数器,并将计数结果在LED或数码管上显示。

2、利用ModelSiml工具进行仿真测试。

四、ModelSim仿真步骤见参考资料《ModelSim操作简介》五、实验报告根据以上实验内容写出实验报告,包括程序设计,软件编译,仿真结果及分析,硬件测试等内容。

实验四时序逻辑电路设计一、实验目的理解触发器和计数器的概念,掌握时序器件的Verilog HDL语言程序设计的方法二、主要仪器设备EDA实验系统1台PC机三、实验内容设计以下内容:1、基本的D触发器;2、同步复位的D触发器;3、异步复位的D触发器;4、同步置位/复位的D触发器;5、设计一个简单的加法或减法计数器,并用LED或数码管显示四、实验报告根据以上实验内容写出实验报告,包括程序设计,管脚分配,用示波器观察D触发器波型;计数器用LED或数码管显示,并提交其仿真结果及分析。

实验五有限状态机(FSM)的设计一、实验目的1、了解FSM的应用范围和两种类型的不同特点;2、掌握FSM的电路结构和设计要点。

二、主要仪器设备EDA实验系统一台三、实验原理FSM适合于设计数字系统的控制模块。

用Verilog HDL的case/if-else等语句能很好地描述基于状态机的设计。

状态机可以认为是组合逻辑和时序逻辑的特殊组合。

时序逻辑部分用于存贮状态,组合电路用于状态译码和产生输出信号。

状态机的下一个状态不仅与输入信号有关,还与状态寄存器当前所处的状态有关。

状态机分为Mealy和Moore两种类型,前者的输出只是当前状态的函数,也就是状态的转换与输入信号无关,后者的输出则是当前状态和当前输入的函数,即状态的转换与输入信号有关。

状态机的表示方法:状态图、状态表和流程图。

四、实验内容检测一个5位二进制序列“10010”五、实验报告根据以上实验内容写出实验报告,包括程序设计,软件编译,仿真结果及分析,硬件测试等内容。

实验六基于模块多层次引用的结构化电路设计一、实验目的1、了解复杂电路与系统的“top-down”设计思想;2、掌握简单多层次电路的描述方法。

二、主要仪器设备EDA/SOPC实验系统1台三、实验原理1、多层次结构电路的设计复杂数字系统可采用“top-down”的方法进行设计:首先把系统分为几个模块,每个模块在分为几个子模块,依次类推,知道易于实现为止。

这种“top-down”的方法能够把复杂的设计分为许多简单的设计来实现,同时也适合于多人进行合作开发。

多层次结构电路的描述既可以采用文本方式,也可以采用图形和文本混合设计的方式。

被调用模块的指定方式:1)文件复制方式;2)使用`include语句;3)库管理方式。

2、设计实例分析这个实例的功能是将并行数据转化为串行数据送交外部电路编码,并将解码后得到的串行数据转化为并行数据交由CPU处理。

显而易见,这实际上是两个独立的逻辑功能,分别设计为独立的模块,然后再合并为一个模块显得目的明确、层次清晰。

模块源代码// ---------------- p_to_s.v ---------------------------------module p_to_s(D_in,T0,data,SEND,ESC,ADD_100);output D_in,T0; // D_in是串行输出,T0是移位时钟并给// CPU中断,以确定何时给出下个数据。

input [7:0] data; //并行输入的数据。

input SEND,ESC,ADD_100; //SEND、ESC共同决定是否进行并到串//的数据转化。

ADD_100决定何时置数。

wire D_in,T0;reg [7:0] DATA_Q,DATA_Q_buf;assign T0 = ! (SEND & ESC); //形成移位时钟。