常用存储器芯片设计指南

I2C总线芯片AT24C02程序设计

I2C总线芯片AT24C02程序设计I2C总线芯片AT24C02是一种常用的存储器芯片,在嵌入式系统中广泛应用。

本文将介绍如何使用AT24C02进行程序设计,包括芯片初始化、读取数据和写入数据等操作。

为了简化整个流程,本文将只介绍关键的代码部分。

首先,我们需要了解AT24C02芯片的连接方式和寄存器地址。

AT24C02通过I2C总线连接到控制器,其中使用两根信号线SCL和SDA进行通信。

芯片的I2C地址为0xA0,并且有256个存储器单元,每个单元8位,总共可以存储2KB的数据。

接下来,我们需要进行芯片的初始化。

初始化过程包括初始化I2C总线、设置AT24C02的I2C地址和其他必要的配置。

以下是AT24C02初始化的代码示例:```c#include <Wire.h>#define AT24C02_ADDRESS 0xA0 // AT24C02芯片的I2C地址void setupWire.begin(; // 初始化I2C总线void loop//主程序代码```在进行读取数据之前,我们需要指定要读取的存储器单元的地址,并将其发送给AT24C02芯片。

以下是读取数据的代码示例:```c#include <Wire.h>#define AT24C02_ADDRESS 0xA0 // AT24C02芯片的I2C地址#define MEMORY_ADDRESS 0x00 // 要读取的存储器单元的地址void setupWire.begin(; // 初始化I2C总线Wire.beginTransmission(AT24C02_ADDRESS); // 开始I2C通信Wire.write(MEMORY_ADDRESS); // 发送存储器单元的地址Wire.endTransmission(; // 结束I2C通信void loop//主程序代码```在进行写入数据之前,我们需要指定要写入的存储器单元的地址,并将数据发送给AT24C02芯片。

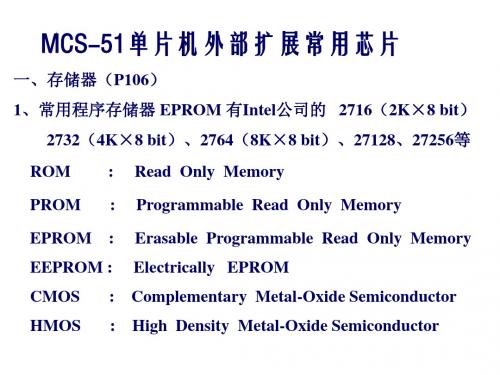

ROM存储器内涵EPROM2716存储器地介绍

课 堂 教 学 实 施 方 案课 题:只读存储器ROM 、主存储器的设计5.3 只读存储器ROM指在微机系统的在线运行过程中,只能对其进行读操作,而不能进行写操作的一类存储器,在不断发展变化的过程中,ROM 器件也产生了掩模ROM 、PROM 、EPROM 、EEPROM 等各种不同类型。

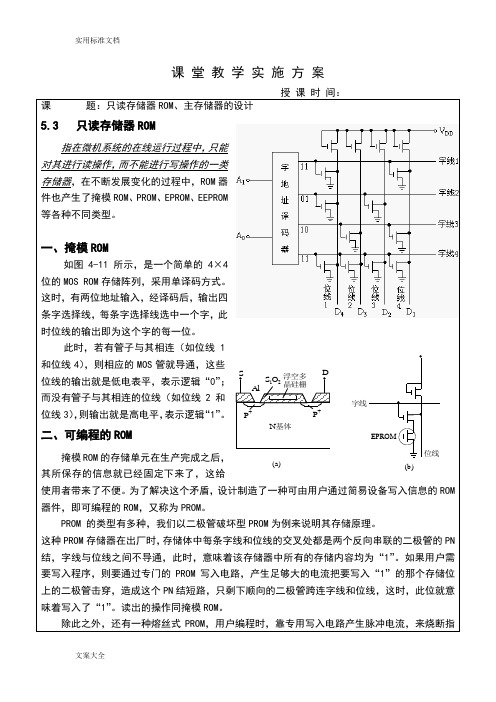

一、掩模ROM如图4-11所示,是一个简单的4×4位的MOS ROM 存储阵列,采用单译码方式。

这时,有两位地址输入,经译码后,输出四条字选择线,每条字选择线选中一个字,此时位线的输出即为这个字的每一位。

此时,若有管子与其相连(如位线1和位线4),则相应的MOS 管就导通,这些位线的输出就是低电表平,表示逻辑“0”;而没有管子与其相连的位线(如位线2和位线3),则输出就是高电平,表示逻辑“1”。

二、可编程的ROM掩模ROM 的存储单元在生产完成之后,其所保存的信息就已经固定下来了,这给使用者带来了不便。

为了解决这个矛盾,设计制造了一种可由用户通过简易设备写入信息的ROM器件,即可编程的ROM ,又称为PROM 。

PROM 的类型有多种,我们以二极管破坏型PROM 为例来说明其存储原理。

这种PROM 存储器在出厂时,存储体中每条字线和位线的交叉处都是两个反向串联的二极管的PN 结,字线与位线之间不导通,此时,意味着该存储器中所有的存储内容均为“1”。

如果用户需要写入程序,则要通过专门的PROM 写入电路,产生足够大的电流把要写入“1”的那个存储位上的二极管击穿,造成这个PN 结短路,只剩下顺向的二极管跨连字线和位线,这时,此位就意味着写入了“1”。

读出的操作同掩模ROM 。

除此之外,还有一种熔丝式PROM ,用户编程时,靠专用写入电路产生脉冲电流,来烧断指P +P +A lS i O 2SD浮空多晶硅栅N 基体字线EPROM(a)(b)位线实用标准文档文案大全。

一名芯片设计工程师的书单

一名芯片设计工程师的书单作为一名芯片设计工程师,我一直都对我的专业充满了热情和好奇心。

在这个快速发展的行业中,学习和保持更新是非常重要的。

为了不断提升自己的技能和知识水平,我经常阅读各种与芯片设计相关的书籍。

下面是我个人的书单推荐,希望对同行们有所帮助。

1.《芯片设计导论》:这本书是芯片设计的入门指南,全面介绍了芯片设计的基本概念、流程和方法。

它以简单易懂的语言解释了复杂的技术,适合初学者阅读。

2.《数字集成电路设计与实践》:这本书详细介绍了数字集成电路的设计原理和方法。

它涵盖了从逻辑门到完整数字系统的设计过程,包括电路设计、时序分析和布局布线等内容。

3.《模拟集成电路设计与实践》:与数字集成电路设计不同,模拟集成电路设计更注重信号处理和电路性能的优化。

这本书深入浅出地介绍了模拟电路设计的基本原理和技术,以及常见的设计方法和工具。

4.《射频集成电路设计与实践》:射频集成电路设计是一门高度专业化的领域,需要掌握特定的设计技术和工具。

这本书系统地介绍了射频电路设计的原理、方法和实践经验,对于从事射频电路设计的工程师来说是一本不可或缺的参考书。

5.《数字信号处理与应用》:数字信号处理在现代芯片设计中起着重要的作用,它涉及到信号采集、滤波、编解码等方面的技术。

这本书对数字信号处理的基本原理和常见应用进行了详细介绍,非常适合对于数字信号处理感兴趣的工程师阅读。

6.《半导体物理与器件基础》:作为芯片设计工程师,了解半导体物理和器件基础是非常重要的。

这本书系统地介绍了半导体物理学的基本原理、晶体生长技术和半导体器件的特性及应用,对于理解芯片工作原理和优化设计具有重要意义。

7.《芯片设计中的可靠性考虑》:芯片设计中的可靠性是一个重要的问题,它关系到芯片的寿命和性能稳定性。

这本书介绍了芯片设计中的可靠性考虑和相关的测试方法,帮助工程师提高芯片的可靠性和稳定性。

8.《面向对象的芯片设计方法》:面向对象的设计方法在软件工程中得到了广泛应用,而在芯片设计领域也有着重要的意义。

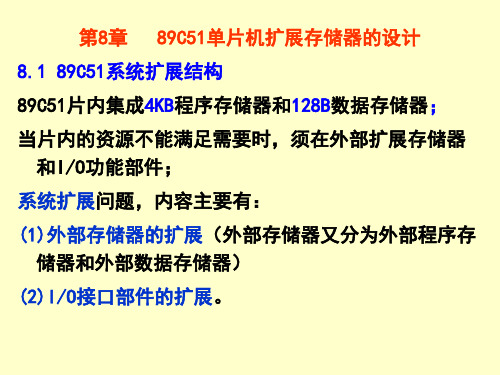

第8章 89C51单片机扩展存储器的设计

8.2 8.2

地址空间分配和外部地址锁存器

8.2.1 8.2.1 存储器地址空间分配 89C51发出的地址是用来选择某个存储器单元 发出的地址是用来选择某个存储器单元, 89C51发出的地址是用来选择某个存储器单元,要完成 这种功能,必须进行两种选择: 这种功能,必须进行两种选择: • “片选”; 片选” • “单元选择”。 单元选择” 常用的存储器地址分配的方法有两种: 1. 常用的存储器地址分配的方法有两种: • 线性选择法(简称线选法); 线性选择法(简称线选法) • 地址译码法(简称译码法):部分译码和全译码。 地址译码法(简称译码法) 部分译码和全译码。

8.1.2 8.1.2 构造系统总线 系统扩展的首要问题是构造系统总线; 系统扩展的首要问题是构造系统总线; 构造系统总线 然后再往系统总线上“ 然后再往系统总线上“挂”存储器芯片或I/O接 存储器芯片或I/O接 I/O 口芯片( 口芯片(“挂”存储器芯片就是存储器扩展, 存储器芯片就是存储器扩展, “挂”I/O接口芯片就是I/O扩展); I/O接口芯片就是I/O扩展); 接口芯片就是I/O扩展 89C51扩展的三总线如8 所示。 89C51扩展的三总线如8-2所示。 扩展的三总线如

1.常用的EPROM芯片 1.常用的EPROM芯片 常用的EPROM 引脚功能如下: 引脚功能如下: A0~A15: A0~A15:地址线引脚 D7~D0: D7~D0:数据线引脚 CE*:片选输入端 OE* :输出允许控制端 编程时, PGM*:编程时,加编程脉冲的输入端 Vpp:编程时,编程电压(+12V +25V Vpp:编程时,编程电压(+12V或+25V)输入端 Vcc:+5V,芯片的工作 工作电压 Vcc:+5V,芯片的工作电压 GND: GND:数字地 NC: NC:无用端

ASIC、NP、X86、RISC、DSP 、ARM、单片机几种常见技术介绍

RISC微处理器不仅精简了指令系统,采用超标量和超流水线结构;它们的指令数目只有几十条,却大大增强了并行处理能力。如:1987年Sun

Microsystem公司推出的SPARC芯片就是一种超标量结构的RISC处理器。而SGI公司推出的MIPS处理器则采用超流水线结构,这些RISC处理器在构建并行精简指令系统多处理机中起着核心的作用。

(2)程序和数据空间分开,可以同时访问指令和数据;

(3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问;

(4)具有低开销或无开销循环及跳转的硬件支持;

(5)快速的中断处理和硬件I/O支持;

● 分级存储器组织: NP存储器一般包含多种不同性能的存储结构,对数据进行分类存储以适应不同的应用目的。

● 高速I/O接口:

NP具有丰富的高速I/O接口,包括物理链路接口、交换接口、存储器接口、PCI总线接口等。通过内部高速总线连接在一起,提供很强的硬件并行处理能力。

现代ASIC常包含整个32-bit处理器,类似ROM、RAM、EEPROM、Flash的存储单元和其他模块.

这样的ASIC常被称为SoC(片上系统)。

FPGA是ASIC的近亲,一般通过原理图、VHDL对数字系统建模,运用EDA软件仿真、综合,生成基于一些标准库的网络表,配置到芯片即可使用。它与ASIC的区别是用户不需要介入芯片的布局布线和工艺问题,而且可以随时改变其逻辑功能,使用灵活。

针对滤波、相关、矩阵运算等需要大量乘和累加运算的特点,DSP的算术单元的乘法器和加法器,可以在一个时钟周期内完成相乘、累加两个运算。近年出现的某些DSP如ADSP2106X、DSP96000系列DSP可以同时进行乘、加、减运算,大大加快了FFT的蝶形运算速度。

3.2 SRAM存储器

A11 A10 A9 A8 A0 片选 译码

8根数据线

CS0

CS1

CS2

CS3

D7

D0 WE

... ..

1K×4

..

1K×4

..

1K×4

..

1K×4

..

1K×4

..

1K×4

..

1K×4

..

1K×4

……

2. 存储器与 CPU 的连接

(1) 地址线的连接 (2) 数据线的连接 (3) 读/写线的连接

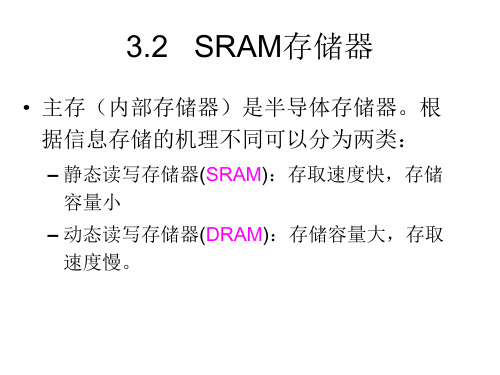

3.2 SRAM存储器

• 主存(内部存储器)是半导体存储器。根 据信息存储的机理不同可以分为两类:

– 静态读写存储器(SRAM):存取速度快,存储 容量小 – 动态读写存储器(DRAM):存储容量大,存取 速度慢。

3.2 SRAM存储器

一、基本的静态存储元阵列(64×4位) 1、存储位元 2、三组信号线

00000H 32KB ROM 96KB RAM 07FFFH 08000H

1FFFFH

(2)由题知:ROM区的容量为32KB, RAM区 的容量为96KB,利用32KB×8位RAM芯片和 32KB×4位ROM芯片,设计128KB×8位存储 器,需要RAM芯片:96/32=3(片);需要 ROM芯片:8/4=2(片)。 其中,两片ROM芯片串联后,与3片RAM 芯片并联。17条地址线中,15条低位地址线 连接到芯片,2位高位地址线利用2:4译码器 生成片选信号。存储器与CPU连接的示意图 如下:

• 分散式刷新:把一个存储系统周期tc分为两半,周 期前半段时间tm用来读/写操作或维持信息,周期后 半段时间tr作为刷新操作时间。这样,每经过128个 系统周期时间,整个存储器便全部刷新一遍。

74hc系列芯片设计手册

74HC系列芯片设计手册1. 介绍74HC系列芯片是数字集成电路中常用的一类器件,广泛应用于数字系统的设计和实现。

本手册旨在提供对74HC系列芯片的详细设计指南,以便工程师和设计者能够充分理解和利用这些强大的数字芯片。

2. 74HC系列概述74HC系列芯片是基于高性能CMOS技术的数字集成电路。

它包括多种逻辑门、触发器、移位寄存器等功能,适用于各种数字电路的设计。

这一系列的特点包括低功耗、高噪声容限、广电源电压范围等,使其成为数字系统设计的理想选择。

3. 芯片分类和功能手册详细介绍了74HC系列中不同芯片的分类及其各自的功能。

例如,74HC00是四个二输入NAND门的集成电路,而74HC74是一个双触发D型触发器。

理解每种芯片的功能对于正确应用它们至关重要,手册将提供清晰的说明和示例。

4. 电气特性设计者在使用74HC系列芯片时需要了解其电气特性,包括输入和输出电压范围、功耗、工作频率等。

手册将提供这些方面的详细规格,以确保设计符合芯片的电气要求,同时兼顾性能和稳定性。

5. 接口和引脚配置每个芯片的引脚配置对于正确的连接和使用至关重要。

手册将提供清晰的引脚图和功能表,帮助设计者正确地连接芯片并确保其在系统中的正常工作。

6. 时序图与时序要求在数字系统中,时序是一个至关重要的考虑因素。

手册将展示每个74HC芯片的时序图和相关的时序要求,以确保在实际应用中能够满足时序约束,从而保证系统的正确操作。

7. 典型应用电路为了更好地指导设计者,手册将提供一系列典型的应用电路示例,涵盖了从基本逻辑门的组合到复杂触发器和计数器的应用。

这些实例将帮助工程师更好地理解如何在实际项目中使用74HC系列芯片。

8. 设计注意事项在设计数字系统时,有一些常见的注意事项需要考虑,如信号完整性、电源噪声、布线等。

手册将提供一些建议和指导,帮助设计者避免一些潜在的问题,提高系统的可靠性和稳定性。

9. 74HC与其他系列的比较除了介绍74HC系列芯片外,手册还将对比其他常见的数字芯片系列,如74LS和74HCT。

芯片设计需要的知识点

芯片设计需要的知识点芯片设计是一门复杂而精密的工程,需要掌握多个知识领域的基础和专业知识。

本文将介绍芯片设计所需的主要知识点,以帮助初学者理解和入门芯片设计。

一、电子学基础知识1.1 电路理论:芯片设计离不开电路理论的基础,掌握电流、电压、电阻等基本概念,了解欧姆定律、基尔霍夫定律等电路理论原理。

1.2 逻辑电路:理解逻辑门电路,如与门、或门、非门等,了解组合逻辑和时序逻辑电路的设计方法。

1.3 模拟电路:了解模拟电路设计原理,如放大电路、滤波电路等,熟悉常见的放大器、滤波器等电路的设计和特性。

二、计算机体系结构知识2.1 计算机组成原理:了解计算机的基本组成部分,如中央处理器(CPU)、存储器、输入输出设备等,熟悉计算机指令和指令的执行过程。

2.2 微处理器架构:掌握微处理器的工作原理和内部结构,了解CPU的指令系统、寄存器、流水线等。

2.3 性能优化:了解性能优化的方法和技术,如流水线设计、指令级并行等,能够通过对芯片结构和设计的优化来提高芯片的性能。

三、数字电路设计知识3.1 布尔代数和逻辑门:掌握布尔代数的基本原理,了解与门、或门、非门等基本逻辑门的特性和应用。

3.2 状态机设计:理解有限状态机的概念和设计方法,熟悉状态图、状态转移表等状态机的表示方法。

3.3 时序逻辑设计:了解时钟信号、触发器、时序逻辑电路的设计和应用,能够进行时序逻辑的设计和分析。

四、模拟电路设计知识4.1 放大器设计:熟悉各种放大电路的设计和特性,如低频放大器、高频放大器等。

4.2 滤波器设计:了解滤波器的设计原理和常见的滤波器类型,如低通滤波器、高通滤波器、带通滤波器等。

4.3 数据转换器设计:了解模数转换器(ADC)和数模转换器(DAC)的设计原理和性能指标,能够进行数据转换器的设计和优化。

五、集成电路设计知识5.1 CMOS工艺:了解CMOS工艺的原理和制程流程,熟悉CMOS器件的特性和参数。

5.2 器件模型:理解器件模型的建立和使用,如MOS模型、BJT模型等,能够进行器件级的仿真和验证。

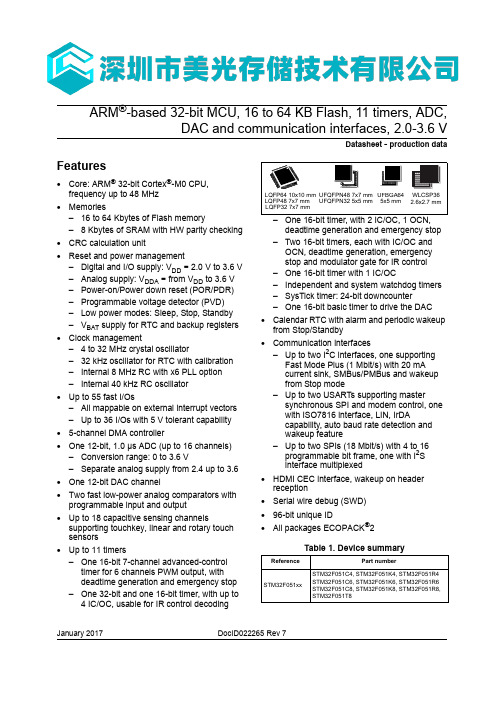

MEMORY存储芯片STM32F051K8T6中文规格书

ARM®-based 32-bit MCU, 16 to 64 KB Flash, 11 timers, ADC, DAC and communication interfaces, 2.0-3.6 VDatasheet - production dataFeatures•Core: ARM® 32-bit Cortex®-M0 CPU, frequency up to 48 MHz•Memories–16 to 64 Kbytes of Flash memory–8 Kbytes of SRAM with HW parity checking •CRC calculation unit•Reset and power management–Digital and I/O supply: V DD = 2.0 V to 3.6 V –Analog supply: V DDA = from V DD to 3.6 V–Power-on/Power down reset (POR/PDR)–Programmable voltage detector (PVD)–Low power modes: Sleep, Stop, Standby–V BAT supply for RTC and backup registers •Clock management– 4 to 32 MHz crystal oscillator–32 kHz oscillator for RTC with calibration–Internal 8 MHz RC with x6 PLL option–Internal 40 kHz RC oscillator•Up to 55 fast I/Os–All mappable on external interrupt vectors –Up to 36 I/Os with 5 V tolerant capability •5-channel DMA controller•One 12-bit, 1.0 µs ADC (up to 16 channels)–Conversion range: 0 to 3.6 V–Separate analog supply from 2.4 up to 3.6•One 12-bit DAC channel•Two fast low-power analog comparators with programmable input and output•Up to 18 capacitive sensing channels supporting touchkey, linear and rotary touchsensors•Up to 11 timers–One 16-bit 7-channel advanced-control timer for 6 channels PWM output, withdeadtime generation and emergency stop –One 32-bit and one 16-bit timer, with up to4 IC/OC, usable for IR control decodingdeadtime generation and emergency stop –Two 16-bit timers, each with IC/OC and OCN, deadtime generation, emergencystop and modulator gate for IR control –One 16-bit timer with 1 IC/OC–Independent and system watchdog timers –SysTick timer: 24-bit downcounter–One 16-bit basic timer to drive the DAC •Calendar RTC with alarm and periodic wakeupfrom Stop/Standby•Communication interfaces–Up to two I2C interfaces, one supporting Fast Mode Plus (1 Mbit/s) with 20 mAcurrent sink, SMBus/PMBus and wakeupfrom Stop mode–Up to two USARTs supporting master synchronous SPI and modem control, onewith ISO7816 interface, LIN, IrDAcapability, auto baud rate detection andwakeup feature–Up to two SPIs (18 Mbit/s) with 4 to 16 programmable bit frame, one with I2Sinterface multiplexed•HDMI CEC interface, wakeup on header reception•Serial wire debug (SWD)•96-bit unique ID•All packages ECOPACK®2Table 1. Device summaryReference Part numberSTM32F051xx STM32F051C4, STM32F051K4, STM32F051R4 STM32F051C6, STM32F051K6, STM32F051R6 STM32F051C8, STM32F051K8, STM32F051R8, STM32F051T8January 2017DocID022265 Rev 7Functional overview STM32F051x4 STM32F051x6 STM32F051x8DocID022265 Rev 7sensor, voltage reference, VBAT voltage measurement) channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.The ADC can be served by the DMA controller.An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.3.10.1 Temperature sensorThe temperature sensor (TS) generates a voltage V SENSE that varies linearly withtemperature.The temperature sensor is internally connected to the ADC_IN16 input channel which is used to convert the sensor output voltage into a digital value.The sensor provides good linearity but it has to be calibrated to obtain good overallaccuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.To improve the accuracy of the temperature sensor measurement, each device isindividually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.3.10.2Internal voltage reference (V REFINT )The internal voltage reference (V REFINT ) provides a stable (bandgap) voltage output for the ADC and comparators. V REFINT is internally connected to the ADC_IN17 input channel. The precise voltage of V REFINT is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.Table 3. Temperature sensor calibration valuesCalibration value nameDescriptionMemory address TS_CAL1TS ADC raw data acquired at a temperature of 30 °C (± 5 °C), V DDA = 3.3 V (± 10 mV)0x1FFF F7B8 - 0x1FFF F7B9TS_CAL2TS ADC raw data acquired at a temperature of 110 °C (± 5 °C), V DDA = 3.3 V (± 10 mV)0x1FFF F7C2 - 0x1FFF F7C3Table 4. Internal voltage reference calibration valuesCalibration value nameDescriptionMemory address VREFINT_CALRaw data acquired at atemperature of 30 °C (± 5 °C), V DDA = 3.3 V (± 10 mV)0x1FFF F7BA - 0x1FFF F7BBSTM32F051x4 STM32F051x6 STM32F051x8Functional overview 3.10.3 V BAT battery voltage monitoringThis embedded hardware feature allows the application to measure the V BAT battery voltageusing the internal ADC channel ADC_IN18. As the V BAT voltage may be higher than V DDA,and thus outside the ADC input range, the V BAT pin is internally connected to a bridgedivider by 2. As a consequence, the converted digital value is half the V BAT voltage.(DAC)converter3.11 Digital-to-analogThe 12-bit buffered DAC channels can be used to convert digital signals into analog voltagesignal outputs. The chosen design structure is composed of integrated resistor strings andan amplifier in non-inverting configuration.This digital Interface supports the following features:•Left or right data alignment in 12-bit mode•Synchronized update capability•DMA capability•External triggers for conversionFive DAC trigger inputs are used in the device. The DAC is triggered through the timertrigger outputs and the DAC interface is generating its own DMA requests.(COMP)3.12 ComparatorsThe device embeds two fast rail-to-rail low-power comparators with programmablereference voltage (internal or external), hysteresis and speed (low speed for low power) andwith selectable output polarity.The reference voltage can be one of the following:•External I/O•DAC output pins•Internal reference voltage or submultiple (1/4, 1/2, 3/4).Refer to Table 24: Embedded internal reference voltage for the value and precision of the internal reference voltage.Both comparators can wake up from STOP mode, generate interrupts and breaks for thetimers and can be also combined into a window comparator.3.13 Touch sensing controller (TSC)The STM32F051xx devices provide a simple solution for adding capacitive sensingfunctionality to any application. These devices offer up to 18 capacitive sensing channelsdistributed over 6 analog I/O groups.Capacitive sensing technology is able to detect the presence of a finger near a sensor whichis protected from direct touch by a dielectric (glass, plastic...). The capacitive variationintroduced by the finger (or any conductive object) is measured using a provenimplementation based on a surface charge transfer acquisition principle. It consists incharging the sensor capacitance and then transferring a part of the accumulated chargesinto a sampling capacitor until the voltage across this capacitor has reached a specificthreshold. To limit the CPU bandwidth usage, this acquisition is directly managed by theDocID022265 Rev 7Functional overview STM32F051x4 STM32F051x6 STM32F051x8DocID022265 Rev 7hardware touch sensing controller and only requires few external components to operate. For operation, one capacitive sensing GPIO in each group is connected to an external capacitor and cannot be used as effective touch sensing channel.The touch sensing controller is fully supported by the STMTouch touch sensing firmware library, which is free to use and allows touch sensing functionality to be implemented reliably in the end application.Table 5. Capacitive sensing GPIOs available on STM32F051xx devicesGroupCapacitive sensingsignal name Pin name GroupCapacitive sensingsignal name Pin name 1TSC_G1_IO1PA04TSC_G4_IO1PA9TSC_G1_IO2PA1TSC_G4_IO2PA10TSC_G1_IO3PA2TSC_G4_IO3PA11TSC_G1_IO4PA3TSC_G4_IO4PA122TSC_G2_IO1PA45TSC_G5_IO1PB3TSC_G2_IO2PA5TSC_G5_IO2PB4TSC_G2_IO3PA6TSC_G5_IO3PB6TSC_G2_IO4PA7TSC_G5_IO4PB73TSC_G3_IO1PC56TSC_G6_IO1PB11TSC_G3_IO2PB0TSC_G6_IO2PB12TSC_G3_IO3PB1TSC_G6_IO3PB13TSC_G3_IO4PB2TSC_G6_IO4PB14Table 6. Effective number of capacitive sensing channels on STM32F051xxAnalog I/O groupNumber of capacitive sensing channelsSTM32F051RxSTM32F051CxSTM32F051TxSTM32F051KxU (UFQFPN32)STM32F051KxT (LQFP32)G133333G233333G332221G433333G533333G633000Number of capacitive sensing channels1817141413DocID022265 Rev 7STM32F051x4 STM32F051x6 STM32F051x8Functional overviewTable 7. Timer feature comparisonTimer typeTimerCounter resolution Counter typePrescaler factorDMA request generationCapture/compare channels ComplementaryoutputsAdvancedcontrol TIM116-bitUp, down, up/down integer from 1 to 65536Yes 43General purposeTIM2 32-bit Up, down, up/down integer from 1 to 65536Yes 4- TIM316-bit Up, down, up/down integer from 1 to 65536Yes 4-TIM1416-bit Up integer from1 to 65536No 1-TIM1516-bit Up integer from 1 to 65536Yes 21TIM16TIM1716-bit Up integer from 1 to 65536Yes 11BasicTIM616-bitUpinteger from 1 to 65536Yes--。

微型计算机原理及接口技术(第三版)(裘雪红)作者提供课件章 (4)

& 1

≥1

G1

G2A Y0

G2B

74LS138

C B

Y1

A

A15 0 A14 0 A13 0 A12 0

A11 x A10

A9 A8

A7

A6 6116 A5 片内 A4 地址

A3 A2 A1 A0

5.2.1 静态读/写存储器(SRAM) 一、异步SRAM 3. 传统异步型SRAM连接举例

(2)利用ROM作译码器 现在要用4片6264构成一个存储容量为32 KB的存储

A12 WE OE CS2 DA000H~DBFFFH DE000H~DFFFFH

CS1 FA000H~FBFFFH FE000H~FFFFFH

19

5.2.1 静态读/写存储器(SRAM)

2. 传统异步型SRAM接口设计 (2) 译码电路的选择

利用译码芯片、门电路 74LS138:3-8译码器 74LS154:4-16译码器

类型

存储容量

特征

标准同步SRAM

2Mb~72Mb 直通型SRAM

流水线型SRAM

NoBL(无总线延Q迟D率R)来型型支同持步两4SMR项Ab同M~时7能2出够M现以b的2倍读数、零据写总传操线输作转速向时间

SRAM

时钟的上升沿和下降沿可分别

QDR型同步SRAM

18传M送b一~1次4数4M据b 四倍数据速率

同步SRAM的所有访问都在时钟的上升/下降沿启动, 地址、数据输入和其它控制信号均与时钟信号相关。

9

5.2.1 静态读/写存储器(SRAM)

1. 典型传统异步型SRAM芯片 SRAM 6264芯片

一、异步SRAM

10

8987654321 21111111111 76543210 C D DDDDDDDD N N CCV G E 89E01234567 4 6 W2SCAA11AO01A1SCAAAAAAAA21A 2 6 98765432 765432100 222222221

flash芯片选型

flash芯片选型Flash芯片是一种常见的存储器件,它可以在断电后仍然保持数据的存储状态。

在现代电子产品中,Flash芯片几乎无处不在,用于存储各种程序、文件和数据。

选择合适的Flash芯片对于设计电子产品至关重要,关系到产品的性能、稳定性和成本。

以下是一些选型Flash芯片的要点,以帮助您做出明智的选择。

1.存储容量:根据产品的需求确定所需的存储容量。

不同的应用场景可能需要不同容量的存储空间。

注意,Flash芯片的存储容量通常以字节(B)计算,常见的容量有128MB、256MB、512MB、1GB、2GB等。

2.接口类型:根据产品的主控芯片确定所需的接口类型。

常见的接口类型有SPI、SDIO、NAND、NOR等。

SPI接口适用于小容量的应用,SDIO接口适用于需要高速数据传输的应用,NAND接口适用于大容量存储器,NOR接口适用于需要较高可靠性和速度的应用。

3.速度等级:根据产品对读写速度的要求确定所需的速度等级。

速度等级通常以MHz表示,常见的等级有25MHz、50MHz、100MHz等。

较高的速度等级可以提高数据传输速度,但也可能导致产品成本的增加。

4.工作电压:根据产品对工作电压的要求确定所需的工作电压范围。

常见的工作电压范围有1.8V、3.3V等。

选择适合产品的工作电压范围可以保证产品的稳定性和可靠性。

5.数据保持能力:Flash芯片的数据保持能力是指在断电情况下,数据可以保持的时间。

根据产品的需求确定所需的数据保持能力。

一般来说,数据保持能力越长,产品的可靠性就越高。

6.耐用性和擦写次数:Flash芯片通常具有一定的擦写次数限制。

根据产品的需求确定所需的耐用性和擦写次数。

对于需要频繁写入和擦除数据的应用,选择具有更高耐用性和擦写次数的Flash芯片可以延长产品的使用寿命。

7.成本:根据产品的预算确定所需的成本范围。

不同品牌和型号的Flash芯片价格差异很大,根据产品需求在合适的价格范围内选购Flash芯片。

数字芯片设计基础知识点

数字芯片设计基础知识点数字芯片设计是现代电子技术领域的重要分支,它涉及到数字电路设计、逻辑设计和芯片设计等多个方面。

本文将介绍数字芯片设计的基础知识点,包括数字电路的基本概念、逻辑门的种类、计数器和触发器等内容。

一、数字电路的基本概念数字电路是由数字元器件(如逻辑门、触发器等)组成的电路,用于处理和传输数字信号。

在数字电路中,主要涉及到0和1两个离散的信号状态,通过组合和连接不同的逻辑门实现各种逻辑功能。

数字电路的基本概念包括布尔代数、逻辑函数和真值表。

其中,布尔代数是数字电路设计的基础,通过逻辑函数和真值表可以描述电路的输入输出关系,帮助设计师分析和设计数字电路。

二、逻辑门的种类逻辑门是数字电路中最基本的逻辑功能模块,常见的逻辑门包括与门、或门、非门、异或门等。

它们通过不同的输入和输出关系实现不同的逻辑功能。

与门是最基本的逻辑门之一,它的输出只有在所有输入都为1时才为1,否则为0。

与门可以用于信号的合并和判断等功能。

或门的输出在至少一个输入为1时为1,否则为0,常用于信号的选择和合并。

非门是一种单输入的逻辑门,它的输出与输入信号相反。

异或门在两个输入不同时输出为1,否则输出为0,常用于信号的比较和判断。

三、计数器和触发器计数器是一种常见的数字电路模块,用于实现计数功能。

常见的计数器包括二进制计数器和BCD码计数器。

计数器可以根据输入的时钟信号进行计数操作,并根据设定的计数范围和触发条件输出相应的计数结果。

触发器是一种用于存储和传递状态信息的数字电路元件。

常见的触发器包括RS触发器、D触发器和JK触发器。

触发器可以存储一个或多个比特的数据,并根据输入信号的变化实现状态的存储和传递。

四、数字芯片设计流程数字芯片设计的整体流程包括需求分析、系统设计、逻辑设计、物理设计和验证等步骤。

需求分析阶段主要确定数字芯片的功能需求、性能指标和设计约束等,为后续的设计提供基础。

系统设计阶段主要进行数字系统的整体设计,包括功能划分、模块选择和接口定义等。

芯片存储的技巧

芯片存储的技巧芯片存储的技巧是指在设计和开发芯片时,如何优化存储器的使用,以提高芯片性能和降低成本。

以下是一些常用的芯片存储技巧:1. 存储器层次结构优化:将存储器按照不同的速度和容量进行分层,使得速度较快但容量较小的存储器放在靠近处理器的地方,速度较慢但容量较大的存储器放在靠近外部的地方。

这样可以在保证性能的同时,降低成本。

2. 存储器访问优化:使用缓存技术可以减少对主存的访问次数。

缓存是一种快速但容量较小的存储器,用于暂时存储最近使用的数据。

通过在处理器和主存之间插入缓存,可以提高数据的访问速度。

3. 存储器压缩技术:通过压缩存储器中的数据,可以提高存储器的容量,并减少存储器读写操作所需的时间和能量。

在设计存储器时,可以使用各种压缩算法和技巧,例如字典压缩、位图压缩等。

4. 存储器编址技术:合理地选择存储器的编址方式,可以提高存储器的访问效率。

例如,使用行列编址方式可以减少读写操作所需的时间和功耗。

5. 存储器划分和映射技术:将存储器按照不同的逻辑功能进行划分,并将每个部分映射到合适的物理地址空间。

这样可以提高存储器的使用效率,并降低设计和测试的复杂度。

6. 存储器预取和预取技术:通过预测程序的执行模式和数据访问模式,提前将可能需要的数据加载到缓存中,以减少对主存的访问次数。

预取和预取算法可以根据不同的应用场景进行优化。

7. 存储器编码和纠错技术:使用适当的编码和纠错技术,可以在一定程度上提高存储器的可靠性和稳定性。

例如,使用哈弗曼编码、循环冗余校验码等技术可以减少存储器中的错误和损坏。

8. 存储器功耗优化技术:在设计存储器时,需要考虑功耗的问题。

通过合理地选择存储器的类型、结构和电压等参数,可以降低存储器的功耗。

9. 存储器测试和调试技术:在芯片开发的过程中,存储器的测试和调试是非常重要的环节。

通过使用各种测试模式和测试工具,可以有效地检测和排除存储器中的错误和故障。

10. 存储器安全性保护技术:随着信息安全的重要性日益增加,对存储器的安全性保护也变得越来越重要。

8051单片机8扩展存储器设计

8.3 常用的扩展存储器芯片

Vpp A12 A7 A6 A4 A4 A3 A2 A1 A0 Q0 Q1 Q2 GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 28 27 26 25 24 23 22 21 20 19 18 17 16 15 Vcc PGM NC A8 A9 A11 OE A10 CE Q7 Q6 Q5 Q4 Q3

8.3 常用的扩展存储器芯片

1. 地址锁存器 地址锁存器74LS373 74LS373 是 一 种 带 输 出三态门的8D锁存器 锁存器。 出三态门的 锁存器。 其中: 其中: 1D~8D为8个输入端 ~ 为 个输入端 1Q~8Q为8个输出端 ~ 为 个输出端 G为使能端 : 当 G为高电平时 , 锁存器输出状态 为使能端: 为高电平时, 为使能端 为高电平时 (1Q~8Q)与输入状态 与输入状态(1D~8D)相同;当G由“1”变 相同; ~ 与输入状态 ~ 相同 由 变 “0”时,输入的数据被锁存在锁存器中,输入端的 时 输入的数据被锁存在锁存器中, 变化不再影响输出端。 变化不再影响输出端。

第八章 扩展存 储器设计

8.1 存储器扩展概述

需求:存取速度快,存储容量大,价格低 需求:存取速度快,存储容量大, 内存: 直接与之沟通的存储器件。 内存:CPU直接与之沟通的存储器件。容量小、速 直接与之沟通的存储器件 容量小、 度快、信息需电维持, 度快、信息需电维持,用于存放当前要执行的程 序和数据, 序和数据,也叫主存储器 外存:容量大、速度慢、信息不需电维持,用于存 外存:容量大、速度慢、信息不需电维持, 放暂时不用的数据和程序, 放暂时不用的数据和程序,也叫辅存储器 注:扩展存储器不属于外存

8.4 片外存储器扩展编址技术

存储器系统设计

ALE

CE

OE

A0~A7 A8~A14 62256 D0~D7

CE

OE

G 373 1D~8D 8

P0

PSEN

WR

RD

系统的EPROM(27256)0000~7FFFH(管理仿真系统的程序),系统的仿 真ROM和数据存储器为8000~FFFFH。当执行系统的管理程序时, 27256有效(尽管有效 PSEN ,但地址不对),62256无效,当执行自己 编的仿真程序时,系统转向62256中执行你输入的程序,当遇到MOVX

ALE

8

2764

2764

2764

P0

PSEN

P2.6 0 0 1 P2.5 0 1 0 /Y0 /Y1 /Y2 0 1 1 0000-1FFFH (8000H-9FFFH) 括号内 1 0 1 2000-3FFFH(A000H-BFFFH) 为重叠 1 1 0 4000-5FFFFH(C000H-DFFFH) 区!

74LS138的真值表

输出有效时,只有一个为低电平,其余为高电平,故用其来接被选的芯片时, 只有一个被选中。保持芯片之间地址的不重叠。(74LS139的介绍见书P158)

5.2.3 程序存储器扩展设计

(1)扩展16KB EPROM(线选法用单片机地址总线高位地址作为选择某 一存贮器的片选信号)。

;将最后一个字节数据取出 ;原始数据比较,陷入死循环! ;最高位不同,再查!

地址 输出

指令 输入

PCL 输出

指令 输入

PCL 输出

P2口输出程序存储器的高8位地址PCH(A15~A8),具有锁存功能。 P0口地址/数据复用线,在ALE上升为高电平时,P0口输出程序存储 器的低8位地址(A7~A0),在ALE的下降沿,把A7~A0锁存到外部地 址锁存器中,得到地址信号,接着,P0口由输出变为输入,高8位地 址不变(低8位已锁存),故已选定外部ROM的某一个地址,随即 PSEN 低电平有效,外部ROM通,对应地址单元中的指令字节出现在数据 总线上供CPU读取。

单片机外部扩展常用芯片讲解

A13

A14 A15

Vcc

AB

PSEN 接8031 RD

WR

CE D0~D7 A0~A12 2764

OE

A0~A15

CE1 D0~D7 A0~A12 6264

OE WR

C BA A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

01000 01000

0 00 0 00 0 0 0 00 0 00 0 00 0 0 0 00

Y2

地址译码范围:4000H~5FFFH 共 8 K字节

特点: 1、电路复杂; 2、地址空间连续; 3、不浪费地址空间,16 条地址线 译出64K字节 ; 4、适用于存储容量较大的系统。

A15 CE

A14 Vcc A0~A12 CE1

6264 CE2

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

01000 01011

0 00 0 00 0 0 0 00 1 11 1 11 1 1 1 11

2764 ROM 地址: 4000H~5FFFH

L L +5 +5 H OUT

L H VPP +5 L IN

1

28

2764 (P311)

14

15

Vcc

PGM NC A8 A9 A11

OE A10

CE D7 D6 D5

D4

D3

2、RAM : Random Access Memory(P115) NC 1

A0~A12: 13条地址线,8KB

D0~D7 : 8条数据线

28 WR NC

存储器入门介绍和选型(ROM SRAM DRAM Nor Nand Flash EEPROM MRAM FRAM)

易失性存储器 - DRAM

2 DRAM特点

由于每个存储位仅用一个晶体 管和小电容,因此集成度比较 高。就单个芯片的存储容量而 言,DRAM可以远远超过 SRAM;就相同容量的芯片而 言,DRAM的价格也大大低于 SRAM。这两个优点使DRAM 成为计算机内存的主要角色。 DRAM的行列地址分时复用控 制和需要刷新控制,使得它比 SRAM的接口要复杂一些。另 外,DRAM的存取速度一般比 SRAM要慢。

MRAM(Magnetic Random Access Memory)是一种 非易失性的磁性随机存储器。它拥有静态随机存储器(SRAM) 的高速读取写入能力;以及动态随机存储器(DRAM)的高集成 度,而且基本上可以无限次地重复写入。

非易失性存储器 – EEPROM

3 EEPROM选型

存储容量: 1Kb-1Mb

接口: IIC;SPI;Microwire

速率: IIC:400KHz,1MHz SPI:10MHz,20MHz Microwire:1MHz,2MHz

EEPROM

电压范围: 常用(FM)1.7-5.5V;1.7-3.6V Min:1.6,1.7,1.8,2.5,2.7,3V Max:2.5,3.6,5.5,6V

1.速度较慢 2.需要刷新来保持数据 3.需要MCU带外部存储控 制器

4.容量大,16Mb-4Gb 5.集成度高,单位容量价 格低

6.运行功耗低

非易失性存储器 - ROM

非易失性存储器主要是用来存放固定数据、固件程序等一 般不需要经常改动的数据。

早先ROM OTP EPROM EEPROM Flash

速率:800/667/533/400(Mhz) 容量:建议512M-2G

速率:2133/1866/1600/1333(Mhz) 容量:建议1G-4G

单片机常用芯片资料

单片机常用芯片资料单片机作为一种常见的嵌入式系统的核心组成部分,广泛应用于各个领域。

而在单片机的设计与开发过程中,选择合适的芯片是至关重要的。

本文将介绍一些常用的单片机芯片资料,以供读者参考。

I. 8051系列芯片8051系列是一种经典的单片机芯片,广泛应用于各种嵌入式系统中。

以下是一些常见的8051系列芯片资料供读者参考:1. AT89S51AT89S51是一种低功耗、高性能的8位CMOS单片机,由Atmel公司生产。

它具有4KB的Flash程序存储器、128字节的RAM和32个I/O引脚,适用于各种应用场景。

2. AT89C52AT89C52也是一种经典的8051系列芯片,同样由Atmel公司生产。

它具有8KB的Flash程序存储器、256字节的RAM和32个I/O引脚,可广泛应用于嵌入式系统中。

II. AVR系列芯片AVR系列芯片是由Atmel公司开发的一种低功耗、高性能的8位RISC微控制器。

以下是一些常见的AVR系列芯片资料供读者参考:1. ATmega328PATmega328P是一种广泛应用于Arduino开发板的AVR系列芯片,具有32KB的Flash程序存储器、2KB的SRAM和23个I/O引脚。

它支持多种通信接口(如SPI、I2C等),适用于各种创意项目。

2. ATtiny85ATtiny85是一种小型的AVR系列芯片,具有8KB的Flash程序存储器、512字节的RAM和6个I/O引脚。

它体积小巧,适合于空间受限的应用场景,如可穿戴设备等。

III. PIC系列芯片PIC系列芯片是由Microchip公司开发的一种低功耗、高性能的8位微控制器。

以下是一些常见的PIC系列芯片资料供读者参考:1. PIC16F877APIC16F877A是一种常用的PIC系列芯片,具有14KB的Flash程序存储器、368字节的RAM和33个I/O引脚。

它适用于各种嵌入式应用,如家用电器、工业控制系统等。

存储器处理单元核心架构的制作方法

存储器处理单元核心架构的制作方法存储器处理单元(Memory Processing Unit,MPU)是一种集成了处理器和存储单元的芯片,它能够更为高效地处理数据。

在这个处理器的核心原理中,存储单元负责存储数据,处理单元则负责执行代码、逻辑和算术运算等操作。

下面将介绍如何制作一款存储器处理单元核心架构。

1.核心原理设计首先需要了解处理器架构设计的重要原理,包括指令集,操作码,中央处理器(CPU)的掌控单元(CU)和执行单元(EU),以及内存模型。

我们需要确定指令集,并确定QFP器件包、哈佛式总线结构以及存储单元的大小,以充足处理器的性能需求。

2.芯片设计在确定核心原理后,需要进行芯片设计。

设计需要考虑最小化芯片的面积、功耗、时钟速率和搭配存储单元扩展位置。

需要确定处理器中的重要功能单元和数据通道,以提高数据传输的效率,削减不必要的指令间跳转。

3.验证设计完成芯片设计之后,需要验证设计是否充足性能要求。

可以进行基于硬件、仿真、虚拟和软件等多种验证方式。

验证还要考虑处理器架构的牢靠性和稳定性,以及信号传输的稳定性。

4.生产生产设计完成之后,进入芯片生产阶段。

建议选择正规的生产厂家,牢靠、先进的技术以及优秀的技术支持,以确保生产出高品质的芯片。

同时需要进行测试并检查芯片的性能是否良好。

假如显现问题,需要返工或修复芯片,以确保芯片性能运行稳定。

以上即是制作一款存储器处理单元核心架构的重要方法,需要从核心原理设计、芯片设计、验证设计和芯片生产等多个方面考虑。

在实践中需要结合实际需求,依据不同场景设计和制作适合的存储器处理单元核心架构。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

信号类型

信号名 DQA[0:8]

信号说明

处理方式 与其接口芯片直连

数据线

DQB[0:8] DQC[0:8] DQD[0:8]

数据线

地址线 时钟线

A[0:18] CLK

地址线 时钟输入,用来捕获芯 片的所有同步输入

与其接口芯片直连 与其接口芯片直连

/OE /GW /CE1 主要 控制信号 CE2 /CE3

二:大容量 FLASH

由于 FLASH 具有在掉电情况下保持数据和容量大的特性,因此在公司的绝大多数运用 中是用在 CPU 系统中存放系统的应用软件的,其运作过程如下:系统上电后,首先 BOOTROM 的片选被选中,它里面放的是 CPU 的初始化程序,这样 CPU 就起来了,接着 FLASH 条的版本程序被下载到内存条中,从而整个软件就在 CPU 系统中运行起来,这样一 来可以提高系统运行速度, 二来是方便版本的管理。 因为一般来说系统支持远程加载和更新 软件版本的功能,因此一般说来 FLASH 中必须开辟两个相同的区域,分别作为软件版本的 保护和备份,这样一旦出现在系统动态加载软件失败时,能保证备用软件版本的正常启动, 使系统不致崩溃。

典型介绍

生产 FLASH 的厂商很多,我们将以广为运用 INTEL 的 28F128J3A 芯片为例子来介绍, 使大家对 FLASH 的操作有一个大致的了解, 此芯片单片容量为 128MBIT,(16BIT X 8M)。 由 于此系列的 FLASH(28F128J3,28F640J3,28F320J3)的引脚完全兼容,因此可以简单地 通过器件替换提供 128MBIT,64MBIT,32MBIT 的容量。 28F128J3A 芯片的管脚简单,分数据总线,地址总线,控制线,电源,地这么几类;在 使用的时候, 只需接出使能, 片选, 写控制三根控制线即可, 其他的控制线可以接固定电平, 下图就是某 CPU 子卡的 FLASH 接法:

二、SSRAM 的电路设计 1、概述 一般来说,SSRAM 的信号主要包括以下几部分:数据线、地址线、时钟以及写使能、 输出使能等控制信号等。 在进行具体的电路设计时, 一般只需将这些主要信号与其接口的特 定芯片的对应信号直接对连即可, 对于一些比较特殊的时序要求可以通过 EPLD 内做逻辑实 现。对于 SSRAM 上的一些不用的输入信号进行适当的上、下拉处理。 2、应用实例 下面以 RNC 中的一块单板 ASC 上采用的 SSRAM 为例,来说明 SSRAM 的具体应用。 首先根据设计要求,ASC 单板上的 ATM 层 UNI/NNI 管理接口芯片 ALM 需要一片数据 宽度为 32 位的 SSRAM 作为外部存储器。综合考虑 ALM 外部存储器所需的容量大小以及 目 前 SSRAM 的 价 格 因 素 及 芯 片 可 采 购 性 等 各 方 面 因 素 , 可 以 选 择 公 司 通 用 件 CY7C1381B-100AC(代码 12300217)来实现。 CY7C1381B-100AC 数据宽度为 32 位,其信号线主要包括地址线、数据线、时钟和一 些控制信号,其具体信号如下表所示。

FLASH 介绍

一、BOOT ROM 简介 我们在 CPU 最小系统中一般采用 AM29LV040B-90 // SST39VF040-90-4C-NH (代码: 10300067,512kB,8 位总线宽度,PLCC32 封装,3.3V 供电)作为 BOOT ROM。 BOOT ROM 中存放的是系统自举程序,实现 CPU 系统的自举。当系统上电后,CPU 首先运行 BOOT ROM 中的程序,完成对 CPU 系统的初始化。

图 1 AM29LV040B-90 // SST39VF040-90-4C-NH 引脚图 该 FLASH 芯片可在线读写,但作为 BOOT ROM 时,我们一般用烧录机烧写入程序, 不对其进行在线写。其读操作时序如图 2 所示。

图 2 读操作时序

下面给出一个 MPC860 最小系统的应用例子。

SST39VF040 BAB BDB BCB AB 244

命令禁止(NOP:Command inhibit) 空操作(NOP:No operation) 激活操作(ACT:Select bank and active row) 读操作 (READ: Select bank and column,and start READ burst) 写操作(WRITE:Select bank and column,and start WRITE burst) 突发操作停止(BTR:Burst terminate) 预充电(PRE:Deactive row in bank or banks) 自动刷新或自我刷新(REF:Auto refresh or self refresh) 配置模式寄存器(LMR:Load mode register)

上拉(理由同上) 上拉或下拉,可根据实际需 要通过电阻选焊实现 上拉或下拉,本应用中下拉 上拉或下拉,本应用中上拉 上拉或下拉,可根据实际需 要通过电阻选焊,本应用中 选择下拉

/ADSC /ADSP MODE

控制器地址选通 处理器地址选通 Burst 序列选择, 接地时 选择线性 burst 顺序, 悬 空或上拉时选择交织 burst

BAB BDB BCB

地址总线 数 据 总 线

28F128

BA[30-7]

动

BD[0-15]

M P C

F L A S H

FLASH 28F128J3A 的操作是通过 CPU 分 来 现的, 其 地址总线,控制线 现某个固定电平 ;下 就是 28F128J3A 有 的定 :

控 制 总 线

BOE BWE 动 CS /CS1

其他 控制 信号

DQA[0:8]DQB[0:8] DQC[0:8]DQD[0:8]

A[0:18]

上 下 拉 处 理

SDRAM 应用

存储器是容量数据处理电路的重要组成部分。 随着数据处理技术的进一步发展, 对于存 储器的容量和性能提出了越来越高的要求。同步动态随机存储器 SDRAM ( Synchronous Dynamic Random Access Memory)因其容量大、读写速度快、支持突发式读写及相对低廉的 价格而得到了广泛的应用。SDRAM 的控制比较复杂,其接口电路设计是关键。 1. SDRAM 的主要控制信号和基本命令 SDRAM 的主要控制信号为: ·CS:片选使能信号,低电平有效;

一、SSRAM 的选用 在选用 SSRAM 时,一般需要考虑以下几个方面: (1)根据设计需求、接口芯片的具体要求等确定 SSRAM 的芯片容量大小、数据宽度 以及芯片速度等级; (2)根据以上信息确定 SSRAM 型号,并尽可能在公司通用件库中选型; (3)根据信号定义及信号时序等确定 SSRAM 及其接口芯片的具体的电路连接关系。

常用存储器芯片设计指南

现代通讯产品中,各种存储器的应用已经是越来越广泛,可以这么说,产品中包含的 存储器的特性的好坏,直接关系到产品整体性能。因此,存储器芯片的设计,在通讯产品的 设计中,也显得愈发重要。 目前在通讯产品中应用的存储器,主要有 FLASH、SSRAM、SDRAM、串行 PROM 等, 由此延伸出去还有在接口电路中经常应用的 FIFO、双口 RAM 等,下面的内容就是这些常 用存储器芯片的原理介绍和在产品中的设计指南。

地 址 总 线

驱 动

BA[31..13]

M P C 8 6 0

DB

数 据 总 线

245 BD[0..7]

缓 冲

244 B\OE 驱 动 \CS0

B O O T

图 3 MPC860 BOOT 电路图 因为我们不需要在线写,所以为防止 BOOT FLASH 的程序被改写,一般将/WE 信号接 高电平。 MPC860 用 8 位数据口的方式访问 BOOT, 经缓冲之后的数据线为 BD00-BD07。 MPC860 地址线使用 A31-A13,经一级驱动与 BOOT 相连。 使用/CS0 片选端,地址范围 0x0800 0000~0x0807 FFFF,使用内部等待,等待周期为 8。 BOOT ROM 中存放的是系统自举程序,实现 MPC860 系统的自举。当系统上电后, MPC860 首先运行 BOOT ROM 中的程序,该程序首先完成 MPC860 的初始化,然后根据参 数,将 Flash ROM 中的应用程序复制到 SDRAM 空间中,然后将控制权移交给该应用程序 运行;或准备应用程序加载,进入 的具体接口信号可知,电路连接方面基本上只要将二者数据 线、地址线、时钟以及几个主要控制信号直连,其他的信号做一些上下拉处理即可。如下图 所示,给出了二者接口的电路连接框图。同时在表 1 中最后一列也给出了在该例中 SSRAM 各具体信号的相应处理方式。

ALM CY7C1381B-100AC DATA[0:31] SDATA[0:31] ADDR[0:18] SADDR[0:18] OEN SOEN WEN SWEN CLK SCLK CLK /GW /OE

图 1 XC17S00A 引脚图 FPGA 的配置数据是事先烧入 PROM 中的,FPGA 采用的是主串行配置方式,上电后 FPGA 产生配置时钟给 PROM, PROM 则按照图 3 的时序对 FPGA 进行配置, 当配置完成后 FPGA 的 DONE 信号就不使能 PROM。

图 2 PROM 配置 FPGA 电路

图 3 PROM 的配置时序 我们公司这类器件没有一个是通用的,我们不推荐使用 PROM 配置这种方式。最好用

CPU 进行 FPGA 配置,这样做增加了 FPGA 版本的灵活性,也大大降低了成本。

SSRAM 介绍

SSRAM 支持高性能 CPU、DSP、网络套片等多种应用场合。目前在公司多种产品中也 有比较广泛的应用。

第二个例子是使用Write_to_Buffer命令过程,我们可以看到,在其过程中,我们可以 看到需要发布Read_Status_Register命令检查芯片的状态信息以判断下一步: