按键数码管显示FPGA程序

FPGA矩阵键盘显示电路的设计实验报告

三、实验数据处理、误差计算及讨论

当设计文件加载到目标器件后,将数字信号源模块的时钟选择为1KHZ,按下矩阵

湖南科技大学

物理与电子科学学院专业实验报告实验课程:FPGA实验

实验项目:矩阵键盘显示电路的设计

专业:

班级:

姓名:

学号:

实验日期:年月日

明,这里不在赘述。

本实验箱上的4X4矩阵键盘的电路原理如下图所示。

实现键盘有两种方案:一是采用现有的一些芯片实现键盘扫描;再就是用软件实

软件,新建一个工程。

VHDL File,打开VHDL编辑器对话框。

开关的不完善导致出现按键抖动。

成绩:教师:。

《FPGA设计与应用》数码管显示实验

《FPGA设计与应用》数码管显示实验一、实验目的1.学习动态数码管的工作原理;2.实现对EGO1开发板四位动态数码管的控制;二、实验内容实现对EGO1开发板四位动态数码管的控制,使其能够正常工作;三、实验要求在EGO1开发板上显示想要的数字。

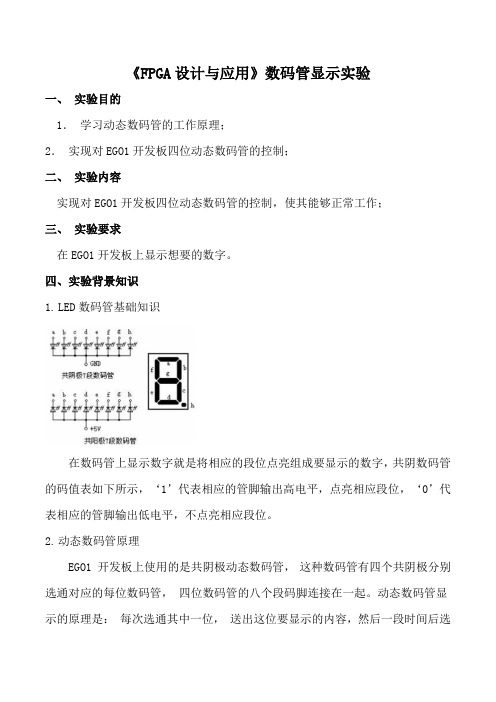

四、实验背景知识1.LED数码管基础知识在数码管上显示数字就是将相应的段位点亮组成要显示的数字,共阴数码管的码值表如下所示,‘1’代表相应的管脚输出高电平,点亮相应段位,‘0’代表相应的管脚输出低电平,不点亮相应段位。

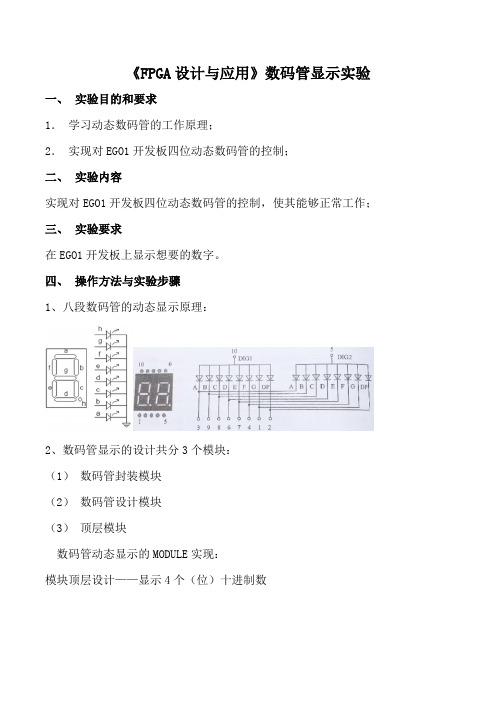

2.动态数码管原理EGO1 开发板上使用的是共阴极动态数码管,这种数码管有四个共阴极分别选通对应的每位数码管,四位数码管的八个段码脚连接在一起。

动态数码管显示的原理是:每次选通其中一位,送出这位要显示的内容,然后一段时间后选通下一位送出对应数据,4 个数码管这样依次选通并送出相应的数据,结束后再重复进行。

这样只要选通时间选取的合适,由于人眼的视觉暂留,数码管看起来就是连续显示的。

五、实验方案及实现1、数码管显示的设计共分3个模块:(1)数码管封装模块(2)数码管设计模块(3)顶层模块数码管封装模块代码:module smg_ip_model(clk,data,sm_wei,sm_duan);input clk;input [15:0] data;output [3:0] sm_wei;output [7:0] sm_duan;integer clk_cnt;reg clk_400Hz;always @(posedge clk)if(clk_cnt==32'd100000)begin clk_cnt <= 1'b0; clk_400Hz <= ~clk_400Hz;endelseclk_cnt <= clk_cnt + 1'b1;reg [3:0]wei_ctrl=4'b1110;always @(posedge clk_400Hz)wei_ctrl <= {wei_ctrl[2:0],wei_ctrl[3]}; reg [3:0]duan_ctrl;always @(wei_ctrl)case(wei_ctrl)4'b1110:duan_ctrl=data[3:0];4'b1101:duan_ctrl=data[7:4];4'b1011:duan_ctrl=data[11:8];4'b0111:duan_ctrl=data[15:12];default:duan_ctrl=4'hf;endcasereg [7:0]duan;always @(duan_ctrl)case(duan_ctrl)4'h0:duan=8'b0011_1111;4'h1:duan=8'b0000_0110;4'h2:duan=8'b0101_1011;4'h3:duan=8'b0100_1111;4'h4:duan=8'b0110_0110;4'h5:duan=8'b0110_1101;4'h6:duan=8'b0111_1101;4'h7:duan=8'b0000_0111;4'h8:duan=8'b0111_1111;4'h9:duan=8'b0110_1111;4'ha:duan=8'b0111_0111;4'hb:duan=8'b0111_1100;4'hc:duan=8'b0011_1001;4'hd:duan=8'b0101_1110;4'he:duan=8'b0111_1000;4'hf:duan=8'b0111_0001;数码管设计模块module test(clk,data);input clk;output [15:0]data;reg clk_1Hz;integer clk_1Hz_cnt;always @(posedge clk)if(clk_1Hz_cnt==32'd2*******-1)begin clk_1Hz_cnt <= 1'b0; clk_1Hz <= ~clk_1Hz;end elseclk_1Hz_cnt <= clk_1Hz_cnt + 1'b1;reg [39:0]disp=40'h1234567890;reg [15:0]data;always @(posedge clk_1Hz)begindisp <= {disp[35:0],disp[39:36]};data <= disp[39:24];endEndmodule顶层模块module smg_ip(clk,sm_wei,sm_duan);input clk;output [3:0]sm_wei;output [7:0]sm_duan;wire [15:0]data;wire [3:0]sm_wei;wire [7:0]sm_duan;test U0 (.clk(clk),.data(data));smg_ip_model U1(.clk(clk),.data(data),.sm_wei(sm_wei),.sm_duan(sm_duan)); endmodule六、实验结果Vivado仿真:上实验板实操:七、实验心得次实验主要学习了利用vivado软件实现数码管的显示,利用编程来实现,并且还对动态数码管的原理进行了一定的学习,包括上次实验学习到的模块化设计,方便程序的调试,程序运行过程中并不顺利,一直没有创建出pin文件夹,最后还是在老师的帮助下完成了pin文件夹的创建,导入到板子后完成了本次实验的设计。

《FPGA设计与应用》数码管显示实验一

《FPGA设计与应用》数码管显示实验一、实验目的和要求

1.学习动态数码管的工作原理;

2.实现对EGO1开发板四位动态数码管的控制;

二、实验内容

实现对EGO1开发板四位动态数码管的控制,使其能够正常工作;

三、实验要求

在EGO1开发板上显示想要的数字。

四、操作方法与实验步骤

1、八段数码管的动态显示原理:

2、数码管显示的设计共分3个模块:

(1)数码管封装模块

(2)数码管设计模块

(3)顶层模块

数码管动态显示的MODULE实现:

模块顶层设计——显示4个(位)十进制数

逻辑实现:

确定当前显示的位

确定当前“位”需要显示的“数”:

将“数”翻译成相应的“段码”

仿真测试台代码编写与仿真测试定义时间标尺:

定义测试Moudle

实例化被测Moudle

定义激励信号与响应信号

构造激励信号:

五、实验数据记录和处理实验代码如下:

设计文件:(部分)

仿真文件:

约束文件:

六、实验结果与分析网表结构:

仿真图像:

实物图:

七、讨论和心得

通过这次实验,我学会了数码管的动态显示,每一个数码管共用一套电路,显示时只需控制哪一个数码管进行显示。

虽然一次只能控制单独一个数码管进行显示,但可以快速切换数码管显示,利用人眼的”视觉暂留"来“同步”进行显示。

最后我明白了我们不要遇到一点困难就退缩,就去向老师同学寻求帮助,自己是自己最好的老师,只有我们靠自己的不断修改出正确结果,才会对这个知识掌握的更加透彻。

《基于fpga按键动态显示设计 》实践报告

《基于fpga按键动态显示设计》实践报告本次实践旨在通过FPGA的实现,设计一套基于按键动态显示的系统,并对其进行实现和测试。

一、实验过程1. 硬件配置通过Xilinx Vivado软件对FPGA进行配置,连接对应的开发板,在连接好开发板之后,根据需要连接对应的按键和LED。

2. 设计硬件逻辑基于FPGA的硬件逻辑设计需要分为以下几个步骤:(1)设计码流译码器为实现按键动态显示,需要对按键进行扫描,并将按下的按键信息转换为对应的二进制码流。

码流译码器需要将码流信息翻译为数字信号,以供后续的逻辑设计使用。

(2)设计LED驱动器需要实现LED驱动器在接收到相应的二进制码流之后,将对应的LED点亮或熄灭。

实现的方式可以是将LED控制器与码流数据进行连接,以实现逐位点亮的效果。

(3)组装硬件逻辑将上述的硬件逻辑进行组装,以便实现目标的按键动态显示效果。

3. 配置Vivado工程文件根据实际需要配置Vivado工程文件,分别设定开发板型号、硬件逻辑文件等,以便在实验时进行调用。

4. 实验测试使用Vivado及开发板进行实验测试,确保按键动态显示系统可以正常工作,并检查相关功能是否实现。

二、实验结果经过上述步骤的实验设计和测试,本次FPGA按键动态显示系统已经实现了预期的功能。

在按下开发板上的按键后,相应的LED灯会逐位点亮,从而实现了按键动态显示的效果。

同时,本次实验还验证了在FPGA硬件逻辑设计中的各项配置和连接操作,进一步加深了对FPGA设计流程的理解和掌握。

三、实验结论通过本次实验,我们成功设计并实现了一套基于按键动态显示的FPGA系统,实验结果表明该系统可以灵活应对各种单片机系统中面临的按键动态显示需求,从而具有较高的实用性和可靠性。

同时,在设计硬件逻辑的过程中,我们也学到了很多有关FPGA逻辑设计的知识和技巧,进一步提升了我们的实践能力。

FPGA液晶显示和数码管显示

Verilog_12864 module lcd (clk, rs, rw, en,dat); input clk;output [7:0] dat;output rs,rw,en;//tri en;reg e;reg [7:0] dat;reg rs;reg [15:0] counter;reg [5:0] current,next;reg clkr;reg [1:0] cnt;parameter set0=6'h0;parameter set1=6'h1;parameter set2=6'h2;parameter set3=6'h3;parameter set4=6'h4;parameter set5=6'h5;parameter set6=6'h6;parameter dat0=6'h7;parameter dat1=6'h8;parameter dat2=6'h9;parameter dat3=6'hA;parameter dat4=6'hB;parameter dat5=6'hC;parameter dat6=6'hD;parameter dat7=6'hE;parameter dat8=6'hF;parameter dat9=6'h10;parameter dat10=6'h12;parameter dat11=6'h13;parameter dat12=6'h14;parameter dat13=6'h15;parameter dat14=6'h16;parameter dat15=6'h17;parameter dat16=6'h18;parameter dat17=6'h19;parameter dat18=6'h1A;parameter dat19=6'h1B;parameter dat20=6'h1C;parameter dat21=6'h1D;parameter dat22=6'h1E;parameter dat23=6'h1F;parameter dat24=6'h20;parameter dat25=6'h21;parameter dat26=6'h22;parameter dat27=6'h23;parameter dat28=6'h24;parameter nul=6'hF1;always @(posedge clk)begincounter=counter+1;if(counter==16'h000f)clkr=~clkr;endalways @(posedge clkr)begincurrent=next;case(current)set0: begin rs<=0; dat<=8'h30; next<=set1; end //*设置8位格式,set1: begin rs<=0; dat<=8'h0C; next<=set2; end //*整体显示,关光标,不闪烁*/ set2: begin rs<=0; dat<=8'h6; next<=set3; end //*设定输入方式,增量不移位*/ set3: begin rs<=0; dat<=8'h1; next<=dat0; end //*清除显示*/dat0: begin rs<=1; dat<=8'hc9; next<=dat1; end //显示第一行dat1: begin rs<=1; dat<=8'hee; next<=dat2; enddat2: begin rs<=1; dat<=8'hdb; next<=dat3; enddat3: begin rs<=1; dat<=8'hda;next<=dat4; enddat4: begin rs<=1; dat<=8'hca; next<=dat5; enddat5: begin rs<=1; dat<=8'hd0; next<=dat6; enddat6: begin rs<=1; dat<="2"; next<=dat7; enddat7: begin rs<=1; dat<="1";next<=dat8; enddat8: begin rs<=1; dat<="E"; next<=dat9; enddat9: begin rs<=1; dat<="D";next<= dat10 ; enddat10: begin rs<=1; dat<=8'hB5; next<=dat11; enddat11: begin rs<=1; dat<=8'hE7; next<=dat12; enddat12: begin rs<=1; dat<=8'hd7;next<=dat13; enddat13: begin rs<=1; dat<=8'hd3; next<=set4; endset4: begin rs<=0; dat<=8'h90; next<=dat14; end //显示第二行dat14: begin rs<=1; dat<="N"; next<=dat15; enddat15: begin rs<=1; dat<="I"; next<=dat16; enddat16: begin rs<=1; dat<="O"; next<=dat17; enddat17: begin rs<=1; dat<="S"; next<=dat18; enddat18: begin rs<=1; dat<=" "; next<=set5; enddat19: begin rs<=1; dat<="I"; next<=dat20; enddat20: begin rs<=1; dat<="I"; next<=set5; endset5: begin rs<=0; dat<=8'h88; next<=dat21; end //显示第三行dat21: begin rs<=1; dat<="F"; next<=dat22; enddat22: begin rs<=1; dat<="P"; next<=dat23 ; enddat23: begin rs<=1; dat<="G"; next<=dat24; enddat24: begin rs<=1; dat<="A"; next<=set6; endset6: begin rs<=0; dat<=8'h98; next<=dat25; end //显示第四行dat25: begin rs<=1; dat<="S"; next<=dat26; enddat26: begin rs<=1; dat<="O"; next<=dat27; enddat27: begin rs<=1; dat<="P"; next<=dat28; enddat28: begin rs<=1; dat<="C"; next<=nul; endnul: begin rs<=0; dat<=8'h00; // 把液晶的E 脚拉高if(cnt!=2'h2)begine<=0;next<=set0;cnt<=cnt+1;endelsebegin next<=nul; e<=1;endenddefault: next=set0;endcaseendassign en=clkr|e;assign rw=0;endmoduleverilog写的LCD1602显示// LCD_Top.v//连接Clock_Gen模块和LCD_Driver模块module LCD_Top(clk_48M,rst,LCD_EN,RS,RW,DB8);input clk_48M,rst;output LCD_EN,RS,RW;output [7:0] DB8;wire clk_LCD; //用于将Clock_Gen模块clk_LCD输出连接至LCD_Driver模块的clk_LCD输入Clock_Gen U1(.clk_48M(clk_48M),.rst(rst),.clk_LCD(clk_LCD));LCD_Driver U2(.clk_LCD(clk_LCD),.rst(rst),.LCD_EN(LCD_EN),.RS(RS),.RW(RW),.DB8(DB8));endmodule// Clock_Gen.v/****************为LCD_Drvier模块产生500Hz的时钟信号**************/module Clock_Gen(clk_48M,rst,clk_LCD);input clk_48M,rst; //rst为全局复位信号(高电平有效)output clk_LCD;wire clk_counter;reg [11:0] cnt; //对时钟进行计数分频wire clk_equ;reg [9:0] count;reg clk_BUF;parameter counter= 50; //多少分频/******************************************************************************** ** 模块名称:分频器** 功能描述:通过计数器实现分频功能.********************************************************************************/ always@(posedge clk_48M)beginif(!rst) //低电平复位cnt <= 12'd0;elseif(clk_equ)cnt <= 12'd0;elsecnt <= cnt+1'b1;endassign clk_equ = (cnt==counter);assign clk_counter = clk_equ;always @(posedge clk_counter or negedge rst)begin //利用计数器分频产生500Hz时钟if(!rst)beginclk_BUF <= 1'b0;count <= 10'b0;endelsebeginif(count == 10'd1000)beginclk_BUF <= ~clk_BUF;count <= 10'b0;endelsebeginclk_BUF <= clk_BUF; //clk_BUF为500Hz的时钟信号count <= count + 1'b1;endendendassign clk_LCD = clk_BUF;//clk_LCD为LCD_Drvier模块所需要的500Hz的时钟信号endmodule// LCD_Driver.v//功能简述:在1602液晶模块上显示字符串,其中第一行显示“Welcom to hx"// 在第二行显示“"//液晶模块为TC1602A,相关特性请参考其数据手册module LCD_Driver(clk_LCD,rst,LCD_EN,RS,RW,DB8);input clk_LCD,rst; //rst为全局复位信号(高电平有效)output LCD_EN,RS,RW;//LCD_EN为LCD模块的使能信号(下降沿触发)//RS=0时为写指令;RS=1时为写数据//RW=0时对LCD模块执行写操作;RW=1时对LCD模块执行读操作output [7:0] DB8; //8位指令或数据总线reg [7:0] DB8;reg [111:0] Data_First_Buf,Data_Second_Buf; //液晶显示的数据缓存reg RS,LCD_EN_Sel;reg [3:0] disp_count;reg [3:0] state;parameter Clear_Lcd = 4'b0000, //清屏并光标复位Set_Disp_Mode = 4'b0001, //设置显示模式:8位2行5x7点阵Disp_On = 4'b0010, //显示器开、光标不显示、光标不允许闪烁Shift_Down = 4'b0011, //文字不动,光标自动右移Write_Addr = 4'b0100, //写入显示起始地址Write_Data_First = 4'b0101, //写入第一行显示的数据Write_Data_Second = 4'b0110, //写入第二行显示的数据Idel = 4'b0111; //空闲状态parameter Data_First = "welcome to hx", //液晶显示的第一行的数据Data_Second = ""; //液晶显示的第二行的数据assign RW = 1'b0; //RW=0时对LCD模块执行写操作assign LCD_EN = LCD_EN_Sel ? clk_LCD : 1'b0;//通过LCD_EN_Sel信号来控制LCD_EN的开启与关闭always @(posedge clk_LCD or negedge rst)beginif(!rst)beginstate <= Clear_Lcd; //复位:清屏并光标复位RS <= 1'b0; //复位:RS=0时为写指令;DB8 <= 8'b0; //复位:使DB8总线输出全0LCD_EN_Sel <= 1'b1; //复位:开启夜晶使能信号//Data_First_Buf <= Data_First;//Data_Second_Buf <= Data_Second;disp_count <= 4'b0;endelsecase(state) //初始化LCD模块Clear_Lcd:beginstate <= Set_Disp_Mode;DB8 <= 8'b00000001; //清屏并光标复位endSet_Disp_Mode:beginstate <= Disp_On;DB8 <= 8'b00111000; //设置显示模式:8位2行5x8点阵endDisp_On:beginstate <= Shift_Down;DB8 <= 8'b00001100; //显示器开、光标不显示、光标不允许闪烁endShift_Down:beginstate <= Write_Addr;DB8 <= 8'b00000110; //文字不动,光标自动右移endWrite_Addr:beginstate <= Write_Data_First;DB8 <= 8'b10000001; //写入第一行显示起始地址:第一行第二个位置Data_First_Buf <= Data_First; //将第一行显示的数据赋给Data_First_Buf?endWrite_Data_First: //写第一行数据beginif(disp_count == 14) //disp_count等于14时表示第一行数据已写完beginDB8 <= 8'b11000001; //送入写第二行的指令RS <= 1'b0;disp_count <= 4'b0;Data_Second_Buf <= Data_Second;state <= Write_Data_Second; //写完第一行进入写第二行状态endelsebeginDB8 <= Data_First_Buf[111:104];Data_First_Buf <= (Data_First_Buf << 8);RS <= 1'b1; //RS=1表示写数据disp_count <= disp_count + 1'b1;state <= Write_Data_First;endendWrite_Data_Second: //写第二行数据beginif(disp_count == 14)beginLCD_EN_Sel <= 1'b0;RS <= 1'b0;disp_count <= 4'b0;state <= Idel; //写完进入空闲状态endelsebeginDB8 <= Data_Second_Buf[111:104];Data_Second_Buf <= (Data_Second_Buf << 8);RS <= 1'b1;disp_count <= disp_count + 1'b1;state <= Write_Data_Second;endendIdel:beginstate <= Idel; //在Idel状态循环enddefault: state <= Clear_Lcd; //若state为其他值,则将state置为Clear_Lcdendcaseendendmodule数码管显示module smg_test_1(keyen,keyclr,clk,smg_du,smg_w);input keyen,keyclr; //an jianinput clk;output [7:0] smg_du;output [3:0] smg_w;reg [25:0] cnt;reg [7:0] smg_dur;reg [3:0] smg_wr;reg keyen_r;reg [3:0] num; //要显示的数据reg [15:0] min; //定义现在时刻寄存器reg sec; //定义标志位always @(negedge clk)begincnt=cnt+1;if(cnt==26'd4*******)begincnt=26'd0;sec=~sec; //zhi weiendendalways @ (keyen)beginif((!keyen)&sec)keyen_r=~keyen_r;endalways @(num)begincase(num)4'h0:smg_dur = 8'hc0;4'h1:smg_dur = 8'hf9;4'h2:smg_dur = 8'ha4;4'h3:smg_dur = 8'hb0;4'h4:smg_dur = 8'h99;4'h5:smg_dur = 8'h92;4'h6:smg_dur = 8'h82;4'h7:smg_dur = 8'hf8;4'h8:smg_dur = 8'h80;4'h9:smg_dur = 8'h90;4'ha:smg_dur = 8'h88;4'hb:smg_dur = 8'h83;4'hc:smg_dur = 8'hc6;4'hd:smg_dur = 8'ha1;4'he:smg_dur = 8'h86;4'hf:smg_dur = 8'h8e;endcaseendalways @ (cnt[11:10])begincase(cnt[11:10])2'b00:num=min[3:0]; //取个位数据2'b01:num=min[7:4]; //取十位数据2'b10:num=min[11:8]; //取百位数据2'b11:num=min[15:12];//取千位数据endcaseendalways @ (cnt[11:10]) //扫描位码begincase(cnt[11:10])2'b00:smg_wr=4'b0111; //扫描最高位2'b01:smg_wr=4'b1011;2'b10:smg_wr=4'b1101;2'b11:smg_wr=4'b1110;//扫描最低位endcaseendalways @(negedge sec)beginif(!keyclr)beginmin=15'h0;endelse if(!keyen_r)beginmin=min+1;if(min[3:0]==4'ha)beginmin[3:0]=4'h0;min[7:4]=min[7:4]+1;if(min[7:4]==4'ha)beginmin[7:4]=4'h0;min[11:8]=min[11:8]+1;if(min[11:8]==4'ha)beginmin[11:8]=4'h0;min[15:12]=min[15:12]+1;endendendendendassign smg_du=smg_dur;assign smg_w=smg_wr;endmodule。

FPGA入门(一)---四位共阴数码管显示

FPGA入门(一)---四位共阴数码管显示--2007。

4。

412--采用4X4键盘进行控制,并显示相应的数字。

3--选自AVR和CPLD的书4--串行联接的七段数码管驱动程序,用了4个数码管5--四位数码管动态显示。

6--高电平选通位选端。

共阴数码管78library i eee;9use i eee.std_logic_1164.all;10use i eee.std_logic_unsigned.all;11entity l ed_7com is12port(clock:in s td_logic;13key_num:IN integer range 0 to 9;14en:out s td_logic_vector(0 to 3);--分别接4个数码管的公共端15display:out s td_logic_vector(0 to 7 ));--接数码管的7 隹刂贫? abcdefgend;1617architecture light of l ed_7com issignal c ounter:integer range 0 to 3;1819begin20process(clock)21variable n um:integer range 0 to 9;22begin23--if rising_edge(clock) thenif c lock'event and c lock='1' then2425if c ounter =3 then26counter<=0;27else28counter<=counter+1;29end if;case counter is3031when 0 =>32en<="1000"; --点亮第一个数码管,屏蔽其它5个数码管33num:=key_num; --显示第一个数34when 1=>en<="0100";3536num:=key_num;37when 2=>38en<="0010";39num:=key_num;40when 3=>en<="0001";4142num:=key_num;43when others=>null;end case;44Page 1 of 2Revision: led_7comcase num is4546when 0=> display <="11111101";--0abcdefg段47when 1=> display <="01100000";--148when 2=> display <="11011011";49when 3=> display <="11110010";50when 4=> display <="01100111";51when 5=> display <="10110110";52when 6=> display <="00111111";53when 7=> display <="11100000";54when 8=> display <="11111111";55when 9=> display <="11100110";56when others => display <="00000000";57end case ;58end if ;59end process;60end ;6162Page 2 of 2Revision: led_7com。

利用按键操作数码管显示

利用按键操作数码管显示数码管是一种常见的显示设备,它由许多小型LED灯组成,可以通过按键操作实现不同数字的显示。

下面是一个利用按键操作数码管显示数字的示例程序:```c#include <Wire.h>#include <Adafruit_GFX.h>#include <Adafruit_LEDBackpack.h>#define BUTTON_PIN 2Adafruit_7segment display = Adafruit_7segment(;void setupinMode(BUTTON_PIN, INPUT_PULLUP);display.begin(0x70);display.setBrightness(15);void loostatic int number = 0;static int prevButtonState = HIGH;int buttonState = digitalRead(BUTTON_PIN);if (buttonState != prevButtonState && buttonState == LOW)number++;if (number > 9)number = 0;}display.writeDigitNum(0, number, false);display.writeDisplay(;}prevButtonState = buttonState;```这个程序使用`Adafruit_7segment`库来控制数码管显示。

首先,需要在Arduino IDE中安装`Adafruit_GFX`和`Adafruit_LEDBackpack`库。

然后,将数码管的SDA引脚连接到Arduino的A4引脚,SCL引脚连接到A5引脚,还需要将按键连接到2号引脚。

在程序的`setup(`函数中,初始化数码管显示,并设置亮度为最大。

FPGA数码管动态显示Verilog

FPGA数码管动态显示(BCD)//smg_top.Vmodule smg_top(clk,rst_n,sm_cs,sm_db,num, //用于仿真dis_data_in //用于仿真);input clk; // 50MHzinput rst_n; // 复位信号,低有效input [9:0] dis_data_in; //用于仿真//reg [9:0] dis_data_in; //显示数据wire [11:0] dis_data_out; //显示数据output [2:0]sm_cs; //数码管片选信号,低有效output [3:0] num; //用于仿真output[6:0] sm_db; //7段数码管(不包括小数点)smg_display smg_display(.clk(clk),.rst_n(rst_n),.dis_data(dis_data_out),.sm_cs(sm_cs),.num(num),.sm_db(sm_db));bin_BCD bin_BCD (.clk(clk),.rst_n(rst_n),.bin( dis_data_in),.BCD_out(dis_data_out));endmodule//bin_BCD.V`timescale 1ns / 1psmodule bin_BCD(clk,bin,rst_n,BCD_out);input [9:0] bin;input clk,rst_n;output [11:0]BCD_out; //十进制BCD码reg [3:0] count;reg [11:0]BCD_out;reg [21:0]shift_reg=22'd0;////////////////////// 计数部分////////////////////////always @ ( posedge clk or negedge rst_n )beginif( !rst_n )count<=4'd0;else if (count==11)count<=4'd0;elsecount<=count+1'b1;end////////////////////// 二进制转换为十进制BCD码/////////////////always @ (posedge clk or negedge rst_n )beginif (!rst_n)shift_reg=22'd0;else if (count==0)shift_reg={12'd0,bin};else if ( count<=10) //实现8次移位操作beginif(shift_reg[13:10]>=5) //判断个位是否>5,如果是则+3beginif(shift_reg[17:14]>=5) //判断十位是否>5,如果是则+3beginshift_reg[17:14]=shift_reg[17:14]+2'b11;shift_reg[13:10]=shift_reg[13:10]+2'b11;shift_reg=shift_reg<<1'd1; //对个位和十位操作结束后,整体左移endelsebeginshift_reg[17:14]=shift_reg[17:14];shift_reg[13:10]=shift_reg[13:10]+2'b11;shift_reg=shift_reg<<1'd1;endendelsebeginif(shift_reg[17:14]>=5)beginshift_reg[17:14]=shift_reg[17:14]+2'b11;shift_reg[13:10]=shift_reg[13:10];shift_reg=shift_reg<<1'd1;endelsebeginshift_reg[17:14]=shift_reg[17:14];shift_reg[13:10]=shift_reg[13:10];shift_reg=shift_reg<<1'd1;endendendend/////////////////输出赋值//////////////////////////always @ ( posedge clk or negedge rst_n )beginif ( !rst_n )BCD_out=12'd0;else if (count==11) //此时8次移位全部完成,将对应的值分别赋给个,十,百位BCD_out<={shift_reg[21:18],shift_reg[17:14],shift_reg[13:10]};endendmodule//smg_display.V`timescale 1ns / 1p smodule smg_display(clk,rst_n,dis_data, //需要显示的数字sm_cs,sm_db,num //用于仿真,选择需要显示的数字);input clk; // 50MHzinput rst_n; // 复位信号,低有效input[11:0] dis_data; //显示数据output [3:0] num; //用于仿真output [2:0]sm_cs; //数码管片选信号,低有效output[6:0] sm_db; //7段数码管(不包括小数点)reg [2:0]sm_cs; //数码管片选信号,低有效(共阴)reg[15:0] cnt; //1ms计数=65536*20nsreg[1:0] cnt_dis;//每毫秒刷新一次显示always @ (posedge clk or negedge rst_n)if(!rst_n)begincnt <= 16'd0;cnt_dis <= 2'd1;endelsebegincnt <= cnt+1'b1;if(cnt==16'hffff)cnt_dis=cnt_dis+1'd1;end//-------------------------------------------------------------------------------parameter seg0 = 7'h3f,seg1 = 7'h06,seg2 = 7'h5b,seg3 = 7'h4f,seg4 = 7'h66,seg5 = 7'h6d,seg6 = 7'h7d,seg7 = 7'h07,seg8 = 7'h7f,seg9 = 7'h6f,sega = 7'h77,segb = 7'h7c,segc = 7'h39,segd = 7'h5e,sege = 7'h79,segf = 7'h71;reg[6:0] sm_dbr; //7段数码管(不包括小数点)reg [3:0] num; //显示数据always @ (posedge clk)case (cnt_dis)2'd1:beginnum <= dis_data[11:8];sm_cs<=3'b011;end2'd2:beginnum <= dis_data[7:4];sm_cs<=3'b101;end2'd3:beginnum <= dis_data[3:0];sm_cs<=3'b110;enddefault:sm_cs<=3'b111;endcasealways @ (posedge clk)case (num) //NUM值显示在两个数码管上4'h0: sm_dbr <= seg0;4'h1: sm_dbr <= seg1;4'h2: sm_dbr <= seg2;4'h3: sm_dbr <= seg3;4'h4: sm_dbr <= seg4;4'h5: sm_dbr <= seg5;4'h6: sm_dbr <= seg6;4'h7: sm_dbr <= seg7;4'h8: sm_dbr <= seg8;4'h9: sm_dbr <= seg9;4'ha: sm_dbr <= sega;4'hb: sm_dbr <= segb;4'hc: sm_dbr <= segc;4'hd: sm_dbr <= segd;4'he: sm_dbr <= sege;4'hf: sm_dbr <= segf;default: ;endcaseassign sm_db = sm_dbr; endmodule//smg_top.vt`timescale 1 ns/ 1 psmodule smg_top_vlg_tst();reg clk;reg rst_n;reg [9:0] dis_data_in; //用于仿真wire [2:0] sm_cs;wire [3:0] num; //用于仿真wire [6:0] sm_db;smg_top i1 (.clk(clk),.rst_n(rst_n),.num(num),.sm_cs(sm_cs),.dis_data_in( dis_data_in),.sm_db(sm_db));initialbeginclk<=1'b0;rst_n<=1'b0;dis_data_in<=10'd987;# 100 rst_n<=1'b1;endalways #10 clk<=~clk; endmodule仿真图:。

vhdl按键控制数码管显示

vhdl按键控制数码管显示

vhdl按键控制数码管显示

在传统的硬件电路设计中,主要的设计文件是电路原理图,而采用HDL 设计系统硬件电路时主要使用HDL编写源程序。

VHDL的主要优点有:

(1)VHDL支持自顶至下的和基于库的设计方法,而且支持同步电路、异步电路、现场可编程门阵列器件FPGA(field programmable gate array)以及其他随机电路的设计。

(2)VHDL语句的行为描述能力和程序结构决定了它具有支持大规模设计的分解和已有设计再利用的功能,它支持系统的数学模型直到门级电路的描述,并且高层次的行为描述与低层次的门级电路描述、结构描述可以混合使用。

(3)VHDL的硬件描述与具体的工艺技术和硬件结构无关,当门级或门级以上的描述通过仿真检验后,再利用相应的工具将设计映射成不同的工艺,因此电路的设计与工艺的改变是相互独立的。

彼此的改变不会产生不良影响,并且VHDL硬件描述语言的实现目标器件的选择范围广泛,可使用各系列的CPLD、FPGA及各种门阵列器件。

FPGA的数码管显示(Verilog)·优选.

FPGA的数码管显示(Verilog)按键与数码管显示module key_led(clk_50M,key,duan_ma,wei_ma);input clk_50M;input [3:0] key; //key为输入的键码的值output [3:0] wei_ma;output [7:0] duan_ma;wire [3:0] key;reg [7:0] duan_ma;reg [3:0] wei_ma;reg [3:0] key_temp; //设置了一个寄存器always @ (posedge clk_50M )beginkey_temp<=key; //把键码的值赋给寄存器case ( key_temp )4'b0111:duan_ma<=8'b1100_0000; //段码,按键后,数码管显示04'b1011:duan_ma<=8'b1001_0000; //段码,数码管显示94'b1101:duan_ma<=8'b1000_0010; //段码,数码管显示64'b1110:duan_ma<=8'b1011_0000; //段码,数码管显示3endcaseendalways @ ( posedge clk_50M )begincase( key_temp )4'b0111:wei_ma<=4'b0111; //位选信号4'b1011:wei_ma<=4'b1011;4'b1101:wei_ma<=4'b1101;4'b1110:wei_ma<=4'b1110;endcaseendendmodule数码管静态显示0-7module led_0_7 (clk,rst,dataout,en);input clk,rst;output[7:0] dataout; //数码管的段码输出output[7:0] en; //数码管的位选使能输出reg[7:0] dataout; //各段数据输出reg[7:0] en;reg[15:0] cnt_scan;//扫描频率计数器reg[4:0] dataout_buf;always@(posedge clk or negedge rst)beginif(!rst) begincnt_scan<=0;endelse begincnt_scan<=cnt_scan+1;endendalways @(cnt_scan)begincase(cnt_scan[15:13])3'b000 :en = 8'b1111_1110;3'b001 :en = 8'b1111_1101;3'b010 :en = 8'b1111_1011;3'b011 :en = 8'b1111_0111;3'b100 :en = 8'b1110_1111;3'b101 :en = 8'b1101_1111;3'b110 :en = 8'b1011_1111;3'b111 :en = 8'b0111_1111;default :en = 8'b1111_1110;endcaseendalways@(en) //对应COM信号给出各段数据begincase(en)8'b1111_1110:dataout_buf=0;8'b1111_1101:dataout_buf=1;8'b1111_1011:dataout_buf=2;8'b1111_0111:dataout_buf=3;8'b1110_1111:dataout_buf=4;8'b1101_1111:dataout_buf=5;8'b1011_1111:dataout_buf=6;8'b0111_1111:dataout_buf=7;default:dataout_buf=8;endcaseendalways@(dataout_buf)begincase(dataout_buf)4'b0000:dataout=8'b1100_0000;4'b0001:dataout=8'b1111_1001;4'b0010:dataout=8'b1010_0100;4'b0011:dataout=8'b1011_0000;4'b0100:dataout=8'b1001_1001;4'b0101:dataout=8'b1001_0010;4'b0110:dataout=8'b1000_0010;4'b0111:dataout=8'b1111_1000;4'b1000:dataout=8'b1000_0000;4'b1001:dataout=8'b1001_1000;4'b1010:dataout=8'b1000_1000;4'b1011:dataout=8'b1000_0011;4'b1100:dataout=8'b1100_0110;4'b1101:dataout=8'b1010_0001;4'b1110:dataout=8'b1000_0110;4'b1111:dataout=8'b1000_1110;endcaseendendmodule最新文件---------------- 仅供参考--------------------已改成word文本--------------------- 方便更改。

利用按键操作数码管显示

实验功能:两位数码管显示功能。

具体功能描述如下:数码管可以显示0-99两位数字,按一下加按键,数字加1;按一下减按键,数字减1。

按下清零按键,数字清零。

程序:/*-----------------------------------------------------------------------*该程序实现的是利用单片机实现两位数码管显示功能。

具体功能描述如下:*数码管可以显示0-99两位数字,按一下加按键,数字加1;按一下减按键,数字减1*此外为了方便,还添加了一个清零按钮,按下清零按钮计数归零。

*-----------------------------------------------------------------------*/#include <reg51.h>#define unchar unsigned char//宏定义#define open 0#define close 1void delayms(char m);//延时函数声明void display();//数码管显示函数声明sbit up = P2^2;//加一按钮sbit down = P2^3;//减一按钮sbit clear = P2^4;//清零按钮sbit Ledshi = P2^0;//十位数码管使能端sbit Ledge = P2^1;//个位数码管使能端unchar LedCode[]={//数码管真值表0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8,0x80,0x90};char count = 0;char ge = 0;char shi = 0;void digitalTube(){if(clear == 0){delayms(10);//按键消抖,是因为实际中按键刚刚被按下时电平抖动不稳定,延时10ms让电平稳定下来再次判断即可if(clear == 0){count = 0;}}while(clear == 0){//松手检测display();}if(up == 0){delayms(10);if(up == 0){count++;if(count == 100)count = 0;}}while(up == 0){//松手检测display();}if(down == 0){delayms(10);if(down == 0){count--;if(count == (-1))count = 99;}}while(down == 0){display();}display();}void display(){//计算各数码管显示的数值ge = count%10;shi = count/10;//关闭数码管使能端,防止乱入Ledge = close;Ledshi = close;//轮流导通两位数码管P0 = LedCode[ge];Ledge = open;//打开个位数码管delayms(1);Ledge = close;P0 = LedCode[shi];Ledshi = open;delayms(1);Ledshi = close;}void delayms(char m){//延时m毫秒char i,j;for(i = 0;i < m; i++)for(j = 0;j < 110;j++); }硬件仿真电路:Welcome To Download !!!欢迎您的下载,资料仅供参考!。

fpga按键控制数码管显示

fpga按键控制数码管显示

按键与数码管显示LED数码管(LEDSegmentDisplays)是由多个发光二极管封装在一起组成8字型的器件,引线已在内部连接完成,只需引出它们的各个笔划,公共电极。

LED数码管常用段数一般为7段有的另加一个小数点,还有一种是类似于3位+1型。

位数有半位,1,2,3,4,5,6,8,10位等等。

LED数码管根据LED的接法不同分为共阴和共阳两类,了解LED的这些特性,对编程是很重要的,因为不同类型的数码管,除了它们的硬件电路有差异外,编程方法也是不同的。

图2是共阴和共阳极数码管的内部电路,它们的发光原理是一样的,只是它们的电源极性不同而已。

颜色有红,绿,蓝,黄等几种。

modulekey_led(clk_50M,key,duan_ma,wei_ma);

inputclk_50M;

input[3:0]key;//key为输入的键码的值

output[3:0]wei_ma;

output[7:0]duan_ma;

wire[3:0]key;

reg[7:0]duan_ma;

reg[3:0]wei_ma;

reg[3:0]key_temp;//设置了一个寄存器

always@(posedgeclk_50M)

begin

key_temp《=key;//把键码的值赋给寄存器

case(key_temp)

4b0111:duan_ma《=8b1100_0000;//段码,按键后,数码管显示0

4b1011:duan_ma《=8b1001_0000;//段码,数码管显示9

4b1101:duan_ma《=8b1000_0010;//段码,数码管显示6。

FPGA 四位数码管显示

module LED_Display(clk,seg,dp,an);input clk; //输入时钟output[6:0] seg; //7个公共段选信号,从低到高对应七段数码管的ABCDEFG output dp; //小数点段选信号DPoutput[3:0] an; //4 位数码管的位选信号reg [15:0] count_for_clk = 0; //分频计数器,65536 分频reg [3:0] an_reg = 0;reg [6:0] seg_reg = 0;assign seg=seg_reg; //7 个段选赋值assign dp=1; //小数点段选赋值assign an=an_reg; //4 个位选赋值parameter //七段数码管显示数字0-9 的段选值zero = 7'b100_0000,one = 7'b111_1001,two = 7'b010_0100,three = 7'b011_0000,four = 7'b001_1001,five = 7'b001_0010,six = 7'b000_0010,seven = 7'b111_1000,eight = 7'b000_0000,nine = 7'b001_0000;//分频计数器always@(posedge clk) begincount_for_clk<=count_for_clk+1;end//段选寄存器赋值,4 位数码管分时复用always@(posedge clk)begincase(count_for_clk[15:14])0: seg_reg<=one; //数码管1 段选1: seg_reg<=two; //数码管2 段选2: seg_reg<=three; //数码管3 段选3: seg_reg<=four; //数码管4 段选endcaseend//位选寄存器赋值,每次只选通一位数码管always@(posedge clk)begincase(count_for_clk[15:14])0: an_reg<=4'b0111;//选通数码管11: an_reg<=4'b1011;//选通数码管22: an_reg<=4'b1101;//选通数码管33: an_reg<=4'b1110;//选通数码管4endcaseendendmodule。

FPGA实验四键盘扫描显示电路

实验四矩形键盘扫描显示电路设计一、实验目的:1、熟悉Verilog语言编写的键盘扫描显示电路。

2、在Libero软件中,并对其电路进行仿真。

二、实验原理:键盘扫描显示电路的Verilog HDL程序主要由3个always模块构成:第一个为模4计数器模块;第二个为完成对键盘进行扫描和编程的功能,在计数器的每个状态从FPGA内部送出一列扫描数据给键盘,然后读入经过去抖处理的4行数据,并根据行,列数据之间的关系,对按键进行编码,确定按下的是哪个键;第三个模块完成键值的显示,即显示按键的编号。

下面是个键盘扫描的程序,大家仿真分析下。

module scankey(outled,scansig,dsw,clk,keyvaule);input clk;//键盘扫描时钟信号input [3:0]dsw;//去抖后的按键信号output [3:0]scansig;//输出扫描信号给键盘output [7:0]keyvaule;output [7:0]outled; //输出七段码给共阴极数码管reg [3:0]scansig;reg [7:0]keyvaule;reg [7:0]outled;reg [1:0] q;always @(posedge clk)beginq<=q+1’b1;endalways @(q or dsw)case(q)2’b00: beginscansig=4’b0111;case (dsw)4'b0111: keyvaule=8'b0111_0111; //key04'b1011: keyvaule=8'b0111_1011; //44'b1101: keyvaule=8'b0111_1101; //84'b1110: keyvaule=8'b0111_1110; //cdefault : keyvaule=8'b1111_1111;endcaseend2’b01: beginscansig=4’b1011;case (dsw)4'b0111: keyvaule=8'b1011_0111; //key14'b1011: keyvaule=8'b1011_1011; //54'b1101: keyvaule=8'b1011_1101; //94'b1110: keyvaule=8'b1011_1110; //ddefault : keyvaule=8'b1111_1111;endcaseend2’b10: beginscansig=4’b1101;case (dsw)4'b0111: keyvaule=8'b1101_0111; //key24'b1011: keyvaule=8'b1101_1011; //64'b1101: keyvaule=8'b1101_1101; //a4'b1110: keyvaule=8'b1101_1110; //edefault : keyvaule=8'b1111_1111;endcaseend2’b11: beginscansig=4’b1110;case (dsw)4'b0111: keyvaule=8'b1110_0111; //key34'b1011: keyvaule=8'b1110_1011; //74'b1101: keyvaule=8'b1110_1101; //b4'b1110: keyvaule=8'b1110_1110; //fdefault : keyvaule=8'b1111_1111;endcaseendendcasealways@(keyvaule)case(keyvaule)8'b0111_0111: outled=8’h3f;8'b0111_1011: outled=8’h66;8'b0111_1101: outled=8’h7f;8'b0111_1110: outled=8’h39;8'b1011_0111: outled=8’h06;8'b1011_1011: outled=8’h6d;8'b1011_1101: outled=8’h6f;8'b1011_1110: outled=8’h5e;8'b1101_0111: outled=8’h5b;8'b1101_1011: outled=8’h7d;8'b1101_1101: outled=8’h77;8'b1101_1110: outled=8’h79;8'b1110_0111: outled=8’h4f;8'b1110_1011: outled=8’h07;8'b1110_1101: outled=8’h7c;8'b1110_1110: outled=8’h71;default: outled=8’h00;endcaseendmodule三、实验步骤:1、先分析Verilog语言编写键盘扫描显示电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

IF(INT='1')THEN

CASE KEY_CODE IS

WHEN"11101110"=>keyvalue<=CONV_STD_LOGIC_VECTOR(0,4);

temp_pressed<='1';

ENTITY KEY_SCAN IS

PORT(

CLK_200:IN STD_LOGIC;

KEY_LIE:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

);

END ENTITY;

ARCHITECTURE ART OF KEY_SCAN IS

SIGNAL CURRENT_STATE,NEXT_STATE:STD_LOGIC_VECTOR(3 DOWNTO 0);

WHEN"1100"=>DIS<="00111001";

WHEN"1101"=>DIS<="01011110";

WHEN"1110"=>DIS<="01111001";

WHEN"1111"=>DIS<="01110001";

WHEN OTHERS=>DIS<="00000000";

END CASE;

END PROCESS;

END ARCHITECTURE;

得到键值后,译成数码管显示的键值,由于只有一个数码管,所以不存在位扫描。

键盘扫描模块

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

);

END COMPONENT;

SIGNAL keyvalue:STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL KEY_CODE:STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL TMP:STD_LOGIC_VECTOR(3 DOWNTO 0);

WHEN"11011110" =>keyvalue<=CONV_STD_LOGIC_VECTOR(4,4);

temp_pressed<='1';

BEGIN

IF(COUNT0>=625)THEN CLK_40K<='1';

ELSE CLK_40K<='0';

END IF;

END PROCESS;

PROCESS(COUNT1)IS

BEGIN

IF(COUNT1>=25000)THEN CLK_1K<='1';

ELSE CLK_1K<='0';

U3:YIMA PORT MAP(TMP,DIS);

INT<=NOT(KEY_HANG(0)AND KEY_HANG(1)AND KEY_HANG(2)AND KEY_HANG(3));

KEY_CODE<=KEY_HANG&KEY_LIE;

PROCESS(CLK_40K)IS

BEGIN

IF(INT='1')THEN

WHEN OTHERS=>NEXT_STATE<="1110";

END CASE;

END PROCESS;

KEY_LIE<=CURRENT_STATE;

END ARCHITECTURE;

键盘扫描的思路是对输出列信号四位轮流输出低电平,检测输入行信号四位是否有低电平,有低电平说明有键码按下,再根据行列的矢量值,判断到底是哪一位按下。

译码模块

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY YIMA IS

PORT(

TMP:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

ELSE COUNT1<=COUNT1+1;

END IF;

IF(COUNT2=249999)THEN COUNT2<=0;

ELSE COUNT2<=COUNT2+1;

END IF;

END IF;

END PROCESS;

PROCESS(COUNT0)IS

WHEN"11101101" =>keyvalue<=CONV_STD_LOGIC_VECTOR(1,4);

temp_pressed<='1';

WHEN"0010"=>DIS<="01011011";

WHEN"0011"=>DIS<="01001111";

WHEN"0100"=>DIS<="01100110";

WHEN"0101"=>DIS<="01101101";

WHEN"0110"=>DIS<="01111101";

DIS:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END ENTITY;

ARCHITECTURE ART OF YIMA IS

BEGIN

PROCESS(TMP)IS

BEGIN

CASE(TMP)IS

WHEN"0000"=>DIS<="00111111";

WHEN"0001"=>DIS<="00000110";

BEGIN

PROCESS(CLK)IS

BEGIN

IF(CLK'EVENT AND CLK='1')THEN

IF(COUNT0=1249)THEN COUNT0<=0;

ELSE COUNT0<=COUNT0+1;

END IF;

IF(COUNT1=49999)THEN COUNT1<=0;

SIGNAL CLK_200,CLK_1K,CLK_40K,INT,temp_pressed:STD_LOGIC;

BEGIN

U1:FENPING PORT MAP(CLK,CLK_200,CLK_1K,CLK_40K);

U2:KEY_SCAN PORT MAP(CLK_200,KEY_LIE);

END IF;

END PROCESS;

PROCESS(COUNT2)IS

BEGIN

IF(COUNT2>=125000)THEN CLK_200<='1';

ELSE CLK_200<='0';

END IF;

END PROCESS;

END ARCHITECTURE;

产生200HZ,1KHZ,40KHZ三中频率

COMPONENT FENPING IS

PORT(

CLK:IN STD_LOGIC;

CLK_200:OUT STD_LOGIC;

CLK_1K:OUT STD_LOGIC;

CLK_40K:OUT STD_LOGIC

);

END COMPONENT;

COMPONENT YIMA IS

PORT(

CLK_40K:OUT STD_LOGIC

);

END ENTITY;

ARCHITECTURE ART OF FENPING IS

SIGNAL COUNT0:INTEGER RANGE 0 TO 1249;

SIGNAL COUNT1:INTEGER RANGE 0 TO 49999;

SIGNAL COUNT2:INTEGER RANGERY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY JIANPAN1 IS

PORT(

CLK:IN STD_LOGIC;

TMP:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

DIS:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END COMPONENT;

COMPONENT KEY_SCAN IS

PORT(

CLK_200:IN STD_LOGIC;

KEY_LIE:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

BEGIN

PROCESS(CLK_200)IS

BEGIN

IF(CLK_200'EVENT AND CLK_200='1')THEN

CURRENT_STATE<=NEXT_STATE;