vxWorks memory

03_VxWorksMemory

内存管理5WDB Memory Pool•在target 上保留给host 工具的内存池–动态加载obj文件–把host shell上以字符串形式输入的参数传给在target 上启动的任务–Host shell和target shell 上临时创建的变量•WDB 管理内存池, 用于保存host 上的数据链等内容•WDB 内存池的大小使用宏WDB_POOL_SIZE来配置–缺省定义为1/16的sysMemTop()-FREE_RAM_ADRS•如果不够, 可以从系统内存池再分配, 加进WDB内存池6System Memory Pool•用于系统中的内存分配–malloc()–创建任务(stack 和TCB)–VxWorks 系统其他的内存需求•系统启动阶段初始化–可以修改USER_RESERVED_MEM在顶端为用户保留一段内存–如果要增加物理内存大小, 需要增加LOCAL_MEM_SIZE •查看BSP相关文档•为内存池增加内存void memAddToPool(pPool, poolSize) pPool是内存起始地址8Allocating/Releasing Memory•动态分配内存void *malloc(nBytes)–分配成功返回内存指针, 分配失败返回NULL.–使用优先匹配算法•释放内存void free (ptr)–邻近block结合–不需要垃圾回收9Examining Memory•内存物理地址与虚拟地址间的映射可以用vmContextShow() 查看11Additional Memory Management Routines•分配内存并清0void *calloc(nElems, size)•修改分配的内存大小void *realloc(ptr, newSize)–内存地址可能会改变–如果newSize比原来的内存大, 内存中的内容不会变–不保证跟原来一样执行对齐操作•返回内存池中最大的一个内存块大小int memFindMax()13Generic Partition Manager•VxWorks提供了底层函数直接创建或操作内存池(内存分区), 内存池的ID作为输入参数以彼此区分–提供给应用层的高层函数malloc() 和free() 通过调用这些底层函数工作, 内存池的ID使用系统内存池(system memory pool)•使用内存分区可以减少内存碎片–使用malloc() 预分配一块内存–在这块内存上创建内存分区–从内存分区上获取(Get)/释放(free) 内存, 不会影响到系统内存池–memPartAlloc()/memPartFree()•内存分区可以具有不同的属性–创建一个板外内存分区, 而不是在板内–创建一个专门服务于指定IO的内存分区14Managing Memory Partitions•内存分区管理函数如下,如果PART_ID 为memSysPartId 则为通常提供给应用层的系统内存操作Generic System Memory PoolmemPartAlloc()malloc()memPartFree()free()memPartShow()memShow()memPartAddToPool()memAddToPool()memPartOptionsSet()memOptionsSet()memPartRealloc()realloc()memPartFindMax()memFindMax()15Creating a Memory PartitionPART_ID memPartCreate(pPool, size)pPool用于创建内存分区的内存起始地址size内存分区的大小•返回内存分区ID(PART_ID), 如果发生错误返回NULL •内存分区的内存(pPool) 可以在:–与系统内存不同的内存区•不在系统内存管理范围内内–从系统内存中分配出来的内存•使用malloc() 分配的内存–内存顶端•参考本章前面的User Reserved Memory Area。

VxWorks实时操作系统内存分配算法优化

VxWorks实时操作系统内存分配算法优化李彦峰;李丽颖;韩广志;徐尚喻【摘要】通过研究VxWorks实时系统内存分配算法,发现VxWorks的内存管理算法的局限性.本文提出通过在VxWorks实时操作系统原有的内存管理功能上添加功能,用于实现固定大小内存分配.新增加的功能利用位图管理内存,通过降低内存管理信息占整个内存块的比率提高内存使用效率,通过将固定大小的内存片合并为一组进行整体的内存分配来降低内存碎片;同时由于减少了内存碎片,从而间接提高内存的分配速度.【期刊名称】《电子世界》【年(卷),期】2016(000)005【总页数】2页(P167-168)【关键词】内存分配;位图管理;内存碎片;分配效率【作者】李彦峰;李丽颖;韩广志;徐尚喻【作者单位】中国科学院软件研究所;中国科学院软件研究所;山东农村信用社;联合社金陵科技学院【正文语种】中文VxWorks内存管理是基于Flat模式实现的,管理框架分为分区(Partition)、Pool(池)、Block(块)。

系统中的具体实现为分区结构体memSysPartition,内存中的空闲内存通过这个结构体的成员变量freelist链接起来。

VxWorks原有的内存分配实现相对而言比较简单——所有任务的内存分配请求调用malloc函数从系统内存分区memSysPartition中获得。

内存请求分配时利用最先适应算法从系统分区结构中来满足内存分配请求,而内存回收时则会将相邻地址的空闲内存给聚合成一个更大的空闲内存。

VxWorks的以上内存分配设计没有考虑小内存分配请求的优化,很容易导致下列问题:第一,当系统中存在大量的小内存分配请求时,就可能使得内存中出现较多的内存碎片;导致系统中存在可用的内存却因为大小不能满足而出现内存分配失败的结果,从而影响系统的稳定性。

第二,freelist链表中的小内存过多时,整个链表长度会很长,从而使得链表的搜索时间效率降低。

内存池在Vxworks系统内存管理中应用

面对在嵌入式系统中广泛存在的数据库类型的 内存需求,即分配多个固定尺寸的内存单元的需求 时,Vxorks系统提供的传统malloc/free带来的内存 碎片、时间不确定等不足,影响了系统的效率,使用 基于内存池技术的内存分配方案无疑是一种很好的 解决之道。

参考文献

1 River W,王金刚,等译.Vxworks程序员指南,北京:清华大学出版 社.2003

图2内存池的结构

万方数据

10期

邹寅伟:内存池在Vxworks系统内存管理中应用

2401

1)内存池控制块结构T_MemPoolCtrl:

typedef struct tag_MemPoolCtrl{

BOOL bIsUsed; SEM—ID smMemPoolSem; WORD32 dwBlockSize; WORD32 dwBlockNum; WORD32 dwFreeBlock;

BYTE 4 pucBlock;

/}指向Block体的指针}/

}T BlockCtrl;

/}Block控制块结构女/

2.2 内存池的操作函数

对内存池的操作包括创建内存池、释放内存池、 从内存池中分配1个内存单元、释放内存单元回内

存池等。由于内存是共享资源所有内存操作时必须

处理信号量问题。 1)Mere—CreatMemPool:创建块内存管理器,参数包

括内存指针(如为NULL,表示自己分配)、块尺寸、

单元尺寸、返回管理器指针。算法如下:

①检验参数合法性。

②初始化结构T—MemPoolCtrl,包括单元尺寸

和块尺寸。设置第1个内存块的指针。如果内存是

外来的,设置块已用标志(已用为0),表示不能增加

块;否则,已用块数设为1。

VxWorks内存

管理内存分区

系统分区管理函数列举如下

创建内存分区

PART_ID memPartCreate(pPool, size) –pPool:指向该分区的内存指针 –size:按字节的内存分区大小 返回值为分区ID(PART_ID)或NULL 该分区内存可以取自: –独立的内存条 –系统内存分区分配的块 –CPU板的RAM

查看内存

附加的内存管理函数

void *calloc(nElems, size) –分配清零内存 void *realloc(ptr, newSize) –重新定义分配块的大小 int memFindMax() –返回系统内存中最大空闲块的大小

内存调整

为了快速,确定的分配固定大小的缓冲区,可以 使用消息队列

Target Server内存池

目标机上保留了一段内存池,用于Tornado工具 –动态加载目标模块 –为目标板上运行的任务传递字符串参数 –为WindSh创建变量 Target Server内存池的初始大小通过 WDB_POOL_SIZE定义。 –默认值为1/16的(sysMemTop()-FREE_RAM_ADRS) 在configAll.h中定义

创建内存分区实例

系统内存池

用于动态内存分配 –malloc() –创建任务(堆栈和TCB) –VxWorks内存请求 系统启动时初始化 –可以修改USER_RESERVED_MEM来保存专用存储器 –向板卡上添加内存需要修改LOCAL_MEM_SIZE的值

分配/释放内存

动态分配内存 –void *malloc(nBytes) –返回值为指向该内存的指针或者NULL 释放分配的内存 –void free(ptr)

Vxworks基础

为各种目标板的硬件功能提供了统一的软件接口 它们包括: 硬件初始化 中断处理和产生 硬件时钟和定时器管理 内存映射和分配 BSP还包括boot Rom和其它启动机制 sysLib和sysALib库是VxWorks可移植的核心

Vxworks操作系统将一切与硬件有关的功能模块都放在BSP库中。该BSP库是硬件与软件的接口,处理硬件的初始化、中断处理与产生、硬件时钟与定时管理、局部和总线内存空间的映射、内存大小定义,等等。能够自行启动目标机、初始化目标机、能够与host通信以下载Vxworks核、把控制权交给Vxworks核来调用用户应用程序等功能。

Tornado 系统结构

POSIX Library

Real-Time Embedded Application

Host

VxSim

Debug Agent

Tornado Plug-ins

Target

Target Server

Launcher

Core OS

BSP

Ethernet

Serial Line

板支持包(BSP)

VxWorks的特点--高度伸缩性的环境

Stand-alone kernel up to full featured OS

0

100

200

300

400

500

Maximum Equipped

File System

Networking

O.S.

m

Memory Requirements (Kbytes)

VxWorks (1)

Vxworks提供了一套丰富的任务间通信机制,包括: ●内存共享(Shared memory):简单的数据共享方法 ●信号量(Semaphore):用于基本的互斥及同步 ●消息队列(Message queues)和管道(pipe): 用于同一CPU上任务间消息的传递 ●套接口(Socket)和远程程序调用(RPC): 用于网络上任务间的通信 ●信号(Signal):用于异常处理 此外,Vxworks提供了三种共享内存的对象(shared-memory objects) 来实现运行在不同CPU上的任务间的高速同步和通信。 ●共享信号量(shared semaphores):有二进制,记数型两种 ●共享消息队列(shared message queues) ●共享内存分区(shared-memory partitions):有系统类型和用户类型

vxworks_08_bspMemory

Chapter8MemoryTornado BSP Training Workshop© Copyright Wind River Systems8-1Wind River SystemsMemory8.1OverviewConfiguring MemoryMMU IssuesCache IssuesMemory ProbesTornado BSP Training Workshop© Copyright Wind River Systems8-2Wind River SystemsWind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-3Overview•Primary memory management issues for BSP:qInitialization.q Access interface.•Main memory initialized by romInit(), bus access (fordevices) initialized in sysHwInit() if required.•BSP will need to support memory access andmanagement strategies:qConfiguration of main memory.qAccess to NVRAM.qVirtual maps for MMU.qCache strategies.q Memory probes.•BSP hardware registers initialized in sysHwInit(), generic devices(except for serial) registers initialized when device is initialized.•To make debugging easier during BSP development disable cache andMMU until:qKernel is successfully activated.q Drivers are tested.MemoryOverview8.2Configuring MemoryMMU IssuesCache IssuesMemory ProbesTornado BSP Training Workshop© Copyright Wind River Systems8-4Wind River SystemsWind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-5Memory Configuration•BSP responsible for configuring main memory for post-kernel operation:qCritical addresses must be defined.qIf MMU is used memory maps must be specified.q Support routines must be provided.•Memory addresses specified in:q config.h - User configurable.q <bsp>.h - Target dependent not user configurable•Required BSP memory support routines:q sysMemTop().q sysNvRamSet().q sysNvRamGet().•Memory maps for MMU will be discussed in a later section of thischapter.Wind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-6RAM LayoutLOCAL_MEM_LOCAL_ADRSRAM_LOW_ADRS sysPhysMemTop()sysMemTop()FREE_RAM_ADRS +WDB_POOL_SIZE WDB PoolVxWorksInitial StackSystemMemory PoolUser Reserved •Figure not to scale.•Figure represents RAM layout after loadable image has been relocated.• A WDB agent memory pool is only required if the Tornado tools are tobe used with the VxWorks image.•User reserved memory not accessed by VxWorks routines.Wind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-7Top of System Memorychar * sysMemTop (void)•Routine returns address of the top of system memory:char * sysMemTop (void){static char * memTop = NULL;if (memTop == NULL){memTop = sysPhysMemTop() - USER_RESERVED_MEM;} return memTop;}•Code in sysLib.c .•Code from reference BSP need not be modified.•Macro USER_RESERVED_MEM specifies the size of user reservedmemory not accessed by VxWorks routines.•If BSP does not support the optional routine sysPhysMemTop() replacecall with LOCAL_MEM_LOCAL_ADRS + LOCAL_MEM_SIZE .Memory Autosizing•Memory autosizing allows the size of physical memory to be configured during initialization.q If autosizing is not activated (or supported) size ofphysical memory is statically defined asLOCAL_MEM_SIZE in config.h.•Autosizing details are architecture dependent, typically:q When DRAM is initialized in romInit(),configuration information is stored in memorycontroller registers or/and software structures.q During autosizing, configuration information is readand interrupted to compute the total size of physicalmemory.•Routine to support autosizing is sysPhysMemTop().Tornado BSP Training Workshop© Copyright Wind River Systems8-8Wind River SystemsWind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-9Memory Autosizing - cont.char * sysPhysMemTop (void)•Routine returns address of top of physical memory.•This routine will provide dynamic memory sizing ifLOCAL_MEM_AUTOSIZE is defined in config.h .•BSP autosizing support is optional. If reference BSPcode is not modified statically defined default valuewill be returned.•sysPhysMemTop() is called by sysHwInit():q Must be called before kernelInit() as this is whensysMemTop() is called.•Kernel activation call:kernelInit ((FUNCPTR) usrRoot, ROOT_STACK_SIZE,#ifdef INCLUDE_WDB(char *) FREE_RAM_ADRS + WDB_POOL_SIZE,#else(char *) FREE_RAM_ADRS,#endifsysMemTop (), ISR_STACK_SIZE, INT_LOCK_LEVEL);Wind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-10NVRAM Configuration•All BSPs must have an NVRAM interface even if thereis no non-volatile RAM in the target environment.Interface must support:qsysNvRamSet()q sysNvRamGet()•Total NVRAM size must be defined in config.h asNV_RAM_SIZE .q If no NVRAM present define as NONE .•If present, NVRAM is used to store boot parameters forloadable images.•Default configuration reserves 255 bytes at thebeginning of NVRAM for boot parameters.•Default boot parameters are specified in config.h , and are staticallylinked into loadable VxWorks images as default if no NVRAM is available.NVRAM Configuration - cont.•NVRAM size and location for boot parameters definedin configAll.h:q BOOT_LINE_SIZE defines NVRAM size reservedfor boot parameters. Default is 255 bytes.q NV_BOOT_OFFSET defines beginning of NVRAMreserved for boot parameters. Default is 0.q To override default values, redefine macros inconfig.h.•Routines to set/get NVRAM contents:q Part of driver located in../src/drv/mem.q If no NVRAM present use../src/drv/mem/nullNvRam.c.q Included in sysLib.c.Tornado BSP Training Workshop© Copyright Wind River Systems8-11Wind River SystemsWind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-12STATUS sysNvRamSet (string, strLen,offset)stringString to be copied into NVRAM.Variable type: char *strLenNumber of bytes to copy. Variable type:int.offset Byte offset into NVRAM, Variable type:int.•Routine will:qCopy string to location NV_BOOT_OFFSET +offset .q Enable NVRAM read/write and write data.•Routine verifies data which is set with a read before returning.STATUS sysNvRamGet (string, strLen,offset)string Where to copy NVRAM. Variable type:char *strLen Number of bytes to copy. Variable type:int.offset Byte offset into NVRAM, Variable tyoe:int.•Routine will:q Copy contents of NVRAM locationNV_BOOT_OFFSET + offset to string.q Read data and terminate string with EOS.Tornado BSP Training Workshop© Copyright Wind River Systems8-13Wind River SystemsWind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-14Caveat For NVRAM Access•NVRAM set/get routines displace offset parameterby NV_BOOT_OFFSET before accessing NVRAM:q offset += NV_BOOT_OFFSET;•If NV_BOOT_OFFSET is greater than zero, provideaccess to NVRAM bytes before boot code with anegative offset values.Start of NVRAM 0BOOT_LINE_SIZENV_BOOT_OFFSETMemoryOverviewConfiguring Memory8.3MMU IssuesCache IssuesMemory ProbesTornado BSP Training Workshop© Copyright Wind River Systems8-15Wind River SystemsWind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-16MMU Overview•MMU is primarily under the control of architecturelibrary, however, BSP is responsible for providingsupport with physical memory description.qPhysical memory description used by MMU to create initial maps to virtual address space.q Default maps are flat, one-to-one between physicaland virtual memory spaces.•MMU initialized by tUsrRoot call to usrMmuInit()which initializes and enables MMU:q First initialization of system memory pool facilities.qSecond initialization of MMU.q MMU available for remainder of post-kernelinitialization.•MMU support can be provided at the basic level or through the optionalproduct VxVMI. Discussion in this section will be restricted to basic MMU support.q For basic MMU support the macro INCLUDE_MMU_BASIC must bedefined in config.h .•Code for usrMmuInit() in ../src/config/usrMmuInit.c .Physical Memory Descriptor•Initial (static) physical memory map defined insysLib.c. It is an array of structures of typeSYS_PHYS_MEM_DESC defined in../h/vmLib.h:typedef struct phys_mem_desc{void *virtualAddr; /* Virtual address. */void *physicalAddr; /* Physical address. */UINT len; /* Length of mapping */UINT initialStateMask; /* State mask for map. */UINT initialState; /* State for map. */} PHYS_MEM_DESC;•States for maps:q Valid or invalid.q Writable or not.q Cacheable or not.Tornado BSP Training Workshop© Copyright Wind River Systems8-17Wind River SystemsWind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-18Physical Memory Descriptor - cont.•Example virtual-to-physical map element:PHYS_MEM_DESC sysPhysMemDesc [] ={{/* Local DRAM */(void *) RAM_LOW_ADRS,(void *) RAM_LOW_ADRS,LOCAL_MEM_SIZE - RAM_LOW_ADRS,VM_STATE_MASK_VALID | VM_STATE_MASK_WRITABLE | VM_STATE_MASK_CACHEABLE, VM_STATE_VALID | VM_STATE_WRITABLE | VM_STATE_CACHEABLE},•Configuration macros used by architecture library toinitialize MMU translation tables.•Configuration macros defined in ../h/vmLib.h.Wind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-19Virtual Memory Mapping•To modify physical-to-virtual memory map(s):qModify sysPhysMemDesc[] (static maps).q Call vmBaseStateSet() (dynamic modification).•Memory mapped on a per page basis:q Page size controlled by macro is VM_PAGE_SIZE defined in configAll.h , Default is 8K (except for PowerPC architectures - 4K).qLength of maps for sysPhysMemDesc[] should be integral number of page size.•Each table entry will require a page table entry inphysical memory:q Sets an upper limit on how many address maps canbe defined.•For VME environments, do not map all of A32 space because of pagetable entry overhead.•Some MMUs will also limit how much memory can mapped, seehardware documentation.Wind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-20Dynamic Virtual MappingSTATUS vmBaseStateSet (context,pVirtual, len, stateMask state)contextContext for map. Variable type:VM_CONTEXT_ID.pVirtualVirtual address to modify state of.Variable type: void *.lenLength of mapping. Variable type: int.stateMaskState Mask. Variable type: Unsigned int.state State. Variable type: Unsigned int.•Routine changes the state of a block of virtual memory.q Use to modify initial memory maps defined bysysPhysMemDesc[].•First argument should be NULL which indicates the current context.•Virtual maps are global for the base MMU support. For information onconstructing and managing private contexts see reference material for VxVMI.Wind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-21Virtual Memory Mapping - cont.•Must map all of physical memory which is to beaccessed. This includes memory mapped devices(Ethernet, SCSI, etc.).•Writing to addresses not included in the virtual-to-physical maps will result in a bus error when the MMUis enabled.•Usually virtual-to-physical maps are configured:qLocal RAM - valid, writable, cacheable.qROM - valid, read-only, often cacheable.qFlash - valid, writable, non-cacheable.qI/O devices - valid, writable, non-cacheable.q Off-target memory - valid, writable, non-cacheable.•Programming flash requires direct access so it should not be cached.However, if flash is read only it can be cached.MemoryOverviewConfiguring MemoryMMU Issues8.4Cache IssuesMemory ProbesTornado BSP Training Workshop© Copyright Wind River Systems8-22Wind River SystemsCache Overview•Cache and MMU configuration is architecturedependent, may be highly integrated or independent.•In VxWorks, if MMU is enabled cache is under MMUcontrol.•Architecture library (cacheLib) provides basic cachemanagement support. BSP responsibilities:q Select appropriate cache library and modes formultiple cache implementations.q If MMU is enabled, memory maps labeled ascacheable or not.q Follow cache strategy guidelines for device drivers,for system devices under BSP control.Tornado BSP Training Workshop© Copyright Wind River Systems8-23Wind River SystemsWind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-24Cache Library InitializationSTATUS cacheLibInit (instMode,dataMode)instModeSpecifies mode for instruction cache.Variable type: CACHE_MODE.dataMode Specifies mode for data cache. Variabletype: CACHE_MODE.•Initializes cacheLib facilities:qCalls architecture specific initialization routine.qPlaces cache in quiet state.q Called by usrInit() before sysHwInit().•Arguments specify modes for instruction/data caches.•CACHE_MODE declared in ../h/cacheLib.h :typedef UINT CACHE_MODE;Wind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-25•Cache mode configuration macros:qUSR_I_CACHE_MODE - first argument.q USR_D_CACHE_MODE - second argument.•Default values for cache mode configuration macrosdefined in configAll.h . If necessary BSP redefines inconfig.h . Choices are defined in ../h/cacheLib.h :#define CACHE_DISABLED 0x00#define CACHE_WRITETHROUGH 0x01#define CACHE_COPYBACK 0x02#define CACHE_WRITEALLOCATE 0x04#define CACHE_NO_WRITEALLOCATE 0x08#define CACHE_SNOOP_ENABLE 0x10#define CACHE_SNOOP_DISABLE 0x20#define CACHE_BURST_ENABLE 0x40#define CACHE_BURST_DISABLE 0x80•Default mode for instruction and data caches is write through.•Cache mode software bits are used by architecture specific cache libraryto configure cache hardware appropriately.Wind River SystemsTornado BSP Training Workshop © Copyright Wind River Systems 8-26•If target supports multiple cache implementations BSPis responsible for selecting appropriate library package:qMacro _ARCH_MULTIPLE_CACHELIB must be defined as TRUE or FALSE in ../h/arch/<someArch>/arch<someArch>.h .q If TRUE supply correct cache initialization routine bydeclaring and initializing sysCacheLibInit in sysLib.c or config.h :FUNCPTR sysCacheLibInit = (FUNCPTR) cacheXLibInit;•For L2 cache, BSP may need to supply separate cachemanagement library:q Maybe obtained from processor manufacturer.•Architecture support will determine if _ARCH_MULTIPLE_CACHELIB isdefined as TRUE . The BSP does not control this.Wind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-27Cache EnableSTATUS cacheEnable (cache)cache Cache to enable. Variable type:CACHE_TYPE.•Enables specified cache type, instruction, data, orbranch using architecture specific routine.•Must undefine macros in config.h to disable:qINCLUDE_CACHE_SUPPORT for any cache type.qUSER_I_CACHE_ENABLE for instruction cache.qUSER_D_CACHE_ENABLE for data cache.q USER_B_CACHE_ENABLE for branch cache.•Routine is called in usrInit() just before kernelInit() call•Default is to define all cache types in configAll.h .•CACHE_TYPE structure is declared in ../h/cacheLib.h :typedef enum /* CACHE_TYPE */{#if (CPU == MC68060)BRANCH_CACHE = _BRANCH_CACHE,#endif /* (CPU == MC68060) */INSTRUCTION_CACHE = _INSTRUCTION_CACHE,DATA_CACHE = _DATA_CACHE} CACHE_TYPE;•Cache types defined in ../h/cacheLib.h :#define _INSTRUCTION_CACHE 0#define _DATA_CACHE 1#define _BRANCH_CACHE 2Wind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-28Cache and Device Code•Guidelines for managing code which accesses devicesare valid whether or not device is BSP independent:qMaintaining cache coherency with respect to DMA devices and hardware registers.qManage device memory access methods.q Preventing out of order instruction execution withRISC processors.•Desired cache management is implemented usingcacheLib :qTo allocate cache safe buffers.q Assign attributes to a driver (system device or BSPindependent device driver) and apply implementation method(s).•Some architectures have special cache libraries. See VxWorks ReferenceManual for more details.Cache and Memory Access•Cache management facilities for devices are related tohow memory accessed by device is allocated.•Memory accessed by devices allocated using:q cacheDmaMalloc().q malloc() and memalign().q Data and bss segment memory.q Special memory region outside of system pool.q Allocation method unknown.•Device register memory:q If memory mapped, will be allocated using one ofthe methods listed above.q If not memory mapped, will not be cacheable.Tornado BSP Training Workshop© Copyright Wind River Systems8-29Wind River SystemsWind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-30cacheLib and Memory Allocationvoid * cacheDmaMalloc (bytes)bytes Number of bytes to allocate. Variabletype: size_t.•Routine allocates cache-aligned, cache-safe buffer for DMA devices. Returns pointer to start of memory.•Cache coherency management for memory allocated with cacheDmaMalloc() is dependent on MMU being enabled or not:qIf MMU is enabled, allocated memory is marked as non-cacheable.q If MMU is not enabled, flush and invalidate macroroutine calls must be inserted into code.•size_t is the unsigned integer type returned by sizeof operator.Wind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-31Cache Macro Routines•cacheLib manages flush, invalidate, and other macroroutines with CACHE_FUNCS and CACHE_LIBstructures (see ../h/cacheLib.h ). Example:typedef struct /* Driver Cache Routine Pointers */{FUNCPTR flushRtn;FUNCPTR invalidateRtn;FUNCPTR virtToPhysRtn;FUNCPTR physToVirtRtn;} CACHE_FUNCS;•Macro routines use routine pointers in CACHE_FUNCS and CACHE_LIB structures. Example:#define CACHE_DRV_FLUSH(pFuncs, adrs, bytes) \(((pFuncs)->flushRtn == NULL) ? OK : \((pFuncs)->flushRtn) (DATA_CACHE, (adrs), (bytes)))•See VxWorks Reference Manual and ../h/cacheLib.h for more details.q There is a CACHE_LIB structure similar to the CACHE_FUNCSstructure shown above.•The third and fourth routines in the CACHE_FUNCS structure translateaddresses between virtual and physical space values.Wind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-32•In general if a particular macro routine is a no-op it’sCACHE_FUNCS or CACHE_LIB routine pointer memberis set to NULL .q For full snooping, flush and invalidate routines areset to NULL .•Macro routines are classified into two groups:q CACHE_DMA_xxxx - These routines flush, invalidate,and perform other operations on memory regions allocated with cacheDmaMalloc().q CACHE_USER_xxxx - These routines flush,invalidate, and perform other operations on(user)memory not acquired using cacheDmaMalloc().•Special purpose memory outside of system memory pool (e.g. DMAtransfer buffers) has no cacheLib management routines.•cacheLib also contains explicit functions which can be called for flush,invalidate, etc. They do not produce portable code. See Tornado BSP Developer’s Kit for VxWorks ,VxWorks Reference Manual , and ../h/cacheLib.h for more details.•CACHE_DMA_XXXX and CACHE_USER_XXXX macrosdefined using lower level macro routinesCACHE_DRV_XXXX.•CACHE_DRV_XXXX macros allow flexibility in providing cache coherency independent of memory allocationmethod:q Routines have additional first argument which is apointer to a CACHE_FUNCS structure.•Developer can use CACHE_DRV_XXXX macros to control cache coherency for:q Driver controlled memory.q Customized cache management.Tornado BSP Training Workshop© Copyright Wind River Systems8-33Wind River SystemsWind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-34Cache Management ExampleSTATUS drvDmaExample (void * pBuf){LOCAL BOOL freeFlag = FALSE;if (pBuf != NULL){/* No buffer cache coherency problems. */pDrvFuncs = cacheNullFuncs;}else{ pBuf = cacheDmaMalloc (BUF_SIZE);pDrvFuncs = cacheDmaFuncs;if (pBuf == NULL)return (ERROR);freeFlag = TRUE;}•pDrvFuncs is declared as pointer to a CACHE_FUNCS structure in aheader file or earlier in this file.Cache Management Example -cont./* Driver initialization and buffer filling. */CACHE_DRV_FLUSH (pDrvFuncs, pBuf, BUF_SIZE);drvWrite (pBuf); /* Output data to device. *//* Driver code. */CACHE_DRV_INVALIDATE (pDrvFuncs, pBuf, BUF_SIZE);drvWait (); /* Wait for device data. *//* Read and handle input data from device. */if (freeFlag)cacheDmaFree (pBuf);/* Return buffer. */return (OK);}Tornado BSP Training Workshop© Copyright Wind River Systems8-35Wind River SystemsCache Strategies and Attributes •Cache strategies for devices will determine whichcacheLib facilities to use.•BSP developer should develop cache strategy basedattributes of driver. Attributes:q WRITE_PIPINGq SNOOPEDq MMU_TAGGINGq USER_DATA_UNKNOWNq DEVICE_WRITES_ASYNCHRONOUSLYq SHARED_CACHE_LINESq SHARED_POINTERS•Attributes will dictate how cacheLib will be of use.Tornado BSP Training Workshop© Copyright Wind River Systems8-36Wind River SystemsWind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-37Example Cache Attribute -WRITE_PIPING•Most RISC processors use write pipelining which candelay delivery of commands or data to a device.•Macro routine CACHE_PIPE_FLUSH will flush writepipeline. Calls placed at appropriate locations in code.• Will not resolve cache issues, driver must still flushcache.•Must know device:qSome devices not impacted by pipelining delays.q Some devices may not function correctly withoutfrequent pipeline flushes to sync. driver and device.•See Tornado BSP Developer’s Kit for VxWorks discussion of otherattributes.•Pipe flush calls will be inserted whenever there is a change from a readsequence to a write sequence of operations, or visa-versa.MemoryOverviewConfiguring MemoryMMU IssuesCache Issues8.5Memory ProbesTornado BSP Training Workshop© Copyright Wind River Systems8-38Wind River SystemsMemory Probes and Busses•VxWorks provides support for bus probes of memory:q vxLib routine to probe an address on the local busfor memory read/write bus errors. Routine isvxMemProbe().q vxALib routine to perform an atomic test and set onlocal bus. Routine is vxTas().•BSP may optionally support system specific bus inquiry routines to probe addresses not on local bus:q Use hook routine supplied for vxMemProbe() toaccess system busses (including an off-board bus ifpresent).q Create test and set routine for external system bus (ifpresent) using vxTas().Tornado BSP Training Workshop© Copyright Wind River Systems8-39Wind River SystemsWind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-40Memory Bus Error ProbeSTATUS vxMemProbe (adrs, mode,length, pVal)adrsAddress to be probed. Variable type: char *.modeRead or write. Variable type: int.length1, 2, or 4 bytes. Variable type: int.pVal Where to return value, or pointer to valueto be written. Variable type: char *.•Routine will trap read/write bus errors; returns OK if nobus error, and returns ERROR after handling bus error.Will not trap other errors, task making call will besuspended if no handler installed.•Read and write specification macros for mode argument are VX_READand VX_WRITE defined in ../h/vxWorks.h .Memory Bus Error Probe Code•vxMemProbe() provides routine pointer to hook BSPspecific memory probe routine:STATUS status;if (_func_vxMemProbeHook != NULL)/* BSP specific probe routine */status = (* _func_vxMemProbeHook)((void *)adrs, mode, length,(void *)pVal);else/* architecture specific probe routine */•_func_vxMemProbeHook variable should beinitialized in sysHwInit() after initialization of busses.Tornado BSP Training Workshop© Copyright Wind River Systems8-41Wind River SystemsWind River SystemsTornado BSP Training Workshop © Copyright Wind River Systems 8-42System Memory Probes•Memory probe hook routine called by vxMemProbe()should determine which bus is being probed based oninput address, and call an appropriate probe routine.q If address corresponds to local bus BSP probe routineshould call VxWorks supplied architecture specific probe routine.•BSP probe routine is also responsible for managing anyerrors generated during probe:q Reset bridge or bus controller registers if necessary.q Execute any device specific exception handlers ifnecessary.•Useful for probing system busses: PCI, VME, ISA, etc.•See Appendix A for discussion of example BSP bus probes.Wind River Systems Tornado BSP Training Workshop © Copyright Wind River Systems 8-43System Test And SetBOOL sysBusTas (adrs)routine Address to be tested and set. Variabletype: char *.•Routine to test and set an address across the systemexternal bus if present. Returns TRUE if the value hadnot been set but is now, returns FALSE if values was setalready.•Routine should provide atomic test and set using indivisible Read Modify Write cycles across externalbus.•Routine calls vxTas() if this is meaningful.•BSP may also supply optional test and clear routine:void sysBusTasClear (adrs)adrs Address to be tested and cleared. Variable type: volatilechar *•Routine clears address set by sysBusTas().•Both routines are optional, it is recommended that they be supported atleast by dummy routines.•Code for both routines placed in sysLib.c .Summary•BSP is responsible for initializing memory andproviding configuration support:q Configure system memory pool parameters andautosizing if supported.q Provide NVRAM access routines.q Provide physical memory descriptor for MMU.q Develop a cache strategy for system devices,initialize the appropriate cache library (or libraries)with appropriate modes, and re-initialize cacheLibfunction pointers in sysHwInit() if required.q Provide libraries for L2 caches if present.q Provide system specific memory probes foraddresses not on local bus if desired. Hook tovxMemProbe() in sysHwInit().Tornado BSP Training Workshop© Copyright Wind River Systems8-44Wind River Systems。

vxworks内存管理_哈尔滨工业大学

嵌入式操作系统

• 用户也可以从USER_RESERVED_MEM划出一 块专用内存分区供某些用户应用程序使用—动态 分配的对象

– 可以自拟内存管理方法,如 • 将该内存区分为若干个内存池 • 每个内存池中的内存块大小固定 • 以固定大小分配各申请者

嵌入式操作系统

3.2 内存管理方式

• 需要对空闲内存块进行合适的管理

嵌入式操作系统

– 用户可以在flash中以文件的形式保存配置信息和日志 信息,存放运行是需要动态加载的应用程序模块,通 过文件传输协议方便的在线升级BootImage、VxWorks 映像和应用程序模块 – 由于大部分嵌入式系统没有类似计算机的硬盘,因 此,flash的存在就显得尤为重要

嵌入式操作系统

– 系统在经过多次内存分配和释放操作之后,可能存在 多个空闲的内存块,后续的内存操作必须能够检测到 这块内存,从而根据一定的算法选择一个合适的内存 块

• 空闲块通常有可用表和自用链两种方法管理

– VxWorks采用自由链管理内存空闲块

嵌入式操作系统

自由链

• 自由链是利用每个空闲内存块的开始几个单元 存放本空闲块的大小及下个空闲块的开始地址 • 管理程序可以通过链首指针可以检索到所有的 空闲块 • 采用自由链管理空闲块,空闲内存块的查询工 作量较大,但由于自由链指针利用的是空闲块 自身的单元,所以不必占用额外的内存块 • 自由链没有大小的限制,容易添加和删除节点 • VxWorks采用自由链管理内存空闲块

– Partition是定长的内存区 – 用户可以从其中分配内存块(buffer或block) – 也可以在某个内存分区再创建一个内存分区

嵌入式操作系统

• VxWorks中主要涉及到的内存单元概念有

Vxworks 操作系统内核

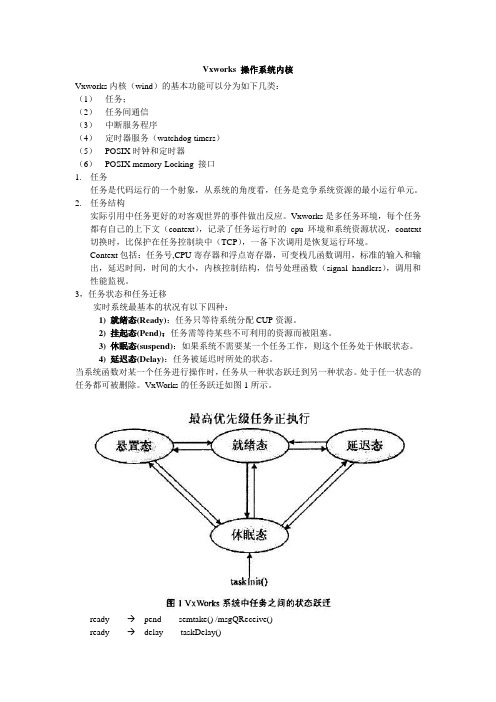

Vxworks 操作系统内核Vxworks内核(wind)的基本功能可以分为如下几类:(1)任务;(2)任务间通信(3)中断服务程序(4)定时器服务(watchdog timers)(5)POSIX时钟和定时器(6)POSIX memory-Locking 接口1.任务任务是代码运行的一个射象,从系统的角度看,任务是竞争系统资源的最小运行单元。

2.任务结构实际引用中任务更好的对客观世界的事件做出反应。

Vxworks是多任务环境,每个任务都有自己的上下文(context),记录了任务运行时的cpu环境和系统资源状况,context 切换时,比保护在任务控制块中(TCP),一备下次调用是恢复运行环境。

Context包括:任务号,CPU寄存器和浮点寄存器,可变栈几函数调用,标准的输入和输出,延迟时间,时间的大小,内核控制结构,信号处理函数(signal handlers),调用和性能监视。

3,任务状态和任务迁移实时系统最基本的状况有以下四种:1) 就绪态(Ready):任务只等待系统分配CUP资源。

2) 挂起态(Pend):任务需等待某些不可利用的资源而被阻塞。

3) 休眠态(suspend):如果系统不需要某一个任务工作,则这个任务处于休眠状态。

4) 延迟态(Delay):任务被延迟时所处的状态。

当系统函数对某一个任务进行操作时,任务从一种状态跃迁到另一种状态。

处于任一状态的任务都可被删除。

VxWorks的任务跃迁如图1所示。

ready →pend semtake() /msgQReceive()ready →delay taskDelay()ready →suspend taskSupend()pend →ready semGive()/msgQsend()pend →suspend taskSuspend()delay →ready expired delay()delay →suspend taskSuspend()suspend →ready taskResume()/ taskActiveate()suspend →pend taskResume()suspend →delayed taskResume()kernelTimeSlice() control round-robin schedulingtaskPrioritySet() change the priority of a tasktaskLock() disable task reschedulingtaskUnlock enable task rescheduling优先级抢占方式抢允许、禁止;如果任务设置了抢占允许位,当此任务处于运行态时,如果高一级优先级任务因某各系统调用阻塞态或挂起态迁移为就绪,则此高优先级任务会立即抢占当前任务的运行,如果设置了禁止,则当前任务不可被处于就绪的高优先级任务抢占,继续运行阻塞,刮起或者改变抢占设置为止。

VxWorks的内存配置和管理

VxWorks的内存配置和管理殷战宁;刘琳【摘要】The memory configuration and management in the environment of VxWorks operating system determine the performance of VxWorks system. This paper expatiates and studies the memory configuration and management method from three aspects: software-hardware configurations, interface function and application optimization.%VxWorks 操作系统环境下内存配置和管理决定了VxWorks的系统性能,重点从软硬件配置、接口函数、应用优化3个方面对内存配置和管理方法进行了阐述和研究。

【期刊名称】《舰船电子对抗》【年(卷),期】2012(035)003【总页数】6页(P104-109)【关键词】VxWorks操作系统;内存控制器;内存管理【作者】殷战宁;刘琳【作者单位】中国电子科技集团公司51所,上海201802;中国电子科技集团公司51所,上海201802【正文语种】中文【中图分类】TP3160 引言对于一般编程人员尤其是Windows等通用平台的编程人员来说,内存配置基本上只要考虑全局变量、局部变量(堆栈变量)的合理安排,内存管理基本上只是使用Malloc、Free等编程接口。

但对于Vx Works嵌入式操作系统而言,由于内存芯片选型、内存的地址空间分配[1]、中央处理器(CPU)级内存管理硬件初始化、映像文件的地址定位、内存的静态和动态占用、内存碎片对系统稳定性的影响等诸多内容都由设计人员来规划和控制,所以涉及内容广泛,需要有一个较好的通篇认识才能解决好与内存有关的问题。

使用VxWorks的一些总结

使用VxWorks的一些总结摘要:本文主要介绍VxWorks操作系统的集成环境Tornado的使用,介绍了PPC平台和X86平台上Tornad o1.0.1集成环境的使用。

内容包括:Tornado集成环境的安装,X86平台上目标机启动软盘的制作;PPC平台上bootrom的制作;一般的使用流程;编译链接;任务调试模式使用;系统调试模式使用。

涉及到的工具主要有CrossWind、Browser、Target Server 、Target Agent、 WindSh、Editor。

1、概述VxWorks操作系统的集成环境叫Tornado。

Tornado集成环境提供了高效明晰的图形化的实时应用开发平台,它包括一套完整的面向嵌入式系统的开发和调测工具。

Tornado环境采用主机-目标机交叉开发模型,应用程序在主机的Windows环境下编译链接生成可执行文件,下载到目标机,通过主机上的目标服务器(Ta rget Server)与目标机上的目标代理(Target Agent)的通信完成对应用程序的调试、分析。

它主要由以下几部分组成:VxWorks高性能的实时操作系统;x 应用编译工具;x 交互开发工具;下面对Tornado集成环境的各组件功能分别介绍:x Tornado开发环境Tornado是集成了编辑器、编译器、调试器于一体的高度集成的窗口环境,同样也可以从Shell窗口下发命令和浏览。

x WindConfig:Tornado系统配置通过WindConfig可选择需要的组件组成VxWorks实时环境,并生成板级支持包BSP的配置。

通过修改config.h可以实现WindConfig的所有功能,并且,可以实现WindConfig不能实现的功能。

x WindSh:Tornado外壳WindSh是一个驻留在主机内的C语言解释器,通过它可运行下载到目标机上的所有函数,包括VxWorks和应用函数。

Tornado外壳还能解释常规的工具命令语言TCL。

Vxworks中的VME总线

在vxworks中地址分配的选择不是一个很重要的问题,本地地址可以使部分VME总线地址空间变得模糊。一些目标板不能对内存总线的低地址进行寻址,因为它们的本地地址从0开始。对于vxworks这不是一个问题,因为所有VME设备的驱动程序都是可以配置的。但设备冲突可能会是一个系统问题。

VME总线中断确认

VME总线中断请求必须得到接收器的确认。一些实施者选择迫使ISR来回应中断的方法,但是更加规范的首选方法是使ቤተ መጻሕፍቲ ባይዱ件自动确认中断请求,并给CPU提供正确的中断向量。

我们并不推荐使用软件中断确认的方法,因为那样会严重影响系统的性能。

系统控制器不是由一个软件设置的寄存器来激活的。对于软件来说,具有能够读取系统控制器状态(开/关)的能力是很有用的。

当一个本地的复位信号被激活时,总线系统控制器应该申明总线复位信号。

系统控制器不需要判断所有的总线优先级,但如果它只判断一个级别,那通常是第三个级别。

VME总线访问的动态总线规模

规范中定义了三种地址类型:

. A16短地址

. A24标准地址

. A32扩展地址

除此之外,板外设备经常有数据长度的限制。很多实施者对同一VME总线提供不同数据长度(D16或D32)不同的窗口大小.

系统控制器负责中断协处理器并且申明一个BERR信号,较好的工具允许这个暂停时间在最短16毫秒到无限长的时间内选择。系统控制器LED可用于判断用户优先级的逻辑状态。

邮箱中断

邮箱中断和位置监视拥有相似的机制,此机制可作为内部处理器的同步方法。

仲裁

如果支持二中选一的仲裁级别,板子应该默认总线请求级别为3,并提供跳线机制。

通常很方便选择总现释放方式,相应的有:RWD(release when done)、ROR(release on

vxworks系统及函数详解

VxWork介绍及编程VxWork介绍及编程一.嵌入式操作系统VxWorks简介VxWorks操作系统是美国WindRiver公司于1983年设计开发的一种嵌入式实时操作系统(RTOS),是嵌入式开发环境的关键组成部分。

良好的持续发展能力、高性能的内核以及友好的用户开发环境,在嵌入式实时操作系统领域占据一席之地。

它以其良好的可靠性和卓越的实时性被广泛地应用在通信、军事、航空、航天等高精尖技术及实时性要求极高的领域中,如卫星通讯、军事演习、弹道制导、飞机导航等。

在美国的F-16、FA-18 战斗机、B-2 隐形轰炸机和爱国者导弹上,甚至连1997年4月在火星表面登陆的火星探测器上也使用到了VxWorks。

实时操作系统和分时操作系统的区别从操作系统能否满足实时性要求来区分,可把操作系统分成分时操作系统和实时操作系统。

分时操作系统按照相等的时间片调度进程轮流运行,分时操作系统由调度程序自动计算进程的优先级,而不是由用户控制进程的优先级。

这样的系统无法实时响应外部异步事件。

实时操作系统能够在限定的时间内执行完所规定的功能,并能在限定的时间内对外部的异步事件作出响应。

分时系统主要应用于科学计算和一般实时性要求不高的场合。

实时性系统主要应用于过程控制、数据采集、通信、多媒体信息处理等对时间敏感的场合。

VxWorks的特点•可靠性操作系统的用户希望在一个工作稳定,可以信赖的环境中工作,所以操作系统的可靠性是用户首先要考虑的问题。

而稳定、可靠一直是VxWorks的一个突出优点。

自从对中国的销售解禁以来,VxWorks以其良好的可靠性在中国赢得了越来越多的用户。

•实时性实时性是指能够在限定时间内执行完规定的功能并对外部的异步事件作出响应的能力。

实时性的强弱是以完成规定功能和作出响应时间的长短来衡量的。

VxWorks 的实时性做得非常好,其系统本身的开销很小,进程调度、进程间通信、中断处理等系统公用程序精练而有效,它们造成的延迟很短。

一种VxWorks内存管理方案

一种VxWorks内存管理方案摘要:探讨嵌入式开发对内存管理的基本要求、嵌入式开发内存管理的关键问题以及给出一种VxWorks内存管理方案,即把除VxWorks系统保留内存以外的内存分为三种类型进行管理:固定大小的缓冲池、动态可变的堆以及由各种固定大小的缓冲区组成的队列。

目前,针对有内存管理单元MMU(Memory Management Unit)的处理器设计的一些桌面操作系统,如Windows、Linux,使用了虚拟存储器的概念。

虚拟内存地址被送到MMU映射为物理地址,实际存储器被分割为相同大小的页面,采用分页的方式载人进程。

大多数嵌人式系统针对没有MMU的处理器设计,不能使用处理器的虚拟内存管理技术,而采用实存储器管理策略。

因而对于内存的访问是直接的,它对地址的访问不需要经过MMU,而是直接送到地址线上输出,所有程序中访问的地址都是实际物理地址;而且,大多数嵌人式操作系统对内存空间没有保护,各个进程实际上共享一个运行空间。

一个进程在执行前,系统必须为它分配足够的连续地址空间,然后全部载人主存储器的连续空间。

由此可见,嵌人式系统的开发人员不得不参与系统的内存管理。

从编译内核开始,开发人员必须告诉系统这块开发板到底拥有多少内存;在开发应用程序时,必须考虑内存的分配情况并关注应用程序需要运行空间的大小。

另外,由于采用实存储器管理策略,用户程序同内核以及其他用户程序在一个地址空间,程序开发时要保证不侵犯其它程序的地址空间,以使得程序不至于破坏系统的正常工作,或导致其他程序的运行异常;因而,嵌人式系统的开发人员对软件中的一些内存操作要格外小心。

1 嵌入式系统中对内存分配的要求嵌人式系统开发对内存分配有很高的要求:① 内存能快速申请和释放,即快速性。

嵌人式系统中对实时性的保证,要求内存分配过程要尽可能地快;② 内存分配保持原子性,即可靠性。

也就是内存分配的请求必须得到满足,如果分配失败可能会带来灾难性的后果;③ 内存应该各尽其用,即高效性。

VxWorks调试手段和方法总结

3

单击 Adcanced 按钮可以打开 Advanced Breakpoint 窗口,如图 4 所示。

图 3 Advanced Breakpoint 窗口 Condition Expression 输入框允许用户给断点附加条件,只有在此条件满足时,断点才会 起作用,程序才会在此暂停。可以在条件框内输入一个整型表达式,或是一个变化的内存值, 只要是非零值,就假定此条件为真。 Number of times to skip 框指定在导致程序暂停之前允许经历的断点次数。 On Break 选项指定了如何处理一个断点: l Keep 将断点定义为永久断点 l Delete 将断点定义为临时断点,程序经历一次此断点即删除它 l Disable 将断点定义为临时断点,程序经历一次此断点即关闭它,以后仍可以经

2 运行程序

单击 CrossWind 工具栏中的 图标或选择 Debug 下拉菜单中的 Run 选项,就会出现

1

Run Task 窗口。如图 1 所示。

图 1 Run Task 窗口 利用 Run Task 窗口指定需要运行的函数和函数参数。函数参数之间以空格键隔开。参 数列表必须是整数或地址,不能是浮点或双精度值、函数调用。选中 Break at Entrypoint 框 可以在函数的第一条语句处设置一个临时断点,这样程序一运行就会停在第一条语句处,用 户可以执行单步,跳过子函数调用或恢复执行。

的每一个起始地址保存下来,可以从下拉列表中选择一个以前显示过的地址。单击 按钮

6

可以更新内存显示。 Memory窗口中显示的内存值不能手工修改。如果想修改某一地址的内存值需要通过

Shell命令m来完成。 在Tools|Options|Debugger窗口中修改Memory Window 选项可以改变Memory窗口中的

vxworks查看剩余内存大小的函数

vxworks查看剩余内存大小的函数VxWorks是一种嵌入式实时操作系统,广泛应用于嵌入式系统开发中。

在开发过程中,了解剩余内存大小对于优化系统性能和确保系统稳定性非常重要。

VxWorks提供了多种方式来查看剩余内存大小,我们将重点介绍两种常用的方法。

方法一:使用sysMemTop()函数VxWorks提供了sysMemTop()函数来获取内存池的顶部地址,通过计算顶部地址与堆栈底部地址之间的差值,即可得到剩余内存大小。

以下是使用sysMemTop()函数的示例代码:```c#include <stdio.h>#include <vxWorks.h>#include <sysLib.h>void printFreeMem(){char* stackBase = NULL;char* memTop = NULL;unsigned int freeMemSize = 0;stackBase = (char*)taskStackBase(taskIdSelf()); // 获取堆栈底部地址memTop = (char*)sysMemTop(); // 获取内存池顶部地址freeMemSize = stackBase - memTop; // 计算剩余内存大小 printf("Free memory size: %u bytes\n", freeMemSize);}int main(){printFreeMem();return 0;}```方法二:使用sysMemInfo()函数VxWorks还提供了sysMemInfo()函数来获取更详细的内存信息,包括总内存大小、已用内存大小和剩余内存大小。

以下是使用sysMemInfo()函数的示例代码:```c#include <stdio.h>#include <vxWorks.h>#include <sysLib.h>void printMemInfo(){MEM_PART_STATS memStats;sysMemInfo(&memStats); // 获取内存信息printf("Total memory size: %u bytes\n", memStats.numBytesTotal);printf("Used memory size: %u bytes\n", memStats.numBytesAlloc);printf("Free memory size: %u bytes\n", memStats.numBytesFree);}int main(){printMemInfo();return 0;}```通过调用sysMemInfo()函数,我们可以获取内存池的详细信息,包括总内存大小、已用内存大小和剩余内存大小。

VxWorks 系统中内存池的应用

Science and Technology &Innovation ┃科技与创新2018年第19期·145·文章编号:2095-6835(2018)19-0145-03VxWorks 系统中内存池的应用安景新1,赵昶宇2(1.海军驻天津八三五七所军事代表室,天津300308;2.天津津航计算技术研究所,天津300308)摘要:针对嵌入式软件内存管理具有快速性、可靠性和高效性的特点,分析了VxWorks 内存管理机制,阐述了内存池结构和工作原理,深入剖析了内存池的分配和释放机制,并对VxWorks 系统下的内存管理提出了建议。

关键词:嵌入式系统;VxWorks ;内存管理;内存池中图分类号:TP316.2文献标识码:ADOI :10.15913/ki.kjycx.2018.19.145利用默认的内存管理函数new/delete 或malloc/free 在堆上分配和释放内存会有一些额外的开销。

如果应用程序频繁地在堆上分配和释放内存,则会导致性能的降低,并且会使系统中出现大量的内存碎片,降低内存的利用率。

经典的内存池(MemPool )技术是一种用于分配大量大小相同的小对象的技术。

该技术可以极大地加快内存分配/释放过程。

如果合理地规划内存池的大小以及数量,可以减少动态分配、释放内存时的消耗,并且可以有效减少内存碎片,避免内存泄漏。

本文以VxWorks 操作系统为例,重点分析了内存池管理机制,并对内存分配和释放给出了解决方案。

1VxWorks 内存管理机制VxWorks 采用用户程序、内核处于同一个地址空间的内存管理策略,软件开发人员在开发程序时必须保证不侵犯其他程序和内核的地址空间,以免破坏系统的正常工作,或导致其他程序异常运行。

内核负责为程序分配内存、动态分配内存和回收内存。

VxWorks 为用户提供2种内存区域,即内存域region 和内存分区partition.region 是可变长的内存区,可以从创建的region 中再分配段segment ,region 的特点是容易产生碎片,但灵活、不浪费;partition 是定长的内存区,用户可以从创建的partition 中分配内存块,或在某个内存分区中再创建一个内存分区。

vxWorks内核解读-5

vxWorks内核解读-5本篇博⽂,我们该谈到Wind内核的内存管理模块了,嵌⼊式操作系统中, 内存的管理及分配占据着极为重要的位置, 因为在嵌⼊式系统中, 存储容量极为有限, ⽽且还受到体积、成本的限制, 更重要的是其对系统的性能、可靠性的要求极⾼, 所以深⼊剖析嵌⼊式操作系统的内存管理, 对其进⾏优化及有效管理, 具有⼗分重要的意义。

在嵌⼊式系统开发中, 对内存的管理有很⾼的要求。

概括地说, 它必须满⾜以下三点要求:实时性, 即在内存分配过程中要尽可能快地满⾜要求。

因此, 嵌⼊式操作系统中不可能采取通⽤操作系统中的⼀些复杂⽽完备的内存分配策略, ⽽是要采⽤简单、快速的分配策略, ⽐如我们现在讨论的VxWorks 操作系统中就采⽤了“ ⾸次适应”的分配策略。

当然了具体的分配也因具体的实时性要求⽽各异。

可靠性, 即在内存分配过程中要尽可能地满⾜内存需求。

嵌⼊式系统应⽤千变万化, 对系统的可靠性要求很⾼, 内存分配的请求必须得到满⾜, 如果分配失败, 则会带来灾难性的后果。

⾼效性, 即在内存分配过程中要尽可能地减少浪费。

在嵌⼊式系统中, 对体积成本的要求较⾼, 所以在有限的内存空间内, 如何合理的配置及管理, 提⾼使⽤效率显的尤为重要实时嵌⼊式系统开发者通常需要根据系统的要求在RTOS提供的内存管理之上实现特定的内存管理,本章研究 VxWorks的Wind内核内存管理机制。

5.1 VxWorks内存管理概述5.1.1 VxWorks内存布局VxWorks5.5 版本提供两种虚拟内存⽀持(Virtual MemorySupport):基本级(Basic Level)和完整级(Full Level)。

基本级虚拟内存以Cache 功能为基础。

当DMA 读取内存前必须确保数据以更新到内存中⽽不是仍缓存在Catch 中。

对于完整级需要购买可选组件VxVMI,其功能为:提供对CPU 的内存管理单元的编程接⼝,同时提供内存保护,它在功能上覆盖了基本级虚存。

VxWorks简介

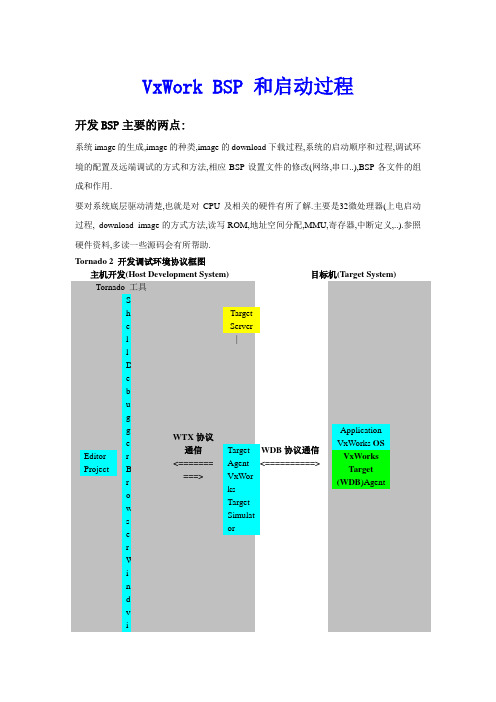

VxWork BSP 和启动过程开发BSP 主要的两点:系统image 的生成,image 的种类,image 的download 下载过程,系统的启动顺序和过程,调试环境的配置及远端调试的方式和方法,相应BSP 设置文件的修改(网络,串口..),BSP 各文件的组成和作用.要对系统底层驱动清楚,也就是对CPU 及相关的硬件有所了解.主要是32微处理器(上电启动过程, download image 的方式方法,读写ROM,地址空间分配,MMU,寄存器,中断定义,..).参照硬件资料,多读一些源码会有所帮助.Tornado 2 开发调试环境协议框图 主机开发(Host Development System) 目标机(Target System)Tornado 工具WTX 协议通信<==========> Editor Project S h e l lDebug g e r B r o w s erWindviTargetServer|Target Agent VxWor ks Target Simulat or WDB 协议通信 <==========> Application VxWorks OS VxWorks Target (WDB )Agentew两个主要两个协议WTX协议(Wind River Tool eXchange): 用于开发机内部Tornado工具与Target Server之间通信.WDB协议(Wind DeBug): 用于主机Target Server与目标机之间的通信.一.基本概念BSP定义:Provides VxWorks with primary interface to hardware environment.作用:在通电后,初始化硬件.支持VxWorks和硬件驱动通信.使hardware-dependent 和hardware-independent在VxWorks系统中很好的结合.主要BSP主要文件目录的组成及主要文件的作用:目录target/config/All:这个目录下的文件是所有BSP文件共享的,不是特别需要不要更改里面的任何文件. configAll.h:缺省定义了所有VxWorks的设置.如果不用缺省的设置,可在BSP目录下的config.h文件中用#define或#undef方式来更改设置.bootInit.c:在romInit.s后,完成Boot ROM的第二步初始化.程序从romInit.s中的romInit()跳到这个文件中的romStart().来执行必要的解压和ROM image的放置.bootConfig.c:完成Boot ROM image的初始化和控制.usrConfig.c: VxWorks image的初始化代码.目录target/config/comps/src:涉及系统核心的components,主要由target/config/All中usrConfig.c中函数调用目录target/config/bspname:包含系统或硬件相关的BSP文件.Makefile一些命令行控制images的生成,参见BSP设置部分及生成下载READMEBSP发布纪录,版本,总的文档config.h包括所有涉及CPU主板的设置及定义(includes,definations),参见BSP设置文件及生成下载configNet.h网络驱动的主要设置文件,主要对END驱动设置.romInit.s汇编语言文件,是VxWorks Boot ROM和ROM based image的入口,参见系统启动部分sysALib.s汇编语言文件,程序员可以把自己的汇编函数放在这个文件里,在上层调用.VxWorks image的入口点_sysInit在这个文件里,是在RAM中执行的第一个函数.sysLib.c包含一些系统相关的函数例程,提供了一个board-level的接口,VxWorks和应用程序可以以system-indepent的方式生成.这个文件还能包含目录target/config/comps/src的驱动. sysScsi.c可选文件用于Scsi设备设置和初始化.sysSerial.c可选文件用于所有的串口设置和初始化.bootrom.hexASIC文件包含VxWorks Boot ROM代码VxWorks运行在目标机上,完整的,连结后的VxWorks二进制文件.VxWorks.sym完全的,连结后带有符号表的VxWorks二进制文件VxWorks.st完全的,连结后,standalone,带有符号表的VxWorks二进制文件BSP用"make"来编译连接生成(Created),而不是用Tornado的工具.BSP和应用程序都可以在"make"或"tornade"上开发(developed)BSP被设置包括以下驱动:中断控制interrupt controller,计时器timer(sys/aux),串口UART(serial),显示屏LCD,键盘Keyboard(opt),触摸屏touch-screen(opt).前面三个是BSP的主要部分.BSP默认的download VxWorks RAM image方式是从ethernet.串口电缆需要用来和开发板(COM1)通信,通过协议WDB.VxWorks Image的种类:Loadable images.ROM-based images---compressed/uncompressed.ROM-Resident images.ROM-resident image 对一些系统内存RAM资源较少的情况下,为了节省资源,只拷贝image 中的数据部分(data segment)到内存RAM,留下程序部分(text segment)在ROM中执行。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

/*当前分配的块数*/ /*当前分配的字数*/ /*累计申请的块数*/ /*累计申请的字数*/

} PARTITION; 对于内存分区中的块,也有两个结构体在管理。包括分配内存时使用的 BLOCK_HDR 和 释放内存时使用的 FREE_BLOCK。

typedef struct blockHdr /* BLOCK_HDR */

int

lockOutLevel /* 中断屏蔽级*/

)

所以,系统内存的起始和结束地址在这里已经确定。

2 系统内存分区的创建

在 kernelInit()里启动的函数 usrRoot()里,根据输入的参数调用系统内存初始化函数 memInit (pMemPoolStart, memPoolSize);函数调用关系如图二。

块在以前的空闲块中间,意味着其后还有一小块未使用的空间,则增加一个空闲块结构管理

并将它加入到系统分区的freeList中。 调整curBlocksAllocated、cumBlocksAllocated、curWordsAllocated和cumWordsAllocated

/*指向对象管理结构*/ /*空闲链表*/ /*内存分区信号量*/ /*分区中的 Words 数。Bytes = Words X 2 */ /*分区中最小块大小,以 Word 为单位*/

2

unsigned options;

/*分区的内存选项,如错误是否上报*/

/* 分配统计 */ unsigned curBlocksAllocated; unsigned curWordsAllocated; unsigned cumBlocksAllocated; unsigned cumWordsAllocated;

如果找不到会按内存选项的设置options决定是否打印失败消息和挂起任务,并设置 error为S_memLib_NOT_ENOUGH_MEMORY,返回空指针。

如果有满足要求的空闲内存块,则调用内存分配算法函数memAlignedBlockSplit(), 从空闲块的高地址开始分配所需空间。并建立一个分配块结构,调整分配块指针。如果分配

(

FUNCPTR rootRtn, /* 用户启动的根任务 */

unsigned int rootMemSize, /* 根任务的堆栈大小 */

char * pMemPoolStart, /* 系统内存起始地址 */

char * pMemPoolEnd, /* 系统内存结束地址 */

unsigned int intStackSize, /* 中断堆栈大小*/

minBlockWords

sizeof (FREE_BLOCK) >> 1;

options

MEM_ALLOC_ERROR_LOG_FLAG|

MEM_BLOCK_ERROR_LOG_FLAG |

MEM_BLOCK_ERROR_SUSPEND_FLAG

| MEM_BLOCK_CHECK;

curBlocksAllocated

} hdr;

DL_NODE node; /*在 BLOCK_HDR 结构体上增加这个 free List 管理节点*/

} FREE_BLOCK;

BLOCK_HDR 和 FREE_BLOCK 在内存中存放规则图三。地址空间由低到高,采用大

端结构。采用 ARM,COLDFIRE,M68K,SH,I86,PPC(PPC604 除外)处理器,要求 4 字节或 8

{

struct blockHdr * pPrevHdr; /*指向前一个申请过的块的地址*/

unsigned

nWords : 31; /*本块的大小,以字为单位*/

unsigned

free : 1;

/*本块是否空闲,TRUE(1)代表空闲*/

#if (_ALLOC_ALIGN_SIZE == 16) /*内存要求 16 字节对齐则填充 8 字节*/

图四 刚初始化后的系统分区

系统内存初始化后,memSysPartition的值如表一。

表一 系统内存分区的初始值

memSysPartition的成员

值

objCore

=memPartClassId

freeList

如图四,指向一个空闲块

sem

ቤተ መጻሕፍቲ ባይዱ

semMInit()返回的信号量

totalWords

(memPoolSize >> 1)

VxWorks 操作系统编程之道

VxWorks 操作系统内存分配解析

嵌入式操作系统分配内存的算法有很多,如最先匹配算法,最优匹配算法,最坏匹配算 法,伙伴算法,还有很多人研究了各式各样的各有优势的算法。目前,常用的有 VxWorks 操 作系统使用的最先匹配算法,linux 操作系统使用的伙伴算法等。

系统分区的标志的 memSysPartition 是 PARTITION 类型的全局静态变量,在程序编译的 时候占用了 BSS 段的内存,其功能相当于电脑的 C 盘描述符,在 VxWroks 定义如下:LOCAL PARTITION memSysPartition;同时使用一个指针指向了它:PART_ID memSysPartId = &memSysPartition。

字节对齐,则不需要填充位,分配的内存空间地址前移 8 字节。

图三 内存块结构体

经过分析memPartAddToPool()函数,memInit ( pMemPoolStart, memPoolSize )初始化

3

后的系统分区分布如图四(传入的参数未对齐的话会在程序里调整到对齐)。整个系统分区 分为两个已分配块和一个空闲块。已分配块就只包含块的头结构体大小,而空闲块则占有除 去两个已分配块的头结构体外的所有空间。同时将空闲块加入到系统分区memSysPartition的 空闲链表freeList中。

RAM_LOW_ADRS:当 VxWorks 映象从 ROM 拷贝到 RAM 时在 RAM 中所处的起始位置;

FREE_RAM_ADRS:由编译器根据代码编译后情况决定,其值为 VxWorks 映象的结束地址

(end)。如果定义了 INCLUDE_WDB,调试代理任务会进行模块的动态加载,占用内存的大小

为 WDB_POOL_SIZE,这时,系统内存就从 WDB_POOL_SIZE 之后到 sysMemTop()。如果

没定义 INCLUDE_WDB,则从 FREE_RAM_ADRS 到 sysMemTop()都是系统内存空间。

操作系统是怎么知道这个区域的呢?原来在内核初始化函数 kernelInit()中会传递系统

VxWorks 操作系统中,内存有分区(partition)和块(block)的概念,代码中的表现是 结构体 PARTITION 和 BLOCK_HDR。一个分区可以分成无数个块。其使用的最先匹配算法 原理是这样的:将整个系统内存当作一个内存分区,创建内存分区时建立一个空闲链表,用 来管理空闲内存块。申请内存时,搜索空闲链表,找到最先满足内存大小的块,建立新的 malloc 块,同时更新空闲链表;释放内存时,空闲的内存将被聚合形成更大的空闲块。

(BLOCK_HDR)) ;就是将申请字节按内存分配的最小对齐方式调整。比如内存要求4字节对 齐,则nbytes是1、2、3或4,经过MEM_ROUND_UP (nBytes)都返回4,是5,6,7或8则返回8。

搜索partId的空闲链表freeList的head指向的空闲块开始搜索,找满足字节数的空闲 块;

作用:将起始地址为pPool,大小为poolSize的这段内存加到内存分区partId中。这里是将整个

系统内存加到系统分区memSysPartition中,正如前面所说的,VxWorks操作系统默认一个系

统分区,malloc()、valloc()、memalign()等函数就是从这个系统分区里获取内存。

void *memPartAlignedAlloc

(

FAST PART_ID partId, /*内存分区的ID*/

unsigned

nBytes, /*申请的字节数*/

unsigned

alignment /*申请内存的边界的对齐值*/

)

{ partId 非法则返回空指针; 调 整 申 请 的 字 节 数 。 真 正 申 请 的 大 小 是 (MEM_ROUND_UP (nBytes) + sizeof

图二 memInit()函数调用关系图 函数memLibInit (void )主要是挂接memLib里的一些分配函数和错误报告函数给全局函

数变量,供其它库文件使用,如_func_valloc = (FUNCPTR) valloc。其它函数的重点落在了

STATUS memPartAddToPool (PART_ID partId, char *pPool, unsigned poolSize);这个函数的

要了解系统分区,PARTITION 结构体相当重要。定义如下:

typedef struct mem_part

{ OBJ_CORE objCore; DL_LIST freeList; SEMAPHORE sem; unsigned totalWords; unsigned minBlockWords;

UINT32

pad[2];

/* 填充 8 字节以方便对齐 */

#endif

} BLOCK_HDR;

typedef struct

/* FREE_BLOCK */

{

struct

{

struct blockHdr * pPrevHdr;

unsigned

nWords : 31;

unsigned

free : 1;

内存初始化的参数。如 kernelInit ((FUNCPTR) usrRoot, ROOT_STACK_SIZE, (char