The International Technology Roadmap for Semiconductors, 2000 Update, Lithography Module. h

集成电路封装基板工艺

ITRS的描述

• The invention of build-up technology introduced redistribution layers on top of cores. While the build-up layers employed fine line technology and blind vias, the cores essentially continued to use printed wiring board technology with shrinking hole diameters. • The next step in the evolution of substrates was to develop high density cores where via diameters were shrunk to the same scale as the blind vias i.e. 50 μm. • The full advantage of the dense core technology is realized when lines and spaces are reduced to 25 μm or less. Thin photo resists (<15 μm) and high adhesion, low profile copper foils are essential to achieve such resolution. • In parallel coreless substrate technologies are being developed. One of the more common approaches is to form vias in a sheet of dielectric material and to fill the vias with a metal paste to form the basic building block.The dielectric materials have little or no reinforcing material. Control of dimensional stability during processing will be essential.

以前瞻性技术预见等战略分析工具支撑关键核心技术的战略突破集成电路领域案例

12020年11月NOV .2020今日科苑MODERN SCIENCE1. 引言科技活动本质上是知识创造活动[1]。

随着科技发展方向的不确定性和复杂性日益增加,国家和地区发展均面临资源有限挑选条件下的关键技术预测、选择以及优化的问题。

运用科学的、具有广泛共识的政策支撑方法识别、遴选和规划前瞻性技术的发展、规划知识创造活动的必要性和有效性已经达成国际共识。

众多发达国家的发展经验证实:“技术预见”及“类预见”活动无疑是一种有效的政策和战略管理工具,其对政策问题识别、政策方案产生与选择、征求意见与修订政策方案的科学支撑和资源优化配置的作用不可忽视[1]。

关于技术预见在政策制定中的功能(function ),Da Costa 等[2]认为基本包含六项:① 为政策提供信息(informing policy ),旨在为政策设计和思考提供知识基础;② 促进政策实施(facilitating policy implementation ),即技术预见通过建立对当前形势和未来挑战的共识及构摘 要:本文深入分析了国际半导体技术发展路线图(ITRS )在引领全球集成电路产业创新发展中的成功经验,旨在回答如何实现技术预见与产业战略发展和支撑政策制定过程深度融合,发挥技术预见等工具在不断修正对长期性、战略性领域未来发展趋势认识和支撑关键领域突破创新实践上的作用。

在此基础上,对我国技术预见与前瞻性技术战略布局、政策制定的趋势发展提出三个思考:一是如何在国家产业技术创新政策决策过程提升战略与系统思维;二是有效整合技术预见与其他决策咨询工具支撑政策全过程;三是以技术预见为核心,构建政府产业技术创新决策咨询分布式网络体系。

关键字:前瞻性技术,技术预见,战略管理,集成电路以前瞻性技术预见等战略分析工具支撑关键核心技术的战略突破:集成电路领域案例余 江1,2,管开轩1,2*,张 越1,2,宋昱晓1,3,4(1 中国科学院科技战略咨询研究院,北京 100190;2 中国科学院大学公共政策与管理学院,北京 100049;3 中国科学院大学 中丹学院,北京 100049;4 中国-丹麦科研教育中心,北京 100049)作者简介:余 江,男,博士,教授,研究员,中国科学院科技战略咨询研究院、中国科学院大学公共政策与管理 学院,博士生导师,研究方向为国家科技政策、新兴技术与产业化、产业创新管理与竞争战略。

PARTICLEADHESIONANDREMOVALINPOST-CMPAPPLICATIONS

dry 55%RH wet 55%RH wet 100%RH

70

60

50

40

30

20

10

0

0

0.2

0.4

0.6

0.8

1

1.2

1.4

1.6

1.8

2

Moment Ratio

Microcontamination Research Lab

RESULTS

Aging Effect on Glass Particle Removal from FPD

Removal Efficiency

u To understand and determine the onset of large adhesion forces after polishing such as the development of covalent bonds.

u Study the removal and adhesion forces for alumina and silica slurry particles from silicon wafers (with different films, TOX, W, Cu, TaN, BPSG, etc.).

u The contaminant particle touches the wafer at one point of contact

u Short range van der Waals force dominates near the surface and the contact area increases.

RESULTS

Imprints on the glass surface ( megasonic cleaned after aging)

技术路线图(TechnologyRoadmap)

技术路线图(Technology Roadmap)什么是技术路线图技术路线图是指应用简洁的图形、表格、文字等形式描述技术变化的步骤或技术相关环节之间的逻辑关系。

它能够帮助使用者明确该领域的发展方向和实现目标所需的关键技术,理清产品和技术之间的关系。

它包括最终的结果和制定的过程。

技术路线图具有高度概括、高度综合和前瞻性的基本特征。

技术路线图是一种结构化的规划方法,我们可以从三个方面归纳:它作为一个过程,可以综合各种利益相关者的观点,并将其统一到预期目标上来。

同时,作为一种产品,纵向上它有力地将目标、资源及市场有机结合起来,并明确它们之间的关系和属性,横向上它可以将过去、现在和未来统一起来,既描述现状,又预测未来;作为一种方法,它可以广泛应用于技术规划管理、行业未来预测、国家宏观管理等方面。

技术路线图的缘起技术路线图最早出现在美国汽车行业,汽车企业为降低成本要求供应商提供他们产品的技术路线图。

20世纪70年代后期和80年代早期,摩托罗拉和康宁公司先后采用了绘制技术路线图的管理方法对产品开发任务进行规划。

摩托罗拉主要用于技术进化和技术定位,康宁公司主要用于公司的和商业单位战略。

继摩托罗拉和康宁公司之后,许多国际大公司,如微软、三星、朗讯公司,洛克-马丁公司和飞利普公司等都广泛应用这项管理技术。

2000年英国对制造业企业的一项调查显示,大约有10%的公司承认使用了技术路线图方法,而且其中80%以上用了不止一次(C.J.Farrukh, R.Phaal, 2001)[1]。

不仅如此,许多国家政府、产业团体和科研单位也开始利用这种方法来对其所属部门的技术进行规划和管理。

技术路线图真正的奠基人是摩托罗拉公司当时的CEO—Robert Galvin。

当时,Robert Galvin在全公司围发动了一场绘制技术路线图的行动,主要目的是鼓励业务经理适当地关注技术未来并为他们提供一个预测未来过程的工具。

这个工具为设计和研发工程师与做市场调研和营销的同事之间提供了交流的渠道,建立了各部门之间识别重要技术、传达重要技术的机制,使得技术为未来的产品开发和应用服务。

在如今的科技界,摩尔定律不管用了吗?

在如今的科技界,摩尔定律不管用了吗?本文只能在《好奇心日报(只能在《好奇心日报()》发布,即使我们允许了也不许*本文转载*旧金山电 — 数十年以来,计算机行业始终信奉着一大指导原则:工程师们总能找到办法让电脑芯片上的电子元件体积更小、运行速度更快、价格更便宜。

在摩尔定律的引领下,各大科技公司从生产大型电脑主机的 1960 年代一直走到了智能机风靡的今天。

然而现在,一个全球芯片制造商联盟却做出了一项和摩尔定律背道而驰的决定。

这表明,计算机行业可能需要重新考量硅谷创新精神的核心原则了。

如今,芯片科学家几乎就快能够处理像原子那么小的材料了。

等用接下来五年左右的时间达成这一目标后,他们可能就要触碰到半导体能够达到的最小体积极限。

之后,芯片科学家们可能得寻找其他可以代替硅的电脑芯片生产原料或者新的设计思路,才能让电脑变得更加强大。

人们很难夸大摩尔定律对于整个世界的重要性。

虽然摩尔定律听上去很有条理,但实际上,它并不是像牛顿运动定律这样的科学规律——它只不过是描述了一种让电脑价格成倍降低的生产制造过程变化的速度。

1965 年,英特尔联合创始人戈登·摩尔(Gordon Moore)最早观察发现,单枚硅片表面能够刻印的电子元件数量每隔一段固定的时间就会翻一倍。

而且在可以预见的未来,这一情况还会继续延续下去。

图片版权:Paul Sakuma / 美联社摩尔观察到这一现象的时候,电子元件最密集的存储芯片还只能容纳约 1000 比特的信息。

换言之:1980 年代,世界上最强大的超级计算机 Cray 2 的体积相当于一台工业用洗衣机,如果放在今天,这台设备造价将会超过 1500 万美元;与之形成鲜明对比的是,2011 年上市的 iPad 2 仅 400 美元,可以轻松放在膝头使用,但它却拥有比Cray2 更强的计算能力。

请注意,和更新的 iPad 设备相比,那款 iPad 2 运行速度已经算是慢的了。

如果没有过去非凡的进步,就不会有如今的计算机行业,Google、亚马逊等公司运营的云计算数据中心造价也将会贵得不可思议;你将无法使用智能机下载使用应用软件,利用应用软件打车回家、叫外卖;破译人类基因组、教会机器倾听等科学突破也不会出现。

MEMS微系统 复习红宝书(北理)

20.BGA : Ball Grid Array 球状矩阵排列

21.SHM:Structural Health Monitoring 结构健康监测

22.ICT:Information and Communications Technologies 信息与通信技术

23.MtM More than Moore 超越摩尔定律

24.FEA:Finite Element Analysis 有限元分析

25.SEM:Scanning Electron Microscope 扫描电子显微镜

12.ITRS International technology Roadmap for Semiconductor 国际半导体技术规

划

.

27.DARPA :Defence Advanced Research Projects Agency of theDepartment of

成,它们各具不同的能带隙。这些材料可以是 GaAs 之类的化合物,也可以是 Si-Ge 之类的半导体合金。按异质结中两种材料导带和价带的对准情况可以把异 质结分为Ⅰ型异质结和Ⅱ型异质结两种。 12.微加工:以微小切除量获得很高精度的尺寸和形状的加工。 13.引线键合:引线键合(Wire Bonding)是一种使用细金属线,利用热、压力、 超声波能量为使金属引线与基板焊盘紧密焊合,实现芯片与基板间的电气互连和 芯片间的信息互通。 14. 倒装芯片:倒装芯片(Flip chip)是一种无引脚结构,一般含有电路单元。 设 计用于通过适当数量的位于其面上的锡球(导电性粘合剂所覆盖),在电气上和 机械上连接于电路。 15.热声焊:热声焊是一种固态键合技术,为热压结合与超音波结合的混合方法。 它可完成电路片与芯片、腔体之间的电连接。 16.各向异性粘接:用各向异性导电胶(主要使用单一或双重成分的环氧树脂)完 成对电路基板与倒装芯片之间的互连。 17.柔性印刷电路:即 FPC,是以聚脂薄膜或聚酰亚胺为基材制成的一种具有高度 可靠性,绝佳曲挠性的印刷电路。通过在可弯曲的轻薄塑料片上,嵌入电路设计, 使在窄小和有限空间中堆嵌大量精密元件,从而形成可弯曲的挠性电路。 18.高深宽比:垂直于加工表面的高度与其加工表面上所具有的特征尺寸的比值 大。 19. 盲孔: 定义 1.位于印刷线路板的顶层和底层表面,具有一定深度,用于表层线路和下面 的内层线路的连接,孔的深度通常不超过一定的比率(孔径)。

一种Sigma-DeltaADC中抽取滤波器的研究

重庆大学硕士学位论文ABSTRACTThis thesis focuses on the study and design a digital decimation filter in the Sigma-Delta ADC which used in the high-end audio device. Because of the merits, such as high-linearity, high-resolution and easy integratoin with digital circuit, it is widely used in the area of audio process, wireless communication and precision measurement. As the advance of the technology, Sigma-Delta ADC will be used in the wideband field, such as the digital video process. The Sigma-Delta ADC has two main parts, the frontend modulator and backend digital decimation filter. The modulator has two functions, the first is oversampling the input, the second is moving the qualitazation noise to higher frequency which called noiseshaping. The backend decimation filter downsamples the signal to the Nyquist Rate,at the same time,filters out the out-of-band quantization noise which be shaped by the modulator. So,the SNR in the baseband rises.The followings are the main content done in this thesis.Firstly, the whole design adopt a Top-down approach. Base on the specification that system must meet, the stucture and type of the filter need to be choosen in the beginning. The filter is implement with multistage multirate stucture. The CIC filter is choosen to be the first stage, followed by two stage of halfband filter and one CIC compensation filter. After comparing and analysis, the CIC compensation filter locates between the two halfband filters is the best choice for calculation efficient. At the same time, for further increase the calculation efficient, the last three stage use a two-phase structure which let the operation of the filter at the downsampled rate.Secondly, the filter is designed in the Matlab with FDAtool toolbox and Fdesign toolbox. The stopband attenuation of the filter is 120dB, passband ripple less than 0.01dB. Also the filter supports 24/20/16 bits output wordwidth, 96/48 kHz output frequency. After the coefficients of the flilter is calculated, they need to be coded into CSD. Due to the wordlength of the coefficient and the output have the effect on the resolution of the filter, after analysis, this design adopt 24 bit coefficient quantization and the most 24 bit output wordlength for meeting the design specifications.Thirdly, the design and testbench are written by Verilog HDL. Using Simulink which embeded in the Matlab and Sdtoolbox to build the model of the Sigma-Delta modulator. Thismodel is used to generate the dataflow of output of the modulator which is used to simulate and validate the function of the filter in the Modelsim.Finally, after validation the code, the next step of the design is synthesis the Verilog HDL by Design Compiler to get the netlist. Then the layout of the design can be achieved by the Auto-Place-and-Route tool, Astro. The technology library in my design is 0.18 um standard cell library. The area of the chip is 1.7mm*1.7mm. As such design adopts the top-down design method, it has good capability of duplication and transplantation. The operation of digital filter is a pure DSP process, so it is suitable for the use of FPGA to implement the filter. At last, Quartus, a FPGA software, is used to simulate the implement of the filter in the FPGA.Keywords: Sigma-Delta ADC, CSD, Decimation filter, CIC filter1 绪论1.1 引言根据“国际半导体技术路线”(International Technology Roadmap for Semiconductor, ITRS)的报告,CMOS工艺的特征尺寸会在未来至少十年当中继续降低,到2013年将会达到32nm。

半导体发展史

前言自从有人类以来,已经过了上百万年的岁月。

社会的进步可以用当时人类使用的器物来代表,从远古的石器时代、到铜器,再进步到铁器时代。

现今,以硅为原料的电子元件产值,则超过了以钢为原料的产值,人类的历史因而正式进入了一个新的时代,也就是硅的时代。

硅所代表的正是半导体元件,包括记忆元件、微处理机、逻辑元件、光电元件与侦测器等等在内,举凡电视、电话、电脑、电冰箱、汽车,这些半导体元件无时无刻都在为我们服务。

硅是地壳中最常见的元素,许多石头的主要成分都是二氧化硅,然而,经过数百道制程做出的积体电路,其价值可达上万美金;把石头变成硅晶片的过程是一项点石成金的成就,也是近代科学的奇蹟!在日本,有人把半导体比喻为工业社会的稻米,是近代社会一日不可或缺的。

在国防上,惟有扎实的电子工业基础,才有强大的国防能力,1991年的波斯湾战争中,美国已经把新一代电子武器发挥得淋漓尽致。

从1970年代以来,美国与日本间发生多次贸易摩擦,但最后在许多项目美国都妥协了,但是为了半导体,双方均不肯轻易让步,最后两国政府慎重其事地签订了协议,足证对此事的重视程度,这是因为半导体工业发展的成败,关系着国家的命脉,不可不慎。

在台湾,半导体工业是新竹科学园区的主要支柱,半导体公司也是最赚钱的企业,台湾如果要成为明日的科技硅岛,半导体工业是我们必经的途径.半导体的起源在二十世纪的近代科学,特别是量子力学发展知道金属材料拥有良好的导电与导热特性,而陶瓷材料则否,性质出来之前,人们对于四周物体的认识仍然属于较为巨观的瞭解,那时已经介于这两者之间的,就是半导体材料。

英国科学家法拉第(MIChael Faraday,1791~1867),在电磁学方面拥有许多贡献,但较不为人所知的,则是他在1833年发现的其中一种半导体材料:硫化银,因为它的电阻随着温度上升而降低,当时只觉得这件事有些奇特,并没有激起太大的火花;然而,今天我们已经知道,随着温度的提升,晶格震动越厉害,使得电阻增加,但对半导体而言,温度上升使自由载子的浓度增加,反而有助于导电,这也是半导体一个非常重要的物理性质。

晶圆凸块技术

晶圆突点技术,产业准备好了吗?摘要: Wafer bumping is a technology whose inherent benefits remain unrealized. While the economy of scale is obvious, limitations include insufficient infrastructure and applications that justify the cost. Yet service providers, captive and merchant operations continue to propel the technology with advanced equipment and streamlined processes that promise to harvest its full potential.Wafer bumping, where interconnections are formed on an entire wafer prior to dicing, promises tremendous technical and economic advantages over traditional single-die packaging. Yet the introduction of wafer bumping as a back-end process faces significant economic hurdles. Beyond investment in infrastructure, the operations cost must compete with sophisticated wire bonding technologies and still produce higher process yields. Today, the percentage of bumped wafers remains very low compared with traditional single-die packaged chips, but interest is growing as infrastructure builds and applications justify the initial cost premium. Once volume becomes established, cost will shift in favor of bumping, and the technology will accelerate at a rapid adoption rate.From a technology perspective, inherent benefits also offer advantages that should propel the technology. An under-bump metallization (UBM) interface layer between wafer pads and bumps provides better bonding and a barrier to prevent materials migration. Redistribution technology, which involves a rerouting of the interconnections of peripheral bond pads to a new array for the package I/Os, accommodates wider pitches that enable both UBM and larger bumps. The bumps themselves provide electrical, mechanical and thermal interconnection, supplying direct contact between the package and the device. This direct interconnection reduces signal propagation delay and relieves the constraints of power and ground distribution. Finally, replacing wire bonds with bump interconnects reduces package size and weight.Bump formation technologiesTwo commonly used wafer bumping methods are screen deposition and electroplating. Each has a different approach to depositing solder on the wafer, and both have been proven in production for some years. Applications range from under-the-hood electronics to high-end logic and CPUs employing these bumping methods. Pitch, necessary I/O count,start-up cost and volume are critical criteria that dictate which method works best.Screen deposition is a lower-cost bumping method, generally for pitches greater than 150 μm, practiced by a number of companies today. Theprocess involves squeezing solder paste through a screen stencil to deposit bumps directly to die pads on the wafer. With modified stencils, yields are in the 99% range on all wafer sizes using both eutectic and lead-free materials. According to Joachim Kloeser, CTO at Ekra GmbH (B?nnigheim, Germany), special modifications to traditional screen printers are required. For example, high-resolution vision systems to recognize small structures, flexibility for teaching fiducials, high alignment accuracy, integrated cleaning, automatic wafer handling and high process repeatability must all be incorporated into a successful wafer bumping screen printer machine.Electroplating technology involves starting at the UBM and performing template, plate, strip, reflow and etch series of processes to form the bump interconnections. Electroplating offers excellent control on deposition rates and uniformity of bumps for void-free formation; variations in bump size can be controlled to within ±1 μm. The bath chemistry and composition must be controlled since it affects properties such as alloy composition, surface roughness or hardness, and crystalline stru cture. This bumping method can produce much finer bumps in the <100 μm range, with tighter pitches and linewidths and corresponding greater bump densities (Fig. 1). Another benefit of electroplating is that yields significantly outperform screen deposition bumping. While startup costs may be higher, some packaging foundries are now offering 300 mm electroplated wafer-level packaging at very competitive prices, which will drive the overall cost more in line with traditional packaging operations. Since the International Technology Roadmap for Semiconductors (ITRS) forecasts continued reduction in bump pitches, lead-free and power redistribution, electroplating will surely capture market share associated with higher-volume operations.Some alternative methods of bump formation build on lithography associated with front-end processes and wire bonding borrowed from back-end interconnection processes. In back-end operations, the resist layers are thick (20-100 μm) with large feature sizes (3-150 μm), which pose special challenges to lithography technology. Y et applications demanding smaller-sized bumps with narrower pitches justify some form of lithography.Forming wafer bumps via lithography can be accomplished by either a photolithography stepper or with a proximity mask aligner, depending on the performance vs. cost equation parameters particular to individual manufacturers. Key subsystems critical to developing a high-performance wafer bumping stepper system include high-fidelity projection lens/illumination, automated substrate alignment, precision X/Y stage, automated reticle handling and storage, and astate-of-the-art suite of metrology sensors. "There is a trend in the industry toward smaller-area array devices and, therefore, feature sizes in the range of 10-15 μm," said Elvino da Silveira, president of Azores Corp. (Wilmington, Mass.). "Azores' photolithography stepper technology is already positioned for that change, with deposition capabilities well beyond traditional technologies."Stud and gold ball bumping is performed by machines based on wire-bond technology that bump singulated die or entire wafers for high-performance devices, R&D and prototyping, batch runs, and contract assembly production. Gold bumping provides superior electrical and thermal connectivity, low inductance values, reduced electrical loss, clean processing, and lower power requirements. One advantage is that these solderless bump connections eliminate the need for UBM and fluxing.Bumps are formed by a modified bonder that uses thermosonic energy to first attach standard 1 mm gold wire to the die pads and then shear the top of the wire without leaving a tail. With the most advanced bonders available today, the result is a planar, flat-top bump that requires no coining in a single-step process (Fig. 2 ). "Gold bumps that are bonded and planarized to a programmable height between 10 and 30 μm with 2 μm co-planarity find application in image sensors, high-brightness LEDs and SA W filters," said Bruce Hueners of Palomar Technologies (Vista, Calif.).Solder reflowSolder bumps must undergo a reflow process to become fully stabilized. Since their composition may be high lead content, eutectic or lead-free, the equipment and process must be capable of handling a wide range of temperature profile variations yet maintain tight thermal uniformity within each process profile. The primary danger during reflow is the formation of oxides that degrade subsequent processes. "Two different reflow processes - nitrogen with flux or hydrogen flux-free - can be used to control oxide formation," said Kristen Mattson, semiconductor products manager at BTU International (North Billerica, Mass.). "The flux-based process presents the challenge of integrating the flux coating process and dealing with volatilized flux in the reflow process chamber, while the hydrogen process requires tight atmosphere control." With either process, atmosphere purity and thermal uniformity ensure robust reflow. Two additional measures, a uniform flux coating across the entire wafer and maintaining at least 95% hydrogen purity, will aid in preventing oxide formation. Cleanliness from particulate formation and flux contamination to the equipment and the process are also ofparamount importance.InspectionImproper wetting with the UBM and excessive flux residue are two common problems that create air gaps resulting in voids. Since bumps typically measure 100-200 μm in diameter, and a voided area of 5-10% of total bump volume will cause collapse, minute amounts of air can create voids. The formation of voids within bumps is a latent defect that jeopardizes the electrical performance of final packaged die in the form of opens, shorts or entire package failure.Bumpingoperations employ a suite of quality assurance tools such as optical microscopes, laser, UV, scanners, shear testers and automated optical imaging technologies to measure volume parameters such as bump height, diameter, shape, shear strength and adhesion. Y et high-resolution X-ray is necessary to explore solder mass, and thus potential voids under the bump surface (Fig. 3 ). "Our customers are under increasing pressure to reduce voids in wafer bumps and to improve their overall productivity," said Lance Scott, president and CEO of FeinFocus USA (Stamford, Conn.).ConclusionAlthough much of wafer bumping technology is based on front-end semiconductor techniques, early indications show that wafer bumping has become associated with back-end semiconductor operations. Two industry consortia, Semiconductor Equipment Consortium for Advanced Packaging (SECAP) and the Advanced Packaging and Interconnect Alliance (APiA), have been formed from both front- and back-end equipment providers to enable wafer bumping technologies. Regardless of location performed, the transition to 300 mm wafers is an important catalyst for wafer bumping and the growth of wafer-level packages, because the additional economy of scale for 300 mm wafers makes wafer-level packaging a preferred solution to wire bonding.However, yield must exceed that of conventional packaging and be racheted up to approximate front-end numbers. And, since packaging itself contributes mightily to total cost, that remains a predominant issue, especially since processing takes place with patterned wafers. One comfort is that, when the technology qualifies on 300 mm tools, smaller wafer sizes are inherently qualified also. However, as with all new technologies, a critical mass must be reached with installed infrastructure and volume growth to derive true cost benefits. Ultimately, wafer bumping technology is real, and applications abound for those pioneers who are ready to exploit its potential.作者信息Greg Reed is a veteran electronics manufacturing industry trade publication journalist. He has held executive editorial positions with Semiconductor International, Electronic Packaging & Production, SMT, Advanced Packaging, and Connector Specifier magazines. He holds a B.A. in English/journalism from Western Illinois University.。

浅析半导体工艺技术(英文版)

浅析半导体工艺技术(英文版)The semiconductor industry has revolutionized the world over the years, enabling the development of modern technology such as smartphones, computers, and other electronic devices. Behind these advancements lies the intricate field of semiconductor process technology.Semiconductor process technology refers to the various techniques and methods used to fabricate semiconductor devices. It involves a series of steps that ultimately transform a silicon wafer into individual transistors, diodes, and other electronic components.The first step in semiconductor process technology is the deposition of thin films onto the wafer surface. This is achieved using techniques such as chemical vapor deposition (CVD) or physical vapor deposition (PVD). These processes create a thin layer of material, such as silicon dioxide or metal, on the wafer that will later form the gate oxide or interconnects of the integrated circuit.After deposition, various layers need to be patterned to define the structure of the device. This is done through a process called lithography, where a photosensitive material called photoresist is exposed to light or electron beam and then etched to create the desired pattern. The use of masks and photomasks is commonly employed to ensure precise alignment and accurate replication of patterns.Etching is then performed to remove unwanted material and form the desired structure. Different etching techniques such as wetetching, dry etching, and plasma etching are used depending on the material being etched and the desired result.To create the necessary electrical connections between different layers or components, a technique called metallization is employed. This involves depositing metal layers, typically aluminum or copper, onto the wafer surface, which are then patterned and etched to form the desired interconnects.Throughout the entire process, various quality control steps are implemented to ensure the reliability and functionality of the fabricated devices. These include testing for defects, measuring electrical parameters, and assessing the overall performance of the components.The constant advancement in semiconductor process technology has led to the miniaturization of devices, with transistors becoming smaller and more efficient with each generation. This has been made possible by improving techniques such as photolithography, which now allows for the creation of features as small as a few nanometers.In conclusion, semiconductor process technology is a critical aspect of the semiconductor industry, enabling the fabrication of complex integrated circuits that power our modern world. The techniques and methods involved in this field continue to evolve, allowing for the development of smaller, faster, and more energy-efficient semiconductor devices.Semiconductor process technology has played a crucial role in driving technological advancements and shaping various industries. In this section, we will exploresome specific aspects of semiconductor process technology and its impact.One of the significant developments in semiconductor process technology is the transition from larger feature sizes to smaller feature sizes. This is commonly referred to as the shrinking of process technology nodes. The International Technology Roadmap for Semiconductors (ITRS) has been instrumental in setting goals and guiding the industry in achieving these advancements. The constant reduction in feature sizes has led to an increase in the number of transistors that can be packed onto a single chip, resulting in more powerful and capable devices.As the feature sizes decrease, new challenges arise due to physical limitations and the behavior of materials at such small scales. One such challenge is the control of leakage current. As feature sizes shrink, the distance between components on a chip reduces, leading to increased current leakage. Semiconductor manufacturers have employed various techniques, such as high-k dielectrics, to counteract this effect and maintain low leakage levels.Another notable development in semiconductor process technology is the implementation of new materials and structures to enhance performance. For instance, the introduction of strained silicon has allowed for higher electron mobility, resulting in faster and more efficient transistors. Additionally, the use of FinFET (Fin Field-Effect Transistor) structures has enabled better control of electrical current flow, leading to lower power consumption and improved performance.Besides feature size reductions, semiconductor process technology has also focused on enhancing device functionality and integration. This has led to the incorporation of new manufacturing techniques, such as three-dimensional (3D) integration. 3D integration allows for stacking multiple layers of devices, optimizing space utilization and enabling the integration of diverse functionalities on a single chip. It facilitates the development of advanced packaging solutions, such as System-on-Chip (SoC) and System-in-Package (SiP), which offer higher performance and more compact form factors.Semiconductor process technology has also played a crucial role in enabling the development of specialty devices, such as microelectromechanical systems (MEMS) and sensors. MEMS devices incorporate mechanical structures and electronics on a single chip, enabling the fabrication of sensors, actuators, and other microscale mechanical components. Semiconductor process technology has enabled the precise fabrication of these structures, allowing for widespread adoption in applications such as automotive, healthcare, and consumer electronics.The advancements in semiconductor process technology have significantly impacted numerous industries. For example, the smartphone industry has greatly benefited from the miniaturization and improved performance of semiconductor devices. Smaller and more energy-efficient transistors have enabled the development of powerful processors and memory, leading to faster and more capable smartphones. Additionally, advancements in semiconductor process technology have enabled the integration of various sensors, such as accelerometers and gyroscopes,facilitating features like motion sensing and augmented reality.The automotive industry has also witnessed significant advancements due to semiconductor process technology. The increasing integration of semiconductor devices in vehicles has enabled the development of advanced safety features, smart infotainment systems, and electric powertrain solutions. Semiconductor process technology has enabled the manufacture of more robust and reliable chips that can withstand harsh operating conditions in automotive applications.Moreover, the field of healthcare has been revolutionized by semiconductor process technology. The development of wearable devices, medical imaging systems, and diagnostic tools has been made possible by the miniaturization and improved functionality of semiconductor devices. These advancements have facilitated more accurate diagnoses, continuous monitoring of vital signs, and efficient delivery of healthcare services.In conclusion, semiconductor process technology has been instrumental in shaping the modern world through its continuous advancements. The ability to fabricate smaller, more efficient, and higher-performing semiconductor devices has revolutionized various industries. As technology continues to evolve and new challenges emerge, semiconductor process technology will remain crucial in addressing these challenges and driving further innovation.。

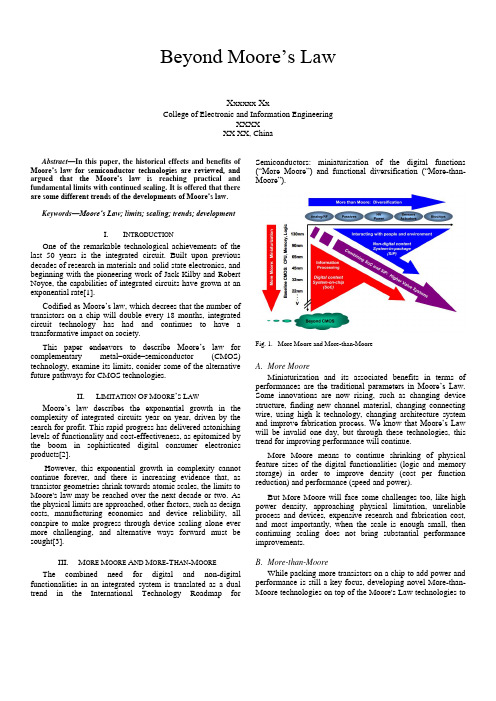

Beyond_Moore's_Law

Beyond Moore’s LawXxxxxx XxCollege of Electronic and Information EngineeringXXXXXX XX, ChinaAbstract—In this paper, the historical effects and benefits of Moore’s law for semiconductor technologies are reviewed, and argue d that the Moore’s law is reaching practical and fundamental limits with continued scaling. It is offered that there are some different trends of the developments of Moore’s law.Keywords—Moore’s Law; limits; scaling; trends; developmentI.I NTRODUCTIONOne of the remarkable technological achievements of the last 50 years is the integrated circuit. Built upon previous decades of research in materials and solid state electronics, and beginning with the pioneering work of Jack Kilby and Robert Noyce, the capabilities of integrated circuits have grown at an exponential rate[1].Codified as Moore’s law, which decrees that the number of transistors on a chip will double every 18 months, integrated circuit technology has had and continues to have a transformative impact on society.This paper endeavors to describe Moore’s law for complementary metal–oxide–semiconductor (CMOS) technology, examine its limits, conider some of the alternative future pathways for CMOS technologies.II.L IMITATION O F M OORE’S L AWMoore’s law describes the exponentia l growth in the complexity of integrated circuits year on year, driven by the search for profit. This rapid progress has delivered astonishing levels of functionality and cost-effectiveness, as epitomized by the boom in sophisticated digital consumer electronics products[2].However, this exponential growth in complexity cannot continue forever, and there is increasing evidence that, as transistor geometries shrink towards atomic scales, the limits to Moore's law may be reached over the next decade or two. As the physical limits are approached, other factors, such as design costs, manufacturing economics and device reliability, all conspire to make progress through device scaling alone ever more challenging, and alternative ways forward must be sought[3].III.M ORE M OORE A ND M ORE-T HAN-M OORE The combined need for digital and non-digital functionalities in an integrated system is translated as a dual trend in the International Technology Roadmap for Semiconductors: miniaturization of the digital functions (“More Moore”) and functional diversification (“More-than-Moore”).Fig. 1.More Moore and More-than-MooreA.More MooreMiniaturization and its associated benefits in terms of performances are the traditional parameters in Moore’s Law. Some innovations are now rising, such as changing device structure, finding new channel material, changing connecting wire, using high k technology, changing architecture system and improve fabrication process. We know that Moore’s Law will be invalid one day, but through these technologies, this trend for improving performance will continue.More Moore means to continue shrinking of physical feature sizes of the digital functionalities (logic and memory storage) in order to improve density (cost per function reduction) and performance (speed and power).But More Moore will face some challenges too, like high power density, approaching physical limitation, unreliable process and devices, expensive research and fabrication cost, and most importantly, when the scale is enough small, then continuing scaling does not bring substantial performance improvements.B.More-than-MooreWhile packing more transistors on a chip to add power and performance is still a key focus, developing novel More-than-Moore technologies on top of the Moore's Law technologies toprovide further values to semiconductor chips has also becomea more important issue.More-than-Moore means that Incorporation into devices offunctionalities that do not necessarily scale according to “M oore’s L aw”, but provide addition al value in different ways.More-than-Moore approach allows for the non-digitalfunctionalities to migrate from the system board-level into thepackage (sip) or onto the chip (soc).The second trend is characterized by functionaldiversification of semiconductor-based devices. These non-digital functionalities do contribute to the miniaturization ofelectronic systems, although they do not necessarily scale at the same rate as the one that describes the development of digital functionality. Consequently, in view of added functionality, this trend may be designated “More-than-Moore” (MtM).But we will face some problems by using the technologies of More-than-Moore. Such as integration of More Moore with More-than-Moore and Creation of intelligent compact systems.More-than-Moore technologies cover a wide range of fields. For example, MEMS applications include sensors, actuators and ink jet printers. RF CMOS applications include Bluetooth, GPS and Wi-Fi. CMOS image sensors are found in most digital cameras. High voltage drivers are used to power LED lights. These applications add value to computing and memory devices that are made from the traditional Moore's Law technology.Fig. 2.2007 ITRS “Moore’s Law and More” Definition Graphic Proposal Fig.2 is a definition of “Moore’s Law and More”. The red part is More Moore and the blue part is More-than-Moore. The red part contains the computing and data storage logic, while the blue part contains RF, HH Power, Passives, Sensors, Actuators, Bio-chips, Fluidics and other functionalities.parisonComparing More Moore and More-than-Moore from Fig.3 and Fig.4, we can draw some conclusions:•More Moore has smallest footprint but limited functionality.•More-than-Moore has full functionality but complex supple chain.They all have advantages and disadvantages. We can use them according to specific application. Fig. 3.Following Moore’s Law is one approach:Monolithic CMOS logic System-on-ChipFig. 4.Adding More-than-Moore is another: System-on-Chip and System-in-PackageIn modern society, the concept of Internet of Things is verypopular. In the past, people may pay attention to computingand storage more, so the IC industry develops rapidly following Moore’s Law. But now, people pay more attention tointernet of things, biomedical and so on. That is to say, peopleneed more demands of the IC besides the computing andstorage functionality.Fig. 5.An ideal application of More-than-MooreFig.5 is an example of More-than-Moore, of course, it is anideal application. But it shows some benefits of this trend.IV.B EYOND C MOSA.What is Beyond CMOSWhat we have talked about before is all based on Si-based CMOS technology. But we should realize that Si-based CMOS technology cannot do everything, especially when the transistors continue shrinking of physical feature sizes towards atomic scale.Fig. 6.More Moore, More-than-Moore and Beyond CMOSWhat More Moore do is to continue to go forward along the road of “Moore’s Law”. And More-than-Moore do is to d evelop and extend “Moore’s Law”. When the scaling bellows about 10nm, traditional Si-based CMOS technology may be invalid. So what Beyond CMOS want to do is to invent new devices or technologies when Si-based CMOS comes across its limitation.Fig. 7.Some new devices and technologyThe main idea of Beyond CMOS is to invent one or several new type switches which can replace the Si-based CMOS to process information. So these ideal devices need to have higher function density, higher performance, less power consumption, acceptable manufacturing cost, stable enough and suitable for large-scale manufacturing and so on.B.Several new devices1)Tunneling FET(TFET)TFET mainly according to the principle of tunneling of quantum mechanics, directly goes through channel from the source to drain rather than by diffusion. Fig. 8.Tunneling FET(TFET)2)Quantum Cellular Automata (QCA)Representing the binary information by changing the structure of the Cellular.Transmitting information based on neighbor interaction.Fig. 9.Quantum Cellular Automata (QCA)Fig. 10.Quantum Cellular Automata (QCA)3)Atomic Switch(QCA)Atomic switch based on the formation and the annihilation of the metal atoms bridge between the two electrons, forming a gate-control switch mode.Fig. 11.Atomic Switch4)SpinFETSpinFET use the spinning direction of electron to carry information.Fig. 12.SpinFETFig. 13.SpinFETThey all have advantages or dis advantages. Maybe they are not the best devices, but they represent the potential development trend of the devices in the future[4].V.S UMMARYMicroelectronics therefore seeks to develop in new ways, not only to continue to deliver better performance in traditional markets, but also to grow into new markets based on devising new, non-electronic, functions on integrated circuits.Microelectronics relies on complementary metal oxide semiconductor (CMOS) technology, the backbone of the electronics industry. Beyond Moore's law, it is foreseen that microelectronics will be a platform to support optical, chemical and biotechnology to deliver a step change beyond electronics-only integration.R EFERENCES[1]Cavin R K, Lugli III P, Zhirnov V V. Science and engineering beyondMoore's law[J]. Proceedings of the IEEE, 2012, 100(Special Centennial Issue): 1720-1749.[2]Cumming D R S, Furber S B, Paul D J. Beyond Moore's law[J].Philosophical transactions. Series A, Mathematical, physical, and engineering sciences, 2014, 372(2012).[3]Saraswat K C. How far can we push Si CMOS and what are thealternatives for future ULSI[C]//Device Research Conference (DRC), 2014 72nd Annual. IEEE, 2014: 3-4.[4]Kazior T E. Beyond CMOS: heterogeneous integration of III–V devices,RF MEMS and other dissimilar materials/devices with Si CMOS to create intelligent microsystems[J]. Philosophical Transactions of the Royal Society of London A: Mathematical, Physical and Engineering Sciences, 2014, 372(2012): 20130105.。

精选半导体业生产计划

Purchasing

Supply Plan

Scheduling

Logistics

Planning

Order Mgmt

Demand Plan

Supply

Distribution

Production

Process Control

Manufacturing Execution System

Production Management: Current Status 生产管理现状

Solution (Resource: ITRS*)

解决方案(源自ITRS*)

Significant improvements in factory planning/scheduling are required. 必须通过先进生产计划和调度系统来提高半导体制造的生产率Improvements in factory forecasting and flexible factory information/control systems that can change with business conditions must be developed and implemented. 必须改进工厂的需求预测,建立柔性的工厂信息和管理软件系统,使得工厂产能可以随着市场环境的改变而改变… scheduling and dispatching… must be developed to improve equipment OEE and extendibility. 必须探索和发展生产调度和分派技术,以改进装备的利用率,提高工厂的可扩展性

Strategy

Plan

Execution

Supply Chain Management

Environmental guideline_Ashrae transaction

ABSTRACTRecent trends toward increased equipment power densityin data centers can result in significant thermal stress, with the undesirable side effects of decreased equipment availability,wasted floor space, and inefficient cooling system operation.In response to these concerns, manufacturers identified the need to provide standardization across the industry, and in 1998 a Thermal Management Consortium was formed. This was followed in 2002 by the creation of a new ASHRAE Tech-nical Group to help bridge the gap between equipment manu-fa cturers a nd fa cility designers a nd opera tors. “Therma l Guidelines for Data Processing Environments” the first publi-cation of TC9.9, is discussed in this paper, along with a histor-ical perspective leading up to the publication and discussion of issues that will define the roadmap for future ASHRAE activ-ities in this field.CURRENT INDUSTRY TRENDS/PROBLEMS/ISSUES Over the years, computer performance has significantly increased but unfortunately with the undesirable side effect of higher power. Figure 1 shows the National/International Tech-nology Roadmap for Semiconductors’ projection for proces-sor chip power. Note that between the years 2000 and 2005 the total power of the chip is expected to increase 60% and the heat flux will more than double during this same period. This is only part of the total power dissipation, which increases geometrically. The new system designs, which include very efficient interconnects and high-performance data-bus design,create a significant increase in memory and other device utili-zation, thus dramatically exceeding power dissipation expec-tations. As a result, significantly more emphasis has beenplaced on the cooling designs and power delivery methods within electronic systems over the past year.In addition, the new trend of low-end and high-end system miniaturization, dense packing within racks, and the increase in power needed for power conversion on system boards have caused an order of magnitude rack power increase. Similarly,this miniaturization and increase in power of electronics scales into the data center environment. I n fact, it wasn’t until recently that the industry has publicly recognized that the increasing density within the data center may have profound impact on the reliability and performance of the equipment it houses in the future. For this reason, there has been a recentflurry of papers addressing the need for new room coolingFigure 1Projection of processor power by the Na tiona l/Intern a tion a l Technology Ro a dm ap for Semiconductors.Evolution of Data Center Environmental GuidelinesRoger R. Schmidt, Ph.D.Christian BeladyAlan Classen Tom DavidsonMember ASHRAEAssociate Member ASHRAEMember ASHRAEMagnus K. Herrlin , Ph.D. Shlomo Novotny Rebecca PerryMember ASHRAERoger Schmidt and Alan Claassen are with IBM Corp., San Jose, Calif. Christian Belady is with Hewlett-Packard, Richardson, Tex. Tom Davidson is with DLB Associates, Ocean N.J. Magnus Herrlin is with ANCIS Incorporated , San Francisco, Calif.Shlomo Novotny and Rebecca Perry are with Sun Microsystems, San Diego, Calif.AN-04-9-1© 2004. American Society of Heating, Refrigerating and Air-Conditioning Engineers, Inc. (). Reprinted by permission from ASHRAE Transactions, Vol. 110, Part 1. This material may not be copied nor distributed in either paper or digital form without ASHRAE’s permission.technologies as well as modeling and testing techniques within the data center. All of these recognize that the status quo will no longer be adequate in the future. So what are the result-ing problems in the data center? Although there are many, the following list discusses some of the more relevant problems:1.Power density is projected to go upFigure 2 shows how rapidly machine power density is expected to increase in the next decade. Based on this figure it can easily be projected that by the year 2010server power densities will be on the order of 20,000 W/m 2. This exceeds what today’s room cooling infrastruc-ture can handle.2.Rapidly changing business demandsRapidly changing business demands are forcingT managers to deploy equipment quickly. Their goal is to roll equipment in and power on equipment immediately.This means that there will be zero time for site prepara-tion, which implies predictable system requirements (i.e.,“plug and play” servers).3.Infrastructure costs are risingThe cost of the data center infrastructure is rising rapidly with current costs in excess of about $1000/ft 2. For this reason, IT and facility managers want to obtain the most from their data center and maximize the utilization of their infrastructure. Unfortunately, there are many barri-ers to achieve this.First, airflow in the data center is often completely ad hoc.In the past, manufacturers of servers have not paid much attention to where the exhaust and inlets are in their equip-ment. This has resulted in situations where one server may exhaust hot air into the inlet of another server (some-times in the same rack). In these cases, the data center needs to be overcooled to compensate for this ineffi-ciency.In addition, a review of the industry shows that the envi-ronmental requirements of most servers from various manufacturers are all different, yet they all coexist in the same environment. As a result, the capacity of the datacenter needs to be designed for the worst-case server with the tightest requirements. Once again, the data center needs to be overcooled to maintain a problematic server within its operating range.Finally, data center managers want to install as many serv-ers as possible into their facility to get as much production as possible per square foot. In order to do this they need to optimize their layout in a way that provides the maxi-mum density for their infrastructure.The above cases illustrate situations that require over-capacity to compensate for inefficiencies.4.There is no NEBS equivalent specification for data centers.(NEBS [Network Equipment–Building Systems] is the telecommunication industry’s most adhered to set of phys-ical, environmental, and electrical standards and require-ments for a central office of a local exchange carrier.)IT/facility managers have no common specification that drives them to speak the same language and design to a common interface document.The purpose of this paper is to review what started as a “grassroots” industrywide effort that tried to address the above problems and later evolved into an ASHRAE Technical Committee. This committee then developed “Thermal Guide-lines for Data Processing Environments” (ASHRAE 2003a),which will be reviewed in this paper.HISTORY OF INDUSTRY SPECIFICATIONS Manufacturers Environmental Specifications In the late 1970s and early 1980s, data center site planning consisted mainly of determining if power was clean (not connected to the elevator or coffee pot), had an isolated ground, and if it would be uninterrupted should the facility experience a main power failure. The technology of the power to the equipment was considered the problem to be solved, not the power density. Other issues concerned the types of plugs,which varied widely for some of the larger computers.In some cases, cooling was considered a problem and, in some isolated cases, it was addressed in a totally different manner, so that the technology and architecture of the machine were dictated by the cooling methodology. Cray Research, for example, utilized a liquid-cooling methodology that forced a completely different paradigm for installation and rge cooling towers, which were located next to the main system, became the hallmark of computing prowess.However, typically the preferred cooling methods were simply bigger, noisier fans. The problem here was the noise and the hot-air recirculation when a system was placed too close to a wall.Over the last ten years, the type of site planning informa-tion provided has varied depending on the company's main product line. For companies with smaller personal computers or workstations, environmental specifications were much like those of an appliance: not much more than what is on the back of a blender. For large systems, worksheets for performingFigure 2Equipment power projection (Uptime Institute).calculations have been provided, as the different configura-tions had a tremendous variation in power and cooling require-ments.I n certain countries, power costs were a hugecontributor to total cost of ownership. Therefore, granularity, the ability to provide only the amount of power required for a given configuration, became key for large systems.In the late 1990s, power density became more of an issue and simple calculations could no longer ensure adequate cool-ing. Although cooling is a factor of power, this does not provide the important details of the air flow pattern and how the heat would be removed from the equipment. However, this information was vitally needed in equipment site planning guides. This led to the need for additional information, such as flow resistance, pressure drop, and velocity, to be available not only in the design stages of the equipment but after the release of the equipment for integration and support. This evolved into the addition of more complex calculations of the power spec-ifications, plus the airflow rates and locations, and improved system layouts for increased cooling capacity.In the early 2000s, power densities continued to increase as projected. Layout, based on basic assumptions, could not possibly create the efficiencies in the airflow that were required to combat the chips that were scheduled to be intro-duced in the 2004 time frame. Because of this, thermal model-ing, which was typically used to design products, began to be viewed as a possible answer for optimizing cooling in a data center environment. However, without well-designed thermal models from the equipment manufacturers and easy-to-use thermal modeling tools for facility managers, the creation or troubleshooting of a data center environment fell again to traditional tools for basic calculations to build a data center or to gather temperatures after a data center was in use.At this point it became apparent that the solution for rising heat densities could not be solved after the delivery of a prod-uct. Nor could it be designed out of a product during develop-ment. Instead, it had to be part of the architecture of the entire industry’s next-generation product offerings.Formation of Thermal Management Consortium In 1998 a number of equipment manufacturers decided to form a consortium to address common issues related to ther-mal management of data centers and telecommunications rooms. I nitial interest was expressed from the following companies: Amdahl, Cisco Systems, Compaq, Cray, Inc., Dell Computer, EMC, HP, BM, ntel, Lucent Technologies, Motorola, Nokia, Nortel Networks, Sun Microsystems, and Unisys. They formed the Thermal Management Consortium for Data Centers and Telecommunications Rooms. Since the industry was facing increasing power trends, it was decided that the first priority was to develop and then publish a trend chart on power density of the industry’s equipment that would aid customers in planning data centers for the future. Figure 2 shows the chart that resulted from this effort. This chart has been widely referenced and was published in collaboration with the Uptime Institute in 2000. Following this publication the consortium formed three subgroups to address what customers felt was needed to align the industry:A.Rack airflow direction/rack chilled airflow require-mentsB.Reporting of accurate equipment heat loadsmon environmental specificationsThe three subgroups worked on the development of guidelines to address these issues until an ASHRAE commit-tee was formed in 2002 that continued this effort. The result of these efforts is “Thermal Guidelines for Data Processing Envi-ronments” (ASHRAE 2003a), which is being published by ASHRAE. The objectives of the ASHRAE committee are to develop consensus documents that will provide environmental trends for the industry and guidance in planning for future data centers as they relate to environmental issues.Formation of ASHRAE GroupThe responsible committee for data center cooling within ASHRAE has historically been TC9.2, Industrial Air Condi-tioning. The 2003 ASHRAE Handbook—HVAC Applications, Chapter 17, “Data Processing and Electronic Office Areas”(ASHRAE 2003b) has been the primary venue within ASHRAE for providing this information to the HV AC indus-try. There is also Standard 127-2001, Method of Testing for Ra ting Computer a nd Da ta Processing Room Unita ry Air-Conditioners (ASHRAE 2001), which has application to data center environments.Since TC9.2 encompasses a very broad range of industrial air-conditioning environments, ASHRAE was approached in January 2002 with the concept of creating an independent committee to specifically address high-density electronic heat loads. The proposal was accepted by ASHRAE, and TG9.HDEC, High Density Electronic Equipment Facility Cooling, was created. TG9.HDEC's organizational meeting was held at the ASHRAE Annual Meeting in June 2002 (Hawaii). TG9.HDEC has since further evolved and is now TC9.9, Mission Critical Facilities, Technology Spaces, and Electronic Equipment.The first priority of TC9.9 was to create a thermal guide-lines document that would help to align the designs of equip-ment manufacturers and aid data center facility designers to create efficient and fault tolerant operation within the data center. The resulting document, “Thermal Guidelines for Data Processing Environments,” was completed in a draft version on June 2, 2003. I t was subsequently reviewed by several dozen companies representing computer manufacturers, facil-ities design consultants, and facility managers. Approval to submit the document to ASHRAE's Special Publications Section was made by TC9.9 on June 30, 2003, and the docu-ment publication is expected in December 2003.TC9.9 ENVIRONMENTAL GUIDELINESEnvironmental SpecificationsFor data centers, the primary thermal management focus is on the assurance that the housed equipment’s temperature and humidity requirements are being met. As an example, one large computer manufacturer has a 42U rack with front-to-rear air cooling and requires that the inlet air temperature into the front of the rack be maintained between 10°C and 32°C for elevations up to 1287 m (4250 feet). Higher elevations require a derating of the maximum dry-bulb temperature of 1°C for every 218 m (720 feet) above 1287 m (4250 feet) up to 3028 m (10000 feet). These temperature requirements are to be maintained over the entire front of the 2 m height of the rackwhere air is drawn into the system. These requirements can be a challenge for customers of such equipment, especially when there may be many of these racks arranged in close proximity to each other and each dissipating powers up to 12.5 kW when fully configured.As noted in the example above, data processing manufac-turers typically publish environmental specifications for the equipment they manufacture. The problem with these speci-fications is that other manufacturers with the same type of equipment and selling into the same customer environment may have a different set of environmental specifications. Not only do discrepancies occur between manufacturers; in some cases, there are discrepancies within the portfolio of a manu-facturer’s products. As one can imagine, customers of such equipment can be left in quandary as to what environment to provide in their data processing room.In an effort to standardize the environmental specifica-tions, the ASHRAE TC9.9 committee first surveyed the envi-ronmental specifications of a number of data processing equipment manufacturers. From this survey, four classes were developed that would encompass most of the specifications. Also included within the guidelines was a comparison to the NEBS specifications for the telecommunications industry to show both the differences and also aid in possible convergence of the specifications in the future.The four data processing classes cover the entire environ-mental range from air-conditioned server and storage environ-ments of classes 1 and 2 to the lesser controlled environments such as class 3 for workstations, PCs, and portables or class 4 for point-of-sales equipment with virtually no environmental control. For each class the allowable dry-bulb temperature, relative humidity, maximum dew point, maximum elevation, and maximum rate of change are specified for product oper-ating conditions. For higher altitudes, a derating algorithm is provided that accounts for diminished cooling. In addition to the allowable ranges, the recommended range for dry-bulb and relative humidity is provided for classes 1 and 2 based on the reliability aspects of the electronic hardware. Non-operating specifications of dry-bulb, relative humidity, and maximum dew point are also included.Finally, psychometric charts for all environmental classes including NEBS are provided in an Appendix of the guide. These are provided in both SI and IP units to aid the user of these charts. Both recommended (where appropriate) and allowable envelopes are provided for all classes.LayoutIn order for seamless integration between the server and the data center to occur, certain protocols need to be devel-oped, especially in the area of airflow. This section provides airflow guidelines for both the IT/facility managers and the equipment manufacturers to design systems that are compat-ible and minimize inefficiencies. To ensure this, the section covers the following items:1.Airflow within the cabinet2.Airflow in the facility3.Minimum aisle pitchIn order for data center managers to be able to design their equipment layouts, it is imperative that airflow in the cabinet be known. Currently, manufacturers design their equipment exhaust and inlets wherever it is convenient from an architec-tural standpoint. As a result, there have been many cases where the inlet of one server is directly next to the exhaust of adjacent equipment, resulting in the ingestion of hot air. This has direct consequences for the reliability of that machine. This guide attempts to steer manufacturers toward a common airflow scheme to prevent this hot air ingestion by specifying regions for inlets and exhausts. The guide recommends one of the three airflow configurations: front-to-rear, front-to-top, and front-to-top-and-rear as shown in Figure 3.Once manufacturers start implementing the equipment protocol, it will become easier for facility managers to opti-mize their layouts to provide maximum possible density by following the hot-aisle/cold-aisle concept. In other words, the front face of all equipment is always facing the cold aisle. Figure 4 shows how the inlets would line up.Finally, the guide addresses minimum practical aisle pitch for a computer room layout. Figure 5 shows a minimum 7 tile pitch where the tile could either be 24 inches or 600 mm.Table 1 shows how the space is allocated across the seventiles for either U.S. (24 in.) or Global (600 mm) tiles. Figure 3Recommended equipment airflow protocol.By following these guidelines, equipment manufacturers enable their customers to use the hot-aisle/cold-aisle protocol,which allows them to maximize the utilization of their data centers. In addition, as manufactures adopt the flow directions specified in the guidelines, the swapping out of obsolete serv-ers becomes much less problematic due to the uniform cooling direction.t is important to note that even if the guideline is followed, it does not guarantee adequate cooling. Although it will provide the best opportunity for success, it is still up to the facility manager to do the appropriate analysis to ensure cool-ing goals are met.Power Methodology and ReportingThe ASHRAE guide’s heat and airflow reporting section defines what information is to be reported by the information technology equipment manufacturer to assist the data center planner in the thermal management of the data center. The equipment heat release value is the key parameter that will be discussed in this section. Several other pieces of information are required if the heat release values are to be meaningful.These are included in the guide’s reporting section and are discussed briefly here.Currently, heat release values are not uniformly reported by equipment manufacturers and, as a result, site planners sometimes estimate equipment heat loads by using electricalinformation. Electrical information is always available because IEC 60950 (IEC 1999) and its USA and Canadian equivalent (CSA I nternational 2000) require the maximum power draw to be reported for safety purposes. The safety stan-dard requires rated voltage and current values to be placed on the equipment name-plate label. Electrical power and heat release are equivalent quantities for a unity power factor and are expressed in the same units (watts or Btu/h), but the name-plate electrical information is not appropriate for heat release estimation for data center thermal management purposes.The design guide states, “Name-plate ratings should at no time be used as a measure of equipment heat release.” The first reason is that the name-plate rating is only indicative of a worst-case maximum power draw. This maximum rating will often not be representative of the actual power draw for the equipment configuration to be installed. Second, there is no standard method for defining the maximum power draw.Equipment manufacturers are sometimes motivated to state high rating values so that safety certification current measure-ments at a rated voltage are well below the rated current. (The safety standard allows the measured current to exceed the rated value by 10%, but this is a situation that manufacturers naturally want to avoid.). The manufacturer may overstate or buffer the rating value to allow the use of higher power compo-nents in the future. If the data center planner starts with an inflated nameplate rating and then applies a factor to account for future power increases, the future increase has been counted twice. Third, multiplying a corresponding rated volt-age and current value results in a V A or kV A value that must be multiplied by a power factor, which may not be known, to get power in watts or Btu/h. While the power factor is a small adjustment for some modern equipment, not applying theTable 1. Aisle Pitch AllocationTile SizeAisle Pitch(cold aisle to cold aisle)1Nominal Cold Aisle Size2Max. Space Allocated forEquipment with No Overhang 3Hot Aisle Size U.S. 2 ft (610 mm)14 ft (4267 mm) 4 ft (1220 mm)42 in. (1067 mm) 3 ft (914 mm)Global600 mm (23.6 in.)4200 mm (13.78 ft)1200 mm (3.94 ft)1043 mm (41 in.)914 mm (3 ft)1If considering a pitch other than seven floor tiles, it is advised to increase or decrease the pitch in whole tile increments. Any overhang into the cold aisle should take into account the specific design of the front of the rack and how it affects access to the tile and flow through the tile.2Nominal dimension assumes no overhang, less if front door overhang exists.3Typically a one-meter rack is 1070 mm deep with the door and would overhang the front tile 3 mm for a U.S. configuration and 27 mm for global configuration.Figure 4Top view of a hot-aisle/cold-aisle configuration.Figure 5Minimum hot-aisle/cold-aisle configuration.power factor for other equipment may result in another cause of conservative heat load estimates.To avoid the above problems, the ASHRAE guide defines how heat release information should be determined and reported for data center thermal management purposes. The conditions used to determine the heat release values are spec-ified. They apply to all aspects of the process—measurement conditions, model conditions, and reporting conditions. The conditions are:•Steady stateValues based on peak currents are useful for power system design but not for data center thermal manage-ment.•All components in the active state, under significant stressThe intent is to avoid both unrealistically low values, such as an idle condition, and unrealistically high values.Significant stress in most power or safety test labs is more representative of normal customer operation, while the workload applied in a performance lab may represent a higher than normal workload. Words such as “worst-case” activity were specifically avoided. If heat release values were based on the unlikely condition of all compo-nents being in a worst-case activity state, the reported values would be excessively high and the resulting situa-tion would be similar to using name-plate rating values.•Nominal voltage input•Nominal ambient temperature from 20°C to 25°C (68°F to 77°F)This temperature range is the recommended operating temperature range for Class 1 and Class 2 in Table 2.1 of the ASHRAE document. At higher temperatures, air-moving devices may speed up and draw more power.Information technology equipment generally has multiple configurations. Heat release values are to be reported for configurations that span the range from mini-mum to maximum heat release values. It is acceptable thata heat release value be measured for every reportedconfiguration. It is also acceptable that a predictive model be developed and validated to provide heat release values for multiple configurations. The model would allow the manufacturer to report heat release values for more configurations than could be practically measured.During equipment development, there may be a period when no heat release measurements are available. During this time the model would be based solely on predictions.The ASHRAE document states, “measured values must be factored into the model by the time the product is announced.” Appropriate values are measured by the equipment manufacturers as part of the safety certifica-tion process, which requires the manufacturer to make electrical measurements. Heat release model validation involves comparing values predicted by the model with measured heat release values for the same configurations.The number of tested configurations is not specified, but the required accuracy is defined: the predicted values must be within 10% of the measured values or the model must be adjusted.Besides heat release values, equipment manufacturers must report additional information for each configuration: •Description of configuration•Dimensions of configurationDividing the heat release value by the equipment foot-print allows the data center planner to calculate the heat load density in W/m2 or W/ft2.•Weight for configurationThis is not directly used for thermal management.However, the weight might result in the equipment being spaced apart to meet floor loading requirements. This would result in a decreased heat density, which is impor-tant to know for data center thermal management.•Minimum/maximum airflow characteristics of each con-figuration in cubic feet per minute (cfm) and cubic meters per hour (m3/h)Unlike the heat release values, which are based on a nominal ambient temperature range, some systems may exhibit variable flow rates due to fan control, which can be dependent upon ambient temperature. For each load-ing condition, flow rate is to be reported along with the ambient temperature relative to that flow rate. The ambi-ent temperature range should be reflective of the temper-ature that produces the minimum flow rate as well as the ambient temperature that produces the maximum flow rate. Presumably these temperatures would reflect the allowable ambient extents for which the hardware is designed. The airflow is also reported with all air-moving devices operating normally. For example, if a fan is only powered when another unit fails, the auxiliary unit should be off when determining the airflow value to be reported.•Airflow diagramThis can be a simple outline of the equipment showing where the airflow enters and leaves the unit. In the future it may be necessary to provide more information. For example, each inlet and exit airflow arrow may need to be associated with a volumetric airflow value, and the exit airflow arrows may also require a number indicating how much heat the airflow picked up while in the equipment.The goal would be to represent the equipment as a compact model in a data center thermal model.An example report is included in the guide. It conveys many important aspects of the information to be reported, but it may not be complete for a given product. The example report provides information for minimum, full, and typical configu-rations. The words “maximum” and “average” configuration were specifically avoided; average particularly may be defined several different ways. I t is hoped that the typical configuration used for thermal management purposes will be the same typical configuration used for acoustic measure-。

Chemical-Reviews-ALD-Overview-Jan-2010