信号完整性测试2

软件开发 信号完整性测试方法模版

文档作者:编写日期:审核:审核日期:文档修订控制目录1. 引言 (3)1.1编写目的 (3)1.2定义 (3)1.3参考资料 (4)2. 测试所需工具说明 (4)2.1需要的软件工具 (4)2.2需要的硬件工具 (5)3. 电源完整性测试 (5)3.1电压转换电路测试 (5)3.1.1 输出电压测试 (5)3.1.2 输出电压过冲测试 (5)3.1.3 输出电压下冲测试 (6)3.1.4 输出电流测试 (6)3.1.5 纹波和噪声测试 (6)3.2单板功耗测试 (7)3.3电源时序测试 (7)3.3.1 电源上电时序测试 (7)3.3.2 电源下电时序测试 (8)4. 板内信号质量测试 (8)4.1时钟信号测试 (8)4.2上电复位时序测试 (8)4.3高速差分信号测试 (9)4.3.1 XAUI信号测试 (9)4.3.2 SGMII信号测试 (9)4.3.3 RGMII信号测试 (9)4.3.4 XGMII信号测试 (10)4.3.5 Interlaken信号质量测试 (10)4.4内存信号测试 (11)4.4.1 DDR 内存信号测试 (11)4.4.2 DDR2 内存信号测试 (11)4.4.3 DDR3 内存信号测试 (11)4.5PCI E信号测试 (12)4.6I2C总线测试 (12)4.7L OCAL B US总线测试 (13)4.8MDIO信号测试 (13)4.9SPI4.2总线测试 (13)4.10SD卡接口信号测试 (14)5. 对外接口信号测试 (14)5.1网口信号测试 (14)5.1.1 100Base-T模板测试 (14)5.1.2 1000Base-T模板测试 (15)5.1.3 GE光眼图测试 (15)5.2串口信号测试 (15)5.3USB口信号测试 (16)6. 附件 (16)1.引言1.1编写目的对信号质量测试的测试项目、测试方法及判决标准进行描述,为各个单板信号质量测试做参考。

【信号完整性测试】—频域测试(频谱、频域阻抗、传输线损耗)、误码测试 及 设备仪器

【信号完整性测试】—频域测试(频谱、频域阻抗、传输线损耗)、误码测试及设备仪器概述信号完整性设计,在电路板设计过程中备受重视。

熟悉各类测试方法的特性,按照测试对象的特征和需求,选用合适些测试方法,对于选择方案,验证效果能够大大提高效率。

上篇,我们介绍了时域测试,其中涵盖波形测试、眼图测试、抖动测试、TDR测试、时序测试。

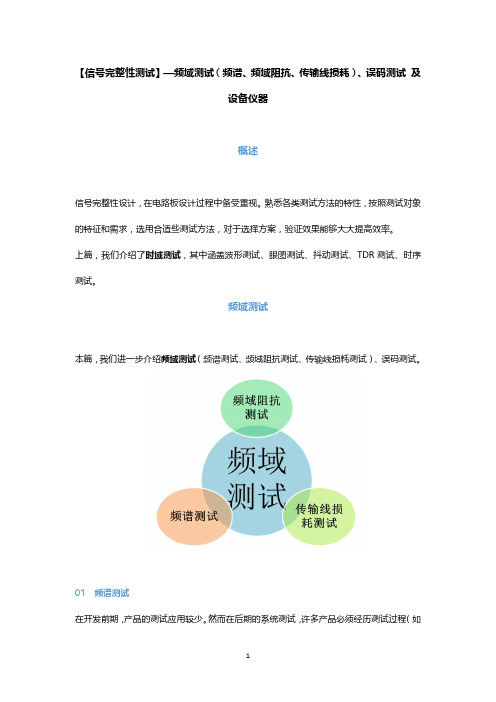

频域测试本篇,我们进一步介绍频域测试(频谱测试、频域阻抗测试、传输线损耗测试)、误码测试。

01频谱测试在开发前期,产品的测试应用较少。

然而在后期的系统测试,许多产品必须经历测试过程(如EMC的试验)。

通过测试发现一些超标的频点,再使用近场扫描仪(核心仪器频谱仪)。

egEMC Scanner分析电路板上具体的区域频谱超标,从而排查超标的原因。

这类设备通常较昂贵,一遍机构都不具备条件。

因此常规情况下都是在设计前期考虑做好匹配和屏蔽,规避后期测试的结果不达标。

02频域阻抗测试目前有许多标准接口如E1(欧洲)/T1(北美)等,目的在于避免太多的能力反射;需要进行较好的匹配,同时在微波或者射频,互相对接,阻抗都有所要求。

通常情况下,需要进行频域的阻抗测试,阻抗测试常用网络分析仪(Network Analyzer),单端输入端口简单,差分输入端口,较为复杂,需要巴伦进行差分和单端转换。

03传输线损耗测试⏹主要针对长的电路板走线、线缆等,传输距离较远,⏹进行高速信号传输、频域的串扰等,均可以通过网络分析仪来测试。

因此,对于PCB的差分信号或者双绞线,可以使用巴伦进行差分转换单端,或者使用4端口网络分析仪来测试。

误码测试误码测试通常是系统测试,使用误码仪、部分软件都可以完成测试。

或通过两台PC,使用软件,测试连接两台PC间的网络误码情况。

误码测试能够对数据的每一位进行测试,相比其它仪器(如示波器)只是部分时间开展采样,剩下大部分时间都在等待。

容易遗漏细节。

尤其是低误码率的设备,误码测试需要耗费大量时间,有时耗时一整天,或者几天。

信号完整性研发测试攻略2.0

信号完整性测试指导书——Ver 2.0编写:黄如俭(sam Huang)钱媛(Tracy Qian)宋明全(Ivan Song)康钦山(Scott Kang)目录1. CLK Test (3)1.1 Differential Signal Test (3)1.2 Single Signal Test (5)2. LPC Test (7)2.1 EC Side Test (7)2.2 Control Sidse Test (8)3. USB Test (11)3.1 High Speed Test (11)3.2 Low Speed Test (12)3.3 Full Speed Test (12)3.4 Drop/Droop Test (12)4. VGA Test (14)4.1 R、G、B Signal Test (14)4.2 RGB Channel to Channel Skew Test (14)4.3 VSYNC and HSYNC Test (15)4.4 DDC_DATA and DDC_CKL Test (15)5. LVDS Test (17)5.1 Differential data signals swing Test (17)5.2 Checking Skew at receiver Test (18)5.3 Checking the offset voltage Test (19)5.4 Differential Input Voltage Test (20)5.5 Common Mode Voltage Test (20)5.6 Slew Rate Test (21)5.7 Data to Clock Timing Test (23)6. FSB Test (26)7. Serial Data(SATA/ESATA, PCIE, DMI,FDI)Test (29)8. HD Audio Test (30)8.1 Measurement at The Controller (30)8.2Measurement at The Codec (31)9. DDR2 Test (34)9.1 Clock (34)9.2 Write (35)9.3 Read (37)10.Ethernet Test (39)11.SMbus Signal Test (40)12. HDMI Test (42)13. DisplayPort Test (43)1. CLK Test1.1 Differential Signal Test测试设备:示波器,两个差分探头,鼠标,键盘测试软件:3D MARK,负载测试步骤:(1)开启示波器预热30分钟,运行测试软件。

信号完整性分析与测试

信号完整性分析与测试信号完整性问题涉及的知识面比较广,我通过这个短期的学习,对信号完整性有了一个初步的认识,本文只是简单介绍和总结了几种常见现象,并对一些常用的测试手段做了相应总结。

本文还有很多不足,欢迎各位帮助补充,谢谢!梁全贵2011年9月16日目录第1章什么是信号完整性 ----------------------------------------------------------------------------------- 3第2章轨道塌陷------------------------------------------------------------------------------------------------ 5第3章信号上升时间与带宽 -------------------------------------------------------------------------------- 6第4章地弹 ------------------------------------------------------------------------------------------------------ 8第5章阻抗与特性阻抗 -------------------------------------------------------------------------------------- 95.1 阻抗 ---------------------------------------------------------------------------------------------------- 95.2 特性阻抗 ---------------------------------------------------------------------------------------------- 9第6章反射 ----------------------------------------------------------------------------------------------------- 116.1 反射的定义------------------------------------------------------------------------------------------- 116.2 反射的测试方法 ------------------------------------------------------------------------------------ 126.3 TDR曲线映射着传输线的各点----------------------------------------------------------------- 126.4 TDR探头选择--------------------------------------------------------------------------------------- 13第7章振铃 ----------------------------------------------------------------------------------------------------- 14第8章串扰 ----------------------------------------------------------------------------------------------------- 168.1 串扰的定义------------------------------------------------------------------------------------------- 168.2 观测串扰---------------------------------------------------------------------------------------------- 16第9章信号质量----------------------------------------------------------------------------------------------- 189.1 常见的信号质量问题 ------------------------------------------------------------------------------ 18第10章信号完整性测试 ------------------------------------------------------------------------------------- 2110.1 波形测试 -------------------------------------------------------------------------------------------- 2110.2 眼图测试 -------------------------------------------------------------------------------------------- 2110.3 抖动测试 -------------------------------------------------------------------------------------------- 2310.3.1 抖动的定义 --------------------------------------------------------------------------------- 2310.3.2 抖动的成因 --------------------------------------------------------------------------------- 2310.3.3 抖动测试 ------------------------------------------------------------------------------------ 2310.3.4 典型的抖动测试工具:------------------------------------------------------------------ 2410.4 TDR测试 ------------------------------------------------------------------------------------------- 2410.5 频谱测试 -------------------------------------------------------------------------------------------- 2510.6 频域阻抗测试-------------------------------------------------------------------------------------- 2510.7 误码测试 -------------------------------------------------------------------------------------------- 2510.8 示波器选择与使用要求: ---------------------------------------------------------------------- 2610.9 探头选择与使用要求 ---------------------------------------------------------------------------- 2610.10 测试点的选择 ------------------------------------------------------------------------------------ 2710.11 数据、地址信号质量测试--------------------------------------------------------------------- 2710.11.1 简述 ----------------------------------------------------------------------------------------- 2710.11.2 测试方法 ----------------------------------------------------------------------------------- 27第1章什么是信号完整性如果你发现,以前低速时代积累的设计经验现在似乎都不灵了,同样的设计,以前没问题,可是现在却无法工作,那么恭喜你,你碰到了硬件设计中最核心的问题:信号完整性。

眼图测试(信号完整性测试)-HDMI2.1

眼图测试(信号完整性测试)-HDMI2.1眼图测试(信号完整性测试)-HDMI2.1HDMI是指⾼清多媒体接⼝,英⽂全称HighDefinitionMultimediaInterface,HDMI接⼝⼴泛应⽤于机顶盒、个⼈计算机、电视、游戏主机、综合扩⼤机、数字⾳响与电视机等设备。

HDMI是⼀种全数字化视频和声⾳发送接⼝,可以发送未压缩的⾳频及视频信号。

⽬前HDMI2.1CTS规范已经全⾯发布,随着HDMI2.1技术更新,HDMI2.1与HDMI1.4/2.0技术规范⼤不同,最新的HDMI2.1规范增加了8K分辨率和eARC的⽀持,给产品开发和测试带来了诸多挑战。

HDMI2.1信号完整性性测试整体⽅案完全向下兼容HDMI?2.0/1.4b,总有关HDMI2.1信号量测相关内容,值得测试⼯程师阅读,篇幅较长,内容概况如下:1、HDMI2.1?有那些新功能2、HDMI2.1Source信号完整性测试⽅案3、HDMI2.1Sink信号完整性测试⽅案⼀HDMI2.1有哪些新功能图1.1?HDMI框图图1.2?HDMITMDS差分对图1.3?HDMI链路测试点?图1.4?HDMI?新功能?图1.5?HDMI?FRL(Fix edRateLink)Mode图1.6HDMI?FRLLinkTraining状态机图1.7?HDMI?FRLLinkTraining流程图1.8?HDMISCDC架构⼆HDMI2.1?Source信号完整性测试⽅案1、HDMI 2.1Source测试挑战:(1)推荐⽰波器和探棒带宽的20GHz或以上(2)新的HDMI2.1治具(3)HDMI 2.0fixture不适⽤于HDMI2.1测试(4)复杂的测试⽅法,考虑插⼊损耗和串扰(5)Source测试需要⽀持新的cable模型和均衡技术(6)Cable模型?Worstcablemodel3?和?ShortCableModel3(7)?DFEandCTLE(8)?EDID/SCDC控制器需要升级(9)涉及多次采集(10)9个测试项⽬,需要超过34次和采集和90+波形图2.1?FRLSource测试项⽬图2.2?HDMI2.1Source测试配置图2.3?FRLSo urce测试⾃动化采集图2.4?FRLSource测试⾃动化采集的难点图2.5?HDMI?2.1?FRL?TX测试装置图2.6FRLSource测试端接电压图2.7?FRLSource测试?单端/差分信号采集图2.8?FRLSource测试?EDID设置图2.9?FRLSource测试?信号速率设定图2.10?FRLSource测试?码型设定图2.11?FR LSource测试TP2_EQEye图2.12?FRLSource测试⼀致性软件图2.13?FRLSource⼿动测试⽅案HDMI2.1Source测试⼩结:(1)HDMI2.1⽅案MOI已获HDMI协会组织的⼀致性规范批准;(2)HDMI认证中⼼(ATC)已正式采⽤泰克HDMI2.1⽅案;(3)⽀持4通道符合CTS规范的>20GHz全带宽同时采集,⾼效省时;(4)?真正的全⾃动化,过程中⽆需任何⼈⼯⼲预,⼀次连接且测试中⽆须改变任何连接,DUT的测试码型和速率切换实现全⾃动控制。

泰克-信号完整性设计以及测试分析2

For cable testing use receptacle fixture (TF-4P22) to mate with SATAe receptacle

– Only port A is accessible (22 pin)

PCIe Cable

SATA devices will coexist with next generation PCIe devices SATA cost/performance benefits

Existing SATA Cable

Requires a connector that supports both PCIe and SATA

SAS Dual Port Receptacle Test Fixture

/

Tektronix Solutions for SATA Express Measurements

DPOJET-based SATA Express setup (requires option PCE3) Support for Base/CEM spec measurements Supports all versions of PCI Express and includes SATA Express PLL configurations

12G+ Design Problem:

1000mV, FFE, Crosstalk, DFE, 50mV

Crosstalk and signal loss problems are the largest design challenge today. Significant advances in high tap count Decision Feedback Equalization are key to operating at 12G+.

信号完整性测试PPT课件

5

2020/5/30

测试能帮我们做些什么?

▪ 验证

–验证我们的硬件设计是否符合设计要求 –验证我们的信号质量是否达到设计要求:波形,时序,电源 –验证仿真结果和实测结果的一致性:波形,时序,电源 –验证模型的准确性

▪ 调试

–调试的目的:发现问题,解决问题 –问题是否是硬件设计的问题? –问题是否是器件的原因:驱动能力?模型? –问题是否是布局布线的问题:拓扑?端接?阻抗?走线长度?串扰?

18

2020/5/30

均衡和预加重的测试

软件实现均衡:

张开眼图进行显示 (示波 器作为接收端)

让设计人员看到接收端内 部的信号波形情况

我们可以使用80SJNB软件 分析均衡后的信号

针对已知PRBS码型自动获 得 Taps 值

19

2020/5/30

抖动、眼图和浴盆曲线

20

2020/5/30

抖动、噪声和误码原因分析

17

2020/5/30

当前高速芯片接收端都使用了均衡

在发送端是一个 “OPEN”的眼睛

在接收端是一个“CLOSE” 的眼睛

Tx + +

path

--

++

--

path

++

path

--

怎么去测试这个眼图?

++

Rcv

EQUALIZER

--

▪ 我不想在这点去测试信号,因 为我想知道通道对信号的影响

▪ 但是如果我在这点进行测试… …我发现眼图是闭合的

41

2020/5/30

探头的选择——等效负载举例

42

电子电路的信号完整性评估考核试卷

8.反射、串扰

9.反射、衰减

10.幅度、相位

四、判断题

1. ×

2. √

3. ×

4. ×

5. ×

6. ×

7. ×

8. ×

9. ×

10. ×

五、主观题(参考)

1.信号完整性问题的产生原因包括传输线效应、阻抗不匹配、信号反射、串扰等。常见的信号完整性问题有信号反射、串扰、抖动、信号衰减等。

2.传输线的特性阻抗影响信号的传播,不匹配会导致信号反射,影响信号完整性。关注特性阻抗有助于优化电路设计,减少信号反射和损耗。

A.信号的频率

B.电源的频率

C.信号的幅度

D.电源的电压

16.在电子电路中,以下哪个元件可以用于改善电源完整性?()

A.电容

B.电感

C.电阻

D.二极管

17.以下哪个因素会影响电源完整性分析中的去耦效果?()

A.去耦电容的容值

B.去耦电容的频率响应

C.电源的电压

D.电源的电流

18.在信号完整性评估中,以下哪个参数与传输线的特性阻抗有关?()

3.差分信号传输是指两根信号线传输相反的信号,其优势在于能提高信号的抗干扰性,减少共模噪声和串扰,提高信号完整性。

4.降低地平面噪声的方法:合理规划地平面布局,增加地平面层数,采用地平面分割,优化地线网格设计,减小地平面与信号线的距离。

A.传输线效应

B.反射

C.折射

D.耦合

5.以下哪种信号完整性问题是由信号反射引起的?()

A.串扰

B.耦合

C.抖动

D.反射

6.下列哪个参数与传输线特性阻抗无关?()

A.电阻

B.电容

C.电感

信号完整性测试资料

缺点 受到模型准确度的限制,特别是链路 模型的精度 不能真实反应信号真实运行环境

16

2018/12/16

链路建模的两种方法:仿真和测试

目前常用的高速测试仪器

– 信号波形质量:实时示波器DPO70K/ 采样示波器DSA8200 – 信号时序关系:逻辑分析仪 TLA5K/TLA7K – 频域测试:采样示波器DSA8200/实 时频谱仪

一致性验证工具

– 采集数据 – 按照标准分析;得出与标 准的符合情况 – 构建基于示波器的专用测 试系统

数据采集器

– 采集数据后分析处理 – 宽带射频接收机

46

2018/12/16

示波器的关键指标

带宽和上升时间

–探头带宽选择

想看看不到

时序不满足带来的问题

–建立时间和保持时间违规会带来数据读取上的问题比如误码等 –毛刺

11

2018/12/16

建立/保持时间

数据 时钟

D CK

Q

输出

数据

输出

时钟

12

2018/12/16

违反建立时间

数据 时钟 D CK Q 输出

数据 输出

?

时钟

建立

保持

13

2018/12/16

PI问题:引起的原因

1k

100 10 1

Active 1.0 pF/1 M

Zo 0.15 pF/500

1X Passive 100 pF/1 M

100

1k

10k

100k

1M

10M

100M

1G

10G

Frequency

43 2018/12/16

信号完整性测试规范和工作流程

信号完整性测试规范和工作流程(Ver0.9x)一.主要目的:信号完整性测试的思想是信号源输出,经过传输线到达信号末端(负载),信号本身的相对变化情况。

主要目的是验证PCB设计是否保证了信号在传输过程中能否保证其完整性,以信号的相对测试为主旨,信号本身8的绝对测试为辅。

信号比较的内容主要是信号的本征特性参数。

同时也部分验证电路原理设计的合理性。

也检验产品的性能符合国家有关标准的要求,比如3C、EMC、ESD等。

从定性参数的角度保证PCB设计达到了电路设计的要求,同时也保证产品的可靠性、一致性。

信号完整性测试一般是在线测试,因此很多测试参数在不同的工作模式下会有较大的差别。

一般情况下需要测试静态工作模式,但一些参数需要测试满负荷工作模式。

另外测试点的选择,特别是接地点的位置会对测试结果有很大的影响。

二.基本要求:要求测试准确、可靠、完善。

并要求有完整的测试报告。

这里的要求是一般通用性的要求,针对具体的产品、产品的不同阶段,可以提出不同的参数要求和具体的测试内容。

由于测试是在PCB板上(或称“在线”)的测试,因此一些测试条件和测试参数的定义条件可能会出现不一致的情况,因此规定:测试的基本状态在没有任何说明的情况下,认为是静态工作模式或额定正常工作模式。

如果在测试方法中有规定或说明的,以测试说明的条件为准。

在类型和参数中列出了比较详细全面的参数,但在测试中可能没有要求,因此,具体产品如果需要测试请加以特别说明。

一般规定:主要参数是必须测试的项目参数。

+三.类型和参数:3.1电源部分:3.1.1电源类型分为LDO电源、DC/DC电源。

3.1.2主要参数有:幅度、纹波、噪声。

3.1.3状态分为:额定负载、空载、轻载、重载、超载。

3.1.4保护能力:输出电流保护、输出电压保护、输入电压保护、热保护。

3.1.5其它参数:输入电压适应性、静态电流、关机电流(漏电流)。

3.2时钟信号:3.2.1时钟源分类:晶体时钟(正弦波时钟)、晶振时钟(方波时钟、钟振时钟)。

I2C总线信号完整性测试

I2C总线信号完整性测试目录CONTENTS•信号完整性测试条件•I2C信号完整性测试一、信号完整性测试条件12<1>.熟悉逻辑电平及I2C总线协议的基本知识,熟练掌握示波器的使用方法;<2>.测试人员在测试操作仪器时必须穿戴防静电服、静电鞋和防静电帽;<3>.在用手持握被测电路板时必须戴防静电手套;<4>.测试人员在使用时必须要按照示波器的具体要求来操作。

31、测试点尽量不要引飞线,非引不可也要尽量短2、尽量减少探头探针与探头地线所构成的环路面积3、手不要触摸测试信号4、2个探头不能共用同一地线5、测量时,使输入信号达到最大示波器的满刻度6、测量时,示波器探头和电缆要远离潜在串扰源的地方7、测试过程中,禁止在测试环境附近打电话或使用其他有强辐射的设备,避免对测试结果产生干扰8、测量时,如果测量结果超出规格,须再次确认测试点与芯片规格,确认测量条件及测量方法无误后,更换新的PCBA板测量,若测量结果仍是Fail,则定性为Bug并与硬件/软件人员确认。

并提单至禅道Bug管理系统或Jira系统4示波器及探头<a>.为了确保测量数据的精度,应尽量采用高输入阻抗、小电容值、高带宽的有源探头和高带宽的示波器<b>.仪器预热:为了避免温度变化带来的误差,在测试进行前,仪器需要预热30分钟。

<c>.测量前,要校准仪器<d>.测量前,保证测试仪器与被测试单板/系统共地<e>.探头和示波器的带宽要超过被测信号带宽的3倍以上<f>.示波器的采样速率至少要超过被测信号最高频率成分的2倍<g>.建议使用示波器厂家推荐的示波器和探头组合进行测量<h>.不允许在探头还连接着被测试电路时插拔探头5根据电路原理图,遍历所有I2C总线信号,详细测试项如下表(1),表(2)所示:(标准速度)表(1)I2C总线SCL信号测试项及标准表(2)I2C总线SDA信号测试项及标准6测试点一般选择信号宿端,尽量在芯片的输入管脚上测量,或者尽量靠近输入管脚对于I2C写操作过程,测试点选择在信号宿端(从设备端)对于I2C读操作过程,测试点选择在驱动端(主设备端)71、满足单板/系统工作在特定的功能状态、业务状态下所测到的信号才是有效信号(I2C总线有通信)2、要求有效信号能够重复出现要求3、能够满足较长时间观察的要求81、《示波器使用操作手册》2、《UM10204-I2C总线协议》3、线路原理图、位置图及各芯片规格书二、I2C总线信号完整性测试1测试目的:验证I2C总线的信号质量是否符合芯片要求,测试指标项应根据具体芯片要求制定,具体指标有SCL和SDA的低电平电压,高电平电压,上升沿时间,下降沿时间,上过冲和下过冲。

信号完整性分析及测试

信号完整性分析及测试讨论议题信号完整性定义高速数字电路的常见问题及现象串行差分信号完整性(以最新的PCI-EXPRESS为例)信号完整性测试(DSO及探棒的选择等)信号完整性定义SI (SIGNAL INTEGRITY ),即信号完整性,是近几年发展起来的新技术。

SI 解决的是信号传输过程中的质量问题,尤其是在高速领域,数字信号的传输不能只考虑逻辑上的实现,物理实现中数字器件开关行为的模拟效果往往成为设计成败的关键败的关键。

111理想状态下的数字信号波形实际测量的数字信号波形(模拟量)Logic Signal +5 Volt S Logic Signal+5 Volt S Supply GroundSupply GroundSI:新概念,旧方法应用的是传统的传输线、电磁学等理论,以及复杂的SI应用的是传统的传输线电磁学等理论以及复杂的算法,解决以下几个方面的问题:反射;串扰;***过冲、振铃、地弹、多次跨越逻辑电平错误;*阻抗控制和匹配*EMC;*热稳定性;**时序分析芯片封装设计; 。

影响信号完整性的因素PCB层设置、PCB材料影响传输线特性阻抗等,间接影响信号完整性;线宽、线长、线间距在高速、高密度PCB设计中对信号完整性影响较大;温度、工艺等对设计参数的影响,间接影响信号完整性;器件工作频率、速度、驱动能力、封装参数等对信号质量有一定的影响;多负载拓扑结构对信号完整性产生较大的影响;阻抗匹配、负载;电源、地分割;趋肤效应;回流路径;连接器;过孔;电磁辐射;。

可见,信号完整性设计的考虑因素是多方面的,设计中应把握主要方面,减少不确定性,以下是一些常见的信号完整性现象及其产生的原因简析:常见的信号完整性现象及其产生的原因电平没有达到逻辑电平门限负载过重 传输线过长电平不匹配 驱动速度慢多次跨越逻辑电平阈值错误电感量过大 阻抗不匹配(Propagation Delay)信号建立时间不满足延时错误(p g y)信号建时间不满足 负载过重传输线过长驱动速度慢上冲/下冲高速、大电流驱动 阻抗未匹配电感量过大常见的信号完整性现象及其产生的原因振铃(不单调)传输线过长串扰多负载阻抗不匹配常见的信号完整性现象及其产生的原因昏睡的眼图原因很多:阻抗不连续,损耗…什么时候需要考虑信号完整性?200KHZ的信号是否为高速信号小问题:的信号是否为高速信号?高速电路有两个方面的含义:一是频率高,通常认为如果数字逻辑电路设计的频率达到或者超过20MHz~33MHz,而且工作在这个频率的电路已经占整个电子系统一定的份量(例如三分之一),则称为高速电路设计。

硬件测试技术【信号完整性测试】分解

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·认真·责任

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

7.过冲/下冲(Over shoot/under shoot):过冲就是指接收 信号的第一个峰值或谷值超过设定电压——对于上升沿是 指第一个峰值超过最高电压;对于下降沿是指第一个谷值 超过最低电压,而下冲就是指第二个谷值或峰值 8.振荡:在一个时钟周期中,反复的出现过冲和下冲,我们就称 之为振荡 9.串扰:串扰是指当信号在传输线上传播时,因电磁耦合对 相邻的传输线产生的不期望的电压噪声干扰,这种干扰是 由于传输线之间的互感和互容引起的。

共享时钟和嵌入式时钟

第三点: 共享时钟=> 嵌入式时钟

共享时钟: 范例: PCI

时钟与数据分别不同路径被传送 布线时要注意不能违反建立与保持时间

源同步Source Synchronous: 范例: AGP

单一Strobe, 或时钟加Strobe, 并行多路数据源同步 布线时要注意不能违反建立与保持时间

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·认真·责任

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

信号完整性的一些概念

1.传输线(Transmission Line):由两个具有一定长度的导 体组成回路的连接线,我们称之为传输线,有时也被称为 延迟线。传输线一共有四种:微波线,带状线,差分线和放射 状传输线

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·认真·责任

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

下冲(undershoot):就是第二个峰值或谷值超过设定电压 ―― 对于上升沿过度地谷值或对于下降沿太大地峰值。 设置时间(settling time)就是对于一个振荡的信号稳定到 指定的最终值所需的时间

【信号完整性测试方法】时域测试(波形、眼图、抖动、TDR、时序)要求 及 仪器设备

【信号完整性测试方法】时域测试(波形、眼图、抖动、TDR、时序)要求及仪器设备信号完整性测试方法简介信号完整性设计,在电路板设计过程中备受重视。

熟悉各类测试方法的特性,按照测试对象的特征和需求,选用合适些测试方法,对于选择方案,验证效果能够大大提高效率。

目前信号完整性的测试方法较多,从大的方向有频域测试、时域测试、其它测试。

(3类方法不是任何情况下都适合使用,信号完整性的测试方法,需要用到的仪器也很多。

)时域测试时域测试涵盖波形测试、眼图测试、抖动测试、TDR测试、时序测试。

01波形测试波形测试:是信号完整性测试最基础的方法,通常使用示波器进行测试。

测试波形的幅度、毛刺、边沿等。

通过测试波形的特征,分析幅度、边沿时间等指标是否满足要求。

波形测试需要遵循一定要求,才能保证测试误差尽量小。

⏹主机和探头一起配套的带宽要满足要求。

基板上测试系统的带宽应该在测试信号带宽的3倍以上。

在工程实践中,有的工程师随意找些探头就测试,不同厂家的探头匹配不同厂家的示波器,综合情况测试系统的误差就会很大。

⏹其次,需要注重细节。

如测试点一般选择在接收器件的附近,若条件限制无法测试,像BGA封装这类的器件,需要放在靠近Pin脚的PCB走线上或者Via上。

间隔接收器件PIn脚太远,信号发射,可能会促使测试结果和实际真实信号差异较大。

探头的接地线,也尽可能选择短的地线等。

⏹最后,应该考虑匹配。

主要关于使用同轴电缆测试的应用场景,同轴接到示波器上,负载常规是50Ω阻抗的直流耦合,对于有的电路,需要直流偏置,直接将测试系统接入会导致电路工作状态有影响,最终导致测试不到正常的波形。

02眼图测试眼图测试:针对有相关规范要求的接口(USB、SATA、HDMI、光接口)等。

通过具有MASK的示波器(含通用示波器、采样示波器、信号分析仪)。

这类示波器内部具有的时钟提取功能,能够显示眼图。

然而对于没有MASK的示波器,需要使用外接时钟实现触发。

信号完整性(SI)分析1-2演示幻灯片

SI的四种分析、描述手段和途径

• 经验法则; • 解析近似; • 数值仿真 (有场和路两种途径); • 实际测量。

34

SI仿真用软件

• SPICE(侧重IC的仿真程序) • Mentor公司:Hyperlynx • Candence公司:SigXP(SigXplorer) • Ansoft: HFSS(高频结构仿真器)、SI2D • Agilent公司:ADS

分析信号完整性分为时域和频域两种途径和手段。 时域(time domain)是对一个信号波形进行的示波器观察,它 通常用于找出管脚到管脚的时延、错位、过冲、下冲以及建立时 间。 频域(frequency domain)是对一个信号波形进行的频谱分析 仪观察,它通常用于波形与 FCC 以及其它 EMI 控制限制之间的比 较。一个生动的例子就是收音机——你在时域中收听它,但是为 了找到喜欢的电台位置你却需要在频域内搜寻。

31

研究中有两种主要的技术工具:分析型和描述表征型。 分析型指的是计算推理工具;表征型指的是测量工具。

分析工具强调推理,又进一步分为三类:经验法则、解 析近似和数值仿真。它们的准确度和难度各不相同。每一 个都很有用,适用于不同场合。

经验法则很实用,例如简单地认为“线段单位长度的自 感是 1nH/mm” ,可能对进一步的概念推理既直观又快捷。

36

0.6 信号完整性测量技术

测量工具也可以分为三类测量仪器:阻抗分析仪;矢量网络 分析仪(VNA)以及时域反射计(TDR)。

阻抗分析仪测量电压/电流比=阻抗。频率从 100Hz 到 40MHz。 有四个接头,一对接头产生流过被测器件(DUT)的正弦波电流, 第二对接头测量被测器件(DUT)的正弦电压。

信号完整性(SI),是指信号电压(电流)完美的波形形状及 质量。由于物理互连造成的干扰和噪声,使得连线上信号的波 形外观变差,出现了非正常形状的变形,称为信号完整性被破 坏。信号完整性问题是物理互连在高速情况下的直接结果。

信号完整性分析之二

2021/2/17

信号完整性分析之二

23

SI分析

• SI分析的原则 a.数字系统可以抽象成三个层次的检查: 逻辑,电路理论,电磁领域; b.逻辑层为三者中的最高层,在这里的SI 问题都很容易识别; c.电磁领域为三者中的最低层,很多SI问 题都属于电磁领域,例如反射,串扰,对地反 弹等;

2021/2/17

9

常见的SI问题

• 串扰产生的原因

a.传输线之间的耦合 b.过孔之间的耦合 c.传输线与平面之间的耦合 d.两个平面之间的耦合

2021/2/17

信号完整性分析之二

10

常见的SI问题

• 电源/地 噪音产生的原因 a.SSO----simultaneous switching output 驱动同步输出对电源或者地的寄生效应 又称做对地反弹. b.SSN---- simultaneous switching noise 同步开关噪音或电流变化噪音

2021/2/17

信号完整性分析之二

31

SI分析

• SI分析的原则(续)

例如:一段1inch的传输线在FR-4材质PCB中的 传输时间大概是200ps,对33M系统而言,它的信 号上升时间大概是3ns,这个时候传输线的延迟 是可以忽略的,所以我们可以使用集总电路模型 法;而对500M的系统而言,它的上升时间约为 200ps,这个时候传输线的延迟我们是不能忽略 的,所以我们必须使用分布式电路模型来分析.

信号完整性分析之二

2

带宽和采样率

• 带宽是指示波器垂直放大器的频率响应 定义为: 信号幅度下降3db.在此频点为示波器的带

宽在3db的带宽频率,信号垂直幅度的误差大约为30%. BW=0.42/Tr

信号完整性测试

信号完整性测试硬件电路测试中非常重要的一项是信号完整性测试,特别是对于高速信号,信号完整性测试尤为关键。

完整性的测试手段种类繁多,有频域,也有时域的,还有一些综合性的手段,比如误码测试。

不管是哪一种测试手段,都存在这样那样的局限性,它们都只是针对某些特定的场景或者应用而使用。

只有选择合适测试方法,才可以更好地评估产品特性。

本文将讲解常用的一些测试方法和使用的仪器。

一、波形测试使用示波器进行波形测试,这是信号完整性测试中最常用的评估方法。

主要测试波形幅度、边沿和毛刺等,通过测试波形的参数,可以看出幅度、边沿时间等是否满足器件接口电平的要求,有没有存在信号毛刺等。

波形测试也要遵循一些要求,比如选择合适的示波器、测试探头以及制作好测试附件,才能够得到准确的信号。

下图是DDR在不同端接电阻下的波形。

常见的示波器厂商有是德科技、泰克、力科、罗德与施瓦茨、鼎阳等等。

二、时序测试现在器件的工作速率越来越快,时序容限越来越小,时序问题导致产品不稳定是非常常见的,因此时序测试是非常必要的。

一般,信号的时序测试是测量建立时间和保持时间,也有的时候测试不同信号网络之间的偏移,或者测量不同电源网络的上电时序。

测试时序基本都是采用的示波器测试,通常需要至少两通道的示波器和两个示波器探头(或者同轴线缆)。

下图是测量的就是保持时间:三、眼图测试眼图测试是常用的测试手段,特别是对于有规范要求的接口,比如USB、Ethernet、PCIE、HDMI和光接口等。

测试眼图的设备主要是实时示波器或者采样示波器。

一般在示波器中配合以眼图模板就可以判断设计是否满足具体总线的要求。

下图是示波器测试的一个眼图:四、抖动测试抖动测试现在越来越受到重视,常见的都是采用示波器上的软件进行抖动测试,如是德科技示波器上的EZJIT。

通过软件处理,分离出各个分量,比如总体抖动(TJ)、随机抖动(RJ)和固有抖动(DJ)以及固有抖动中的各个分量。

对于这种测试,选择的示波器,长存储和高速采样是必要条件,比如2M以上的存储器,20GSa/s的采样速率。

信号完整性 常用的三种测试方法

信号完整性常用的三种测试方法信号完整性测试的手段有很多,主要的一些手段有波形测试、眼图测试、抖动测试等,目前应用比较广泛的信号完整性测试手段应该是波形测试,即使用示波器测试波形幅度、边沿和毛刺等,通过测试波形的参数,可以看出幅度、边沿时间等是否满足器件接口电平的要求,有没有存在信号毛刺等。

信号完整性的测试手段主要可以分为三大类,下面对这些手段进行一些说明。

1. 抖动测试抖动测试现在越来越受到重视,因为专用的抖动测试仪器,比如TIA(时间间隔分析仪)、SIA3000,价格非常昂贵,使用得比较少。

使用得最多是示波器加上软件处理,如TEK的TDSJIT3软件。

通过软件处理,分离出各个分量,比如RJ和DJ,以及DJ中的各个分量。

对于这种测试,选择的示波器,长存储和高速采样是必要条件,比如2M以上的存储器,20GSa/s的采样速率。

不过目前抖动测试,各个公司的解决方案得到结果还有相当差异,还没有哪个是权威或者行业标准。

2. 波形测试首先是要求主机和探头一起组成的带宽要足够。

基本上测试系统的带宽是测试信号带宽的3倍以上就可以了。

实际使用中,有一些工程师随便找一些探头就去测试,甚至是A公司的探头插到B公司的示波器去,这种测试很难得到准确的结果。

波形测试是信号完整性测试中最常用的手段,一般是使用示波器进行,主要测试波形幅度、边沿和毛刺等,通过测试波形的参数,可以看出幅度、边沿时间等是否满足器件接口电平的要求,有没有存在信号毛刺等。

由于示波器是极为通用的仪器,几乎所有的硬件工程师都会使用,但并不表示大家都使用得好。

波形测试也要遵循一些要求,才能够得到准确的信号。

其次要注重细节。

比如测试点通常选择放在接收器件的管脚,如果条件限制放不到上面去的,比如BGA封装的器件,可以放到最靠近管脚的PCB走线上或者过孔上面。

距离接收器件管脚过远,因为信号反射,可能会导致测试结果和实际信号差异比较大;探头的地线尽量选择短地线等。

最后,需要注意一下匹配。

信号完整性测试介绍

信号完整性测试介绍目录CONTENTS 1•信号完整性SI2•信号完整性测试内容3•信号完整性测试条件•信号完整性测试标准45•信号完整性问题总结一、信号完整性SI信号完整性SI(Signal Integrity):是指在电路设计中互连线引起的所有问题,它主要研究互连线的电气特性参数与数字信号的电压电流波形相互作用后,如何影响到产品性能的问题。

如果电路系统中信号能够以要求的时序,持续时间和电压幅度到达IC,则该电路系统具有较好的信号完整性。

反之,当传输的信号不能被IC正常响应时,就出现了信号完整性问题。

SI解决的是信号传输过程中的质量问题,尤其是在高速领域,数字信号的传输不能只考虑逻辑上的实现,物理实现中数字器件开关行为的模拟效果往往成为设计成败的关键。

理想数字信号波形实际数字信号波形(模拟量)SI 解决的问题 反射串扰过冲振铃地弹 时序 EMC在数字电路系统中,信号以逻辑“0”或“1”的方式从一个器件传输到另外一个器件,信号到底是“0”还是“1”,一般来说它们都是有一个参考电平。

在接收端的输入门里面,如果信号的电压超过高电平参考电压Vih,则该信号被识别为高逻辑;如果信号的电压低于低电平的参考电压Vil,则该信号就被识别为低逻辑。

如下图所示为一个理想信号经传输线后的接收端实际接收的信号理想数字信号接收端实际数字信号问题图形原因分析备注电平没有到达逻辑电平负载过重传输线过长电平不匹配驱动速度慢上冲/下冲高速、大电流驱动阻抗未匹配电感量过大其它相邻信号串扰典型的信号完整性问题及其产生的原因分析问题图形原因分析备注振铃(不单调)电感量过大阻抗不匹配延时错误负载过重传输线过长驱动速度慢二、信号完整性测试内容1 信号(SI)测试内容2 电源(SI)测试内容三、信号完整性测试条件1 单板/系统工作条件单板/系统工作在室温条件(20℃~27℃)单板/系统要可靠接地单板/系统上电正常工作,各模块工作均正常,30分钟后再开始测试单板/系统在轻载及满载情况下均应测试单板/系统电源稳定在额定电压±3%范围内2 测试人员要求<1>.熟悉逻辑电平及信号时序的基本知识,熟练掌握示波器及万用表的使用方法;<2>对单板/系统电路原理有深刻的认识,对信号分类及信号的流向有清楚认识,了解单板/系统上器件的工作原理、工作速度及工作电平;<3>.测试人员在测试操作仪器时必须穿戴防静电服、静电鞋和防静电帽;<4>.在用手持握被测电路板时必须戴防静电手套;<5>.测试人员在不同仪器时必须要按照仪器的具体要求来操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2013-8-18

CDR对眼图和抖动测试的影响

时钟恢复单元:CRU

– 当需要测试一个高速串行信号眼图时,需要一个时钟恢复单元,从被测信号 中恢复出时钟用于触发 – 事实上,一个真实的高速器件内部就有一个时钟恢复单元

CRU的要求

– 内置Golden-PLL,跟随信号的变化并解出时钟 – 内置针对于信号抖动的低通滤波器 – 内置抖动滤波器的带宽为被测数据率的1/1667 – 内置抖动滤波器的滚降特性满足-20dB/Dec

2013-8-18

眼图模板(MASK)的定义

16

2013-8-18

为什么要测试眼图

眼图是高速信号质量的最直接反映 眼图的好坏和信号传输的误码率相关 眼图是信号测试分析的最常用手段 MASK 可以直接反映您设计的系统是否“PASS”

17

2013-8-18

眼睛张开是否就表示信号传输没有问题?

6.25Gb/s at 17in (43cm) of backplane

6.25Gb/s after 34in (86cm) of backplane

Tx

+ + - -

path

+ -

Small differences in levels being measured

12 2013-8-18

眼图和信号传输质量

(between clock triggers the sampled DATA could be either a logical 1 or 0)

21

2013-8-18

时钟恢复CDR的功能

Differential serial data is sent without any clock signal across the interconnect to the receiver

27

2013-8-18

抖动的定义

What is jitter?

–“the deviation of an edge from where it should be”

抖动的表示方法

–时间(Jpp=100ps) –归一化UI (2.5Gbps datarate, Jpp=0.25UI) –弧度(Jpp=.25UI*2Pi=Pi/2 radians)

Networks”

29

2013-8-18

抖动 vs 相位 vs 频率

30

2013-8-18

为何抖动是问题?

在同步系统如SDH, 传输时钟的抖动影响子系统的同步, 过大的抖动直接造成误码, 或减低了 信号的消光比ER (等同电信号的信噪比SNR)。所以ITU-T, Bellcore, ANSI都制定模板Mask 来检定眼图是否拥有过大的抖动,以及测量传输时钟的抖动漂移。 传统的并行式数据通信,即多通道数据与时钟分别传送,往往因为PCB阻抗不匹配,传输路 径不一致而产生建立与保持时间违反。当速度增加的时候,准确控制传输时延显得异常的困 难,今天新颖的数据通信都已经是串行了, 不单只使用一对差分线来传送数据,以减低信 号EMI的干扰,更往往将时钟嵌入在数据中, 而接收端则使用CDR从数据中恢复时钟出来 。 所以,若数据的抖动过大,频率过高,接收端的CDR将无法恢复时钟而导致误码。 所以 需要控制系统的时钟与输出的数据抖动。 抖动直接减小了逻辑数字系统的建立保持时间的余量, 严重的影响逻辑运作。 有些情况,尤其以计算机行业应用为多(因不能有足够的空间进行EMI控制),使用一低频 信号调制其高速时钟,在频谱上的效果是使其能量被扩散, 从而减小EMI干扰。在时域上效 果是时钟的周期性抖动,其抖动波形正是调制信号。

抖动的基本术语

传统的测试方法 抖动的高级术语

高级抖动测试和分析方法

通过抖动分析定位电路故障根源

8

2013-8-18

眼图定义

9

2013-8-18

眼图的形成

10

2013-8-18

眼图的形成

11

2013-8-18

眼图反映了什么

6.25Gb/s at Tx launch into backplane

–4Extinction Ratio = PTopmean /PBasemean –4Quality Factor = (PTopmeanPBasemean)/(PTopsigma+PBasesigma) –OMA (Optical Modulation Amplitude)=PTop-Pbase

15

PCI-E信号完整性分析方法

–眼图分析,抖动分析,误码分析

5

2013-8-18

茶歇和Q/A

6

2013-8-18

高速电路信号完整性测试,调试和验证

高速眼图和抖动测试与分析

7

2013-8-18

内容

什么是眼图 眼图测试和分析的重要性 眼图测试和分析方法 眼图测试和分析对测试设备的要求 常见眼图反应的信号问题 抖动的定义

20

2013-8-18

眼图测试分类:等效眼图的生成

voltage Data

Mask test

Eye patterns are the common result of clock-triggering in Equivalent time sampling: vectors are not drawn since adjacent samples can jump from logical 1 to 0 frequently

18

2013-8-18

眼图测试分类:实时采样眼图

One trigger can initiate the real-time sampling of the entire record length Minimum time between real-time sampled points is determined by the fastest sample rate the realtime scope is capable of. 40GSamples/sec results in 25ps between sampled points.**

28

2013-8-18

抖动 ABC – 抖动 vs 漂移

快过10Hz的偏离为 : 抖动 Jitter 慢过10Hz的偏离为: 漂移 Wander

参考: ITU-T Recommendation G.810 (08/96) “Definitions and Terminology for Synchronization

time

Clock

Precision variable delay

A clock trigger can be usersupplied or recovered from the data to trigger the equivalent time sampler

When a clock signal is used to trigger the equivalent-time 8200 scope the sampled DATA signals generally create EYE PATTERNS

更大的眼睛意味着更多的信号幅度和 时间的余量 更大的眼睛系统可靠性更好 眼图过窄意味着信号的抖动过大,误 码率上升 眼图中心点

13

2013-8-18

眼图参数

14

2013-8-18

眼图测试项目

Jitter RMS = TCross1sigma Jitter Pk-Pk = TCross1pk-pk Eye Height = (PTopmean-3*PTopsigma)(PBasemean+3*PBasesigma) Eye Width = (TCross2mean-3*TCross2sigma)(TCross1mean+3*TCross1sigma) Crossing Percent, Duty Cycle Distortion, Noisepk-pk, NoiseRMS, SNR 高速光眼图测试中的项目

voltage

Data

time

A realtime scope does not require a separate signal to trigger: the signal under test can act as the trigger for initiating fast real-time sampling to acquire a waveform.

25

2013-8-18

如何得到张开的眼图

走线长度

– 短走线并非始终能够满足.短走线意 味低损耗.

走线宽度

– 宽走线可以降低趋肤效应.

减小板材的介电常数

– 即降低介电损耗(Dielectric Loss), 但将通过对跳变位预加重(Pre-Emphasis) 处理补偿线路上因信号跳变产生的 针对高频分量的损耗,需要器件支 持。

23

2013-8-18

眼图测试的时钟选择

采样示波器的CLK选择

–用户DUT提供的时钟作为外触发 –直接从数据中恢复时钟(需要硬件时钟恢复CDR)

实时示波器的时钟选择

–不需附加时钟作为触发信号,通过内嵌软件CDR恢复软件时钟,生 成眼图

24

2013-8-18

思考题

–对于一个1.25G的并行LVDS信号,如何测试眼图? –对于下图中的5Gbps串行信号,如何测试眼图,哪一类仪器合适? –在高速电路设计中,如何获得张开的眼图?

Tx

+ + - -

path

+ + -

Rcv

CDR DATA