基于FPGA的VHDL语言温度控制

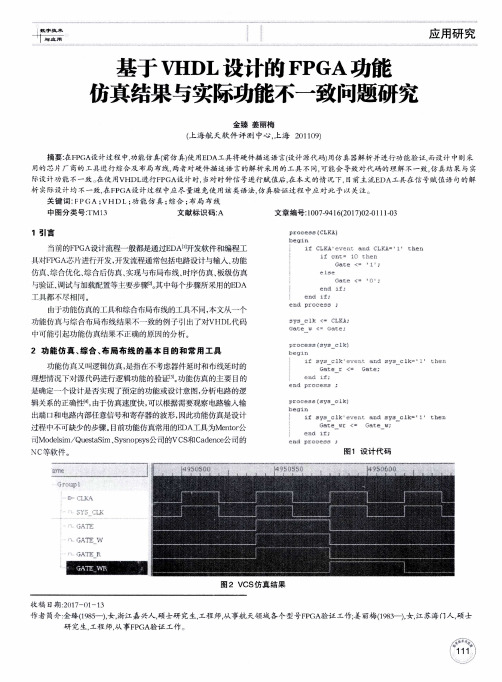

基于VHDL设计的FPGA功能仿真结果与实际功能不一致问题研究

图5 Ga t e — r 综 合 结 果

即 表 。 网表 文 件主 要 记 录 的是 所 用 工 艺 库 门级 单 元 之 间 的互 连 关 导致该时钟产生的信号用赋值后的时钟进行延时处理 时, 第一个节 系( 即门级结构) 。 而布 局布线则是对 表 中的每一个门级单元在器 拍 的延迟未起作用 , 仿真的信号 比实际信号在该处提前一个时钟周

n

一

0

窖

功能仿真 义叫逻辑仿真 , 是指在不考虑器 件延I t 寸 和布线延时的 理 想情 况下对源代码进行逻 辑功 能的验证l 3 】 。 功能仿真 的主要 目的 是确定一个设计是否实现了预定的功能或设计意 图, 分析 电路的逻 謇

A

L C d n 魏 矗 n e ~ , . l 。 f I ,

,

3 s

—

c lk <幸 CLKA;

s

G a te ;

一

G x e

l 0 e 一 ;

Gate

G 一

孽

C

2 功能仿真 、 综合 、 布局 布 线 的基 本 目的 和 常用 工具

≈

14

乞 肇

<

£ e

‘

; ,

i

k r

,都是通过E DA t I 开发软件和编程工 具; t C F P GA; 片进行开 发, 开发流程通常包括 电路设计与输入 、 功能

仿真、 综合优化 、 综合后仿真 、 实现与布局布线、 时序仿真 、 板级仿真

: r具都 小 尽相 同 。

j 验证 、 凋试 ! - - 5 J J 1 1 载配置等主要步骤 。 其 中每 个步骤所采用的E D A 触 e 0诺 p i b n K C 叫 _ L 1 w啦妇 f c 1 ; l e d n量 瞎1 : 畦 ; 巍 硅 哇 ; 3 0 r n e

基于vhdl的vivado使用流程

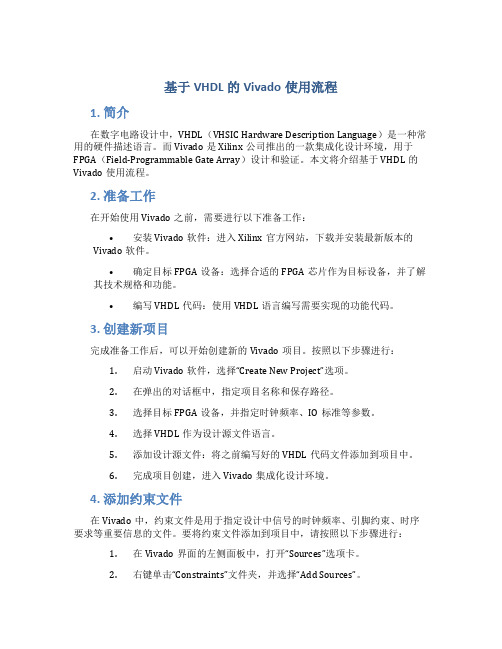

基于VHDL的Vivado使用流程1. 简介在数字电路设计中,VHDL(VHSIC Hardware Description Language)是一种常用的硬件描述语言。

而Vivado是Xilinx公司推出的一款集成化设计环境,用于FPGA(Field-Programmable Gate Array)设计和验证。

本文将介绍基于VHDL的Vivado使用流程。

2. 准备工作在开始使用Vivado之前,需要进行以下准备工作:•安装Vivado软件:进入Xilinx官方网站,下载并安装最新版本的Vivado软件。

•确定目标FPGA设备:选择合适的FPGA芯片作为目标设备,并了解其技术规格和功能。

•编写VHDL代码:使用VHDL语言编写需要实现的功能代码。

3. 创建新项目完成准备工作后,可以开始创建新的Vivado项目。

按照以下步骤进行:1.启动Vivado软件,选择“Create New Project”选项。

2.在弹出的对话框中,指定项目名称和保存路径。

3.选择目标FPGA设备,并指定时钟频率、IO标准等参数。

4.选择VHDL作为设计源文件语言。

5.添加设计源文件:将之前编写好的VHDL代码文件添加到项目中。

6.完成项目创建,进入Vivado集成化设计环境。

4. 添加约束文件在Vivado中,约束文件是用于指定设计中信号的时钟频率、引脚约束、时序要求等重要信息的文件。

要将约束文件添加到项目中,请按照以下步骤进行:1.在Vivado界面的左侧面板中,打开“Sources”选项卡。

2.右键单击“Constraints”文件夹,并选择“Add Sources”。

3.在弹出的对话框中,选择约束文件并添加到项目中。

4.在Vivado界面的左侧面板中,打开“Constraints”选项卡,确认约束文件已成功添加。

5. 进行综合和实现在Vivado中,综合是将HDL(硬件描述语言)代码和约束文件结合起来,生成逻辑网表的过程。

fpga设计中vhdl语言简介

fpga设计中vhdl语言简介

VHDL是一种硬件描述语言(HDL),旨在帮助工程师和设计师进行复杂电路和系统的设计和仿真。

VHDL语言是由美国国防部发起的,现在已经成为全球应用最广泛的HDL之一。

VHDL语言的基础包括三个部分:实体(entity)、体(architecture)和过程(process)。

实体定义组件的接口,在其内部,architecture结构体提供了具体的实现。

过程是编写复杂操作的基本方式,类似于C语言中的函数。

VHDL语言的数据类型包括标准逻辑类型,如布尔、位和字符类型,以及更复杂的数据类型,如数组和记录类型。

此外,VHDL也支持自定义数据类型。

在FPGA设计中,VHDL语言的主要作用是设计和实现可编程逻辑电路。

VHDL语言描述的电路可以在硬件上运行,也可以使用仿真器进行验证和测试。

总体而言,VHDL语言是一种强大的硬件描述语言,对于设计和实现复杂的电路和系统非常有用。

在FPGA设计中,VHDL语言是必不可少的一部分。

基于FPGA的测控系统设计与实现

基于FPGA的测控系统设计与实现一、引言随着科技的发展,现代工程领域对于高精度、高速度、高可靠性的测控设备的需求也越来越大。

其中,基于FPGA的测控系统具有极高的灵活性和可扩展性,能够满足不同领域的测控需求。

本文将介绍基于FPGA的测控系统设计与实现,主要包括系统架构、硬件设计、软件编程等方面。

二、系统架构设计基于FPGA的测控系统一般由FPGA芯片、外设模块、存储设备和通信接口等部分组成。

其中,FPGA芯片作为核心部分,负责控制整个系统的运行。

外设模块提供不同功能的接口,如模拟采集、数字转换、时钟输入、GPIO等。

存储设备用于存储测量数据和程序代码。

在系统架构设计时,需要根据实际需求选择适合的外设模块和通信接口,以及合适的存储设备。

此外,还需要考虑不同模块之间的数据传输和控制信号,确定系统的总体布局和数据流图。

三、硬件设计基于FPGA的测控系统的硬件设计主要包括电路原理图设计、PCB设计和硬件调试等部分。

在电路原理图设计时,需要根据系统架构设计绘制不同模块的电路图,并考虑电路参数的选择和优化。

在PCB设计时,需要将电路原理图转化为布局图和线路图,并按照标准的PCB设计流程进行布线、加强电路抗干扰性、防止电磁辐射等操作。

在硬件调试过程中,需要用示波器、万用表等工具对电路进行调试和测试,确保电路稳定运行。

四、软件编程基于FPGA的测控系统的软件编程主要包括FPGA芯片的Verilog/VHDL编程、上位机程序的编写等内容。

在FPGA芯片的Verilog/VHDL编程中,需要根据不同外设模块的接口来编写对应的硬件描述语言代码,如时钟控制、数据输入输出、状态控制等。

在上位机程序编写中,需要使用不同编程语言(如C/C++、Python等)来编写程序,实现与FPGA芯片的通信、测控算法的实现、数据可视化等功能。

五、系统应用与实现基于FPGA的测控系统应用广泛,如测量、控制、自动化、通信等领域。

在实际应用中,需要根据具体的应用场景和需求来设计相应的测控系统,并进行相关智能算法的设计和调试。

FPGA开发技术及VHDL语言

FPGA与CPLD的辨别和分类

④ CPLD的速度比FPGA快,并且具有较大的 时间可预测性。 ⑤ CPLD保密性好,FPGA保密性差。 ⑥一般情况下,CPLD的功耗要比FPGA大,且 集成度越高越明显。

FPGA与DSP的选择

DSP(digital singnal processor)是一种独 特的微处理器,有自己的完整指令系统,是以 数字信号来处理大量信息的器件。一个数字信 号处理器在一块不大的芯片内包括有控制单元 、运算单元、各种寄存器以及一定数量的存储 单元等等,在其外围还可以连接若干存储器 , 并可以与一定数量的外部设备互相通信, 有软、硬件的全面功能,本身就是一个微型计 算机。

FPGA技术与VHDL设计

南阳理工学院 计算机科学与技术系 通信工程教研室 路新华 Tel:62076343 Email:ieluxinhua@

课程学习内容

是什么 能做什么 怎么做 学习方法是什么 达到什么目标

一、是什么——概念

EDA:电子设计自动化 Electronic Design Automation

(

说明: (3)在RTL仿真阶段,应该建立一个测试台。此测

试台可以在整个FPGA流程中进行仿真验证(RTL级

、功能级、时序门级)。测试台不但提供测试激励

与接收响应信息,而且可以测试HDL仿真流程中的

关键功能(如运算部件输出值的正确性等)。

说明:

(

4)在功能级仿真阶段,一般验证综合后是

否仍与RTL级仿真结果相同。 (5)在门级仿真阶段,由于已经针对具体的 FPGA厂家技术进行了功能级仿真,因此可以 通过布局布线得到标准延格式下的时序信息 进行门级仿真。

一般地说,利用EDA技术进行电子系统设计,归纳起来主要 有以下4个应用领域:

基于FPGA智能温度传感器监控报警系统的设计

基于FPGA智能温度传感器监控报警系统的设计概述本文将详细介绍基于FPGA智能温度传感器监控报警系统的设计。

该系统由FPGA、温度传感器和报警器等组成,可以实时采集环境温度数据并进行处理,同时还可以根据设定的报警阈值进行温度报警。

该系统具有实时性、准确性和灵敏度高等优点,在工业、仓储等领域有广泛应用价值。

设计方案系统硬件设计智能温度传感器智能温度传感器采用DS18B20数字温度传感器,其精度高、体积小、响应速度快、使用方便等优点,能够满足系统的需要。

传感器输出数字量信号,可通过FPGA进行处理并转化为模拟量信号。

FPGAFPGA是本系统的核心部件,负责实现数字信号处理和温度阈值报警功能。

我们选用Xilinx Spartan-6系列FPGA,其具有高速、低功耗、可编程等特点,同时还有丰富的外设资源可以扩展。

报警器为了保证报警的及时和可靠性,我们使用了声光报警器,其能够在温度超出设定阈值时及时报警。

系统软件设计VHDL设计我们采用了VHDL语言对系统进行设计,通过其高级抽象、可移植性强等特点,实现了可适应性强、代码简洁的设计。

其中,数字信号处理主要包含数据的采集、过滤和频率变换等部分;温度阈值报警主要包含数据的计算和闸门控制等。

界面设计为了让用户更加便捷地使用该系统,我们设计了简洁明了的界面,包括温度值显示、报警阈值设置和报警状态等。

系统实现硬件实现按照上述设计方案,我们完成了硬件电路的设计,其中智能温度传感器采用了标准接口,与FPGA连接顺畅稳定。

报警器也能有良好的响应效果。

软件实现通过VHDL语言,我们完成了数字信号处理和温度报警部分的代码编写,在模拟器中进行了仿真和调试,并进行了综合和布局。

最终在FPGA平台上进行了验证,并与界面进行了充分交互。

结果分析经过系统实现,我们完成了一个基于FPGA智能温度传感器监控报警系统的设计。

在实际测试中,该系统具有所需的准确性、灵敏度和实时性等特点,能够实时采集环境温度并进行温度阈值报警。

《VHDL语言程序设计》课程教学大纲

《VHDL语言程序设计》课程教学大纲课程简介课程简介:本课程为软件工程专业嵌入式专业方向的专业课,是开发基于FPGA/CPLD嵌入式系统的必备基础。

主要内容包括FPGA/CPLD目标器件的结构和工作原理、EDA技术和工作流程、VHDL基础知识、VHDL实用方法和设计深入、原理图输入法、LPM宏功能模块实用方法、状态机设计以及EDA优化设计。

目的是为后续课程的学习和嵌入式系统的设计作必须的基础准备。

课程大纲一、课程的性质与任务:本课程是软件工程专业的专业方向课程。

教学任务主要包括使学生了解EDA技术的工作流程,正确使用开发平台,掌握以VHDL为代表的硬件描述语言的基本知识、编程实用方法和工程设计方法,掌握原理图设计法、状态机设计法,能够正确使用IP Core和LPM等宏功能模块。

本课程是软件工程专业嵌入式专业方向的第一门专业方向课,是后续课程的必备基础,具有较重要的地位。

二、课程的目的与基本要求:本课程涉及到的学科基础知识面广,要求软硬件兼备,需要较好的学科基础。

通过本课程的学习,最终达到能够设计基于FPGA/CPLD的ASIC,并能进行EDA优化的目的。

三、面向专业:软件工程四、先修课程:《计算系统基础》五、本课程与其它课程的联系:本课程的先行课程是计算系统基础。

服务的主要后续课程包括基于FPGA的嵌入式软件开发、基于ARM的嵌入式软件开发等。

六、教学内容安排、要求、学时分配及作业:第一章概述(2学时)1.1 EDA技术及其发展(C)1.2 硬件描述语言硬件描述语言种类、自顶向下设计方法、EDA工程设计流程。

(A)1.3 面向FPGA/CPLD的开发流程设计输入、分析综合、布局布线、仿真、下载和硬件测试。

(A)1.4 IP Core 及EDA技术发展趋势。

(C)第二章 FPGA硬件特性与编程技术(8学时)2.1 PLD发展历程及其分类(c)2.2 低密度PLD工作原理PROM、PLA、PAL、GAL。

《VHDL语言程序设计》课程教学大纲

GDOU-B-11-213《VHDL语言程序设计》课程教学大纲课程简介课程简介:本课程为软件工程专业嵌入式专业方向的专业课,是开发基于FPGA/CPLD嵌入式系统的必备基础。

主要内容包括FPGA/CPLD目标器件的结构和工作原理、EDA技术和工作流程、VHDL基础知识、VHDL实用方法和设计深入、原理图输入法、LPM宏功能模块实用方法、状态机设计以及EDA优化设计。

目的是为后续课程的学习和嵌入式系统的设计作必须的基础准备。

课程大纲一、课程的性质与任务:本课程是软件工程专业的专业方向课程。

教学任务主要包括使学生了解EDA技术的工作流程,正确使用开发平台,掌握以VHDL为代表的硬件描述语言的基本知识、编程实用方法和工程设计方法,掌握原理图设计法、状态机设计法,能够正确使用IP Core和LPM等宏功能模块。

本课程是软件工程专业嵌入式专业方向的第一门专业方向课,是后续课程的必备基础,具有较重要的地位。

二、课程的目的与基本要求:本课程涉及到的学科基础知识面广,要求软硬件兼备,需要较好的学科基础。

通过本课程的学习,最终达到能够设计基于FPGA/CPLD的ASIC,并能进行EDA优化的目的。

三、面向专业:软件工程四、先修课程:《计算系统基础》五、本课程与其它课程的联系:本课程的先行课程是计算系统基础。

服务的主要后续课程包括基于FPGA的嵌入式软件开发、基于ARM的嵌入式软件开发等。

六、教学内容安排、要求、学时分配及作业:第一章概述(2学时)1.1 EDA技术及其发展(C)1.2 硬件描述语言硬件描述语言种类、自顶向下设计方法、EDA工程设计流程。

(A)1.3 面向FPGA/CPLD的开发流程设计输入、分析综合、布局布线、仿真、下载和硬件测试。

(A)1.4 IP Core 及EDA技术发展趋势。

(C)第二章 FPGA硬件特性与编程技术(8学时)2.1 PLD发展历程及其分类(c)2.2 低密度PLD工作原理PROM、PLA、PAL、GAL。

毕业设计(论文)-利用VHDL语言在FPGA上实现I2C总线控制器的功能模板

摘要随着微电子技术的发展,现场可编程逻辑门阵列FPGA(Field Programmable Gate Array)可以实现数字电路系统设计的功能。

尤其现场可编程逻辑门阵列FPGA具有集成度高的优点,受到工程界高度的重视。

I2C 总线以接口简单,成本底,可扩展性好在数字系统中得到了广泛的应用。

硬件描述语言是数字系统高层设计的核心,是实现数字系统设计新方法的关键技术之一。

本课题正是利用VHDL语言在FPGA上实现I2C总线控制器的功能。

首先研究了I2C总线的规范,又简要介绍了QuartusⅡ设计环境以及FPGA 的设计流程。

在此基础上,重点介绍了I2C控制器的总体设计方案,以及在QuartusⅡ平台上的时序仿真。

关键词Quartus II;I2C总线控制器;现场可编程逻辑门阵列;时序仿真AbstractWith the development of micro electric and EDA(electronic design automation)technology, FPGA(field programmable gates array) can realize the function of digital circuit system design .FPGA have the merit of filed programmability and High integration rate ,therefore is highly recognized for engineering.I2C bus is widely applied in the digital system as simple interface ,expedient use ,low cost and good expansibility .VHDL is considered as a core of digital system design and a key technique of implement digital system.The design realizes the function of I2C bus interface on the FPGA .At first the thesis deeply research I2C bus specification ,then briefly introduce the Quartus II design environment and the design method ,as well as FPGA design flow .In this foundation,I2C bus controller design scheme and the timing simulation under Quartus II is particularly introduced.Key words Quartus II;I2C bus controller ;FPGA ;timing simulation目录摘要 (I)Abstract .................................................................................................................. I I 第1章绪论.. (5)1.1 课题背景 (5)1.2 I2C总线的产生及发展 (6)1.3 FPGA的现状与展望 (6)1.4 相关工作 (6)第2章I2C总线技术的研究 (8)2.1 I2C总线的概念 (8)2.2 I2C总线的传输 (9)2.2.1 数据的有效性 (9)2.2.2 I2C总线数据传送的开始和停止条件 (9)2.2.3 I2C总线传输过程中的应答信号 (10)2.2.4 I2C总线数据传送的重复开始条件 (11)2.2.5 I2C总线的传输过程中的字节格式 (11)2.2.6 I2C总线的器件子地址 (11)2.2.7 I2C总线传输信号的时序 (12)2.3 本章小结 (14)第3章VHDL语言的基础知识 (15)3.1 VHDL语言的概述 (15)3.2 VHDL语言的特点 (15)3.3 VHDL语言的程序结构 (16)3.3.1 VHDL程序的库 (16)3.3.2 包集合 (16)3.3.3 实体说明 (17)3.3.4 构造体 (18)3.3.5 配置 (18)3.4 本章小结 (18)第4章设计工具和设计方法 (19)4.1 设计工具 (19)4.2 基于FPGA的数字电路的设计流程 (20)4.3 本章小结 (21)第5章I2C总线的功能设计 (23)5.1 I2C总线完成的功能 (23)5.2 用VHDL语言实现写操作时的串行转并行 (24)5.3 用VHDL语言实现顺序读操作时的并行转串行 (24)5.4 I2C总线控制器的顶层设计 (25)5.5 本章小结 (26)第6章I2C总线的硬件时序仿真 (27)6.1 器件的选择 (27)6.2 硬件仿真 (28)6.2.1 用VHDL语言实现写字节周期 (29)6.2.1 用VHDL语言实现顺序读字节周期 (30)6.2.3 用VHDL语言实现选择性读字节周期 (30)6.3 本章小结 (31)结论 (32)致谢 (33)参考文献 (34)第1章绪论1.1 课题背景近年来,随着社会的发展,电子产品越来越多的进入人们的生活和工作中,成为了我们生活中必不可少的一部分,随着计算机的普及,以及电子设备之间相互沟通的更加频繁,为了更方便的实现器件与器件之间的通信,研发人员从消费者电子、电讯和工业电子中许多看上去不相关的设计中寻找到了他们的相似之处,例如几乎每个系统都包括:(1)一些智能控制,通常是一个单片的微控制器。

基于FPGA的嵌入式CPU的VHDL设计

基于 F P GA 的嵌入 式 C P U的 V HD L设计

史 展 李 占宣 z

( 1 、 黑龙江农垦石油化工销 售公 司 , 黑龙江 哈 尔滨 1 5 0 0 3 6 2 、 哈 尔滨金 融学院计算机 系, 黑龙 江 哈 尔滨 1 5 0 0 3 0 )

摘 要: 提 出一种 嵌入 式 C P U核 的 V H D L行 为设 计 方 法 , 是 基 于指令 对 数 据流 流 通控 制 行 为 的描 述 。该 方法 可 以 快速 创 建 兼 容 已有指令集的 C P U核的 V H D L模型 , 易于修改, 提 高设计效率。同时介 绍兼容 8 0 5 1 单片机指令的 C P U的 V H D L设计例子 , 并给 出使 用 A h e r a Q u a r t u s l I 工具 在 E P 3 C 4 0 Q 2 4 0 C 8 N 器件 上进 行 综 合 实现 C P U核 设 计 的结 果 。 关键 词 : F P G A; 嵌入式 C P U ; V H D L ; 指令 ; 仿 真 嵌人 式 C P U 的设 计 是 S O C设 计 的核 心 ,在 F P G A器 件 中嵌 入 块 , 应该 与 电路模 块相 接 。电 路模 块 可 以 由 7 4 1 6 5 、 7 4 1 6 4及 一 个 三 式C P U有 硬 核和 软 核 两种 。 态 门组 成 。连 接方 式 是 三态 门的 输 出端 口接 单 片机 的 P 3 . 0 , 三 态 门 1 C P U行 为模 型 的控制端可 以由单片机的 P 3 . 6 来控制; 当P 3 . 6 = 0时 , 信号从单片机 C P U数 据 流行 为 模 型 是 根 据 C P U 对 数 据 流 的控 制 行 为 建 立 的 P 3 . 0输 出进 入 7 4 1 6 4的数 据输 入 端 ; 而当 P 3 . 6 = 1 时, 7 4 1 6 5的数 的, 符合 自顶 向下( T o p — t o — D o w n ) 的全正 向设计原则 。 数据流控制 的 据 输 出 至 P 3 . 0 。 行为描述 不涉及 C P U具 体 的 电 路 结 构 或 总 线 结 构 ,抽 象 和 概 括 3 . 2 . 4 锁 相环 应 用 C P U的行 为 。 单 片 机 的时 钟信 号 必 须 来 自锁 相 环 , 频 率 高低 可根 据 实 际需 要 2 C P U模 块 结 构 来确定 。例如配合延 时程序而选择 的主频频率 , 或在 串行通信 中特 根据 C P U数 据 流行 为模 型 , 目标 器 件 的 写 控制 、 数 据 源 选 择 和 定波特率所对应 的特定的主频频率等。 此外 , 若需高速运算, 则可将 传输通道选择行为都是 由 i n s t r _ e o d e指令码决定的 ,可用指令译码 时钟频率设得 比较高。 尽管最高可大于 8 0 0 M H z , 但为了确保工作 的 模 块 实 现数 据 流 控制 行 为 。 稳定 性 , 一 般 频 率不 要 大 于 5 5 0 MH z 。当然 , 锁相 环 还 能 为 F P G A中 R O M 的地 址 r o m —a d d r 连至 P c寄存 器 输 出 , R O M 的数 据 线 或外 部 的其 他 扩 展模 块 提供 品质 良好 和 精 确 的时 钟信 号 。 连 接 到控 制 器 的 数据 输 入 。 控 制 器 是一 个 状 态机 , C P U先 从 R O M读 3 . 2 . 5软 件 设计 与 调试 取并保存 指令码和立即数 , 输 出指令码 i n s t r_ c o d e 、 立 即数 i n s t r 所有硬件电路设计完成后 , 要为单片机的工作编写软件。 d a t a l 、 立 即数 i n s t r— d a t a 2 至 译 码器 , 然后输出 i n s t r o p 信号有效 , 电路 系 统设 计 和 调试 步 骤 如下 : 数据被写入 目标器件 , 完成指令操作 , 再读取下一条指令 。C P U 中 ( 1 ) 调入 8 0 5 1 C P U核 : C P U 8 0 5 1 V1 . v q m。 的寄存器 由特殊 和通用寄存器组成。为提高程序执行效率和速度 , ( 2 ) 调入 L P M— R O M程序存储器 , 存储 量大小可根据应用程序 累加器设计成具有移位功能 , P c寄存器具有 自加功能、 P C计数器 的大小 来 决 定 。 和D P T R 具有和地址总线相 同位宽 、标志寄存器 P S W具有位操作 对7 4 1 6 5和 7 4 1 6 4的读 写程 序 如 下 : 等功能 。通用寄存器 R 0 一R 7可用分布式 R A M实现 , 用块 R A M实 S E T B P 3 . 6 ; P 3 . 6 = 1:选 择 S F T模 块 ( 即7 4 1 6 5 ) , 读人 8 现双 端 口 R A M。A L U是 1 6位运 算 器 , 实现 1 6 位加 、 减、 8 位 乘 法 运 位 数据 算 和 逻 辑 运算 。指令 译 码 模块 是 一 个组 合 电路 , 当C P U读 取 新 的指 C L R P 3 . 5 ; 当P 3 . 5 = 1 时, 时钟 信 号到 令码 I n s t r— c o d e 后 ,指 令译 码 模 块 根 据 当前 的指 令 选 择数 据 源 、 S E T B P 3 . 5 ; 把 并 行 输 入 的 8位 数 据 D [ 7 — 0 1 锁 人 移 位 寄 选 择 数 据通 道 和 选择 数 据 写入 目标 器 件 。 存 器 3设 计 综合 仿 真 CLR P3 . 1 3 . 1 K 8 0 5 1 单 片机 软 核 基本 功 能 和结 构 S E T B P 3 . 1 ; 时 钟上 升 沿 后锁 存 O [ 7 . . 0 1 CLR P 3. 5 K 8 0 5 1 单 片 机 核 属 于 8位 复 杂 指 令 C P U,存 储 器 采 用 哈 佛 结 构。指令 系统与 8 0 5 1 / 2 、 8 0 3 1 / 2 等完全兼容 , 硬件接 口也基本相 同。 M O V S C O N, # 1 0 H ; 设置 串 口数据 读 入 不 同之 处 主 要有 : G G G : J N B R I , G G G ; 检测 R I 标 志 MOV A, S BUF ( 1 ) K 8 0 5 1 C P U是 以 网表 文 件 的方 式 存 在 的 ,只 有 通 过 编 译 综 合, 并载入 F P G A 中才 以 硬件 的方 式 工 作 , 而普通 8 0 5 1总是 以硬 件 C L R R I ; 清0 , R I 标 志 方 式存 在 的 。 MO V 4 4 H , A ; 将来 自 F P G A的 8 位数据存入 4 4 H单 ( 2 ) K 8 0 5 1 C P U无 内部 R O M和 R A M,所 有 程 序 R O M 和 内 部 兀 R A M都必须外接 , 但仍是在 F P G A内部 。 C L R P 3 . 6 ; P 3 . 6 = 0: 选择 7 4 1 6 4 , 输出 8 位数 据 M OV S CON . 加 OH ( 3 ) 以软核方式存在能进行硬件修改和编辑 ; 能对 其进行仿真 和嵌 人 式 逻 辑 分 析 仪 实 现 实 时 时 序 测 试 ;能 根 据 设 计 者 的 意愿 将 M0 V A, # 5 B H ; 输出 5 B H C P U、 R A M、 R O M、硬件功能模块和接 口模块等实现于同一 片 F P G A M OV SBUF , A 中。 3 - 3使用逻辑分析仪 3 - 2单片机扩展功能模块的 S O C设计 S i g n a l T a p I I 和I n — S y s t e m S o u r c e s a n d P r o b e s 了 解 系 统 中某 些 3 . 2 . 1 C P U核 及 其端 口信 号 硬件模块在单片机软件控制下功能行为的正确性 ,特别是对 F P G A 8 0 5 1 C P U软核在配接上了程序存储器 R O M和数据 R A M后就 外 部 接 口电路 的控 制 情 况 的 了解 。 成为一个完整 的 8 0 5 1 单片机最 小系统 了。其 中的 C P U 8 0 5 1 V 1 是 4结 束语 8 0 5 1 单片机 C P U核 , 模块文件是 C P U 8 0 5 1 V1 . v q m, 由V Q M 原 码 表 仿真 显示 5条 指令 执 行 的结 果 是符 合 指令 功 能 要求 的。 每 一条 述, 可 用 例化 方 式直 接 调 用 。该 元 件 可 以 与其 他 不 同语 言 表述 的元 指 令 执 行 需 要 2 n s( 3 个c l k 时钟 周 期 ) ,其 中 R O M 取 指延 迟 约 为 件一同综合与编译 , 该核指令与标 准 8 0 5 1 指令系统完全兼容 , 外部 l n s , 译 码 延 迟 约为 l n s ,加 法运 算 延 迟 约 I n s 。仿 真 显 示 C P U时 钟 总 线 可 以连 接 2 5 6字 节 的 “ 内部” R A M和最大至 6 4 K字 节 的 程 序 最高频率为 8 0 0 MH z , 运行速度超过 9 0 MI P S , 是8 0 5 1 单片机 ( 时钟 R0M 。 频率 为 1 2 M H z ) 的近 4 0 0 倍。 若增加 3 级指令流水操作 , 可以使 C P U 3 . 2 . 2 C P U核工 作 存储 器 的C P I 为1 , 运 行速 度 可 以达 到 2 8 5 M I P S 。 为单片机核 配置 的数据存 储器是 2 5 6个字节 的 L P M — R A M 单 参考 文 献 元r a m 2 5 6 。该 R A M 可 由 内部 指 令 直 接 访 问 ,显 然 此 C P U

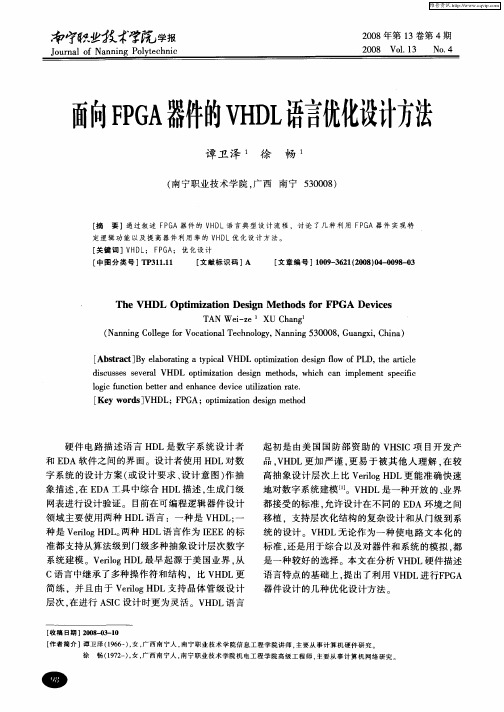

面向FPGA器件的VHDL语言优化设计方法

[ yw r sV L F G o t zt nd s nme o Ke o d ] HD ; P A; pi ai ei t d i m o g h

硬 件 电 路 描 述 语 言 HD L是 数 字 系 统 设 计 者 和E DA软 件 之 间 的界 面 。设 计者 使 用 HD L对 数 字 系统 的设 计 方 案 ( 或设 计 要 求 、 计 意 图 ) 抽 设 作 象描 述 , E 在 DA工 具 中综 合 HD L描 述 , 成 门级 生 网表 进 行 设计 验 证 。 目前 在 可 编 程 逻辑 器 件 设 计 领 域 主要 使 用 两 种 HD L语 言 :一 种 是 V L 一 HD : 种 是 V ro L 两 种 HDL语 言作 为 IE ei gHD 。 l E E的标

徐 畅 (9 2 , , 西 南 宁人 , 宁职 业 技 术 学 院 机 电工 程 学 院 高 级 工 程 师 , 17 一)女 广 南 主要 从 事 计 算 机 网络 研 究 。

o Βιβλιοθήκη 维普资讯 谭 卫泽

徐

畅

面 向 F GA 器 件 的 VHDL语 言优 化 设计 方 法 P

有 可能 的信 号 路径来使 设计 者决 定速 度关键 路

一

.

F GA器 件 结构 特 点 P

径 和 要 求 赋 予某 些 特 性 的路 径 , 可 指 出 设 计 的 也

系统级 时序建立要求 和保持要求 。

F G 器 件 在 结 构 上 类 似 于 门 阵列 ,但 是 它 PA

24在 E . DA 工 具 中生 成 芯 片编 程 文 件 , 用 利

V D HL

谭 卫 泽 徐 畅

( 宁职 业 技 术 学 院 , 西 南 宁 50 0 ) 南 广 3 0 8

基于FPGA的温度监控系统概要

摘要本论文介绍了一个基于FPGA的数字温度计电路的设计与实现。

该电路采用数字温度传感器DS18B20采集外界环境温度,同时结合该传感器的数据接口和特点,使用FPGA作为控制器,严格控制DS18B20 的时序 ,在单总线上实现读写功能,完成测量数字温度的功能。

再将采集的二进制数转换为BCD码 ,并通过数码管显示。

该系统软件设计通过 Verilog HDL 语言进行编译。

这次设计相比于传统的数字温度计具有结构简单,抗干扰能力强,功耗小,可靠性高,反应时间短等优点。

关键词:数字温度计;FPGA ;Verilog HDL ;DS18B20ABSTRACTThis paper expounds a design and implementation of a digital thermometer circuit based on FPGA. The circuit adopts the digital temperature sensor DS18B20 collecting the environment temperature, combining with the characteristics of the sensor data interface, using FPGA as the controller, strict control over the timing of DS18B20, read and write functions on 1-wire, complete the function of digital temperature measurement. Then measure the binary number into BCD code, and display it on the digital tube. The program design of the system is compiled by Verilog HDL language. Compared to the traditional digital thermometer, it has many advantages such as simpler structure, strong anti-interference ability, low consumption, high reliability, short reaction time.Keywords:Digital thermometer, FPGA, Verilog HDL, DS18B20目录1绪论 (1)1.1课题研究意义 (1)1.2课题相关技术的发展 (2)1.3课题的主要研究内容 (3)1.4论文结构安排 (3)2 总体方案的论证 (5)2.1 方案的选择 (5)2.2 方案论证与确立 (7)2.3 Quartus II介绍 (7)3. 系统的硬件设计 (10)3.1 系统的总体结构设计 (10)3.2 数据处理模块 (15)3.3数码管显示模块 (21)4 系统总体模块设计 (24)4.1 Verilog HDL语言介绍 (24)4.2 软件程序设计 (25)5整体编译结果与分析 (30)5.1 整体编译 (30)5.2 程序的下载调试 (31)6 设计中遇到的问题 (33)7结束语 (34)参考文献 (35)附录 (36)附录A系统总体电路图 (37)附录B 系统总程序 (37)附录 C 外文翻译 (49)1绪论1.1课题研究意义温度是生活中最基本的环境参数。

太阳能热水器控制仪设计(毕设)

摘要本课题的目的是结合太阳能热水器的具体应用,设计一种用于太阳能热水器的检测控制系统,以更好的实现对太阳能热水器的监控与控制。

太阳能热水器作为太阳能利用中最常见的一种装置,经济效益明显,正在迅速的推广应用。

根据太阳能热水器特点以及对控制器的要求,本文提出了一种基于单片机AT89C52的太阳能热水器智能控制器的设计方法。

本文在分析了解太阳能热水器及其控制器的发展和市场分布状况的基础上,描述了太阳能热水器控制器的组成及其工作原理.论文完成了控制器的硬件设计和软件设计。

在硬件设计中,利用AT89C52单片机作为控制的中心环节,控制整个系统运作.利用温度传感器DS18B20和分段式水位传感器作为水温水位测量环节,并将测量结果送单片机进行处理。

利用DS12887作为时钟芯片,以实现时间以及日期的显示。

选用液晶显示模块12864显示水温水位时间及日期,显示部分是人机交换的重要媒介之一。

在软件设计部分采用模块化结构,完成了包括主程序,水位检测子程序、LCD显示等子程序的设计。

系统主程序主要完成一些初始化功能,温度的检测以及控制辅助加热系统,同时完成信号转换及送显示功能;水位检测子程序完成水位测量及送数据功能;显示子程序完成水温水位及时间日期的显示功能;键盘扫描子程序实现功能转换及水温水位时间的设定。

论文通过对整体设计方案,硬件电路,软件程序的设计分析,实现了太阳能热水器的水温水位的检测与控制,具有实际的意义。

关键词:太阳能热水器;传感器;DS12887;单片机; FYD12864—0402BIAbstractThe purpose of this study is to introduce a kind of solar water heater detection based on the application of solar water heater,achieving to do the better monitoring and controling of the solar water heater. Solar water heater,as one of the most common use of the solar energy utilization. The economic benefit is obviously and the popularization and application is rapidly。

微波炉系统设计

1 选题的目的和意义1.1 选题的背景在现代人快节奏生活中,微波炉已成为便捷生活的一部分。

随着控制技术和智能技术的发展,微波炉也向着智能化、信息化发展。

而现有市售的微波炉其主要弊端为:不能按既有程序进行烹调,需要使用者根据食物的类型、数量、温度等因素去设定微波炉的工作时间,若设定的工作时间过长,含水分较多的食物可能会产生过热碳化的现象,若时间过短则达不到预期的烹调效果。

不仅在节能方面未做过多考虑,使用者还需要经常翻看使用说明书才能完成操作过程。

针对这些问题,笔者认为有必要研制一种操作简单且烹调效果好的微波炉,根据一些家常菜按固定程序烹调的现象,可采取分时、分档火力加热,节时又节能。

1.2 设计的目的和意义目前大部分微波炉控制器采用单片机进行设计,电路比较复杂,性能不够灵活。

本设计采用先进的 EDA 技术,利用 VHDL 设计语言,设计一种新型的微波炉控制器。

该控制器具有系统复位、状态控制、时间设定、火力档位选择、烹饪计时、温度控制、显示译码和音效提示等功能,基于 FPGA 芯片实现。

该微波炉控制系统,除实现常规的解冻、烹调、烘烤的基本功能外,还进行了创新设计,实现了微波炉的自定义设置。

本系统控制部分以 FPGA 芯片为核心,通过功能按键设置和手动数据输入,完成不同功能时自动以预置方案或者自定义方案加热。

其中,预制方案提供烹调、烘烤、解冻等系统烹调流程,仅供用户选择,无需设置;而自定义方案,用户根据食物含量、重量等手动设置时间、温度和选择火力等操作。

在烹饪过程中,能通过数码管显示或者指示灯提示知道食物的成熟度,可以智能控制。

该系统在功能执行时,能实现门开关检测、键盘输入扫描、温度控制、LED 显示、工作状态指示、蜂鸣等。

1.3 选题的技术现状目前大部分微波炉控制器采用单片机进行设计,电路比较复杂,性能不够灵活。

本文采用先进的 EDA 技术,利用 Quartus II 工作平台 VHDL 设计语言,设计一种新型的微波炉控制器系统。

基于FPGA的温度传感报警系统设计

基于FPGA的温度传感报警系统设计一、引言温度传感器在许多领域中被广泛使用,用于监测环境或设备的温度变化。

为了及时发现温度异常并采取相应措施,设计一个基于FPGA的温度传感报警系统具有重要意义。

本文将介绍如何利用FPGA实现温度传感器数据采集、处理和报警功能的设计方案。

二、系统结构基于FPGA的温度传感报警系统通常包括温度传感器模块、FPGA开发板、显示模块和报警器。

温度传感器用于采集环境温度数据,将数据传输给FPGA开发板;FPGA开发板负责接收并处理传感器数据,根据预设阈值判断是否触发报警;当温度超过设定阈值时,FPGA会触发报警器进行提示。

三、设计原理1. 数据采集:FPGA通过接口与温度传感器通信,获取实时温度数据。

2. 数据处理:FPGA对采集到的温度数据进行处理,与预设阈值比较,判断是否触发报警。

3. 报警功能:当温度超过设定阈值时,FPGA触发相应报警装置,如LED灯闪烁、蜂鸣器响声等。

四、软件实现1. Verilog/VHDL编程:使用Verilog或VHDL语言编写FPGA的逻辑设计,包括数据采集、阈值比较和报警逻辑。

2. 开发工具:选择适合的FPGA开发工具,如Xilinx ISE、Quartus II 等,进行逻辑综合、布局布线和下载等操作。

3. 调试验证:通过仿真和实验验证系统设计的正确性和稳定性。

五、性能分析通过对基于FPGA的温度传感报警系统进行性能分析,可以评估系统的响应速度、准确性和稳定性等指标。

同时,还可以分析系统的功耗、资源利用情况和可靠性等方面,为系统优化提供依据。

六、总结基于FPGA的温度传感报警系统设计结合了硬件设计和软件编程技朧,具有广泛的应用前景。

通过合理设计系统结构和软硬件实现,可以实现对温度异常的及时监测和报警提示,保障设备和环境的安全。

希望本文的介绍能够为读者深入理解基于FPGA的温度传感报警系统设计提供参考和启发,促进相关领域的技术创新和应用。

基于FPGA的智能温度控制系统的设计

基于FPGA的智能温度控制系统的设计智能温度控制系统是一种基于FPGA(现场可编程门阵列)的系统,旨在实现对温度的精确控制和自动调节。

随着科技的进步和人们对舒适生活的不断追求,温度控制在日常生活和工业生产中变得越来越重要。

传统的温度控制方法常常需要人工干预和手动调节,效率低下且容易产生误差。

因此,开发一种智能温度控制系统来解决这些问题变得至关重要。

本文的目的是设计一种基于FPGA的智能温度控制系统,通过使用FPGA的高度可编程性和强大的实时处理能力,实现对温度的准确测量、控制和调节。

同时,系统将具备智能化的特点,能够根据预设的温度范围和环境条件,自动调节温度并保持在合适的水平。

通过该系统的应用,可以提高温度控制的精确性和效率,提供更加舒适和节能的环境。

本文的框架将按照以下顺序展开:首先,介绍智能温度控制系统的基本原理和架构;然后,详细阐述FPGA在温度控制系统中的应用;接着,说明设计过程中的关键问题和解决方法;最后,对系统进行性能测试和实验验证,并对结果进行分析和讨论。

通过这些内容的阐述,旨在为读者提供有关基于FPGA的智能温度控制系统设计的全面参考,为今后的研究和应用奠定基础。

本文所提出的基于FPGA的智能温度控制系统设计具有一定的创新性和实用性,有望在温度控制领域产生积极的影响。

本文详细描述了基于FPGA的智能温度控制系统的设计过程,包括硬件和软件设计。

硬件设计硬件设计是构建基于FPGA的智能温度控制系统的关键步骤。

以下是硬件设计的主要内容:温度传感器:选择合适的温度传感器,例如热敏电阻或数字温度传感器。

将温度传感器与FPGA连接,以实时获取温度数据。

温度控制器:设计一个可调节的温度控制系统,可以根据测量到的温度对输出进行调整。

使用FPGA内部逻辑和外部元件(如开关和继电器)来实现温度控制功能。

显示界面:设计一个用户友好的显示界面,用于显示当前的温度和控制系统的状态。

可以使用液晶显示屏或LED显示器等显示设备。

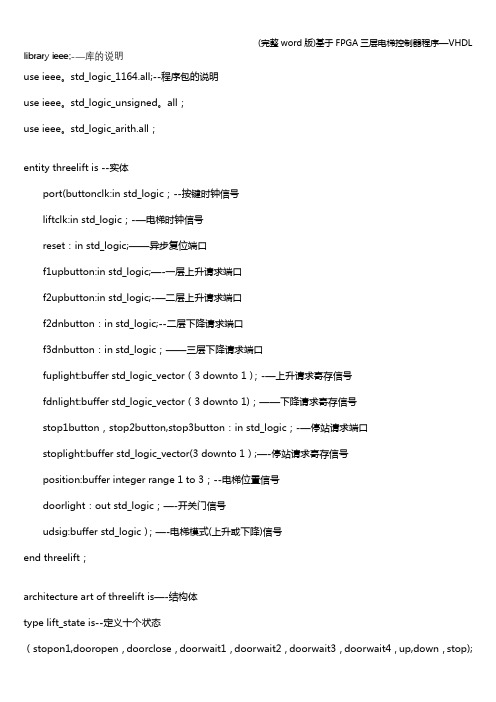

(完整word版)基于FPGA三层电梯控制器程序—VHDL

library ieee;-—库的说明use ieee。

std_logic_1164.all;--程序包的说明use ieee。

std_logic_unsigned。

all;use ieee。

std_logic_arith.all;entity threelift is --实体port(buttonclk:in std_logic;--按键时钟信号liftclk:in std_logic;-—电梯时钟信号reset:in std_logic;——异步复位端口f1upbutton:in std_logic;—-一层上升请求端口f2upbutton:in std_logic;-—二层上升请求端口f2dnbutton:in std_logic;--二层下降请求端口f3dnbutton:in std_logic;——三层下降请求端口fuplight:buffer std_logic_vector(3 downto 1);-—上升请求寄存信号fdnlight:buffer std_logic_vector(3 downto 1);——下降请求寄存信号stop1button,stop2button,stop3button:in std_logic;-—停站请求端口stoplight:buffer std_logic_vector(3 downto 1);—-停站请求寄存信号position:buffer integer range 1 to 3;--电梯位置信号doorlight:out std_logic;—-开关门信号udsig:buffer std_logic);—-电梯模式(上升或下降)信号end threelift;architecture art of threelift is—-结构体type lift_state is--定义十个状态(stopon1,dooropen,doorclose,doorwait1,doorwait2,doorwait3,doorwait4,up,down,stop);signal mylift:lift_state;signal clearup:std_logic;——上升和停站请求清除信号signal cleardn:std_logic;-—下降和停站请求清除信号begincontrolift:process(reset,liftclk)-—状态机进程variable pos:integer range 3 downto 1;beginif reset=’1' thenmylift 〈= stopon1;--异步复位,电梯的初始状态为一层开门状态clearup 〈= ’0’;cleardn 〈= ’0';pos:=1;position〈=1;elseif liftclk'event and liftclk=’1’ thencase mylift iswhen stopon1 => doorlight 〈= ’0’;position <= 1;pos:=1;mylift <= doorwait1;—-电梯等待4swhen doorwait1 => mylift 〈=doorwait2;when doorwait2 =>clearup〈='0';cleardn〈='0';mylift 〈=doorwait3;when doorwait3 => mylift 〈=doorwait4;when doorwait4 => mylift 〈= doorclose;when doorclose =〉doorlight 〈= '1’;—-关门,判定电梯下一个运行方式if udsig='0' then--电梯处在上升模式if position=3 thenif stoplight=”111" and fuplight="111" and fdnlight="111" then——没有请求信号时,电梯停在当前层udsig <= '1';mylift 〈= doorclose;elsif fdnlight(3)='0' or stoplight(3)=’0' then——本层有请求信号是,电梯开门udsig〈=’1';mylift<=dooropen;else ——否则下降udsig〈=’1’;mylift〈=down;end if;elsif position=2 thenif stoplight=”111" and fuplight="111” and fdnlight="111” thenudsig<=’0’;mylift〈=doorclose;elsif fuplight(2)='0' or stoplight(2)='0' then—-本层有上升或停站请求时时,电梯开门udsig<='0';mylift<=dooropen;elsif f uplight="111” and stoplight="111” and fdnlight="101" then-—只有二层有下降请求时,电梯开门udsig<='1’;mylift〈=dooropen;elsif stoplight(3)='0' or fdnlight(3)='0’ then--三层有停站请求或下降请求,则上升udsig<=’0';mylift<=up;else udsig<='1’;mylift<=down;end if;elsif position=1 thenif stoplight="111" and fuplight="111" and fdnlight=”111" thenudsig〈='0';mylift〈=doorclose;elsif stoplight(1)=’0' or fuplight(1)=’0' thenudsig<=’0';mylift<=dooropen;elseudsig〈=’0';mylift<=up;end if;end if;elsif udsig=’1' then--电梯处在下降模式if position=1 thenif stoplight="111" and fuplight="111” and fdnlight=”111" then udsig〈=’0’;mylift<=doorclose;elsif stoplight(1)='0' or fuplight(1)=’0’ thenudsig<='0’;mylift〈=dooropen;else udsig〈=’0';mylift<=up;end if;elsif position=2 thenif stopli ght=”111” and fuplight="111” and fdnlight="111” then udsig<=’1’;mylift〈=doorclose;elsif fdnlight(2)='0’ or stoplight(2)=’0’ thenudsig<=’1’;mylift<=dooropen;elsif fdnlight="111" and stoplight="111" and fuplight=”101" then udsig<=’0';mylift<=dooropen;elsif stoplight(1)=’0’ or fuplight(1)='0' thenudsig〈='1’;mylift<=down;else udsig〈='0';mylift<=up;end if;elsif position=3 thenif st oplight=”111" and fuplight="111" and fdnlight="111” then udsig〈=’1';mylift〈=doorclose;elsif fdnlight(3)='0' or stoplight(3)=’0' thenudsig<=’1';mylift<=dooropen;else udsig<='1';mylift〈=down;end if;end if;end if;when up=〉——电梯处于上升状态position〈=position+1;—-电梯楼层数加一pos:=pos+1;if pos 〈3 and (stoplight(pos)=’0' or fuplight(pos)=’0’) then mylift 〈= stop;——电梯在一层或二层,本层有停站或上升请求时,则停止elsif pos=3 and (stoplight(pos)='0' or fdnlight(pos)='0') then mylift 〈= stop;—-电梯处在三层,并且有三层停站或下降请求,则停止elsemylift <= doorclose;end if;when down =〉——电梯处在下降状态position 〈=position-1;--电梯楼层数减一pos:=pos—1;if pos 〉1 and (stoplight(pos)='0’ or fdnlight(pos)='0’) thenmylift <= stop;elsif pos=1 and (stoplight(pos)=’0’ or fuplight(pos)=’0’) then mylift 〈= stop;else mylift 〈= doorclose;end if;when stop =〉mylift 〈= dooropen;when dooropen => doorlight <= '0';if udsig=’0' thenif position〈3 and (stoplight(pos)=’0' or fuplight(pos)=’0’) then clearup 〈= '1';—-清除当前层上升和停站请求elseclearup〈=’1';cleardn<=’1’;end if;elsif udsig='1’ thenif position >1 and (stoplight(pos)=’0' or fdnlight(pos)=’0’)then cleardn 〈= '1';——清除当前层下降和停站请求else clearup <= '1';cleardn <= '1’;end if;end if;mylift <= doorwait1;end case;end if;end if;end process controlift;controlight:process(reset,buttonclk)beginif reset=’1' thenstoplight <= "111”;fuplight <= "111”;fdnlight <= ”111”;elseif buttonclk’event and buttonclk=’1’ thenif clearup='1' then--上升和停站请求清零stoplight(position)<= '1’;fuplight(position)<= ’1’;elseif f1upbutton=’1' then -—记忆各层上升请求fuplight(1)〈=’0’;elsif f2upbutton='1’ thenfuplight(2)<=’0';end if;end if;if cleardn=’1' thenstoplight(position)〈= '1';fdnlight(position)〈= ’1’;elseif f2dnbutton=’1' then --记忆各层下降请求fdnlight(2)〈=’0’;elsif f3dnbutton=’1’ thenfdnlight(3)〈='0’;end if;end if;if stop1button='1’ then -—记忆各层停站请求stoplight(1)<='0’;elsif stop2button='1' thenstoplight(2)〈='0’;elsif stop3button=’1' thenstoplight(3)<=’0';end if;end if;end if;end process controlight;end art;。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的恒温控制系统孵化器是一种最新的孵化禽蛋的机器,通过人工制造适合禽蛋孵化的恒温环境,来以较小的经济投入孵化禽蛋,通过调查,市面上的孵化器多数是以模拟电路的方式制造恒温环境,如下图这种模拟电路控制在实际应用中很难做到恒温控制,温度会在最终归的预设值附近上下浮动,影响禽蛋的孵化。

而且,孵化器的温度设置也是模拟电路,这样是完全达不到精准的温度设置。

通过学习FPGA,我设想运用数字电路来对禽蛋孵化器内部温度进行控制,来实现可控,可调,温度恒定的禽蛋孵化器。

具体的设计框架如下通过前向温度采集电路,采集当前孵化器内部的温度信号,将采集到的模拟信号通过ADC0809模数转换芯片,转变为FPGA可控的数字信号,FPGA芯片根据输入的当前实际温度,控制输出合理的数字信号,再由DAC0832转换为模拟信号,输入到后向加热执行电路,以此来完成对整个孵化器的温度控制。

整个系统中,带有温度传感器的前向温度采集电路作为系统的反馈环节,实时反映当前环境的具体温度,具体的电路图如下。

前向温度采集电路图此电路设计以AD590作为温度触感器,通过添加相应的调节电阻,让温度与输出电压保持一个相对线性的关系其中: W1R 为调零电阻2w R 为调满度电阻最终得到的温度与输出电压的关系式为: 0U 5T 100 模数转换芯片采用的是ADC0809,具体的连接电路图如下IN0—IN7管角中任选一路作为前向温度采集电路的输入,VCC与VREF同时接+5V电压,_VREF与GND接地,OUT1—OUT8数据输出端连接FPGA,START,OE,EOC,ADDA-C均连接FPGA,根据ADC0809的工作时序图,由FPGA给出相应的信号控制ADC0809。

数模转换部分采用的是DAC0832,具体连接图如下DI0-DI7分别于FPGA的8位数据输出端相连,因为DAC0832工作在连续的负反馈电路中,故采用直通的工作方式,将WR1与WR2直接与地相连,ILE与CS,Xfer引脚均接至FPGA,有FPGA发送控制信号来控制DAC0832的工作。

输出引脚Iout1与Iout2连接一个流压转换器,将输出的电流信号转换为需要的电压信号,并进行适当的放大。

最后输出到孵化器的加热电路。

FPGA模块控制ADC0809的工作状态,并接收来自ADC0809的数字信号,与键盘输入的预设信号进行比较后,将控制信息传送给DAC0832,经由数模转换器转换后加在发热装置两端,对整个孵化器内部温度进行控制。

整个的FPGA模块分为以下几个部分;分频模块:由于外界的时钟源一般都较高,而ADC0809以及键盘扫描模块需要的时钟频率较低,故需要对外界时钟源进行分频,这里外界输入时钟源为20MHz,对其进行64分频。

波形仿真图如下:从波形图可以看出,clk每经过64个脉冲,clk1跳转一次。

分频模块工作正常;统计报告图如下:分频模块的VHDL 文件见附录1.键盘模块:键盘模块的脉冲输入来自分频模块。

其中,输入端口为两位二进制数,分别接两个按键,来对预设温度进行加减调控。

输出有两个端口,xianshi 端口作为保留端口,存储着当前预设温度的数值,可外接显示设备。

zhi 端口为信息传送端口,其存储值为当前预设温度值经由采集电路温度—电压公式换算后的十进制数值。

换算公式如下: 0U 5T 100 例:38摄氏度对应的ADC0809输出数据为5*38*256/100/5,得到十进制值为97;波形仿真图如下:图(1)图(2)图中,shuru(1)为温度减按键,shuru(0)为温度加按键,相应的预设温度对应相应的ADC0809输出值,由图2得,当预设温度为38摄氏度时,对应换算后的ADC0809输出数据为97,与计算相符。

键盘输入模块工作正常。

统计报告图如下:键盘模块的VHDL文件见附录2.ADC0809控制模块:经查阅资料,DAC0832需采用直通式,故,将DAC0832的控制语句直接写在了ADC0809的控制语句块内。

ile为输出到ADC0832的输入锁存允许信号,cont 为ADC0832WR1,WR2,CS等引脚。

Wendu为预设温度的输入引脚。

din为ADC0809转换后的输出信号,dout为受FPGA控制的输出到DAC0832的控制信号。

clk8为来自为频器的时钟信号。

根据ADC0809的时序图,总结出相应的状态转移图,一次来编写控制ADC0809的VHDL语言文件,状态转移图如下:具体波形仿真图如下:波形仿真建立在预设温度为38摄氏度的条件下。

前面提到,38摄氏度对应的ADC0809输出值为97,VHDL程序中设定,当ADC0809输入值大于或等于97时(当前温度大于或等于预设温度),FPGA输出到DAC0832的控制信号为0,即停止加热。

当ADC0809输入值小于92(即36摄氏度,与设定温度相差大于两度)时,FPGA 输出到DAC0832的控制信号为255,即以最大功率加热。

当ADC0809输入值小于92时,将会细分为5个阶段,即以逐次递减的功率加热。

由图可知,ADC0809工作正常。

统计报告图如下:ADC0809模块的VHDL仿真文件见附录3.最后,将三个模块运用元件例化语句连接在一块,并进行电路观察,生成相应的逻辑电路,如下图:总体波形仿真如下图波形分析:刚开始,FPGAjia置1,预设温度逐渐增加,如下图当温度到达38摄氏度后停止增加,即将38摄氏度作为预设温度,随后,观察FPGAin与FPGAout。

当预设温度为38摄氏度时,输入为97时,对应输出为0,当为92时,对应输出为5,当为96时,对应输出为1,当输入不在92-97之间,输入大于97时,输出为0,输入小与92时,输出为255.观察上图波形仿真,完全符合程序设计。

后面给FPGAjian置1,预设温度会随之降低。

统计报告图如下:总体的VHDL程序见附录4.附录1:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;entity fenpin isport(clk :in std_logic; --外部输入时钟源clk1: out std_logic);end fenpin; --分频后的时钟源architecture b of fenpin issignal count : std_logic_vector(7 downto 0); --信号定义signal clk2 : std_logic;beginprocess(clk)beginif(clk'event and clk='1') then --计数脉冲上升沿if(count="01000000") thencount<=(others=>'0');clk2<=not clk2; --当达到64个脉冲时count置0,clk2取反elsecount<=count+1; --未达到64脉冲时继续计数;end if;end if;clk1<=clk2; ——将产生的分频信号给输出端口end process;end b;附录2:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity jianpan isport(clk:in std_logic; --分频后的时钟输入shuru:in std_logic_vector(1 downto 0); --输入端,按键加0位,按键减1位zhi :out integer; --预设温度转化为ADC0809输出值xianshi :out integer); --当前预设温度end entity;architecture beha of jianpan issignal x:integer range 0 to 200; --定义信号beginprocess(clk)beginif(clk'event and clk='1') thencase shuru is --检测是否有输入when "01"=>x<=x+1; --按键加按下,温度+1when "10"=>if(x=0)then x<=0; --按键减按下,判断温度是否为0 else x<=x-1; --若为0,则依旧为0,否则,温度-1 end if;when others=>x<=x; --其他按键情况,温度不变end case;end if;xianshi<=x; --将温度赋给显示输出端zhi<=x*5*256/100/5; --将温度转化后赋给输出端end process;end beha;附录3:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity ADC0809 isport(din :in std_logic_vector(7 downto 0); --ADC0809输出的采样数据clk8 :in std_logic; --时钟信号eoc :in std_logic; --ADC0809转换结束指示,高电平有效ale :out std_logic; --ADC0809地址锁存次信号ile: out std_logic; --DAC0832数据锁存允许cont: out std_logic; --DAC0832控制信号(WR1,WR2,CS,Xfer)start :out std_logic; --ADC0809转换启动信号oe :out std_logic; --ADC0809数据输出允许信号wendu:in integer; --温度显示adda :out std_logic; --ADC0809信号通道控制位addb :out std_logic; --ADC0809信号通道控制位addc :out std_logic; --ADC0809信号通道控制位lock0 :out std_logic; --ADC0809观察数据锁存时钟dout :out std_logic_vector(7 downto 0)); --输出到DAC0832的8位数据end ADC0809;architecture beha of ADC0809 istype states is(st0,st1,st2,st3,st4); --定义ADC0809工作状态signal current_state,next_state:states:=st0; --定义信号signal regl :std_logic_vector(7 downto 0);signal shuchu :std_logic_vector(7 downto 0);signal lock :std_logic;signal count :std_logic_vector(7 downto 0);beginadda<='1'; --地址输入001,选择IN1 addb<='0';addc<='0';dout<=shuchu; -将处理后的数据传输到输出端口lock0<=lock; --数据传输ile<='1'; --DAC0832的控制信号cont<='0';com:process(current_state,eoc) --状态转移begincase current_state iswhen st0=>ale<='0';start<='0';lock<='0';oe<='0';next_state<=st1;when st1=>ale<='1';start<='1';lock<='0';oe<='0';next_state<=st2;when st2=>ale<='0';start<='0';lock<='0';oe<='0';next_state<=st1;if(eoc='1')then next_state<=st3;else next_state<=st2;end if;when st3=>ale<='0';start<='0';lock<='0';oe<='1';next_state<=st4;when st4=>ale<='0';start<='0';lock<='1';oe<='1';next_state<=st0;when others=>next_state<=st0;end case;end process com;reg:process(clk8)beginif(clk8'event and clk8='1')then current_state<=next_state; --在时钟上升沿改变状态end if;end process reg;latch1:process(lock)beginif lock='1'and lock'event then regl<=din; --将输入数据赋给中间变量end if;end process latch1;kongzhi:process(regl)beginif(regl<wendu) then --判断输入数据与预设温度的大小case wendu-regl is --判断输入数据与预设温度的when "00000101"=>shuchu<="00000101"; --差值为5时输出控制信号5when "00000100"=>shuchu<="00000100"; --差值为4时输出控制信号4when "00000011"=>shuchu<="00000011"; --差值为3时输出控制信号3when "00000010"=>shuchu<="00000010"; --差值为2时输出控制信号2when "00000001"=>shuchu<="00000001"; --差值为1时输出控制信号1when others=>shuchu<="11111111"; --差值大于5时输出255end case;else shuchu<="00000000"; --当前温度大于预设温度,输出0 end if;end process kongzhi;end beha;附录4:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity FPGA isport(clkin:in std_logic; --定义外部时钟端口FPGAeoc:in std_logic;FPGAin :in std_logic_vector(7 downto 0);FPGAout:out std_logic_vector(7 downto 0);FPGAale :out std_logic;FPGAjia :in std_logic;FPGAjian :in std_logic;FPGAwendu:out integer;FPGAile: out std_logic;FPGAcont: out std_logic;FPGAstart :out std_logic;FPGAoe :out std_logic;FPGAadda :out std_logic;FPGAaddb :out std_logic;FPGAaddc :out std_logic);end entity;architecture beha of FPGA iscomponent ADC0809 is --元件例化声明port(din :in std_logic_vector(7 downto 0);clk8 :in std_logic;eoc :in std_logic;ale :out std_logic;ile: out std_logic;cont: out std_logic;start :out std_logic;wendu:in integer;oe :out std_logic;adda :out std_logic;addb :out std_logic;addc :out std_logic;lock0 :out std_logic;dout :out std_logic_vector(7 downto 0));end component;component fenpin is --元件例化声明port(clk :in std_logic;clk1: out std_logic);end component;component jianpan isport(clk:in std_logic;shuru:in std_logic_vector(1 downto 0);zhi :out integer;xianshi:out integer);end component;signal c:std_logic; --定义中间变量signal n:integer;beginU0:fenpin port map(clk=>clkin,clk1=>c); --元件例化U1:ADC0809 port map(clk8=>c,wendu=>n,din=>FPGAin,eoc=>FPGAeoc,dout=>FPGAout,ale=>FPGAale,ile=>FP GAile,cont=>FPGAcont,start=>FPGAstart,oe=>FPGAoe,adda=>FPGAadda,addb=>FPGAaddb,addc=> FPGAaddc);U2:jianpan port map(clk=>c,shuru(1)=>FPGAjian,shuru(0)=>FPGAjia,zhi=>n,xianshi=>FPGAwendu);end beha;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;entity fenpin isport(clk :in std_logic; --外部输入时钟源clk1: out std_logic);end fenpin; --分频后的时钟源architecture b of fenpin issignal count : std_logic_vector(7 downto 0); --信号定义signal clk2 : std_logic;beginprocess(clk)beginif(clk'event and clk='1') then --计数脉冲上升沿if(count="01000000") thencount<=(others=>'0');clk2<=not clk2; -当达到64个脉冲时count置0,clk2取反elsecount<=count+1; --未达到64脉冲时继续计数;end if;end if;clk1<=clk2; ——将产生的分频信号给输出端口end process;end b;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity jianpan isport(clk:in std_logic; --分频后的时钟输入shuru:in std_logic_vector(1 downto 0); --输入端,按键加0位,按键减1位zhi :out integer; --预设温度转化为ADC0809输出值xianshi :out integer); --当前预设温度end entity;architecture beha of jianpan issignal x:integer range 0 to 200; --定义信号beginprocess(clk)beginif(clk'event and clk='1') thencase shuru is --检测是否有输入when "01"=>x<=x+1; --按键加按下,温度+1 when "10"=>if(x=0)then x<=0; --按键减按下,判断温度是否为0 else x<=x-1; --若为0,则依旧为0,否则,温度-1 end if;when others=>x<=x; --其他按键情况,温度不变end case;end if;xianshi<=x; --将温度赋给显示输出端zhi<=x*5*256/100/5; --将温度转化后赋给输出端end process;end beha;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity ADC0809 isport(din :in std_logic_vector(7 downto 0); --ADC0809输出的采样数据clk8 :in std_logic; --时钟信号eoc :in std_logic; --ADC0809转换结束指示,高电平有效ale :out std_logic; --ADC0809地址锁存次信号ile: out std_logic; --DAC0832数据锁存允许cont: out std_logic; --DAC0832控制信号(WR1,WR2,CS,Xfer)start :out std_logic; --ADC0809转换启动信号oe :out std_logic; --ADC0809数据输出允许信号wendu:in integer; --温度显示adda :out std_logic; --ADC0809信号通道控制位addb :out std_logic; --ADC0809信号通道控制位addc :out std_logic; --ADC0809信号通道控制位lock0 :out std_logic; --ADC0809观察数据锁存时钟dout :out std_logic_vector(7 downto 0)); --输出到DAC0832的8位数据end ADC0809;architecture beha of ADC0809 istype states is(st0,st1,st2,st3,st4); --定义ADC0809工作状态signal current_state,next_state:states:=st0; --定义信号signal regl :std_logic_vector(7 downto 0);signal shuchu :std_logic_vector(7 downto 0);signal lock :std_logic;signal count :std_logic_vector(7 downto 0);beginadda<='1'; --地址输入001,选择IN1 addb<='0';addc<='0';dout<=shuchu; --将处理后的数据传输到输出端口lock0<=lock; --数据传输ile<='1'; --DAC0832的控制信号cont<='0';com:process(current_state,eoc) --状态转移begincase current_state iswhen st0=>ale<='0';start<='0';lock<='0';oe<='0';next_state<=st1;when st1=>ale<='1';start<='1';lock<='0';oe<='0';next_state<=st2;when st2=>ale<='0';start<='0';lock<='0';oe<='0';next_state<=st1;if(eoc='1')then next_state<=st3;else next_state<=st2;end if;when st3=>ale<='0';start<='0';lock<='0';oe<='1';next_state<=st4;when st4=>ale<='0';start<='0';lock<='1';oe<='1';next_state<=st0;when others=>next_state<=st0;end case;end process com;reg:process(clk8)beginif(clk8'event and clk8='1')then current_state<=next_state; --在时钟上升沿改变状态end if;end process reg;latch1:process(lock)beginif lock='1'and lock'event then regl<=din; --将输入数据赋给中间变量end if;end process latch1;kongzhi:process(regl)beginif(regl<wendu) then --判断输入数据与预设温度的大小case wendu-regl is --判断输入数据与预设温度的when "00000101"=>shuchu<="00000101"; --差值为5时输出控制信号5when "00000100"=>shuchu<="00000100"; --差值为4时输出控制信号4when "00000011"=>shuchu<="00000011"; --差值为3时输出控制信号3when "00000010"=>shuchu<="00000010"; --差值为2时输出控制信号2when "00000001"=>shuchu<="00000001"; --差值为1时输出控制信号1when others=>shuchu<="11111111"; --差值大于5时输出255end case;else shuchu<="00000000"; --当前温度大于预设温度,输出0 end if;end process kongzhi;end beha;。