海思芯片TC 测试技术规范

5g核心芯片及器件测试标准

5g核心芯片及器件测试标准

目前,对5G核心芯片及器件的测试标准主要包括以下几个方面:

1. 无线通信性能测试标准:包括功率输出、接收灵敏度、信号质量、频率稳定性、调制解调等

性能指标的测试。

2. 时延性能测试标准:对5G核心芯片及器件的时延进行测试,包括用户面时延、控制面时延等。

3. 功耗测试标准:对5G核心芯片及器件的功耗进行测试,包括待机功耗、通信功耗、功耗管

理等。

4. 安全性能测试标准:对5G核心芯片及器件的安全性能进行测试,包括加密算法、认证协议、数据完整性等方面的测试。

5. 热失效测试标准:对5G核心芯片及器件的温度、湿度等环境因素下的热老化及失效进行测试。

6. 可靠性测试标准:对5G核心芯片及器件的可靠性进行测试,包括震动、冲击、振动等环境

因素下的可靠性测试。

7. 兼容性测试标准:对5G核心芯片及器件的兼容性进行测试,包括对不同网络制式、不同运

营商网络等的兼容性测试。

以上只是对5G核心芯片及器件测试标准的一些主要方面进行了简要介绍,实际测试中还会涉

及到更多细节和具体指标。

不同国家、地区和组织可能会有不同的测试标准和要求。

IC芯片IQC来料检验作业指导书

将元器件在规格书规定的最高温环境下,放置 48h 后, 取出在常态(温度 25±3℃ 湿度 40-80%)下恢复 2h。 将元器件放在-25±5℃低温环境中放置 48h,取出充分除 去表面水滴并在常态(温度 25±3℃ 湿度 40-80%)下 恢复 2h 后

芯片无击穿,电性能符合产品规格书要求。 须提供第三方静电测试报告

用静电测试仪在芯片名引脚空气放电打 8KV 测试 ★★整机匹配 对应型号样品装入对应的整机老化至少 2 小时,要求无异常

整机

8

有害物质

ROHS 测试 按《电磁炉公司 ROHS 物料检验流程》标准执行

REACH 评估 供应商提供第三方 RECH 检测报告及提供声明函

电子元器件评价检验标准

物料类别

名

称

IC 芯片

序号

类别

检验项目

1

外观

外观质量

2

尺寸 外形尺寸

功能

3

电气性能 V/I 特性

Mos 管耐压

技术要求

检验方法

1.封体光洁,无毛刺及缺损。2.引脚牢固,光亮笔直,无机械伤痕,变形等缺陷。(报告中标示清楚封装地, 本体标示))

2.核对样品,表面丝印要与样品相符,用沾水的擦 15s 仍清晰完整。

高温箱 低温箱

★冷热循环

外观无可见损伤,电性能测试应符合产品规格书 要求。进行声扫,芯片里面不允许有异物,杂质

将元器件放在-40~150℃环境中各保持 0.5h,关键元器件 要求 100 循环,取出充分除去表面水滴并在常态(温度 25±3℃ 湿度 40-80%)下恢复 2h 后

冷热冲击试验 仪

6

静电试验 ★★静电测试

SOC芯片测试要求

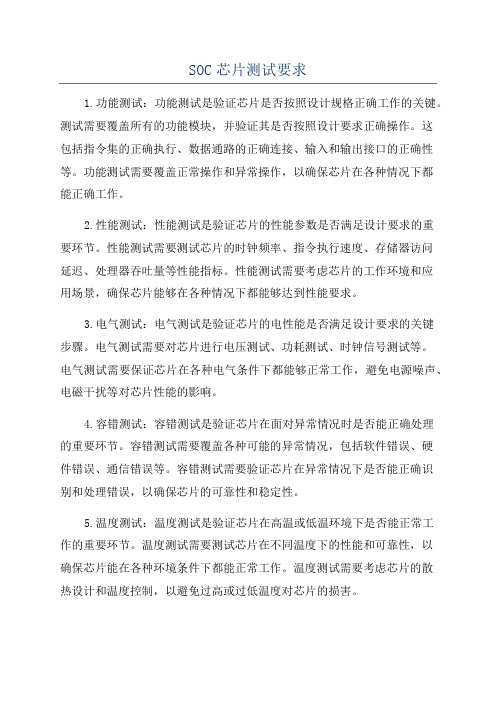

SOC芯片测试要求1.功能测试:功能测试是验证芯片是否按照设计规格正确工作的关键。

测试需要覆盖所有的功能模块,并验证其是否按照设计要求正确操作。

这包括指令集的正确执行、数据通路的正确连接、输入和输出接口的正确性等。

功能测试需要覆盖正常操作和异常操作,以确保芯片在各种情况下都能正确工作。

2.性能测试:性能测试是验证芯片的性能参数是否满足设计要求的重要环节。

性能测试需要测试芯片的时钟频率、指令执行速度、存储器访问延迟、处理器吞吐量等性能指标。

性能测试需要考虑芯片的工作环境和应用场景,确保芯片能够在各种情况下都能够达到性能要求。

3.电气测试:电气测试是验证芯片的电性能是否满足设计要求的关键步骤。

电气测试需要对芯片进行电压测试、功耗测试、时钟信号测试等。

电气测试需要保证芯片在各种电气条件下都能够正常工作,避免电源噪声、电磁干扰等对芯片性能的影响。

4.容错测试:容错测试是验证芯片在面对异常情况时是否能正确处理的重要环节。

容错测试需要覆盖各种可能的异常情况,包括软件错误、硬件错误、通信错误等。

容错测试需要验证芯片在异常情况下是否能正确识别和处理错误,以确保芯片的可靠性和稳定性。

5.温度测试:温度测试是验证芯片在高温或低温环境下是否能正常工作的重要环节。

温度测试需要测试芯片在不同温度下的性能和可靠性,以确保芯片能在各种环境条件下都能正常工作。

温度测试需要考虑芯片的散热设计和温度控制,以避免过高或过低温度对芯片的损害。

6.可靠性测试:可靠性测试是验证芯片在长时间工作条件下是否能保持稳定和可靠的关键步骤。

可靠性测试需要对芯片进行加速寿命测试、高温老化测试、电磁干扰测试等,以验证芯片的可靠性和耐久性。

可靠性测试需要模拟芯片在实际应用中的工作条件,并测试其在不同工作条件下的稳定性和可靠性。

综上所述,SOC芯片测试要求包括功能测试、性能测试、电气测试、容错测试、温度测试和可靠性测试等。

通过全面、系统地测试和验证,确保芯片具有稳定、高效、可靠的性能,满足用户的需求。

关于measureThresh参数的技术通告

关于measureThresh参数的技术通告

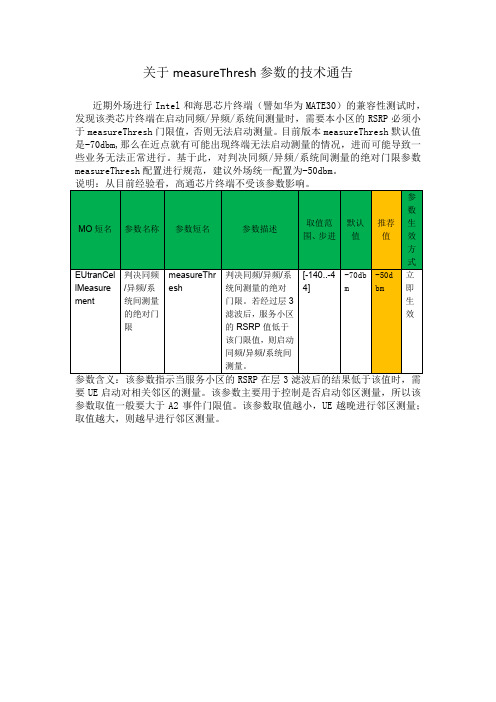

近期外场进行Intel和海思芯片终端(譬如华为MATE30)的兼容性测试时,发现该类芯片终端在启动同频/异频/系统间测量时,需要本小区的RSRP必须小于measureThresh门限值,否则无法启动测量。

目前版本measureThresh默认值是-70dbm,那么在近点就有可能出现终端无法启动测量的情况,进而可能导致一些业务无法正常进行。

基于此,对判决同频/异频/系统间测量的绝对门限参数measureThresh配置进行规范,建议外场统一配置为-50dbm。

要UE启动对相关邻区的测量。

该参数主要用于控制是否启动邻区测量,所以该参数取值一般要大于A2事件门限值。

该参数取值越小,UE越晚进行邻区测量;取值越大,则越早进行邻区测量。

measureThresh参数网管修改路径:无线参数->LTE FDD -> E-UTRAN FDD 小区->测量参数->measureThresh

网管操作指引:。

tc8测试标准

tc8测试标准

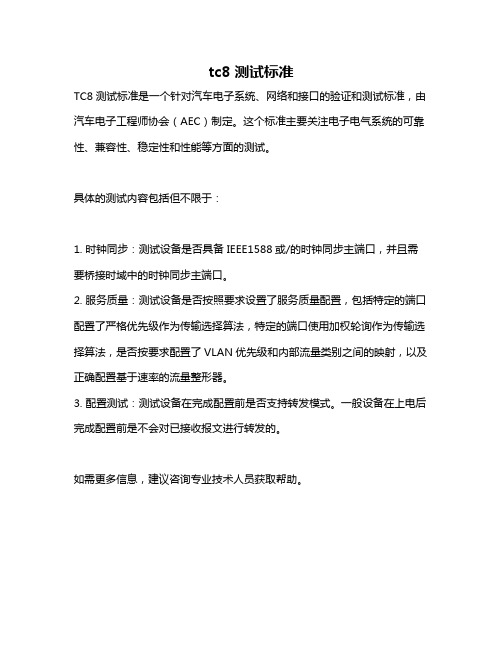

TC8测试标准是一个针对汽车电子系统、网络和接口的验证和测试标准,由汽车电子工程师协会(AEC)制定。

这个标准主要关注电子电气系统的可靠性、兼容性、稳定性和性能等方面的测试。

具体的测试内容包括但不限于:

1. 时钟同步:测试设备是否具备IEEE1588或/的时钟同步主端口,并且需要桥接时域中的时钟同步主端口。

2. 服务质量:测试设备是否按照要求设置了服务质量配置,包括特定的端口配置了严格优先级作为传输选择算法,特定的端口使用加权轮询作为传输选择算法,是否按要求配置了VLAN优先级和内部流量类别之间的映射,以及正确配置基于速率的流量整形器。

3. 配置测试:测试设备在完成配置前是否支持转发模式。

一般设备在上电后完成配置前是不会对已接收报文进行转发的。

如需更多信息,建议咨询专业技术人员获取帮助。

集成电路的质量标准及检验方法

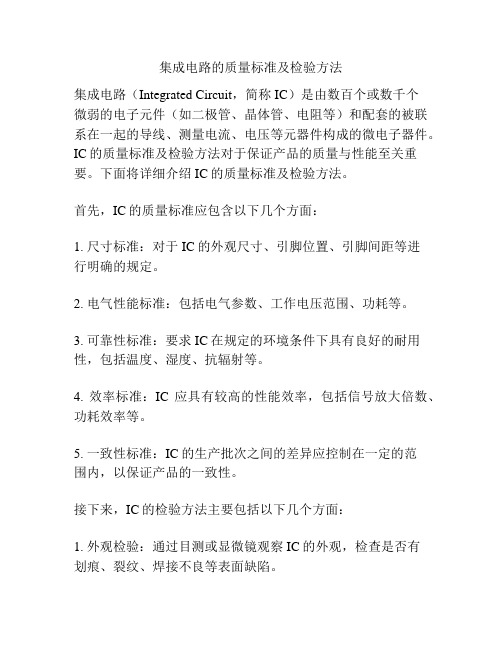

集成电路的质量标准及检验方法集成电路(Integrated Circuit,简称IC)是由数百个或数千个微弱的电子元件(如二极管、晶体管、电阻等)和配套的被联系在一起的导线、测量电流、电压等元器件构成的微电子器件。

IC的质量标准及检验方法对于保证产品的质量与性能至关重要。

下面将详细介绍IC的质量标准及检验方法。

首先,IC的质量标准应包含以下几个方面:1. 尺寸标准:对于IC的外观尺寸、引脚位置、引脚间距等进行明确的规定。

2. 电气性能标准:包括电气参数、工作电压范围、功耗等。

3. 可靠性标准:要求IC在规定的环境条件下具有良好的耐用性,包括温度、湿度、抗辐射等。

4. 效率标准:IC应具有较高的性能效率,包括信号放大倍数、功耗效率等。

5. 一致性标准:IC的生产批次之间的差异应控制在一定的范围内,以保证产品的一致性。

接下来,IC的检验方法主要包括以下几个方面:1. 外观检验:通过目测或显微镜观察IC的外观,检查是否有划痕、裂纹、焊接不良等表面缺陷。

2. 引脚间距检验:使用千分尺或显微镜测量IC引脚之间的间距是否符合规范要求。

3. 电性能检验:使用特定的测试仪器,通过量测IC在不同电压下的电流、电压等参数来判断IC的电性能是否符合标准要求。

4. 可靠性检验:将IC置于不同的环境条件下,例如高温、低温、高湿度等,观察其性能是否受到影响以及是否满足可靠性要求。

5. 一致性检验:通过对生产批次中的多个IC进行抽样测试,对比其性能参数,判断是否在规定的一致性范围内。

6. 功能检验:根据IC所设计的功能,通过电路连接和信号输入,观察IC的功能是否正常。

总结:IC作为重要的电子元件,其质量标准及检验方法直接关系到电子产品的品质与性能。

通过明确的质量标准,可以确保IC 在制造过程中符合规范要求;通过有效的检验方法,可以及时发现IC的缺陷,并采取相应措施进行修正或淘汰。

因此,合理制定和实施IC的质量标准及检验方法是保证IC产品质量的重要保证。

海思消费类芯片可靠性测试技术总体规范V2.0

可靠性测试技术总体规范V2.0拟制:审核:批准:历史版本记录适用范围:本规范规定了芯片可靠性测试的总体规范要求,包括电路可靠性、封装可靠性。

适用于量产芯片验证测试阶段的通用测试需求,能够覆盖芯片绝大多数的可靠性验证需求。

具体的执行标准可能不是本规范文档,但来源于该规范。

本规范描述的测试组合可能不涵盖特定芯片的所有使用环境,但可以满足绝大多数芯片的通用验证需求。

简介:本标准规定芯片研发或新工艺升级时,芯片规模量产前对可靠性相关测试需求的通用验收基准。

这些测试或测试组合能够激发半导体器件电路、封装相关的薄弱环节或问题,通过失效率判断是否满足量产出口标准。

相比正常使用场景,该系列测试或测试组合通常以特定的温度、湿度、电压加速的方式来激发问题。

引用文件:下列文件中的条款通过本规范的引用而成为本规范的条款。

凡是注日期的引用文件,其随后所有的修改单(不包括勘误的内容)或修订版均不适用于本规范,然而,鼓励根据本规范达成协议的各方研究是否可使用这些文件的最新版本。

凡是不注日期的引用文件,其最新版本适用于本规范。

1.可靠性概念范畴“可靠性”是一个含义广泛的概念,以塑封芯片为例,狭义的“可靠性”一般芯片级可靠性,包括电路相关的可靠性(ESD、Latch-up、HTOL)和封装相关的可靠性(PC、TCT、HTSL、HAST等)。

但是芯片在应用场景中往往不是“独立作战”,而是以产品方案(PCB板上的一个元器件)作为最终应用。

因此广义的“可靠性”还包括产品级的可靠性,例如上电温循试验就是用来评估芯片各内部模块及其软件在极端温度条件下运行的稳定性,产品级的可靠性根据特定产品的应用场景来确定测试项和测试组合,并没有一个通用的规范。

本规范重点讲述芯片级可靠性要求。

2.通用芯片级可靠性测试要求2.1 电路可靠性测试High Temperature Operating Life JESD22-A108,JESD85HTOLT≥ 125℃Vcc ≥ Vccmax3 Lots/77 units1000 hrs/ 0 FailEarly Life FailureRate JESD22-A108,JESD74ELFRT≥ 125℃Vcc ≥ VccmaxSee ELFR Table48 ≤ t ≤ 168 hrs RLow Temperature Operating Life JESD22-A108LTOLT≤ 50℃Vcc ≥ Vccmax1 Lot/32 units1000 hrs/0 Fail CHigh TemperatureStorage LifeJESD22-A103HTSL T≥ 150 °C 3 Lots/45 units1000 hrs/0 Fail Electrical ParameterAssessmentJESD86ED Datasheet 3 Lots/10 units T per datasheet RLatch-Up JESD78LU Class I orClass II1 Lot/3 units0 FailHuman Body ModelESDJS-001ESD-HBM T = 25 °C 3 units ClassificationCharged Device Model ESD JS-002ESD-CDM T = 25 °C3Stress Ref.Abbv.ConditionsRequirements Required (R)/Considered (C) #Lots/SS per Lot Duration/AcceptRRRRR3units ClassificationAccelerated Soft Error Testing JESD89-2,JESD89-3ASER T = 25 °C 3 units Classification C“OR” System Soft Error Testing JESD89-1SSER T = 25 °CMinimum of 1E+06Device Hrs or 10 fails.Classification CJJJAAAAAA12注1:ELFR可包含在HTOL测试中,HTOL测试会在168h回测,作为评估早期失效率的重要判据。

海思芯片HTOL老化测试技术规范

HTOL测试技术规范拟制:克鲁鲁尔审核:批准:历史版本记录适用范围:该测试它以电压、温度拉偏方式,加速的方式模拟芯片的运行状况,用于芯片寿命和长期上电运行的可靠性评估。

本规范适用于量产芯片验证测试阶段的HTOL老化测试需求。

简介:HTOL(High Temperature Operating Life)测试是芯片电路可靠性的一项关键性的基础测试,它用应力加速的方式模拟芯片的长期运行,以此评估芯片寿命和长期上电运行的可靠性,通常称为老化测试。

本规范介绍DFT和EVB两种模式的HTOL测试方法,HTOL可靠性测试工程师需要依据实际情况选择合适的模式完成HTOL测试。

引用文件:下列文件中的条款通过本规范的引用而成为本规范的条款。

凡是注日期的引用文件,其随后所有的修改单(不包括勘误的内容)或修订版均不适用于本规范,然而,鼓励根据本规范达成协议的各方研究是否可使用这些文件的最新版本。

凡是不注日期的引用文件,其最新版本适用于本规范。

1. 测试流程1.1 HTOL测试概要HTOL主要用于评估芯片的寿命和电路可靠性,需要项目SE、封装工程师、可靠性工程师、硬件工程师、FT测试工程师共同参与,主要工作包括:HTOL向量、HTOL测试方案、HTOL环境调试、HTOL测试流程执行、测试结果分析、失效定位等。

HTOL可以用两种方式进行测试:DFT测试模式和EVB测试模式。

1.2 DFT和EVB模式对比DFT(Design For Testability)测试模式:集成度较高的IC一般有DFT设计,其HTOL模式一般在DFT测试模式下进行,以扫描链、内建BIST、内部环回、JTAG,实现内部逻辑的翻转、读写、自测试和IO的翻转等,其数字逻辑、memory、IP、IO的以串行方式运行。

EVB(Evaluation Board)功能模式:即正常应用模式,HTOL也可以在该模式下更符合实际应用场景,该模式下芯片各模块一般按照真实的应用场景并行运行。

开关电源芯片通用测试要求和步骤-antonychen概论

开关电源芯片通用测试要求和步骤By Antony Chen开关电源必须通过一系列的测试,使其符合所有功能规格、保护特性、安规(如UL、CSA、VDE、DEMKO、SEMKO,长城等之耐压、抗燃、漏电流、接地等安全规格)、电磁兼容(如FCC、CE等之传导与幅射干扰)、可靠性(如老化寿命测试)、及其他特定要求等。

测试开关电源是否通过设计指标,需要各种精密的电子设备去模拟电源在各种环境下实际工作中的性能。

一、理论上的DCDC测试指标清单1.描述输入电压影响输出电压的几个指标形式(line)1.1绝对稳压系数:K=△Uo/△Ui1.2相对稳压系数:S=△Uo/Uo / △Ui/Ui1.3电网调整率(也称线性调整率):它表示输入电网电压由额定值变化+-10%时,稳压电源输出电压的相对变化量,有时也以绝对值表示。

line reg=△Uo/Uo*100%@ -10%<Ui<+10%1.4电压稳定度:负载电流保持为额定范围内的任何值,输入电压在规定的范围内变化所引起的输出电压相对变化△Uo/Uo(百分值),称为稳压器的电压稳定度。

STB=△Uo/Uo*100%@ 0<I load<max2.负载对输出电压影响的几种指标形式(load)2.1负载调整率(也称电流调整率)在额定电网电压下,负载电流从零变化到最大时,输出电压的最大相对变化量,常用百分数表示,有时也用绝对变化量表示。

2.2输出电阻(也称等效内阻或内阻)在额定电网电压下,由于负载电流变化△IL 引起输出电压变化△Uo,则输出电阻为Ro=|△Uo/△IL|Ω3.纹波电压的几个指标形式(ripple)3.1最大纹波电压在额定输出电压和负载电流下,输出电压的纹波(包括噪声)的绝对值的大小,通常以峰峰值或有效值表示。

V ripple=V MAX-V MIN3.2纹波系数Y(%)在额定负载电流下,输出纹波电压的有效值Urms 与输出直流电压Uo 之比,即Y=Umrs/Uo x100%3.3纹波电压抑制比(PSRR:Power Supply Rejection Ratio)在规定的纹波频率(例如50HZ)下,输入电压中的纹波电压Ui~与输出电压中的纹波电压Uo~之比,即:纹波电压抑制比=Ui~/Uo~ 。

ic认证 测试项目

ic认证测试项目IC认证测试项目IC认证是指集成电路认证,是国家对集成电路产品进行质量和安全评估的一项认证制度。

IC认证测试项目是指在进行IC认证前需要进行的测试项目,以确保集成电路产品符合国家相关技术规范和标准。

本文将详细介绍IC认证测试项目的内容和要求。

一、物理性能测试物理性能测试是对集成电路产品的外观、尺寸、材质等进行测试和评估。

测试项目包括但不限于外观检查、尺寸测量、材质分析等。

外观检查主要是检查集成电路产品的表面是否存在明显的划痕、破损、氧化等问题;尺寸测量是对集成电路产品的尺寸进行测量,确保其符合相关标准要求;材质分析是对集成电路产品的材质进行分析,检测是否存在禁用物质等。

二、电气性能测试电气性能测试是对集成电路产品的电气性能进行测试和评估。

测试项目包括但不限于电压测试、电流测试、功耗测试、温度测试等。

电压测试是对集成电路产品的电压参数进行测试,确保其在正常工作范围内;电流测试是对集成电路产品的电流参数进行测试,确保其在正常工作范围内;功耗测试是对集成电路产品的功耗进行测试,确保其符合相关要求;温度测试是对集成电路产品的工作温度进行测试,确保其能在规定的温度范围内正常工作。

三、功能性能测试功能性能测试是对集成电路产品的功能进行测试和评估。

测试项目根据产品的具体功能而定,包括但不限于输入输出测试、通信测试、运算测试等。

输入输出测试是对集成电路产品的输入输出接口进行测试,确保其能正常连接和传输数据;通信测试是对集成电路产品的通信功能进行测试,确保其能正常与其他设备进行通信;运算测试是对集成电路产品的运算功能进行测试,确保其能正常进行计算和处理。

四、可靠性测试可靠性测试是对集成电路产品的可靠性进行测试和评估。

测试项目包括但不限于温度循环测试、湿热循环测试、振动测试、冲击测试等。

温度循环测试是对集成电路产品在不同温度条件下的可靠性进行测试,模拟产品在不同环境下的工作情况;湿热循环测试是对集成电路产品在高温高湿条件下的可靠性进行测试,模拟产品在潮湿环境下的工作情况;振动测试是对集成电路产品在振动环境下的可靠性进行测试,模拟产品在运动中的工作情况;冲击测试是对集成电路产品在冲击环境下的可靠性进行测试,模拟产品在受到冲击时的工作情况。

海思终端芯片ATE技术手册

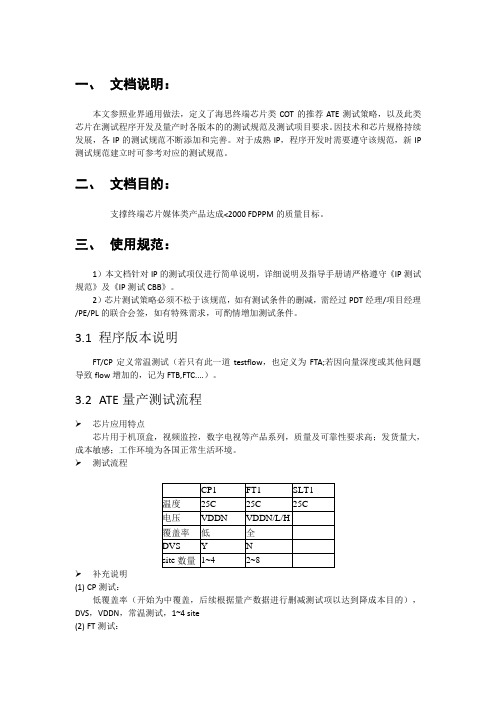

一、文档说明:本文参照业界通用做法,定义了海思终端芯片类COT的推荐ATE测试策略,以及此类芯片在测试程序开发及量产时各版本的的测试规范及测试项目要求。

因技术和芯片规格持续发展,各IP的测试规范不断添加和完善。

对于成熟IP,程序开发时需要遵守该规范,新IP 测试规范建立时可参考对应的测试规范。

二、文档目的:支撑终端芯片媒体类产品达成<2000 FDPPM的质量目标。

三、使用规范:1)本文档针对IP的测试项仅进行简单说明,详细说明及指导手册请严格遵守《IP测试规范》及《IP测试CBB》。

2)芯片测试策略必须不松于该规范,如有测试条件的删减,需经过PDT经理/项目经理/PE/PL的联合会签,如有特殊需求,可酌情增加测试条件。

3.1 程序版本说明FT/CP定义常温测试(若只有此一道testflow,也定义为FTA;若因向量深度或其他问题导致flow增加的,记为FTB,FTC....)。

3.2 ATE量产测试流程➢芯片应用特点芯片用于机顶盒,视频监控,数字电视等产品系列,质量及可靠性要求高;发货量大,成本敏感;工作环境为各国正常生活环境。

➢测试流程➢补充说明(1)CP测试:低覆盖率(开始为中覆盖,后续根据量产数据进行删减测试项以达到降成本目的),DVS,VDDN,常温测试,1~4 site(2)FT测试:全覆盖,VDDN+VDDH+VDDL,常温测试(高温待验证必要性),GB(根据CHAR结果),2~ 8sites。

(3)量产SLT:可选项,长期可根据ATE覆盖率更新情况进行抽检或取消。

(4)可靠性测试:建议By wafer lot进行HTOL/uHAST抽检3.3 测试项目标准ATE向量规格要求如下:ATE向量规格要求(CP_FT).xlsx3.4 降成本策略当量产程序稳定后,即可开始量产测试降成本工作,降成本细节请参考《海思COT芯片ATE测试降成本规范》,本文仅针对无线终端芯片进行策略性指导。

micro tec 验收标准

micro tec 验收标准

对于Micro TEC(微电子技术)的验收标准,具体的要求和标准会根据具体的项目和应用而有所不同。

微电子技术是一个涉及到微观尺度的电子工艺和器件领域,常见的应用包括芯片制造、集成电路设计等。

一般而言,Micro TEC的验收标准可能包括以下方面:

1. 规格和要求:验证设备或产品是否符合规定的规格和要求,例如尺寸、结构、电性能等。

2. 工艺流程:对于微电子工艺,验证工艺流程是否正常,工艺步骤是否按照要求进行。

3. 器件特性:验证微电子器件的特性参数是否在设定范围内,例如电阻值、电容值、传输特性等。

4. 质量控制:检查生产过程中的质量控制措施是否到位,例如实验室条件、设备校准等。

5. 可靠性测试:对于微电子产品,可能需要进行可靠性测试,包括温度循环测试、湿热测试、电热老化等,以验证产品在各种环境下的稳定性和可靠性。

6. 器件标识和追溯:对于微电子器件,可能需要验证标识和追溯体系是否完善,以确保产品的追溯和溯源能力。

以上仅为一般性的参考,具体的验收标准需要根据具体项目和应用场景进行制定。

建议在进行Micro TEC验收时,参考所涉及的技术标准、行业规范以及产品设计要求,以确保满足项目的需求和要求。

海思HAST 测试技术规范V1

HAST(Highly Accelerated Temperature and Humidity Stress Test)测试技术规范VL2拟制:审核:批准:日期:2023-6-12历史版本记录适用范围:该试验检查芯片长期贮存条件下,高温和时间对器件的影响。

木规范适用于量产芯片验证测试阶段的HAST测试需求,仅针对非密封封装(塑料封装),带偏置(bHAST)和不带偏置QHAST)的测试。

简介:该试验通过温度、湿度、大气压力加速条件,评估非密封封装器件在上电状态下,在高温、高压、潮湿环境中的可靠性。

它采用了严格的温度,湿度,大气压、电压条件,该条件会加速水分渗透到材料内部与金属导体之间的电化学反应。

引用文件:下列文件中的条款通过本规范的引用而成为本规范的条款。

凡是注日期的引用文件,其随后所有的修改单(不包括勘误的内容)或修订版均不适用于本规范,然而,鼓励根据本规范达成协议的各方研究是否可使用这些文件的最新版本。

凡是不注日期的引用文件,其最新版本适用于本规范。

1. HAST 测试流程2. HAST 测试条件2.1 温度、湿度、气压、测试时间HAST 试验条件如下表所示:> 通常选择HAST-96,即:130℃、85%RH 、230KPa 大气压,96hour 测试时间。

>测试过程中,建议调试阶段监控芯片壳温、功耗数据推算芯片结温,要保证结温不能过 高,并在测试过程中定期记录。

结温推算方法参考《HTOL 测试技术规范》。

> 如果壳温与环温差值或者功耗满足下表三种关系时,特别是当壳温与环温差值超过10℃时,需考虑周期性的电压拉偏策略。

2.1.1 Choosing and reportingCriteria for choosing continuous or cyclical bias, and whether or not to report the amount by which the die temperature exceeds the chamber ambient temperature, arc summarized in the following table:> 注意测试起始时间是从环境条件达到规定条件后开始计算;结束时间为开始降温降压操 作的时间点。

海思芯片PC 测试技术规范

海思PC(Preconditioning)测试技术规范拟制:克鲁鲁尔审核:批准:日期:2019-11-09历史版本记录适用范围:该测试用来评估芯片在包装、运输、焊接过程中对温度、湿度冲击的抗性。

本规范适用于量产芯片验证测试阶段的PC(Preconditioning)测试需求,仅对非封闭的封装(塑料封装)芯片约束。

简介:表面贴器件会在焊接过程经受高温,该高温过程或导致内部水汽损坏电路。

PC预处理测试用于在可靠性测试之前模拟器件焊接过程。

PC预处理测试是芯片进行部分封装可靠性测试前要求进行的测试,这类可靠性测试的样品要求以符合本规范的PC测试为入口条件。

引用文件:下列文件中的条款通过本规范的引用而成为本规范的条款。

凡是注日期的引用文件,其随后所有的修改单(不包括勘误的内容)或修订版均不适用于本规范,然而,鼓励根据本规范达成协议的各方研究是否可使用这些文件的最新版本。

凡是不注日期的引用文件,其最新版本适用于本规范。

1. Precondition 测试流程1.1 要求PC 预处理的可靠性测试要求在先做PC 预处理测试的可靠性测试项:THB 、HAST 、TC 、AC 、UHAST 。

其中,一般HAST 、TC 是必做的。

1.2 测试流程1.2.1 完整流程冷却15min~4hours失效分析BGA\CGA\LGA 封装不做要求HAST TC AC THB1.2.2 规范流程表1.2.3 简化流程(推荐)步骤事项详细描述1 外观检查检查外观,排除封装、管脚有缺陷的芯片2 功能\ATE筛片筛选功能、性能正常芯片3 烘烤125℃烘烤24h4 潮敏处理13级潮敏处理:30℃, 60%RH存储192h。

潮敏处理后须室温冷却最低15min但不超4hour。

5 回流焊23次;回流焊的升温曲线、峰值温度须符合附1、附3的要求或符合《J-STD-020E》标准。

每次回流焊须冷却≥15min。

6 浸润活化水溶性助焊剂浸润10s。

芯片可靠性测试要求及标准解析

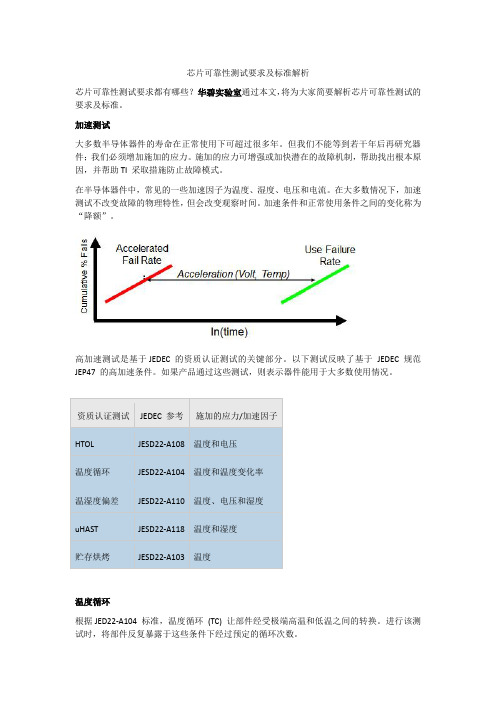

芯片可靠性测试要求及标准解析芯片可靠性测试要求都有哪些?华碧实验室通过本文,将为大家简要解析芯片可靠性测试的要求及标准。

加速测试大多数半导体器件的寿命在正常使用下可超过很多年。

但我们不能等到若干年后再研究器件;我们必须增加施加的应力。

施加的应力可增强或加快潜在的故障机制,帮助找出根本原因,并帮助TI 采取措施防止故障模式。

在半导体器件中,常见的一些加速因子为温度、湿度、电压和电流。

在大多数情况下,加速测试不改变故障的物理特性,但会改变观察时间。

加速条件和正常使用条件之间的变化称为“降额”。

高加速测试是基于JEDEC 的资质认证测试的关键部分。

以下测试反映了基于JEDEC 规范JEP47 的高加速条件。

如果产品通过这些测试,则表示器件能用于大多数使用情况。

温度循环根据JED22-A104 标准,温度循环(TC) 让部件经受极端高温和低温之间的转换。

进行该测试时,将部件反复暴露于这些条件下经过预定的循环次数。

高温工作寿命(HTOL)HTOL 用于确定高温工作条件下的器件可靠性。

该测试通常根据JESD22-A108 标准长时间进行。

温湿度偏压高加速应力测试(BHAST)根据JESD22-A110 标准,THB 和BHAST 让器件经受高温高湿条件,同时处于偏压之下,其目标是让器件加速腐蚀。

THB 和BHAST 用途相同,但BHAST 条件和测试过程让可靠性团队的测试速度比THB 快得多。

热压器/无偏压HAST热压器和无偏压HAST 用于确定高温高湿条件下的器件可靠性。

与THB 和BHAST 一样,它用于加速腐蚀。

不过,与这些测试不同,不会对部件施加偏压。

高温贮存HTS(也称为“烘烤”或HTSL)用于确定器件在高温下的长期可靠性。

与HTOL 不同,器件在测试期间不处于运行条件下。

静电放电(ESD)静电荷是静置时的非平衡电荷。

通常情况下,它是由绝缘体表面相互摩擦或分离产生;一个表面获得电子,而另一个表面失去电子。

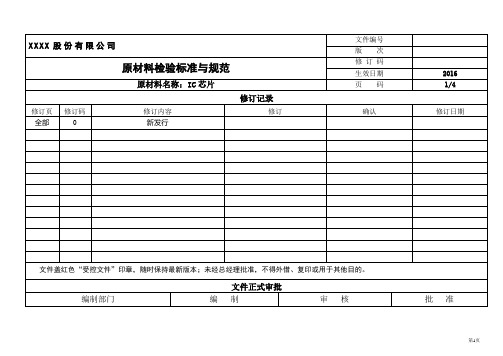

IC芯片检验标准与规范

文件编号

版 次

原材料检验标准与规范

修 订 码

生效日期

2016

原材料名称:IC芯片

页 码

1/4

修订记录

修订页

修订码

修订内容

修订

确认

修订日期

全部

0

新发行

文件盖红色“受控文件”印章,随时保持最新版本;未经总经理批准,不得外借、复印或用于其他目的。

文件正式审批

编制部门

编 制

审 核

批 准

品质部

4整齐成直线无弯曲现象引脚灰暗有氧化现象且排列不整齐有弯曲现象v10以上视力静电环尺寸本体一般抽样用卡尺测得主体长宽高或与样品对比主体长宽高应符合装配或样品要求主体长宽咼应不符合装配或样品要求v卡尺静电环引脚一般抽样用卡尺测得引脚长宽高及间距或样品对比引脚长宽高及间距符合装配或样品要求弓1脚长宽咼及间距不符合装配或样品要求v卡尺静电环匹配试验12pcs将ic芯片试装于所使用的pcb板中与pcb板完全匹配与pcb不匹配或很难装入vpcb板静电环xxxx股份有限公司文件编号版次原材料检验标准与规范修订码生效日期2016原材料名称

4.3环境管理物质检验:

4.3.1环境管理物质管控项目:环境管理物质管控项目:RoHS、PAHS、PHTS、SVHC、无卤素等(客户有要求时管控)

4.3.2 ROHS六项检验:每批来料抽取足量样品送XRF检测,XRF检测结果判定依亿邦公司XRF限值标准进行判定.

4.3.3环境管理物质管控:供应商向我司签定环保协议书,提供权威性第三方检测机构出具之检测报告,亿邦公司要求检测报告有效期为一年,并通过我司综合评估,符合我司环保合格供应商标准要求,列入亿邦公司合格环保供应商名录;来料检验时,供应商若不属于环保合格供商名录则CRI判定处理。。

TC 检测方法简介

IPC-TM-650 测试方法手册编号:2.6.26目的:直流热循环测试生成日期:99.111.0 概述:此项测试测量PCB板通孔孔壁和孔和内层连接在热循环下的电阻的变化,应用特定设计的测试COUPON进行相应的测试。

该测试技术通过在特定的科邦的内层和通孔的连接回路上通3分钟的直流电,使被测COUPON测试区的温度升温至设定的温度,该温度略高于生产材料的Tg温度。

测试采用直流的通断使测试COUPON从室温达到设定温度,在温度变化下对被测COUPON进行抗疲劳测试,加速潜在问题的发生。

测试通过的循环测试为生产出成品的性能决定。

详细的测试信息请见6.0。

2.0 应用文档2.1 IPC-TM-650 2.1.1 微切片制作2.2 IPC-TM-650 2.1.1.2 微切片制作-半自动/自动技术3.0 测试样件典型的测试COUPON如图一所示。

4.0 仪器或材料4.1 内层连接应力测试系统(IST)如6.04.2 四线2.54mm(0.1inch)公头连接器(参见MOLEX 2241-4042)4.3 Sn60Pb40或Sn63Pb37焊料4.4 阻焊剂4.5 电烙铁4.6 万用表-可选4.7 热影仪-可选5.0 程序5.1 测试样件准备5.1.1 在COUPON的第一面左右两端分别在0.040inch孔径中焊接上4个公头连接器,不能出现焊接不良即焊锡需灌满通孔。

5.1.2 由于测试前需进行预处理,故在COUPON安装入IST测试区前需使被测COUPON的温度降低到室温(降温过程大概需要10分钟)。

5.2 IST测试程序5.2.1 将测试COUPON 安装入IST 设备测试箱内5.2.3 输入数据文件名和启动预测试循环处理。

当预测试循环结束后,IST 测试系统开始对被测COUPON 进行热循环测试。

IST 测试过程中将对孔铜和孔壁与内层连接之间的电阻变化进行监控,并且记录各个COUPON 的测试表现资料。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

海思TC(Temperature Cycling)测试技术规范

拟制:克鲁鲁尔

审核:

批准:

日期:2019-11-11

历史版本记录

适用范围:

该测试用来检查芯片是否会因为热疲劳失效。

本规范适用于量产芯片验证测试阶段的TC(Temperature Cycling)测试需求。

简介:

该测试是为了确定芯片在高低温交替变化下的机械应力承受能力。

这些机械应力可能导致芯片出现永久的电气或物理特性变化。

引用文件:

下列文件中的条款通过本规范的引用而成为本规范的条款。

凡是注日期的引用文件,其随后所有的修改单(不包括勘误的内容)或修订版均不适用于本规范,然而,鼓励根据本规范达成协议的各方研究是否可使用这些文件的最新版本。

凡是不注日期的引用文件,其最新版本适用于本规范。

1. TC 测试流程

失效分析

功能、性能失效

物理损伤

注意:做TC 测试的芯片需经过PC(Preconditioning)预处理。

2. TC 测试条件

2.1 温度

温循的高低温条件如下表:

实际的高低温须参照Datasheet 说明,一般在“建议运行条件(Recommended Operating Conditions)”会给出建议运行的环境温度范围。

例如进芯的ADP16F0X :

温循温度示意图:

说明:

Ts(min)为温循最低温度

Ts(max)为温循最高温度

cycle time为温循周期

Ramp rate为温升率

建议Cycle周期0.5h,即2 cycles/hour。

建议温升率(Ramp rate)不超过15℃/min。

Ts(min)和Ts(max)的持续时间不低于1min。

2.2 循环次数

参考JESD47标准:

推荐循环总次数为1000次,并且在200、500、700、1000次时复测。

3.TC测试装置

高低温箱——温度范围、测试时间可控。

4.失效判据

温循过程,出现机械形变、断裂等物理损伤。

ATE\功能筛片有功能失效、性能异常。