mp424数据采集卡说明要点

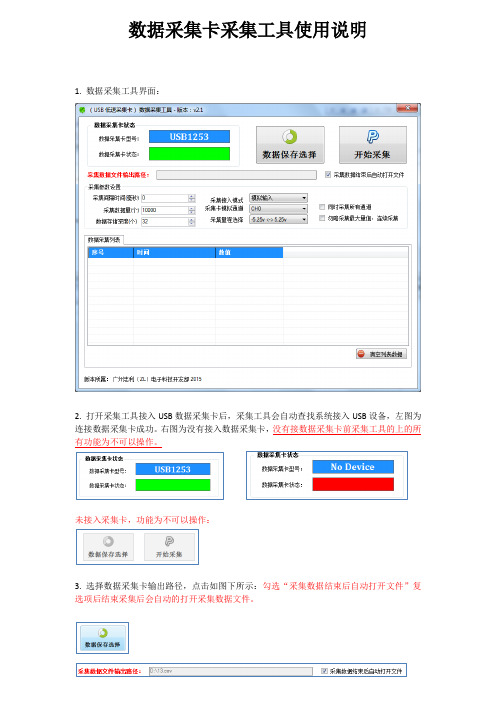

数据采集卡采集工具使用说明

数据采集卡采集工具使用说明1. 数据采集工具界面:2. 打开采集工具接入USB数据采集卡后,采集工具会自动查找系统接入USB设备,左图为连接数据采集卡成功。

右图为没有接入数据采集卡,没有接数据采集卡前采集工具的上的所有功能为不可以操作。

未接入采集卡,功能为不可以操作:3. 选择数据采集卡输出路径,点击如图下所示:勾选“采集数据结束后自动打开文件”复选项后结束采集后会自动的打开采集数据文件。

4. 采集参数设置:A.采集间隔时间(毫秒):采集每次数据点之间的等待时间设置,设置为0表示不等待连续采集数据。

B.采集数据量(个):最大采集数量值,采集到最大值后程序自动停止结束。

勾选“勿略采集最大量值,连续采集”复选框后此设置将无效。

采集结束在点击“停止采集”按键后结束。

C.数据存储深度(个):存储深度主要解决实时显示数据软件所占用的时间,存储深度值越大显示数据越慢,此显示速度慢不影响正常采集速度,只是影响显示速度。

如采集时频率比较慢时需要设置采集间隔时间,把存储深度设置为1表示实时值。

D.采集接入模式:采集模拟分为三种:模拟输入(单极性),差分输入,真双极输入。

模拟输入只能采集大于0V以上的电压值,不能采集负电压。

差分输入可以测试正负电压,测试正负电压需要按差分方式接线,差分方式接线与地线无关。

真双极输入可以测试正负电压,可以直接测试负电压。

采集工具会根据采集卡类型显示不同的输入模式,工具只会显示支持的模式选择项。

详细支持输入模式请参考产品说明书参数规格。

E.采集卡输入通道:输入通道表示采集卡指定的采集通道,不同型号采集有不同数量的采集通道。

采集卡支持:单通道采集和全通道采集功能。

全通道采集功能可以勾选“同时采集所有通道”复选框。

F.采集量程选择:不同类型采集卡支持不同的量程选择,详细参数可以参考用户说明。

5.清空列表数据点击“清空列表数据”按键后会清除列表数据,注意:清空后的数据不可恢复:6.数据采集:点击“开始采集”按键后采集工具自动开始采集数据,点击“停止采集”后程序自动停止并保存采集数据。

采集卡使用说明书

数字网络硬盘录像机用户使用指南(使用前请仔细阅读本手册)使用系统前,请检查下列各项条件:不得安装于高湿度、有灰尘或黑色脏物处。

避免阳光直射和直接受热.高温对产品不利。

避免电击和磁性物质。

避免高温或低温.(推荐温度范围应为 5 °C ~35°C)。

避免将导电物质滴入通风孔。

安装前,关闭系统。

确保系统后留有足够的电缆空间。

不得安装于可对产品造成晃动的地方。

在通风良好处,使用本产品。

收音机、电视或无线电通信设备均可造成对系统的损坏。

不得擅自拆卸系统。

不得在产品之上放置重物。

目录1. 产品介绍与功能 (3)1.1 产品简介 (3)1.2 产品功能特性 (4)1.2.1 主机端(服务器端) (4)1.2.2 IE 远程客户端 (6)2.产品安装 (7)2.1 服务器端与驱动安装 (7)2.2 软件的启动与卸载 (8)3.软件功能介绍 (9)3.1 登录系统 (9)3.2 服务器设置与操作 (10)3.2.1 设置本地用户权限 (12)3.2.2 设置网络用户权限 (13)3.2.3 录象质量设置 (14)3.2.4 报警设置 (15)3.2.5 设置自动工作计划 (18)3.2.6 普通云台设置 (19)3.2.7 录象回放相关 (20)3.2.8 调色方案设置 (21)3.2.9 网络端口参数设置 (22)4. 客户端操作使用说明 (23)1. 产品介绍与功能1.1 产品简介数字网络硬盘录像机以数码方式记录影像,它除了提供了清晰的画面,还能连续重复地录像,避免了模拟录像机频繁更换磁带的缺点。

另外它所具有的远程功能能让您轻松地在远端实施监控。

它是多种现代科技的技术结晶。

随着计算机、网络以及图像处理、传输技术的飞速发展,它必将成为网络视频监控系统发展的趋势。

系统推荐1)硬件系统推荐配置注意:1、建议请使用INTEL的CPU,我公司软件可能在某些AMD平台及其它平台上存在不兼容。

2、主板请使用华硕、技嘉等知名商用主板(之所以选用华硕、技嘉等知名品牌主板,是因为它们技术工艺先进,品质好,稳定性好,兼容性好)。

数据采集卡MF624手册

MF624M ULTIFUNCTION I/O C ARDUSER'S MANUAL© 2006 HUMUSOFT®© COPYRIGHT 2006 by HUMUSOFT s.r.o.. All rights reserved.No part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written consent of HUMUSOFT s.r.o.Limited Warranty: HUMUSOFT s.r.o. disclaims all liability for any direct or indirect damages caused by use or misuse of the MF 624 device or this documentation. HUMUSOFT is a registered trademark of HUMUSOFT s.r.o.Other brand and product names are trademarks or registered trademarks of their respective holders.Printed in Czech RepublicTable of ContentsTable of Contents1. Introduction41.1. General Description (4)1.2.Features L ist (4)1.3.Specifications (5)1.3.1. A/D Converter (5)1.3.2. D/A Converter (6)1.3.3. Digital Inputs (6)1.3.4.Digital Outputs (6)1.3.5. Quadrature Encoder Inputs (6)1.3.6. Counters/Timers (7)2. Installation82.1.Board Installation (8)2.2.Driver Installation (9)3. Programming Guide113.1.Register Map (11)3.2. Register Description (14)3.3. A/D Converter (25)3.4. D/A Converters (26)3.5.Digital I/O (27)3.6. Quadrature Encoder Inputs (27)3.7. Timer/Counter (28)4. I/O Signals294.1. Output Connector Signal Description (29)3Introduction Introduction41. Introduction1.1. General DescriptionThe MF 624 multifunction I/O card is designed for the need of connecting PC compatible computers to real world signals. The MF 624 contains 8 channel fast 14 bit A/D converter with simultaneous sample/hold circuit, 8 independent 14 bit D/A converters, 8 bit digital input port and 8 bit digital output port, 4 quadrature encoder inputs with single-ended or differential interface and 5 timers/counters. The card is designed for standard data acquisition and control applications and optimized for use with Real Time Toolbox for Simulink®. MF 624 features fully 32 bit architecture for fast throughput.1.2. Features ListThe MF 624 offers following features:C32-bit architectureC14 bit A/D converter with simultaneous sample & hold circuitC Conversion time 1.6 µs for single channel or 3.7 µs for 8 channelsC8 channel single ended fault protected input multiplexerC Input range ±10VC Internal clock & voltage referenceC8 D/A converters with 14 bit resolution and ±10V output rangeC 4 quadrature encoder inputs with single-ended or differential interface C Software selectable digital input noise filter (0.3 µs)Introduction C Quadrature input frequency up to 2.5 MHzC Software selectable index pulse operationC 4 channel 32-bit timer/counter with 20 ns resolutionC8 bit TTL compatible digital input portC8 bit TTL compatible digital output portC InterruptC Requires one PCI 2.3 slot and optional second slot for second connector C Can be used in 5V or 3.3V slotC Power consumption 500 mA@+5V, 150 mA@+12V, 150 mA@-12VC Operating temperature 0°C to +70°C1.3. Specifications1.3.1. A/D ConverterResolution:14 bitsNumber of channels:8 single endedSample/hold circuit:simultaneous sampling of all channels Conversion time: 1.6 µs single channel1.9 µs 2 channels2.5 µs 4 channels3.7 µs 8 channelsFIFO:8 entries/one conversion cycleInput ranges:±10VInput protection:±18VInput impedance:> 1010 Ohm5Introduction61.3.2. D/A ConverterResolution:14 bitNumber of channels:8Settling time:max. 31 µs (full scale swing, 1/2 LSB) Slew Rate:10 V/µsOutput current:min. ±10 mAShort circuit current:±15 mADC output impedance:max. 0.5 OhmLoad capacitance:max. 50 pFDifferential nonlinearity:±1 LSB1.3.3. Digital InputsNumber of bits:8Input signal levels:TTLLogic 0:0.8 V max.Logic 1: 2.0 V min.1.3.4. Digital OutputsNumber of bits:8Output signal levels:TTLLogic 0:0.5 V max. @ 24 mA (sink)Logic 1: 2.0 V min. @ 15 mA (source)1.3.5. Quadrature Encoder InputsNumber of axes: 4 independentResolution:32 bitsIntroductionCounter modes:quadrature X4 or up/down counterIndex input:programmableInputs:differential with Schmitt triggersInput noise filter:digital, programmable (0.3 µs)Input frequency:max. 2.5 MHz1.3.6. Counters/TimersCounter chip:customNumber of channels:5, 4 of them available on I/O connector, one used forA/D triggering and interruptResolution:32 bitsClock frequency:50 MHZCounter modes:up, down, binaryTriggering:software, externalClock source:internal, prescalers, externalInputs:TTL, Schmitt triggersOutputs:TTL7Hardware Installation82. Installation2.1. Board InstallationMF 624 has no switches or jumpers and you can install it in any free PCI expansion slot of your computer. Follow the steps outlined below:C Turn off the power of the computer system and unplug the power cord.C Disconnect all cables connected to the computer system.C Using a screwdriver, remove the cover-mounting screws. These screwsare at the rear side of the PC.C Remove the computer system's cover.C Find an empty expansion slot in your computer for MF 624 card. If theslot still has the metal expansion-slot cover attached, remove the coverwith a screwdriver. Save the screw to install the MF 624.C Hold the MF 624 firmly at the top of the board, and press the gold edgeconnector into an empty PCI expansion slot.C Using a screwdriver, screw the retaining bracket tightly against the rearplate of the computer system.C In case of using also quadrature encoder inputs or timer/counters installalso the aditional connector with metal slot cover to the neighbouringslot. Otherwise you can disconnect the aditional connector from theboard and save it for future use.C Replace the cover of the computer, and plug in the power cord.C Reconnect all cables that were previously attached to the rear of thecomputer.Hardware Installation2.2. Driver InstallationOnce you have installed MF 624 to PCI slot you can install Windows driver. Follow the steps outlined below:Turn on the computer, boot Microsoft Windows. MF 624 is detected by system automatically. In Add Hardware Wizzard window click Next.Insert installation floppy into drive a. In Found New Hardware Wizzard select Install the software automatically and click Next.9Hardware InstallationWhen prompted for driver location type a:\ and click Next. Click Finish to complete installation.10Programming Guide3. Programming Guide3.1. Register MapMF 624 uses PCI Vendor ID 0x186C and Device ID 0x0624. Registers of MF 624 card are located in 3 memory mapped regions:Region Function Size(bytes)Width (bits)BADR0 (memory mapped)PCI chipset, interrupts, status bits,special functions3232BADR1(memory mapped)A/D, D/A, digital I/O12816/32BADR2(memory mapped)Counter/timer chip12832 Table 1. Base Address RegionsPCI chipset (PCI 9030) and counter/timer chip are located in 32-bit regions and should be accessed by 32-bit instructions. BADR1 containing analog I/O has 16-bit architecture and registers are naturally 16-bit wide, but 32-bit access to this area is allowed as well under certain conditions. 32-bit access is broken by PCI chipset into two 16-bit cycles on the MF 624 internal bus. This allows increasing throughput by accessing two consecutive internal 16-bit registers by single PCI cycle. Therefore two D/A channels can be written or two A/D channels can be read at once which increases speed of data transfers almost twice. Do not use 32-bit access to other registers than ADDATA and DA0 - DA7.Programming GuideAddress Read WriteBADR0+0x4C INTCSR INTCSRBADR0+0x54GPIOC GPIOCTable 2. BADR0 Memory MapAddress Read Write BADR1+0x00ADDATA - A/D data ADCTRL - A/D control BADR1+0x02ADDATA - A/D data mirrorBADR1+0x04ADDATA - A/D data mirrorBADR1+0x06ADDATA - A/D data mirrorBADR1+0x08ADDATA - A/D data mirrorBADR1+0x0A ADDATA - A/D data mirrorBADR1+0x0C ADDATA - A/D data mirrorBADR1+0x0E ADDATA - A/D data mirrorBADR1+0x10DIN - Digital input DOUT - Digital output BADR1+0x20ADSTART - A/D SW trigger DA0 - D/A 0 data BADR1+0x22DA1 - D/A 1 data BADR1+0x24DA2 - D/A 2 data BADR1+0x26DA3 - D/A 3 data BADR1+0x28DA4 - D/A 4 data BADR1+0x2A DA5 - D/A 5 data BADR1+0x2C DA6 - D/A 6 dataBADR1+0x2E DA7 - D/A 7 data Table 3. BADR1 Memory MapProgramming Guide Address Read WriteBADR2+0x00CTR0STATUS CTR0MODEBADR2+0x04CTR0CTR0ABADR2+0x08CTR0BBADR2+0x10CTR1STATUS CTR1MODEBADR2+0x14CTR1CTR1ABADR2+0x18CTR1BBADR2+0x20CTR2STATUS CTR2MODEBADR2+0x24CTR2CTR2ABADR2+0x28CTR2BBADR2+0x30CTR3STATUS CTR3MODEBADR2+0x34CTR3CTR3ABADR2+0x38CTR3BBADR2+0x40CTR4STATUS CTR4MODEBADR2+0x44CTR4CTR4ABADR2+0x48BADR2+0x60CTRXCTRLBADR2+0x6C IRCSTATUS IRCCTRLBADR2+0x70IRC0BADR2+0x74IRC1BADR2+0x78IRC2BADR2+0x7C IRC3Table 4. BADR2 Memory MapProgramming Guide3.2. Register DescriptionINTCSR BADR0+0x4C Interrupt Control/Status R/W Bit Description Default0ADINT Enable. 1 enables A/D interrupt, 0 disables A/Dinterrupt.1ADINT Polarity. 1 active high, 0 active low. Connected toEOLC of A/D converter, should be set to active low fornormal operation.2ADINT Status. 1 indicates interrupt active, 0 indicatesinterrupt not active.3CTR4INT Enable. 1 enables counter 4 (or external trigger) interrupt, 0 disables counter 4 interrupt.4CTR4INT Polarity. 1 active high, 0 active low. Connectedto counter 4 output (or external trigger input).5CTR4INT Status. 1 indicates interrupt active, 0 indicatesinterrupt not active.6PCI Interrupt Enable. 1 enables PCI interrupt.07Software Interrupt. 1 generates PCI interrupt (INTA#) ifPCI Interrupt Enable bit is set (bit [6]=1).8ADINT Select Enable. 1 indicates edge triggered, 0 indicateslevel triggered interrupt.Note: Operates only in High-Polarity mode (bit [1]=1)9CTR4INT Select Enable. 1 indicates edge triggered, 0indicates level triggered interrupt.Note: Operates only in High-Polarity mode (bit [4]=1)10ADINT Clear. Writing 1 to this bit clears ADINT in edgemode.11CTR4INT Clear. Writing 1 to this bit clears CTR4INT inedge mode.31:12Reserved0x000300 Table 5. INTCSR - Interrupt Control/Status Register FormatProgramming Guide GPIOC BADR0+0x54Genaral Purpose I/O Control R/W Bit Description Default 16:0Reserved.0x006C017EOLC. Reads EOLC (end of last conversion) bit of A/D converter. Active low, 0 when all channels converted, 1during A/D conversion.21:18Reserved.0x1023LDAC. Load D/A converters, active low. Writing 0 makesA/D latches transparent, 1 holds D/A outputs. Can be used for simultaneous update of analog outputs.25:24Reserved.1026DACEN. 1 enables D/A outputs. 0 forces 0V to all D/Aoutputs.31:27Reserved.0 Table 6. GPIOC - General Purpose I/O Control Register FormatADCTRL BADR1+0x00 A/D Control W Bit Description Default 0CH0 select. 1 enables chanel 0 in channel scan list.01CH1 select. 1 enables chanel 1 in channel scan list.02CH2 select. 1 enables chanel 2 in channel scan list.03CH3 select. 1 enables chanel 3 in channel scan list.04CH4 select. 1 enables chanel 4 in channel scan list.05CH5 select. 1 enables chanel 5 in channel scan list.06CH6 select. 1 enables chanel 6 in channel scan list.07CH7 select. 1 enables chanel 7 in channel scan list.0 15:8Reserved.0x00 Table 7. ADCTRL - A/D Control Register FormatProgramming GuideADDATA BADR1+0x00 A/D Data R Bit Description Default13:0A/D Data. Reads data from A/D. Data is valid after EOLC bitin GPIOC goes low. Data from channels selected in ADCTRLregister are available in FIFO, lower number channels first.N/A15:14Reserved N/A Table 8. ADDATA - A/D DATA Register FormatNote: ADDATA register has 7 mirror registers located from BADR1+0x02 to BADR1+0x0E. This arrangement remaps FIFO to linear address space and allows reading consecutive values from A/D FIFO by 32-bit instructions.DIN BADR1+0x10 Digital Input R Bit Description Default 7:0Digital input 7:0. Reads digital input port.115:8Reserved N/A Table 9. DIN - Digital Input Register FormatDOUT BADR1+0x10 Digital Output W Bit Description Default 7:0Digital output 7:0. Writes to digital output port.015:8Reserved N/A Table 10. DOUT - Digital Output Register FormatADSTART BADR1+0x20 A/D Conversion Start R Bit Description Default15:0A/D Conversion Start. Reading this register triggers A/Dconversion for all channels selected in ADCTRL.N/ATable 11. ADSTART - A/D Conversion Start Register FormatProgramming GuideDA0BADR1+0x20 D/A Converter 0W DA1BADR1+0x22 D/A Converter 1W DA2BADR1+0x24 D/A Converter 2W DA3BADR1+0x26 D/A Converter 3W DA4BADR1+0x28 D/A Converter 4W DA5BADR1+0x2A D/A Converter 5W DA6BADR1+0x2C D/A Converter 6W DA7BADR1+0x2E D/A Converter 7W Bit Description Default 13:0DAx. D/A converter channel n data.0x3FFF 15:14Reserved.N/A Table 12. DAx - D/A Converter Data Register FormatNote: D/A converter outputs are updated only if LDAC bit in GPIOC registrer is set low (bit [23] at BADR0+0x54 =0). Otherwise D/A outputs are keeping old values and data written to DAn registers are kept until LDAC goes low. LDAC bit can be used for simultaneous update of D/A outputs.CTR0STATUS CTR1STATUS CTR2STATUS CTR3STATUS CTR4STATUS BADR2+0x00BADR2+0x10BADR2+0x20BADR2+0x30BADR2+0x40Counter 0 StatusCounter 1 StatusCounter 2 StatusCounter 3 StatusCounter 4 StatusRRRRRBit Description Default 0Counter Running. 1 if counter is running, 0 if stopped.0 1Counter Output. Reads counter toggle output.0 31:2Reserved.N/A Table 13. CTRxSTATUS - Counter Status Register FormatProgramming GuideCTR0MODE CTR1MODE CTR2MODE CTR3MODE CTR4MODE BADR2+0x00BADR2+0x10BADR2+0x20BADR2+0x30BADR2+0x40Counter 0 ModeCounter 1 ModeCounter 2 ModeCounter 3 ModeCounter 4 ModeWWWWWBit Description Default 0Count Direction. 1 counts up, 0 counts down.01Repetition. If 0, counter stops after terminal count. If 1,counter reloads after terminal count and starts new cycle.2Load Toggle. If 0, counter always reloads from register A on terminal count. If 1, counter reloads alternately from Aregister or from B register depending on output toggle status.3Output Toggle. If 0, counter output pin is connected toterminal count. If 1 counter output is connected to outputtoggle which is inverted on every terminal count.5:4Output Control. Controls output value and polarity.00: direct output01: inverted output10: force output low11: force output high107:6Trigger source. Controls counter hardware trigger source.00: trigger disabled01: trigger by counter input (TxIN)10: trigger by counter n-1 output11: trigger by counter n+1 output9:8Trigger type. Controls counter hardware trigger edge.00: trigger disabled01: trigger by rising edge of trigger signal10: trigger by falling edge of trigger signal11: trigger by either edge of trigger signal10Retrigger. If 0, retrigger is disabled and counter can betriggered only when stopped. If 1, counter can be retriggeredwhen running.Programming Guide12:11Gate source. Controls counter hardware gate source.00: gate set high01: counter gated by counter input (TxIN)10: counter gated by counter n-1 output11: counter gated by counter n+1 output13Gate polarity. Selects value of gate input which disablescounting. If set to 0, low level of gate signal disablescounting. If set to 1, high level of gate signal disablescounting.17:14Clock source. Selects counter clock source.0000: 50 MHz internal clock0001: 10 MHz internal clock0010: 1 MHz internal clock0011: 100 kHz internal clock0100: reserved0101: counter input (TxIN) rising edge0110: counter input (TxIN) falling edge0111: counter input (TxIN) either edge1000: reserved1001: counter n-1 output rising edge1010: counter n-1 output falling edge1011: counter n-1 output either edge1100: reserved1101: counter n+1 output rising edge1110: counter n+1 output falling edge1111: counter n+1 output either edge29:18Reserved030ADTRIGSRC. A/D trigger source. 0 triggers by falling edgeof counter 4 output. 1 triggers by falling edge of externaltrigger input. Implemented in CTR4MODE register only.31CTR4INTSRC. Interrupt signal source. 0 interrupts byfalling edge of counter 4 output. 1 interrupts by falling edgeof external trigger input. Implemented in CTR4MODEregister only.Table 14. CTRxMODE - Counter Mode Register FormatProgramming GuideCTR0 CTR1 CTR2 CTR3 CTR4BADR2+0x04BADR2+0x14BADR2+0x24BADR2+0x34BADR2+0x44Counter 0 DataCounter 1 DataCounter 2 DataCounter 3 DataCounter 4 DataRRRRRBit Description Default 31:0Counter Data. Reads current contents of counter.0 Table 15. CTRx - Counter Data Register FormatCTR0A CTR1A CTR2A CTR3A CTR4A BADR2+0x04BADR2+0x14BADR2+0x24BADR2+0x34BADR2+0x44Counter 0 Load ACounter 1 Load ACounter 2 Load ACounter 3 Load ACounter 4 Load AWWWWWBit Description Default 31:0Counter Load A. Counter load register A0 Table 16. CTRxA - Counter Load A Register FormatCTR0B CTR1B CTR2B CTR3B BADR2+0x08BADR2+0x18BADR2+0x28BADR2+0x38Counter 0 Load BCounter 1 Load BCounter 2 Load BCounter 3 Load BWWWWBit Description Default 31:0Counter Load B. Counter load register B0 Table 17. CTRxB - Counter Load B Register FormatNote: Counter 4 does not have Load B register and is always being loaded from Load A register.Programming GuideCTRXCTRL BADR2+0x60Counter Conrol Register W Bit Description Default 0CTR0START. Writing 1 starts counter 0.01CTR0STOP. Writing 1 stops counter 0.02CTR0LOAD. Writing 1 loads counter 0 from Load A orLoad B register.3CTR0RESET. Writing 1 resets counter 0.0 4CTR0TSET. Writing 1 sets counter 0 output toggle register.05CTR0TRESET. Writing 1 resets counter 0 output toggleregister.6CTR1START. Writing 1 starts counter 1.0 7CTR1STOP. Writing 1 stops counter 1.08CTR1LOAD. Writing 1 loads counter 1 from Load A orLoad B register.9CTR1RESET. Writing 1 resets counter 1.0 10CTR1TSET. Writing 1 sets counter 1 output toggle register.011CTR1TRESET. Writing 1 resets counter 1 output toggleregister.12CTR2START. Writing 1 starts counter 2.0 13CTR2STOP. Writing 1 stops counter 2.014CTR2LOAD. Writing 1 loads counter 2 from Load A orLoad B register.15CTR2RESET. Writing 1 resets counter 2.0 16CTR2TSET. Writing 1 sets counter 2 output toggle register.017CTR2TRESET. Writing 1 resets counter 2 output toggleregister.18CTR3START. Writing 1 starts counter 3.0 19CTR3STOP. Writing 1 stops counter 3.020CTR3LOAD. Writing 1 loads counter 3 from Load A orLoad B register.21CTR3RESET. Writing 1 resets counter 3.0Programming Guide22CTR3TSET. Writing 1 sets counter 3 output toggle register.023CTR3TRESET. Writing 1 resets counter 3 output toggleregister.24CTR4START. Writing 1 starts counter 4.0 25CTR4STOP. Writing 1 stops counter 4.026CTR4LOAD. Writing 1 loads counter 4 from Load A orLoad B register.27CTR4RESET. Writing 1 resets counter 4.0 28CTR4TSET. Writing 1 sets counter 4 output toggle register.029CTR4TRESET. Writing 1 resets counter 4 output toggleregister.31:30Reserved.0 Table 18. CTRXCTRL - Common Counter Control Register FormatNote: Bits 29:0 are active by writing 1. Writing 0 to these bits is not necessary and has no action asigned.Programming GuideIRCCTRL BADR2+0x6C IRC Conrol Register W Bit Description Default1:0IRC0MODE. Selects IRC0 counter operation.00: IRC, 4 edge detection01: bidirectional counter, rising edge10: bidirectional counter, falling edge11: bidirectional counter, either edge3:2IRC0COUNT. IRC0 count control.00: IRC0 count enabled01: IRC0 count disabled10: IRC0 count enabled if I0 input is 011: IRC0 count enabled if I0 input is 16:4IRC0RESET. IRC0 reset control.000: IRC0 reset disabled001: IRC0 reset010: IRC0 reset if I0 is 0011: IRC0 reset if I0 is 1100: IRC0 reset by rising edge of I0101: IRC0 reset by falling edge of I0110: IRC0 reset by either edge of I0111: Reserved7IRC0FILTER. IRC0 digital filter control. 1 enables digitalfilter on IRC0 inputs. 0 disables filtering.9:8IRC1MODE. Selects IRC1 counter operation. SeeIRC0MODE11:10IRC1COUNT. IRC1 count control. See IRC0COUNT0 14:12IRC1RESET. IRC1 reset control. See IRC0RESET015IRC1FILTER. IRC1 digital filter control. 1 enables digitalfilter on IRC1 inputs. 0 disables filtering.17:16IRC2MODE. Selects IRC2 counter operation. SeeIRC0MODE19:18IRC2COUNT. IRC2 count control. See IRC0COUNT0 22:20IRC2RESET. IRC2 reset control. See IRC0RESET0Programming Guide23IRC2FILTER. IRC2 digital filter control. 1 enables digitalfilter on IRC2 inputs. 0 disables filtering.25:24IRC3MODE. Selects IRC3 counter operation. SeeIRC0MODE27:26IRC3COUNT. IRC3 count control. See IRC0COUNT0 30:28IRC3RESET. IRC3 reset control. See IRC0RESET031IRC3FILTER. IRC3 digital filter control. 1 enables digitalfilter on IRC3 inputs. 0 disables filtering.Table 19. IRCCTRL - IRC Control Register FormatNote: Digital filter on IRC inputs is a low-pass filter improving noise immunity. The filter also decreases maximum input frequency and signal changes shorter than 320 ns are ignored.IRCSTATUS BADR2+0x6C IRC Status Register R Bit Description Default 0IRC0INDEX. Reads I0 input.17:1Reserved.N/A8IRC1INDEX. Reads I1 input.115:9Reserved.N/A 16IRC2INDEX. Reads I3 input.1 23:17Reserved.N/A 24IRC3INDEX. Reads I3 input.131:25Reserved.N/A Table 20. IRCSTATUS - IRC Status Register FormatProgramming GuideIRC0 IRC1 IRC2 IRC3BADR2+0x70BADR2+0x74BADR2+0x78BADR2+0x7CIRC0 Data RegisterIRC1 Data RegisterIRC2 Data RegisterIRC3 Data RegisterRBit Description Default 31:0IRCx. Reads data from IRC counter.0 Table 21. IRCx - IRCx Data Register Format3.3. A/D ConverterA/D converter is controlled through ADDATA, ADCTRL, ADSTART and GPIOC registers.Before starting a conversion it is necessary to configure channels which will be converted by ADCTRL register. Each A/D channel has one bit in ADCTRL. Setting this bit includes the channel in conversion scan list. Conversion can be initiated by a read operation from ADSTART register, by timer/counter T4 or by external trigger. Once the conversion is started, selected channels are simultaneously sampled and converted. When the conversion of all selected channels is complete, EOLC (bit 17 in GPIOC register) is set low which means that converted data is available in output FIFO and can be read from ADDATA register. EOLC remains low until next conversion is started. Starting new conversion resets FIFO.A/D conversion can be triggered also by timer 4 output or by external trigger input according to setting of ADTRIGSRC (bit 30 in CTRXCTRL register). These signals can also generate interrupt according to setting of INT2SRC (bit 31 in CTRXCTRL register).A/D converter has fixed input range ±10V and uses two's complement binary coding. A/D converter zero offset can be adjusted by R23. A/D gain can be adjusted by R25.Programming GuideDigital Value Analog Voltage0x3FFF-0.0012 V0x2000-10.0000 V0x1FFF9.9988 V0x00000.0000 VTable 22. A/D Inputs Coding3.4. D/A ConvertersD/A converters are accessed through eight data input latch registers DA0 - DA7. D/A converter outputs are initially connected to ground until DACEN (bit 26 in GPIOC register) is set to 1. This bit can be used to disconnecting all analog outputs from D/A converters. Data from D/A input latch registers are passed to D/A converters only if LDAC (bit 23 in GPIOC register) is 0. If this bit is set to 1, data remains just in input latches without being written to D/A converters. Then if LDAC is set to 0, all D/A outputs are updated simultaneously from input latch registers.Output voltage ranges of D/A converters are ±10V and straight binary coding is used. After power-on or hardware reset the output voltage is set to 0V. D/A converter positive range can be adjusted by R5 while negative range can be adjusted by R8.Programming GuideDigital Value Analog Voltage0x3FFF9.9988 V0x20000.0000 V0x1FFF-0.0012 V0x0000-10.0000 VTable 23. D/A Outputs Coding3.5. Digital I/OMF 624 contains one 8-bit digital input port and one 8-bit digital output port. Digital input port can be accessed directly by read from DIN register. Inputs are TTL compatible. Digital output port can be accessed by byte or word write to DOUT register. Outputs are TTL compatible. After power-on or hardware reset digital outputs are set to 0.3.6. Quadrature Encoder InputsMF 624 contains four quadrature encoder inputs with single-ended or differential interface and index inputs. Inputs are differential TTL compatible with Schmitt triggers.MF 624 can be used either with single-ended or differential encoder outputs. In case of single-ended encoder outputs use + signal inputs and leave - inputs disconnected. If differential encoder outputs are used connect both + and - inputs of MF 624 to encoder outputs. In both cases connect encoder signal ground to GND on X2 connector of MF 624.Each IRC channel has one 32 bit data register IRC0 - IRC3. Control and statusProgramming Guideregisters IRCCTRL and IRCSTATUS are common for all IRC channels. Each IRC counter can be switched to bidirectional counter mode. In such case A is clock input and B controls direction (1 up, 0 down). In IRC and counter modes counter reset can be controlled by I input.3.7. Timer/CounterMF 624 contains 5 timers/counters with 50 MHz clock. The first four timers are accessible through external connector X2 while the fifth timer can generate system interrupt or trigger A/D conversion, or can be used as a clock source for other timers or for similar internal functions. TxIN pin on I/O connector can serve either as clock, gate or trigger input depending on configuration. Inputs and outputs are TTL compatible, Schmitt triggers are at all inputs to improve noise immunity.Counters are implemented in programmable gate array chip offering wide range of operation modes allowing:C up/down, binary countingC internal or external clock and gate sourcesC prescalingC one shot/continuous outputsC software/external triggeringC programmable gate and output polaritiesC pulse countingC frequency measurementC pulse generation including PWMC programmable clock sourceI/O Signals4. I/O Signals4.1. Output Connector Signal DescriptionThe MF 624 multifunction I/O card is equipped with an on-board 37 pin D-type female connector X1 and with an aditional 37 pin D-type female connector X2 on cable extender. For pin assignment refer to Tables 24 and 25. TB 620 Terminal Board can be connected to both connectors.AD0-AD7Analog inputsDA0-DA7Analog outputsDIN0-DIN7TTL compatible digital inputsDOUT0-DOUT7TTL compatible digital outputsIRC0-IRC3Quadrature encoder A, B and Index inputsT0IN-T3IN Timer/counter gate and clock inputsT0OUT-T3OUT Timer/counter outputsTRIG A/D converter external trigger input+12V+12V power supply-12V-12V power supply+5V+5V power supplyAGND Analog groundGND Digital ground。

数据采集卡分析报告精品PPT课件

触发、后触发、匹配触发和延时触 发

◆工作温度-20-70 价格8239(淘宝现价) 地址:西安市高新技术产业开发区 科技二路68号西安软件园秦风阁 综合楼301

Tel: /87607004 伍勇

阿尔泰PCI8602 ◆16位AD精度,250KS/s采样频 率

◆单端32路/差分16路 模拟量输 入

◆工作温度-20-60 价格1900 地址:西安市高新区高新三路2 号海佳云顶B座2202室 联系方式:

手机:联系人:张琦

QQ:1599940642 公司官网:

NI USB-6009 ◆输入14位分辨率,48

kS/s)

◆8路模拟输入通道 ◆12位分辨率, 150 S/s ◆输出2路模拟输出通道 ◆12条数字I/O线 ◆32位计数器 ◆获取用于OEM的仅含 板卡的套件 ◆NI-DAQmx驱动软件 和NI LabVIEW ◆SignalExpress交互式 数据记录软件 价格:2150

数据采集卡分析 报告

报告目的

❖ 车体振动的测试,采用加速度传感器对车体各个轴向的相关唯一跳动 量进行测量,并通过labview对数据进行采集与处理等,来实现试验 中稳定性测试的方法。利用计算机对测量点的处理,编制出基于虚拟 仪器的测量软件,同时还可以对测量的数据进行快速傅里叶变换,所 需要的仪器设备有加速度传感器、数据采集卡、被测量的车体、计算 机、电源,信号调理设备。为了能够圆满完成这次测试任务,需要购择口碑好,有试验者使用过的,测量稳定的三个 产品进行对比,初步选择 方案一 选择:研华的1712 理由:1本实验室就有研华的板卡(测试良好),只需配一根电缆线及端子。 经 查找问价,电缆线端子合计890元,国产阿尔泰PCI8602效果相比较, 价格虽 然便宜,但性能没有研华的好。NI PCI-4472价格太高。

数据采集卡(待完善)

基础知识

方乐 2019年10月23日

什么是数据采集卡?

数据采集是指对设备被测的模拟或数字信号,自动采集并送到上 位机中进行分析、处理。

数据采集卡,即实现数据采集功能的计算机扩展卡,可以通过 USB、PXI、PCI、PCI Express、火线(1394)、PCMCIA、ISA、 Compact Flash、485、232、以太网、各种无线网络等总线接入计算 机。

采样频率:单位时间采集的数据点数,与AD芯片的转换一个点 所需时间有关,例如:AD转换一个点需要T=10us,则其采样频率 f=1/T为100K(即100kHz),即每秒钟AD芯片可以转换100K的数据 点数。常有100K、250K、500K、800K、lM、40M等。

03.技术参数(缓存)

缓存:主要用来存储AD芯片转换后的数据。带缓存板卡可以设 置采样频率,否则不可改变。缓存有RAM和FIFO两种。FIFO主要用 作数据缓冲,存储量不大,速度快;RAM一般用于高速采集卡,存储 量大,速度较慢。

01.分类(处理信号)

③:现在电能计量的常用方法是电能脉冲计量法,即使电能表转盘每 转一圈便输出一个或两个脉冲,用输出的脉冲数代替转盘转动的圈数, 并将脉冲量通过计数器计数后输入测控装置,由CPU进行存储、计算。

01.分类(总线PCI)

PCI是Peripheral Component Interconnect(外设部件互连标准)的缩 写,它是目前个人电脑中使用最为广 泛的接口,几乎所有的主板产品上都 带有这种插槽。PCI插槽也是主板带有 最多数量的插槽类型,在目前流行的 台式机主板上,ATX结构的主板一般 带有5~6个PCI插槽,而小一点的 MATX主板也都带有2~3个PCI插槽, 可见其应用的广泛性。

数据采集卡软件使用说明

数据采集卡软件使用说明:1.使用前应先进行DAC硬件校准。

打开“窗口”——“脚本编辑器”,打开文件“DAC校准.vbs”,单击“运行”,用电压表测量DAC0和DAC1是否输出+5V电压,若有误差,则调整电位器R16和R15进行校准,校准完成后单击“停止”后,测量DAC0和DAC1是否输出0V电压,若不准则调整R60和R59。

注意:这两组调整存在关联,只能折中调整。

若折中值有较大误差,则与我联系。

ADC输入的零点调整。

调整电位器R58和R57调零,脚本程序中通过ReadData(1)和ReadData(2)读入电压值进行校验。

2.双踪示波器打开“窗口”——“双踪示波器”,如图1所示:图1双踪示波器调节好CH1和CH2的Y轴方向的刻度单位及X轴方向的时间刻度后,单击“运行”,即可显示波形,此时“运行”按钮显示为“停止”,单击它即可停止。

也可通过分别勾选两个输入通道的“显示交流”,使波形基于各自的零线对称(即只保留交流成份)。

注:每次重新选取X轴方向的时间刻度后,自动进入停止状态,需手工重启“运行”。

通过鼠标左键按下后拖动左边沿的白色滑块可调节CH1零电压基线位置,同样,通过鼠标左键按下后拖动右边沿的白色滑块可调节CH2零电压基线位置。

在“停止”状态下,可以手工测量水平方向的时间或垂直方向的电压值。

先在窗体的左上边的“手工测量”选定一个测量项,用鼠标左键按下后拖动即可完成测量,左键释放后会显示测量结果,此时按鼠标右键或对“手工测量”重新选定一项均可清除前一次测量结果。

勾选“自动计算机电参数”即可显示输入通道的频率、振幅、初相、直流分量值,反之,则不显示。

勾选“李沙育图”,则显示切换为图2所示的李沙育图,也可调节两个通道的刻度单位观察李沙育图的变化,反之,则返回双踪示波图。

图2李沙育图3.DAC输出(信号发生器)采集卡接电后自动处于DAC双通道均输出50Hz,振幅10V 左右的交流信号,在设置好输出通道号,频率,强度(%)值后,单击“DAC输出”按钮即可实现DAC输出。

数据采集卡说明指导书

PC-6311D模入模出接口卡技术阐明书1.概述:PC-6311D 模入模出接口卡合用于具备ISA 总线PC系列微机,具备较好兼容性,CPU从当前广泛使用64位解决器直到初期16位解决器均可合用,操作系统可选用典型MS-DOS,当前流行Windows系列,高稳定性Unix等各种操作系统以及专业数据采集分析系统 LabVIEW 等软件环境。

在硬件安装上也非常简朴,使用时只需将接口卡插入机内任何一种ISA总线插槽中,信号电缆从机箱外部直接接入。

也可插入我所研制PC扩展箱内使用。

PC-6311D模入模出接口卡安装使用以便,程序编制简朴。

其模入模出及I/O信号均由卡上37芯D型插头及另配转换插头与外部信号源和设备连接。

对于模入某些,顾客可依照实际需要选取单端或双端输入方式。

对于模出某些,顾客可依照控制对象需要选取电压或电流输出方式以及不同量程。

2. 重要技术参数:2.1 模入某些2.1.1输入通道数:(标*为出厂原则状态,下同)单端32路;* / 双端16路2.1.2输入信号范畴:0V~10V*;/ ±5V2.1.3输入阻抗:≥10MΩ2.1.4A/D转换辨别率:12位2.1.5A/D转换速度:10μS2.1.6A/D启动方式:程序启动/外触发启动2.1.7A/D转换结束辨认:程序查询/中断方式2.1.8A/D转换非线性误差:±1LSB2.1.9A/D转换输出码制:单极性原码*/双极性偏移码2.2.10系统综合误差:≤0.2% FSR2.2 模出某些:2.2.1输出通道数:2路 (互相独立,可同步或分别输出,具备上电自动清零功能。

)2.2.2输出范畴:电压方式:0~5V;0~10V*;±5V;±2.5V电流方式:0~10mA;4~20mA2.2.3输出阻抗:≤2Ω (电压方式)2.2.4D/A转换器件:DAC12102.2.5D/A转换辨别率:12位2.2.6D/A转换输入码制:二进制原码(单极性输出方式时)*;二进制偏移码(双极性电压输出方式时)2.2.7D/A转换综合建立时间:≤2μS2.2.8D/A转换综合误差:电压方式:≤0.2% FSR电流方式:≤ 1% FSR2.2.9电流输出方式负载电阻范畴:使用机内+12V电源时:0~250Ω外加+24V电源时:0~750Ω2.3 数字量输入输出某些:2.3.1DI:8路;TTL原则电平2.3.2 DO:8路;TTL原则电平;有输出锁存功能2.4 电源功耗:+5V(±10%)≤400mA;+12V(±10%)≤100mA;-5V(±10%)≤10mA2.5 使用环境规定:工作温度:10℃~40℃;相对湿度:40%~80%;存贮温度:-55℃~+85℃2.6 外型尺寸:(不含档板)长×高=182.6mm×106.7 mm (7.2英寸×4.2英寸) 3. 工作原理:PC-6311D模入模出接口卡重要由模数转换电路、数模转换电路、数字量输入输出电路、接口控制逻辑电路构成。

图像采集卡的基础知识介绍

STROBE/PLCK

像元时钟信号。 STROBE是图像数据的像元时钟。它的 频率与数据速率相同,即使数据无效, STROBE仍然连续交 变。为了获得有效的图像数据,采集卡一般在FVAL和LVAL 为高电平时,在STROBE的下降沿进行数据锁存。 FVAL 帧同步信号。一般FVAL高电平表明相机正输出一帧有效 数据。 LVAL 行同步信号。当FVAL为高电平时, LVAL高电平表明相 机正输出一个有效的像元行。

北京微视凌志技术支持培训 2011.4

Part. 3—图像采集卡的基础知识介绍

一、图像采集卡基本概念

图像采集卡(FrameGraber)

图像采集卡是图像采集部分和处理部分的接口。硬件上可

理解为相机与计算机之间的接口,图像经过采样量化以后 转换为数字图像并输入、储存到帧存储器的过程,叫做采 集、数字化。

一、图像采集卡基本概念

模拟采集卡的数字化精度

像素抖动

像素抖动是由图像采集卡的A/D转换器的采样时钟的误差 产生的像元位置上的微小的错误从而导致对距离测量的错

误。

一、图像采集卡基本概念

模拟采集卡的数字化精度

像素抖动

一、图像采集卡基本概念

模拟采集卡的数字化精度

灰度噪音

图像采集卡的数字化转换的过程包括对模拟视频信号的放 大和对其亮度(灰度值)进行测量。在此过程中会有一定的

–

– – – –

数字信号——USB

接口是4芯,其中2根为电源线、2根为信号线,接口体

积小,可热拔插,可真正实现即插即用,适合传送多 媒体数据的传送模式,连接方便。

USB 2.0向下兼容USB 1.1、USB 1.0,数据的传 输率可

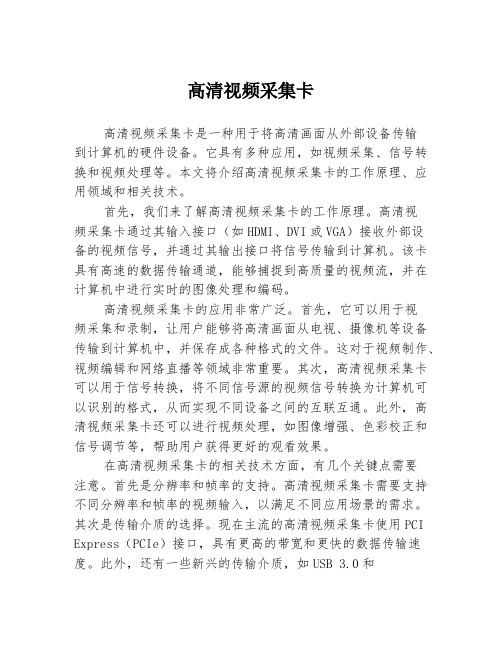

高清视频采集卡

高清视频采集卡高清视频采集卡是一种用于将高清画面从外部设备传输到计算机的硬件设备。

它具有多种应用,如视频采集、信号转换和视频处理等。

本文将介绍高清视频采集卡的工作原理、应用领域和相关技术。

首先,我们来了解高清视频采集卡的工作原理。

高清视频采集卡通过其输入接口(如HDMI、DVI或VGA)接收外部设备的视频信号,并通过其输出接口将信号传输到计算机。

该卡具有高速的数据传输通道,能够捕捉到高质量的视频流,并在计算机中进行实时的图像处理和编码。

高清视频采集卡的应用非常广泛。

首先,它可以用于视频采集和录制,让用户能够将高清画面从电视、摄像机等设备传输到计算机中,并保存成各种格式的文件。

这对于视频制作、视频编辑和网络直播等领域非常重要。

其次,高清视频采集卡可以用于信号转换,将不同信号源的视频信号转换为计算机可以识别的格式,从而实现不同设备之间的互联互通。

此外,高清视频采集卡还可以进行视频处理,如图像增强、色彩校正和信号调节等,帮助用户获得更好的观看效果。

在高清视频采集卡的相关技术方面,有几个关键点需要注意。

首先是分辨率和帧率的支持。

高清视频采集卡需要支持不同分辨率和帧率的视频输入,以满足不同应用场景的需求。

其次是传输介质的选择。

现在主流的高清视频采集卡使用PCI Express(PCIe)接口,具有更高的带宽和更快的数据传输速度。

此外,还有一些新兴的传输介质,如USB 3.0和Thunderbolt,它们提供了更便捷和高效的视频传输方式。

再者,驱动程序的稳定性和兼容性也是衡量高清视频采集卡质量的重要指标。

用户需要选择那些具有稳定驱动程序和广泛兼容性的产品,以确保设备的正常运行和兼容性。

总之,高清视频采集卡是一种非常实用的硬件设备,可以将高清画面从外部设备传输到计算机中,具有广泛的应用领域和相关技术。

它在视频采集、信号转换和视频处理等方面提供了便捷和高质量的解决方案,对于视频制作、视频编辑和网络直播等领域具有重要意义。

数据采集卡基本简介

具体来说,这种设计分两部分:数据采集部分和数据处理部分。

数据采集就是利用LabVIEW的驱动程序对数据采集卡进行设置并使其按设置工作,进行数据的采集;数据处理则是将采集到的数据送至计算机进行运算处理等等。

对于初学者,可先从第二部分开始。

将实际的数据采集先用LabVIEW自带的数组或者波形函数来代替,着重设计数据处理的软件部分。

这部分可以包括:滤波、数据存储、数据读取、波形显示、波形分析处理(如傅立叶变换、谱密度计算等等)。

这些在LabVIEW中都有集成的函数模块,也就是VI,只要对每个VI的输入输出设置正确就好。

当软件部分设计完成后,再设计数据采集部分。

这是软硬件结合的部分。

既要对所用的数据采集卡的参数和工作方式有充分的正确的认识,又要对如果利用LabVIEW驱动采集卡掌握。

一般来说采集卡都带有LabVIEW的驱动,只要参看数据采集卡的使用说明(PDF),就可以掌握了。

选择好数据采集卡后,将该采集卡的驱动光盘放入计算机并按其指示进行安装,则其驱动模块将装入原LabVIEW软件中,然后和第一步的软件编程一样,对驱动所要用的VI的输入输出参数设置正确,编写程序即可。

当两部都做完后,将整个采集系统运行一下,对于设计中存在的疏漏再进行修改。

推荐使用《LadVIEW8.20程序设计从入门到精通(附光盘)》作者:陈锡鸿这本书不错,深入浅出,初学必备~~数据采集(DAQ)基础知识现今,在实验室研究、测试和测量以及工业自动化领域中,绝大多数科研人员和工程师使用配有PCI、PXI/CompactPCI、PCMCIA、USB、IEEE1394、ISA、并行或串行接口的基于PC的数据采集系统。

许多应用使用插入式设备采集数据并把数据直接传送到计算机内存中,而在一些其它应用中数据采集硬件与PC分离,通过并行或串行接口和PC相连。

从基于PC的数据采集系统中获取适当的结果取决于图示一中的各项组成部分:•PC•传感器•信号调理•数据采集硬件•软件本文详细介绍了数据采集系统的各个组成部分,并解释各个部分最重要的准则。

mp424数据采集卡说明

MP424

wwlab 2007/5 ☐USB2.0总线AD采集模块☐4路并行12位 AD

☐开关量:8DI/8DO

使用手册

✧VB编程需要的声明模块程序MP424.bas。

☐MP424.EXE:测试程序。

☐在光盘的\USB\MP424\Delphi目录中包含:

✧Delphi的编程例子

驱动安装

安装方法:

1.将MP424插入一个USB接口。

安装的模块的设备号为“0”。

2.Windows将会显示找到新硬件,可按找到新硬件向导进行下一步

3.选择不搜索软件

4.下一步,选择从列表指定位置安装

5.选择不要搜索,我自己安装驱动

6.下一步,选择从磁盘安装,并指定目录(光盘:\USB\MP424\DRIVER\MP424.INF),找到MP424.inf文件,进行安装

7.Windows将显示完成添加/删除硬件向导,单击完成即可完成安装过程。

安装后,程序自动将MP424.dll动态链接库程序拷贝到

前工作目录中。

驱动安装完毕后在\控制面板\系统\设备管理中的。

莫非电子 MPS-020101 24位多功能微弱信号采集卡 使用说明

CMOS

2.5、工作温度

▪ -40℃-+85℃

三、 应用领域

微弱信号采集 便携式仪表和测试设备 传感器信号采集控制 工业流程控制

四、 软件支持

提供 Windows95/98/NT/2000 下的驱动程序,提供通用 DLL 文件,并提供在 LabVIEW 图像化语言编写的应用软件范例程序。

五、 销售清单

莫非电子

MPS-020101 24 位多功能微弱信号采集卡使用说明

MPS-020101 24 位多功能微弱信号采集卡

使用说明

Ver 1.0

莫非电子

MPS-020101 24 位多功能微弱信号采集卡使用说明

第一章 产品概述

MPS-020101 24 位多功能微弱信号采集卡

一、 产品简介

MPS-020101 数据采集卡是一款基于 USB 总线的 24 位多功能微弱信号数据采集卡,具有 4 路差分(或 8 路单端)24 位模拟信号采集,集成可编程增益放大器、Bornout 检测、板载参 考电压输出等功能,并具有 2 路电流信号输出和 8 路数字信号输入/输出端口。可用于实验 室、产品质量检测中心和大专院校等各种领域的数据采集、分析和数据处理系统,也可用于 工业现场的过程监控系统,尤其适用于微弱信号的检测。

名与某个 重名时 就 这个 当 与同 函数

函数

公 变 任何 它 名称相同时 如果该 用 量、常数或

, 可以使用 其 过程的

参数。 动态链接库的函数 ,也可以使用 Alias。

一范围内的 动态链接库

某个 符不符合 命名约定时 函数中的 字

动态链接库的

如果首 符不 符 # 则 Aliasname(可选)动态链接库。

字

采集卡使用说明书

A:可设置存盘路径。 B:自动存盘为每采集一次,存为一个文件。 C:手动存盘为设定间隔时间存一个文件。

3.2.12 波形回放

按

16

按钮,将整个波形重新播放一遍,没有放完,不能终止。

PCI8200

3.2.13 其它功能 A:拖动波形显示区下的滑块,水平移动波形,可观测波形其它部分。 B:在暂停时,波形显示区内,按CTRL+鼠标右键,无级放大波形。 C:在暂停时,波形显示区内,按CTRL+鼠标左键,无级缩小波形。

≥80dB

尺寸:

187mm×112mm

重量:

0.2Kg

PCI8200 信号发生部分主要性能指标

参数

任意波形部 分(ARB)

正弦波形部分 (DDS)

波形频率 频率分辨率 DAC 时钟 通道数 波形长度 垂直分辨率

0.1Hz(DC) ~100KHz 0.1Hz~20MHz (最高可到 50MHz)

△F=fclk/dots

PCI8200 采集部分主要性能指标

最大采样率: 50Msps

单台通道数:

并行双通道

AD 分辨率:

12bits,系统精度:≤±0.5%

存储容量:

每通道最大 16Msa/CH

量程:

±100mV~±40V(共分 9 挡)

输入方式:

BNC 单端双极性电压输入

输入阻抗:

1MΩ;输入电容≤25pF

输入信号带宽:

Windows2000/XP

提供常用开发平台下的 DEMO 源代码(Vc、Cvi、Vb、 LabView、C++ Builder)。

主要功能 ★ 自检功能 ★ 波形存储、恢复 ★ 波形运算:加、减、反向 ★ 高级功能:FFT 频谱分析、数字滤波、平均等 ★ 自动测定:最大值、最小值、均方值、平均值、峰峰值、占空比 ★ 光标测量时间和电压 ★ 数字 I/O ★ 外部触发同步 ★ 支持二次开发

YAV 8AD PRO 24位高精度RJ45网口多功能采集卡技术手册RJ8452

YAV8AD PRO RJ4524位高精度采集卡技术手册V1801武汉亚为电子科技有限公司RJ8452关于本手册为亚为推出的YAV8AD PRO24位高精度无线采集卡的用户手册,主要内容包括功能概述、8路模拟量输入功能、8路IO功能、应用实例、性能测试、注意事项及故障排除等。

说明序号版本号编写人编写日期支持对象应用时间特别说明1 1.0郑先科2014.05YA V8AD PRO采集卡2 2.0郑先科2016.01YA V8AD PRO采集卡3 3.0郑先科2017.01YA V8AD PRO采集卡2017.01适用于RS232\485\WiFi\GPRS ZIGBEE\蓝牙\433M无线4 4.0李雪2017.08YA V8AD PRO采集卡2017.08目录1.快速上手 (1)产品包装内容 (1)应用软件 (1)接口定义 (1)通信 (2)2.产品概述 (2)技术指标 (2)⏹模拟信号输入 (3)⏹数字信号输入 (4)⏹数字信号输出 (4)⏹通信总线 (4)⏹温度参数 (4)硬件特点 (5)原理框图 (5)机械规格 (6)3.采集卡信号接线 (7)AI模拟量接线 (7)DI数字量接线 (8)DO数字量接线 (9)4.模拟量输入功能 (9)模拟量输入 (9)输入采样原理 (10)输入接线 (10)采样值计算 (11)⏹无符号整型 (11)⏹模拟量值 (11)⏹24位精度采集值的计算方法 (12)5.数字量输入功能 (12)数字量输入原理 (12)DI高低电平/无源触点输入 (13)计数功能输入 (13)测频功能输入 (14)PWM功能输入 (14)6.数字量输出功能 (15)输出原理 (15)DO高低电平输出 (15)PWM测试输出 (15)AO输出 (15)输出接线方式 (15)7.通信协议 (16)WSN无线通信 (16)数据采集(被动接收) (19)启动发送(默认启动) (20)停止发送 (20)配置通道 (20)清空计数 (20)8.应用实例 (21)采集卡连接 (21)软件功能 (23)⏹YA V-WDS WIFI信号采集软件 (23)9.注意事项及故障排除 (24)注意事项 (24)⏹存储说明 (24)⏹出货清单 (24)⏹质保及售后 (24)⏹特别说明 (24)故障排除 (25)⏹无法正常采集数据 (25)⏹不显示波形 (26)⏹DI测频计数没反应 (26)⏹采集速度不够 (26)⏹软件错误 (26)10.性能测试 (26)安全规范 (26)耐电压范围测试 (27)环境适应性测试 (27)11.文档权利及免责声明 (28)12.联系方式..................................................................................................................错误!未定义书签。

采集卡安装及远程使用说明书分析

乔安68系列安装及远程使用说明书基本安装1、把电脑的机箱打开,将采集卡的金手指垂直对准主板上的PCI槽,轻轻往下一压,再用一颗小螺丝把采集卡固定到电脑机箱上就完成采集卡硬件安装。

注意:硬件安装成功之后,电脑启动之后会提示发现新硬件以及弹出找到新硬件向导,如下图:2、驱动软件的安装:硬件安装完成之后启动电脑,把随卡配带的小光盘放到电脑的光驱上,打开光盘,把光盘里面的所有文件都复制到电脑上。

打开“install”,图标为:,显示安装信息的页面,如下图:在显示的页面上先点第一个安装采集卡驱动,驱动安装完成之后会提示驱动安装完成,再点击第二个选项安装数字监控软件,安装完成之后会在电脑桌面形成一个快捷图标,如图:3、软件的启动,在电脑桌面上打开摄像机的图标,在显示的页面上输入软件的登录用户名和密码(软件默认用户名和密码都是:admin),如图:输入软件的登录用户名和密码之后,点界面右下角的绿色对勾,就可以打开监控软件,如驱动以及电脑的配置正常,同时接上了摄像机之后就会显示监控画面,如下图:远程监控电脑设置:关闭电脑防火墙,打开电脑的控制面板,在控制面板上双击打开防火墙,用鼠标左键将选项设置点到关闭,确定保存完成操作,如图:路由器设置:以当前使用的TP-LINK路由器为例,在电脑浏览器地址栏里面输入路由器的连接网关192.168.1.1(路由器登陆的网关一般情况下有两个,分别是:192.168.1.1和192.168.0.1,登陆网关以客户当前使用的路由器为准。

),在弹出的路由器登陆框里面输入登陆的用户名和密码点登陆,进到路由器的设置界面,如下图:在路由器的设置界面里面选中“转发规则”,在下拉列表里面再选中“Upnp设置”,将Upnp设置里面的状态改成“开启”状态,如图:如果路由器的upnp设置功能起作用或是开启成功,会在upnp设置列表里面显示监控设备的信息,表示监控设备自动映射成功,如下图:远程连接:路由设置完成之后,在浏览器地址栏里面输入服务器远程登陆界面的地址:连接到服务器的登陆界面,如图:备注:一般情况下打开网页变会自动安装activex控件,如果特殊情况不能正常安装,请按照以下指示调整浏览器设置。

PCIe采集卡使用手册说明书

03安全性须知04硬件安装05驱动安装07属性07设备信息09时序13OSD14HDMI15视频18输入26输出格式26Video Crossbar 目录2安全性须知电气方面的安全性操作方面的安全性为避免可能的电击造成严重损害,在搬动计算机主机之前,请先将计算机电源线暂时从电源插座中移除。

■当您要加入硬件装置到系统中或者要移除系统中的硬件装置时,请务必先连接或移除该装置的信号线,然后再连接或移除电源线。

建议在安装硬件装置之前先移除计算机的电源线。

■当您要从主板连接或移除任何的信号线之前,请确定所有的电源线已事先移除。

■在使用硬件卡或扩展卡之前,我们建议您可以先寻求专业人士的协助。

这些装置有可能会干扰接地的回路。

■请确定电源的电压设定已调整到本国/本区域所使用的电压标准值,若您不确定您所属区域的供应电压值多少,那么请就近询问当地的电力公司人员。

■如果电源已损坏,请不要尝试自己修复。

请将之交给专业技术服务人员或经销商来处理。

■在您安装视频采集卡以及加入硬件装置之前,请务必详细阅读本手册提供的相关信息。

■在使用产品之前,请确定所有的排线、电源线都已正确地连接好。

若您发现产品有任何重大的瑕庇,请尽速联系您的经销商。

■为避免发生电气短路情况,请务必妥善保管所有备用螺丝、回形针及其他零件,不要遗留在视频采集卡上或计算机主机中。

■灰尘、湿气以及剧烈的温度变化都会影响视频采集卡的使用寿命,因此,请尽量避免在类似环境中放置、使用。

■请勿将计算机主机放置在容易摇晃的地方。

■若在本产品的使用上有任何的技术性问题,请和经过检定或有经验的技术人员联系。

■3(a)机箱内主板示意图(b)机箱内主板上插上采集卡后的示意图操作步骤1. 关闭计算机电源,拔除电源线。

2. 移除机箱盖,找到 PCI Express 插槽,如图 (a)。

3. 移除您要安装视频采集卡的扩展槽上的槽位盖。

4. 将视频采集卡插入扩展槽直到牢牢插入,如图 (b)。

研华板卡参数说明

研华板卡参数说明 Modified by JACK on the afternoon of December 26, 2020研华采集卡参数说明摘要:数据采集卡名目繁多、类型丰富,功能强大,很多数据采集卡不仅具有模拟量的输入、输出功能,同时也具有开关量的输入、输出功能和其他很多特殊功能。

这些数据采集卡能满足绝大多数检测与控制系统中数据采集要求。

熟悉与数据采集卡向光的技术指标和技术术语,对理解数据采集卡的工作原理并正确地做出选型,具有十分重要的意义。

下面以研华数据采集卡来说明一)模拟量输入1、通道数(Channels)通道数指可同时采集模拟量的个数,例如在温度场实验中,我们需要检测6个不同物理位置的温度,这时就需要在6个不同位置安装温度传感器,每一个传感器都会输出自己位置的温度信号,数据采集卡就至少需要6个AD转换器,来满足系统检测的要求。

绝大多数数据采集卡上只有一个AD转换器,通过使用模拟开关来分时采集不同通道的数据,从而得到多通道的数据采集卡。

2、分辨率(Resolution)一般数据采集卡的分辨率也是该设备中AD转换器的分辨率,大多数数据采集设备采用逐次比较型AD转换器,分辨率一般有8位、10位、12位和16位,目前大多数数据采集卡都具有12位和16位两种分辨率。

12位的分辨率可以分辨,满程电压的1/4096,16位可以分辨满程电压的1/65536。

3、精度精度是指数据采集卡在满量程范围内任意一点的输出值相对于其理想值之间的偏离程度。

数据采集卡的精度受卡上放大倍数的影响比较大,一般厂商给出的数据采集卡的精度指标都很高,12位AD采集卡的精度在满程输入电压(FSR)的%+1LSB,但在实际检测过程中,受到很多因素,特别是外部电磁干扰信号,电源干扰和传感器噪声等影响因素的限制,检测的精度往往达不到这样的水平。

在实际应用中,干扰严重的环境可能使采样结果与厂商标称的精度相差甚远,在弱信号(例如热电偶信号)和高阻抗输出信号(例如压电陶瓷传感器、锆氧传感器输出信号)的才集中尤其如此,原因是逐次比较型AD采集的是微秒级时刻的电信号,而实际输入的信号是传感器输出信号与干扰信号的叠加,在这些干扰信号中,工频干扰信号是比较普遍的,防止工频干扰信号比较有效的方法是与工频信号同步,在工频周期时间内连续采集若干个信号取平均值,这样操作会降低实际的采样速度,在不需要高速采集但要求高精度采样的情况下可以得到比较好的效果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MP424

wwlab 2007/5 ☐USB2.0总线AD采集模块☐4路并行12位 AD

☐开关量:8DI/8DO

使用手册

✧VB编程需要的声明模块程序MP424.bas。

☐MP424.EXE:测试程序。

☐在光盘的\USB\MP424\Delphi目录中包含:

✧Delphi的编程例子

驱动安装

安装方法:

1.将MP424插入一个USB接口。

安装的模块的设备号为“0”。

2.Windows将会显示找到新硬件,可按找到新硬件向导进行下一步

3.选择不搜索软件

4.下一步,选择从列表指定位置安装

5.选择不要搜索,我自己安装驱动

6.下一步,选择从磁盘安装,并指定目录(光盘:\USB\MP424\DRIVER\MP424.INF),找到MP424.inf文件,进行安装

7.Windows将显示完成添加/删除硬件向导,单击完成即可完成安装过程。

安装后,程序自动将MP424.dll动态链接库程序拷贝到

前工作目录中。

驱动安装完毕后在\控制面板\系统\设备管理中的。