FPGA学习步骤30页

FPGA入门培训教材共45张PPT课件

# STEP#4: run router, report actual utilization and timing, write checkpoint design, run drc, write verilog and xdc out route_design write_checkpoint -force $outputDir/post_route report_timing_summary -file $outputDir/post_route_timing_summary.rpt report_timing -sort_by group -max_paths 100 -path_type summary -file $outputDir/post_route_timing.rpt report_clock_utilization -file $outputDir/clock_util.rpt report_utilization -file $outputDir/post_route_util.rpt report_power -file $outputDir/post_route_power.rpt report_drc -file $outputDir/post_imp_drc.rpt write_verilog -force $outputDir/bft_impl_netlist.v write_xdc -no_fixed_only -force $outputDir/bft_impl.xdc

FPGA学习步骤

FPGA学习步骤FPGA(Field Programmable Gate Array)是一种可编程的数字逻辑设备,具有强大的计算能力和灵活性。

学习FPGA涉及多个方面的知识和技能,以下是一个学习FPGA的步骤。

1.学习数字电路基础知识:学习数字逻辑、组合逻辑、时序逻辑、时钟域等基础知识。

了解逻辑门、多路选择器、编码器、解码器等基础组件的工作原理和常见应用。

2. 学习HDL语言:FPGA设计通常使用硬件描述语言(HDL)进行,如VHDL或Verilog。

学习HDL语言的基本语法、数据类型、运算符以及模块化设计方法。

掌握HDL语言的基本语法和常用语句,能够编写简单的模块。

同时,了解设计模块之间的连接和通信方式。

3. 熟悉开发工具:选择一款FPGA开发工具,如Xilinx ISE、Altera Quartus等,并熟悉其使用方法。

掌握工具的安装、项目的创建、仿真、烧写等基本操作。

了解工具中提供的IP核和库函数,以及如何使用这些资源来简化设计过程。

4.学习FPGA体系结构:了解FPGA的基本组成元件和工作原理,包括可编程逻辑单元(PLU)、片上存储器(BRAM)和片上时钟管理等。

熟悉FPGA的时序特性和时钟域设计方法,掌握时钟驱动设计的原则和技巧。

5.设计简单的数字逻辑电路:从简单的数字逻辑电路开始,如全加器、加法器、乘法器等。

通过HDL语言编写这些电路的设计和仿真测试,然后在FPGA上实现并验证电路功能。

通过不断实践,加深对数字逻辑电路设计和FPGA实现的理解。

6.学习FPGA高级应用:掌握FPGA高级应用的设计方法,如时序逻辑设计、状态机设计、数据通路设计等。

了解时分复用(TDM)、频分复用(FDM)、空分复用(SDM)等常用数据传输方式的原理。

学习高级FPGA设计技术,如流水线设计、多周期设计、并行设计等。

7.学习FPGA外设接口:了解FPGA的外设接口标准,如UART、SPI、I2C、PCIe等,以及各种外设的工作原理和接口电路设计。

fpga入门培训例程

fpga入门培训例程欢迎大家参加本次FPGA入门培训,本例程将介绍FPGA的基本知识和使用方法,并提供一些实例让大家进行实践和学习。

希望通过本次培训,能够帮助大家快速入门FPGA,并享受到这项技术带来的乐趣和创造力。

一、FPGA简介FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,具有灵活性高、可重构性好的特点。

通过在FPGA芯片内部配置可编程逻辑门和连接方式,可以实现各种数字电路的设计与实现。

相比其他可编程器件如微控制器和DSP,FPGA在高速数据处理、并行计算等方面具有优势。

二、FPGA入门准备在开始学习FPGA之前,我们需要准备一些必要的软硬件设备:1. 开发板:选择一块适合入门的FPGA开发板作为学习平台。

常见的开发板有Xilinx、Altera等品牌,在价格和功能上有所区别,初学者可以选择价格适中的开发板。

2. 开发环境:安装并配置开发环境,常见的开发环境有Xilinx ISE、Quartus II等软件。

根据所选开发板的不同,选择相应的开发环境。

3. 资源学习:查找合适的FPGA学习资源,如书籍、文档、网络教程等。

这些资源将帮助你理解FPGA的原理和开发流程。

三、FPGA入门步骤1. 学习FPGA基础知识:了解FPGA的结构、原理以及其与传统硬件的区别。

熟悉FPGA的编程语言,如VHDL或Verilog,并学习其语法和基本设计原则。

2. 设计简单电路:选择一个简单的电路设计进行学习和实践。

例如,使用FPGA实现一个加法器或计数器。

通过这些简单的电路设计,你可以熟悉FPGA的开发流程和工具的使用。

3. 深入学习:学习更复杂的FPGA设计,如状态机、数值处理等。

尝试设计并实现一个功能完善的电路,以锻炼你的设计能力和解决问题的能力。

4. 加载到FPGA开发板:将设计好的电路加载到FPGA开发板上进行实验。

通过实际测试,检验你的设计是否符合预期,并对其性能进行评估和优化。

FPGA开发入门教程

FPGA开发入门教程FPGA(Field-Programmable Gate Array)是一种可重新配置的集成电路,能够根据用户需求实现不同的功能。

作为硬件开发的重要技术之一,FPGA具有灵活性高、性能强、功耗低等优点,因此受到了广泛的关注和应用。

本文将介绍FPGA开发的入门教程,帮助初学者快速上手FPGA开发。

第一步:了解FPGA第二步:选择开发工具和开发板FPGA开发需要选择合适的开发工具和开发板。

常用的FPGA开发工具有Xilinx的Vivado和Altera的Quartus等。

这些工具提供了图形化界面以及一些示例代码,方便用户进行开发和调试。

开发板是用户在FPGA开发中搭建硬件平台的重要部分,通过开发板可以将FPGA芯片与其他外设相连接,进行实际的验证和测试。

选择开发工具和开发板时要考虑到自己的需求和预算。

第三步:学习HDL编程语言HDL(Hardware Description Language)是用于描述数字电路的编程语言,FPGA开发中常用的HDL有Verilog和VHDL。

要掌握FPGA开发,我们必须学习和熟悉HDL编程语言。

HDL语言可以描述数字电路的结构、功能和时序等信息,通过HDL编写的代码可以被FPGA开发工具转化成对应的硬件电路。

学习HDL编程语言需要掌握其语法规则和基本概念,理解时序逻辑和组合逻辑的原理,并通过练习和实践进行巩固。

第四步:学习FPGA开发流程第五步:完成第一个FPGA项目通过以上几个步骤的学习和实践,我们已经具备了进行FPGA开发的基本能力。

接下来我们可以尝试完成一个简单的FPGA项目,例如实现一个LED闪烁的功能。

我们可以使用HDL语言编写一个简单的计数器,将计数值输出到FPGA开发板上的LED灯,通过改变计数值的频率实现LED的闪烁。

完成这个项目可以加深对FPGA开发流程的理解,并为后续更复杂的项目奠定基础。

总结FPGA开发入门需要掌握FPGA的基本概念和工作原理,选择合适的开发工具和开发板,学习HDL编程语言,了解FPGA开发流程,并通过实践完成一个简单的FPGA项目。

怎么学习FPGA?菜鸟学习FPGA的步骤

怎么学习FPGA?菜鸟学习FPGA的步骤一、入门首先要掌握HDL(HDL=verilog+VHDL)。

第一句话是:还没学数电的先学数电。

然后你可以选择verilog或者VHDL,有C语言基础的,建议选择VHDL。

因为verilog太像C 了,很容易混淆,最后你会发现,你花了大量时间去区分这两种语言,而不是在学习如何使用它。

当然,你思维能转得过来,也可以选verilog,毕竟在国内verilog用得比较多。

接下来,首先找本实例抄代码。

抄代码的意义在于熟悉语法规则和编译器(这里的编译器是硅编译器又叫综合器,常用的编译器有:Quartus、ISE、Vivado、Design Compiler 、Synopsys的VCS、iverilog、LatTIce的Diamond、Microsemi/Actel的Libero、Synplify pro),然后再模仿着写,最后不看书也能写出来。

编译完代码,就打开RTL图,看一下综合出来是什么样的电路。

HDL是硬件描述语言,突出硬件这一特点,所以要用数电的思维去思考HDL,而不是用C语言或者其它高级语言,如果不能理解这句话的,可以看《什么是硬件以及什么是软件》。

在这一阶段,推荐的教材是《Verilog传奇》、《Verilog HDL高级数字设计》或者是《用于逻辑综合的VHDL》。

不看书也能写出个三段式状态机就可以进入下一阶段了。

此外,你手上必须准备Verilog或者VHDL的官方文档,《verilog_IEEE官方标准手册-2005_IEEE_P1364》、《IEEE Standard VHDL Language_2008》,以便遇到一些语法问题的时候能查一下。

二、独立完成中小规模的数字电路设计。

现在,你可以设计一些数字电路了,像交通灯、电子琴、DDS等等,推荐的教材是《Verilog HDL应用程序设计实例精讲》。

在这一阶段,你要做到的是:给你一个指标要求或者时序图,你能用HDL设计电路去实现它。

FPGA学习步骤

FPGA学习步骤FPGA(Field-Programmable Gate Array)是可编程逻辑器件的一种,它具有高度可编程性和灵活性,被广泛应用于数字电路设计和嵌入式系统开发。

学习FPGA可以使我们了解数字电路的原理和设计方法,并能够利用FPGA开发和优化各种应用。

下面是一个FPGA学习的步骤,帮助你逐步了解FPGA的原理和应用。

步骤1:掌握数字电路基础知识FPGA是用于设计数字电路的器件,因此首先需要掌握数字电路的基础知识。

学习数字电路的基本逻辑门、布尔代数和组合逻辑电路等概念,理解时序电路、存储器和状态机等高级概念。

步骤2:了解FPGA的原理和架构学习FPGA的原理和架构有助于理解FPGA是如何实现数字电路的。

学习FPGA的片上资源,如查找表、触发器和运算器等,以及FPGA的内部连接结构。

还可以探索FPGA的编程方式,包括寄存器传输级综合(RTL)和硬件描述语言(HDL)等。

步骤3:学习硬件描述语言(HDL)硬件描述语言是FPGA设计的基础,通常使用的HDL是Verilog和VHDL。

学习HDL的语法和基本结构,并掌握如何使用HDL描述数字电路。

可以通过书籍、在线教程和实践项目等方式学习HDL。

步骤4:使用FPGA开发工具步骤5:完成简单的FPGA设计项目开始进行一些简单的FPGA设计项目,如实现基本的逻辑门、组合逻辑电路和时序电路等。

通过这些项目,学会如何使用HDL描述和实现数字电路,如何利用FPGA的资源和工具进行设计和优化。

步骤6:进阶学习FPGA应用进一步学习FPGA的应用,例如数字信号处理(DSP)、图像处理、通信系统和嵌入式系统等。

根据自己的兴趣和需求选择相应的应用领域,并实践相关项目。

学习如何使用FPGA实现更复杂的功能和算法,并了解相应的设计方法和技术。

步骤7:参加竞赛或项目参加FPGA设计竞赛或实际项目有助于提升自己的FPGA设计能力。

通过参赛或项目,可以锻炼自己的团队合作能力和解决问题的能力,并将学到的知识应用到实际应用中。

FPGA初级入门课程

仿真:使用 Ve r i l o g 仿 真 工具对网表文 件进行仿真, 验证设计是否 符合预期。

综合:使用 Ve r i l o g 综 合 工具将网表文 件综合成门级 网表,用于后 续布局布线和

实现。

布局布线:使 实现:使用 用Verilog布 Verilog实现 局布线工具对 工具将物理级 门级网表进行 网表实现成具 布局布线,生 体的FPGA器 成物理级网表。 件,完成设计。

下载与配置

下

载

FPGA开

发工具

安

装

FPGA开

发工具

配

置

FPGA开

发环境

导

入

FPGA设

计文件

编

译

FPGA设

计文件

下

载

FPGA配

置文件到

目标板

Part Six

FPGA应用实例

LED闪烁控制实例

添加标题

硬件需求:FPGA开发板、LED灯、电阻

添加标题

软 件 需 求 : F P G A 开 发 环 境 、 Ve r i l o g 语 言

添加标题

扩展应用:可以扩展到其他LED控制应用,如LED条形图、LED点阵显示等

数码管显示实例

数码管简介:由多个发光二极管组成,用于显示数字和字符 数码管驱动:FPGA通过控制数码管的阳极和阴极来显示不同的数字和 字符 实例一:使用FPGA实现数码管动态显示,如倒计时、时钟等

实例二:使用FPGA实现数码管字符显示,如显示文字、图标等

仿真验证:使用仿真工具, 对VHDL代码进行仿真验 证

综合优化:对VHDL代码 进行综合优化,提高性能 和可靠性

布局布线:将优化后的 VHDL代码布局布线到 FPGA芯片上

FPGA学习步骤

第一步:学习了解FPGA结构,FPGA到底是什么东西,芯片里面有什么,不要开始就拿个开发板照着别人的东西去编程。

很多开发板的程序写的很烂,我也做过一段时间的开发板设计,我觉得很大程度上,开发板在误人子弟。

不过原厂提供的正品开发板,代码很优秀的,可以借鉴。

只有了解了FPGA 内部的结构才能明白为什么写Verilog和写C整体思路是不一样的。

第二步:掌握FPGA设计的流程。

了解每一步在做什么,为什么要那么做。

很多人都是不就是那几步吗,有什么奇怪的?呵呵,我想至少有一半以上的人不知道synthesize和traslate的区别吧。

了解了FPGA的结构和设计流程才有可能知道怎么去优化设计,提高速度,减少资源,不要急躁,不要去在为选择什么语言和选择哪个公司的芯片上下功夫。

语言只是一个表达的方式,重要的是你的思维,没有一个好的指导思想,语言用得再好,不过是个懂语言的人。

第三步:开始学习代码了。

我建议要学代码的人都去Altera或Xilinx的网站上下原厂工程师的代码学习。

不要一开始就走入误区。

fpga自学流程

fpga自学流程FPGA(现场可编程门阵列)是一种可编程逻辑器件,具有广泛的应用领域,包括计算机科学、电子工程、通信等。

如果你对FPGA感兴趣,并希望自学这一领域,下面是一些流程和步骤,帮助你开始学习。

1. 学习数字电子学基础知识:在开始学习FPGA之前,了解数字电子学的基础知识非常重要。

这包括数字电路、逻辑门、组合逻辑和时序逻辑等内容。

有了这些基础知识,你将更好地理解FPGA的工作原理和应用。

2. 学习HDL(硬件描述语言):HDL是用于描述FPGA设计的语言,常见的HDL包括VHDL和Verilog。

选择一种HDL语言,并系统地学习它。

掌握HDL将使你能够描述和设计FPGA电路,并能将其实现在硬件上。

3. 学习FPGA开发工具和平台:学习并熟悉FPGA开发工具和平台是必不可少的一步。

常用的FPGA开发工具包括Xilinx的Vivado和Altera的Quartus等。

这些工具提供了设计、仿真和综合FPGA电路所需的环境和工具。

4. 完成入门项目:在开始复杂的FPGA设计之前,先从一些入门级项目开始。

这些项目旨在帮助你熟悉FPGA开发流程和基本的电路设计。

一些常见的入门项目包括LED闪烁、数码管显示和按钮输入等。

5. 深入学习FPGA设计技术:一旦你完成了入门项目,就可以开始深入学习更高级的FPGA设计技术。

学习如时钟管理、状态机设计、并行处理和通信接口等高级概念。

还可以尝试设计更复杂的项目,如数字信号处理和图像处理等。

6. 参与在线社区和论坛:在学习过程中,参与在线FPGA社区和论坛可以帮助你与其他FPGA爱好者交流经验和获取实际指导。

在这些平台上,你可以提问问题、分享项目经验,并从其他人的经验中学习。

7. 实践和不断练习:FPGA是一门实践性很强的学科,通过实践和不断练习你的技能将得以提高。

尝试设计不同类型的项目,并挑战自己解决问题的能力。

通过不断实践和尝试,你会逐渐成为一位熟练的FPGA工程师。

FPGA入门资料

FPGA的学习流程FPGA作为一个技术含量高的器件,让许多学单片机的人望而生畏,也有许多的初学者很关心FPGA到底该怎样来学,下面发表一下本人的浅见,不对的地方还请各位大侠指点指点.我认为学习FPGA可分为以下三个步骤:第一步:学好硬件描述语言。

以夏宇闻那本书为教材,一般都要2到3个星期,有C语言基础入门更快,还要做一些练习,巩固语法。

第二步:针对一款硬件来学习,这一步非常重要,一般需要1~3个月,这个过程遇到的问题往往是最多的,因此要有恒心与耐力,遇到问题可以找老师或者上论坛求教.第三步:融会贯通。

有了以上的基础,这时候就要看一个人的知识背景了,把你的专业与FPGA相结合,如果你数学比较好,就可以去做算法如果你通信方面比较好,就可以做通信方面的东西,如果你高频比较好,就可以做射频方面的东西,等等。

FPGA学习、发展方向自从接触和认识FPGA以后,自由电子科技坚定的选择了FPGA器件作为我们创新和实现自身价值的承载平台,对此,我想从以下几个方面介绍一下。

1. 对FPGA的认识,为什么要选择FPGA现在的FPGA器件在电子行业中是一颗明星,这是一种正在不断采用新的半导体制造工艺,逻辑容量不断增加,应用领域不断拓展,器件成本不断下降的器件,FPGA厂商激烈的竞争使开发软件和方法不断的进步,是一个正在盘古开天时期的事物。

很多人对此的解释是FPGA拥有很大的灵活性,在半导体制造工艺的NRE不断增加、应用需求不断变更、品种要求多而数量要求少的现实情况下,FPGA是一个最佳选择,这正是现在FPGA厂商们宣传时耳目能详的陈词。

我们认为,FPGA在电子产业和信息产业上的地位并不是这么简单。

实际上如果通过我们对计算机发展的历史、软件发展历史的认识,可以推断FPGA器件是一方向性的创新,几千年以前我国的祖先们感悟了蕴涵在简单的阴、阳中的事理有了太极,阴阳可以生万物。

一百多年前的布尔代数使我们从数学上有了坚实的基础,从机械计算机到电子计算机的演变中,我们得到了冯.诺依曼型的程序存储类的计算机体系,并在当代发展为及至,极大的推动了人类社会的前进。

FPGA学习笔记(二)——FPGA学习路线及开发流程

FPGA学习笔记(⼆)——FPGA学习路线及开发流程###### 【该随笔部分内容转载⾃⼩梅哥】 #########⼀、FPGA学习路线 ⼯具使⽤ -> 语法学习 -> 逻辑设计 -> IP使⽤ ->接⼝设计 -> 时序分析 -> ⽚上系统1、⼯具使⽤ Altera:Quartus II Xlinx: Vivado2、语法学习 Verilog HDL(FPGA设计的是电路)3、逻辑设计 组合逻辑:多路选择器、加法器、译码器、乘法器 ······· 时序逻辑:计数器、分频器、移位寄存器、定时器 ······· 接⼝逻辑:UART,CAN,SPI,LVDS ······ 状态机,线性序列机4、IP使⽤ 计数器、IO、FFT、各种软核CPU(MC8051)·······5、接⼝设计 Avalon ST、Avalon MM、FSMC和FPGA6、时序分析 时序分析和时序约束7、⽚上系统 SOPC: 使⽤FPGA通⽤逻辑搭建CPU和外围设备电路 Intel: NIOS II 软核CPU,ARM CortexA9硬核 Xilinx: MicroBlaze软核CPU,PowerPC硬核,硬核ARM CortexA9 MCS8051、开源软核CPU、CortexM0⼆、FPGA开发流程 1、设计定义 2、设计输⼊(verilog、原理图) 3、分析和综合 4、功能仿真(modelsim) 5、布局布线 6、时序仿真 7、IO分配及配置⽂件的⽣成 8、配置(烧写FPGA) 9、在线调试三、⼯程模板 1、Quartus IIprj ----- ⼯程⽂件存放⽬录(ip⽂件夹存放⽣成的ip核⽂件)rtl ----- verilog可综合代码img ----- 设计相关图⽚存放⽬录(⽅便写⽂档)doc ----- 设计相关⽂档存放⽬录testbench ----- 对应的testbench仿真测试⽂件存放⽬录 2、Vivado 使⽤Vivado软件⽐较⽅便,直接指定存放⼯程⽬录就可以,源⽂件和测试⽂件会⾃动分类存放在⼦⽂件夹下:。

FPGA入门教程word精品文档20页

FPGA入门教程1.数字电路设计入门2.FPGA简介3.FPGA开发流程4.RTL设计5.QuartusⅡ设计实例6. ModelSim和Testbench1.数字电路设计入门1.1数字电路设计数字电路设计的核心是逻辑设计。

通常,数字电路的逻辑值只有‘1’和‘0’,表征的是模拟电压或电流的离散值,一般‘1’代表高电平,‘0’代表低电平。

高低电平的含义可以理解为,存在一个判决电平,当信号的电压值高于判决电平时,我们就认为该信号表征高电平,即为‘1’。

反之亦然。

当前的数字电路中存在许多种电平标准,比较常见的有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVDS、HSTL、SSTL等。

这些电平的详细指标请见《补充教程1:电平标准》。

数字电路设计大致可分为组合逻辑电路和时序逻辑电路。

一般的数字设计的教材中对组合逻辑电路和时序逻辑电路的定义分别为:组合逻辑电路的输出仅与当前的输入有关,而时序逻辑电路的输出不但与输入有关,还和系统上一个状态有关。

但是在设计中,我们一般以时钟的存在与否来区分该电路的性质。

由时钟沿驱动工作的电路为时序逻辑电路。

大家注意,这两种电路并不是独立存在的,他们相互交错存在于整个电路系统的设计中。

1.1.1 组合逻辑电路组合逻辑电路由任意数目的逻辑门电路组成,一般包括与门、或门、非门、异或门、与非门、或非门等。

一般的组合逻辑电路如下图:其中A,B,C,D,E,F为输入,G为输出。

1.1.2 时序逻辑电路时序逻辑电路由时钟的上升沿或下降沿驱动工作,其实真正被时钟沿驱动的是电路中的触发器(Register),也称为寄存器。

触发器的工作原理和参数如下图:下面是两个简单的时序逻辑电路例子:(1)、时钟分频电路该时序电路的功能为实现对时钟’clk’的4分频,其中’clk_2’为2分频时钟,’clk_4’为4分频时钟,’enable’为该电路的使能信号。

其功能仿真波形如下图所示:(2)、序列检测器该时序电路实现了一个序列检测器,当输入序列‘datain’中出现‘101’时,标志位F将输出‘1’,其他时刻输出‘0’。

FPGA入门教程

简单地讲,PLD 是这样一种 ASIC(专用集成电路):内部有大量 的门电路,通过软件编程可以实现这些门电路不同的连接关系,从而 整个 PLD 对外就完成了不同的功能,并且这些门电路的连接关系可以 不断用软件来改变。

和单片机比较,PLD 在时序和延迟的实现上不如单片机,但是 PLD 在芯片容量、组合逻辑、工作速度、编程难度以及可以擦写次数上(特 别是 FPGA)远优于单片机;另外还有很重要地一点,PLD 加密性能很 好,具我们所知,目前国内只有 7032LC 系列可以解密,并且费用达 到 3 万,其他都不可以解密,而单片机几千到几万一般都可以解密了。

4

沪生电子

FPGA/CPLD 入门教程(第一章 FPGA/CPLD 概述)

FPGA/CPLD 概述

FPGA(现场可编程门阵列)与 CPLD(复杂可编程逻辑器件)都是可编程 逻辑器件,它们是在 PAL,GAL 等逻辑器件的基础之上发展起来的。同 以往的 PAL,GAL 等相比较,FPGA/CPLD 的规模比较大,它可以替代 几十甚至几千块通用 IC 芯片。这样的 FPGA/CPLD 实际上就是一个子 系统部件。这种芯片受到世界范围内电子工程设计人员的广泛关注和 普遍欢迎。经过了十几年的发展,许多公司都开发出了多种可编程逻 辑器件。比较典型的就是 Xilinx 公司的 FPGA 器件系列和 Altera 公 司的 CPLD 器件系列,它们开发较早,占用了较大的 PLD 市场。通常 来说,在欧洲用 Xilinx 的人多,在日本和亚太地区用 ALTERA 的人多, 在美国则是平分秋色。全球 PLD/FPGA 产品 60%以上是由 Altera 和 Xilinx 提供的。可以讲 Altera 和 Xilinx 共同决定了 PLD 技术的发 展方向。当然还有许多其它类型器件,如:Lattice,Vantis,Actel, Quicklogic,Lucent 等。 (99 年 Lattice 收购了 Vantis,成为第 三大 PLD 供应商;同年 Xilinx 收购了 Philips 的 PLD 部门)

我的FPGA学习步骤

目录我的FPGA学习步骤 (1)第一步了解FPGA (1)1.1 FPGA概念 (1)1.2 FPGA结构 (1)1.3 FPGA如何工作 (2)1.4 FPGA内部各模块功能 (2)1.5遗留问题 (4)第二步FPGA开发流程 (4)第三步学习Verilog语言 (6)第四步开发板学习 (6)我的FPGA学习步骤第一步了解FPGA1.1FPGA概念FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

1.2 FPGA结构FPGA的基本结构FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个新概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。

现场可编程门阵列(FPGA)是可编程器件,与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构。

1.3 FPGA如何工作FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。

FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。

FPGA是由存放在片内RAM中的程序来设置其工作状态的,因此,工作时需要对片内的RAM进行编程。

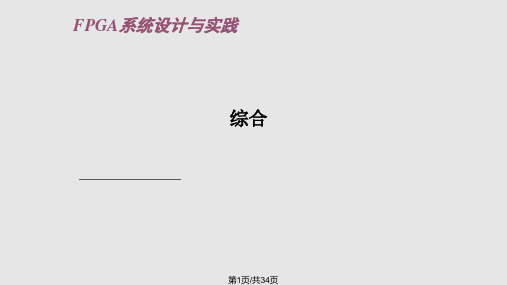

FPGA详细教程综合PPT课件

第15页/共34页

综合属性

• (5)全局优化目标(Global Optimization Goal)

•

全局优化目标参数仅对FPGA有效,它用于一些时钟优化策略,包括的

优化属性有:

FPGA系统设计与实践

综合

第1页/共34页

第五章 综合

内容提要

•

本章介绍了Xilinx公司的中的综合工具XST的综合属性、HDL代码参数

设置、专用参数选项设置,使用XST综合设计、实行设计的步骤与方法。集成

的 下 载 配 置 工 具 iMPACT 的 结 构 、 操 作 步 骤 与 方 法 。Altera 公 司 的Qua 编 译 器

•

ISE中XST设计流程的综合阶段约束文件与实现阶段约束文件的概念并不分明,

综合阶段的约束条件常常通过实现阶段的约束文件来完成。

第7页/共34页

5.1 中的综合工具XST

•

XST的综合约束文件是XCF(XST Constrain File),而

在 布 局 布 线 阶 段 , 最 重 要 的 约 束 文 件 是 用 户 约 束 文 件 UCF(User Constraint File),两者有着千丝万缕的关系,UCF几乎支持XCF的所有约束语言与命令。通常 在使用XST综合流程时,仅仅通过综合属性设置来设置全局性的综合策略与参数,细 化的约束是通过实现阶段的约束文件UCF完成的。

注意综合、实行、配置或者编译与编程中属性参数的设置对设计的影响。应通过

大量的实际设计过程加深对综合、实行、配置或者编译与编程的理解。

第4页/共34页

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA学习步骤,我的体会FPGA在目前应用领域非常,在目前的单板设计里面,几乎都可以看到它的身影。

从简单的逻辑组合,到高端的图像、通信协议处理,从单片逻辑到复杂的ASIC原型验证,从小家电到航天器,都可以看到FPGA应用,它的优点在这里无庸赘述。

从个人实用角度看,对于学生,掌握FPGA可以找到一份很好的工作,对于有经验的工作人员,使用fgpa可以让设计变得非常有灵活性。

掌握了fpga的设计,单板硬件设计就非常容易(不是系统设计),特别是上大学时如同天书的逻辑时序图,看起来就非常亲切。

但fpga的入门却有一定难度,因为它不像软件设计,只要有一台计算机,几乎就可以完成所有的设计。

fpga的设计与硬件直接相关,需要实实在在的调试仪器,譬如示波器等。

这些硬件设备一般比较昂贵,这就造成一定的入门门槛,新人在入门时遇到一点问题或者困难,由于没有调试设备,无法定位问题,最后可能就会放弃。

其实这时如果有人稍微指点一下,这个门槛很容易就过去。

我用FPGA做设计很多年了,远达不到精通的境界,只是熟悉使用,在这里把我对fpga的学习步骤理解写出来,仅是作为一个参考,不对的地方,欢迎大家讨论和指正。

1、工欲善其事,必先利其器。

计算机必不可少。

目前FPGA应用较多的是Altera 和xilinx这两个公司,可以选择安装quartusII或者ISE软件。

这是必备的软件环境。

硬件环境还需要下载器、目标板。

虽然有人说没有下载器和目标板也可学习fpga,但那总是纸上谈兵。

这就像谈女朋友,总是嘴上说说,通个电话,连个手都没牵,能说人家是你朋友?虽说搭建硬件环境需要花费,但想想,硬件环境至多几百元钱,你要真的掌握FPGA的设计,起薪比别人都不止高出这么多。

这点花费算什么?2、熟悉verilog语言或者vhdl语言,熟练使用quartusII或者ISE软件。

VHDL和verilog各有优点,选择一个,建议选择verilog。

熟练使用设计软件,知道怎样编译、仿真、下载等过程。

起步阶段不希望报一些培训班,除非你有钱,或者运气好,碰到一个水平高、又想把自己的经验和别人共享的培训老师,不然的话,培训完后总会感觉自己是一个冤大头。

入门阶段可以在利用网络资源完成。

3、设计一个小代码,下载到目标板看看结果此时可以设计一个最简答的程序,譬如点灯。

如果灯在闪烁了,表示基本入门了。

如果此时能够下载到fpga 外挂的flash,fpga程序能够从flash启动,表明fpga的最简单设计你已经成功,可以到下一步。

4、设计稍微复杂的代码,下载到目标板看看结果。

可以设计一个UART程序,网上有参考,你要懂RS232协议和fpga内置的逻辑分析仪。

网上下载一个串口调试助手,调试一番,如果通信成功了,恭喜,水平有提高。

进入下一步。

5、设计复杂的代码,下载到目标板看看结果。

譬如sdram的程序,网上也有参考,这个设计难度有点大。

可用串口来调试sdram,把串口的数据存储到sdram,然后读回,如果成功,那你就比较熟悉fpga的设计饿了6、设计高速接口,譬如ddr2或者高速串行接口这要对fpga的物理特性非常了解,而且要懂得是时序约束等设计方法,要看大量的原厂文档,这部分成功了,那就对fpga的物理接口掌握很深,你就是设计高手了7、设计一个复杂的协议譬如USB、PCIexpress、图像编解码等,锻炼对系统的整体把握和逻辑划分。

完成这些,你就是一个一流的高手、8、学习再学习学习什么,我也不知道,我只知道“学无止境,山外有山”。

上述只是一些简单的学习步骤,希望能对大家有所帮助!Verilog经验谈规范很重要工作过的朋友肯定知道,公司里是很强调规范的,特别是对于大的设计(无论软件还是硬件),不按照规范走几乎是不可实现的。

逻辑设计也是这样:如果不按规范做的话,过一个月后调试时发现有错,回头再看自己写的代码,估计很多信号功能都忘了,更不要说检错了;如果一个项目做了一半一个人走了,接班的估计得从头开始设计;如果需要在原来的版本基础上增加新功能,很可能也得从头来过,很难做到设计的可重用性。

在逻辑方面,我觉得比较重要的规范有这些:1.设计必须文档化。

要将设计思路,详细实现等写入文档,然后经过严格评审通过后才能进行下一步的工作。

这样做乍看起来很花时间,但是从整个项目过程来看,绝对要比一上来就写代码要节约时间,且这种做法可以使项目处于可控、可实现的状态。

2.代码规范。

a.设计要参数化。

比如一开始的设计时钟周期是30ns,复位周期是5个时钟周期,我们可以这么写:parameter CLK_PERIOD = 30;parameter RST_MUL_TIME = 5;parameter RST_TIME = RST_MUL_TIME * CLK_PERIOD;...rst_n = 1'b0;# RST_TIME rst_n = 1'b1;...# CLK_PERIOD/2 clk <= ~clk;如果在另一个设计中的时钟是40ns,复位周期不变,我们只需对CLK_PERIOD进行重新例化就行了,从而使得代码更加易于重用。

b.信号命名要规范化。

1) 信号名一律小写,参数用大写。

2) 对于低电平有效的信号结尾要用_n标记,如rst_n。

3) 端口信号排列要统一,一个信号只占一行,最好按输入输出及从哪个模块来到哪个模块去的关系排列,这样在后期仿真验证找错时后方便很多。

如:module a(//inputclk,rst_n, //globle signalwren,rden,avalon_din, //related to avalon bussdi, //related to serial port input//outputdata_ready,avalon_dout, //related to avalon bus...);4) 一个模块尽量只用一个时钟,这里的一个模块是指一个module或者是一个tity。

在多时钟域的设计中涉及到跨时钟域的设计中最好有专门一个模块做时钟域的隔离。

这样做可以让综合器综合出更优的结果。

5) 尽量在底层模块上做逻辑,在高层尽量做例化,顶层模块只能做例化,禁止出现任何胶连逻辑(glue logic),哪怕仅仅是对某个信号取反。

理由同上。

6) 在FPGA的设计上禁止用纯组合逻辑产生latch,带D触发器的latch的是允,比如配置寄存器就是这种类型。

7) 一般来说,进入FPGA的信号必须先同步,以提高系统工作频率(板级)。

所有模块的输出都要寄存器化,以提高工作频率,这对设计做到时序收敛也是极有好处的。

9) 除非是低功耗设计,不然不要用门控时钟--这会增加设计的不稳定性,在要用到门控时钟的地方,也要将门控信号用时钟的下降沿打一拍再输出与时钟相与。

clk_gate_en -------------------------|D Q |------------------|_out| |-------o|> | |clk | -------- |------------------------------------10)禁止用计数器分频后的信号做其它模块的时钟,而要用改成时钟使能的方式,否则这种时钟满天飞的方式对设计的可靠性极为不利,也大大增加了静态时序分析的复杂性。

如FPGA的输入时钟是25M的,现在系统内部要通过RS232与PC通信,要以rs23 1xclk的速率发送数据。

不要这样做:always (posedge rs232_1xclk or negedge rst_n)begin...而要这样做:always (posedge clk_25m or negedge rst_n) begin...else if ( rs232_1xclk == 1'b1 )...end11)状态机要写成3段式的(这是最标准的写法),即...always @(posedge clk or negedge rst_n)...current_state <= next_state;...always @ (current_state ...)...case(current_state)...s1:if ...next_state = s2;...always @(posedge clk or negedge rst_n)...elsea <= 1'b0;c <= 1'b0;c <= 1'b0; //赋默认值case(current_state)s1:a <= 1'b0; //由于上面赋了默认值,、c赋值了(b、c在该状态为0,不会产生锁存器,下同)s2:b <= 1'b1;s3:c <= 1'b1;default:......3.ALTERA参考设计准则1) Ensure Clock, Preset, and Clear configurations are free of glitc es.2) Never use Clocks consisting of more than one level of combinator al logic.3) Carefully calculate setup times and hold times for multi-Clock s stems.4) Synchronize signals between flipflops in multi-Clock systems whe the setup and hold time requirements cannot be met.5) Ensure that Preset and Clear signals do not contain race conditi ns.6) Ensure that no other internal race conditions exist.7) Register all glitch-sensitive outputs.Synchronize all asynchronous inputs.9) Never rely on delay chains for pin-to-pin or internal delays.10)Do not rely on Power-On Reset. Use a master Reset pin to clear a l flipflops.11)Remove any stuck states from state machines or synchronous logic其它方面的规范一时没有想到,想到了再写,也欢迎大家补充。