应用于saradc中逐次逼近寄存器的设计

分段电容sar adc原理

分段电容sar adc原理

分段电容SAR(Successive Approximation Register) ADC是

一种逐次逼近寄存器ADC的结构,其中电容电荷的分离和逼

近过程通过相继将一对对电容连接到不同的电压源上来实现。

SAR ADC由一系列比特逼近单元(Bit Approximation Unit,BAU)组成,每个BAU都包含一个比较器、一个DAC(数

字模拟转换器)和一个寄存器。

它们按照权重的顺序排列,最高位的BAU具有最高的权重,最低位的BAU具有最低的权重。

SAR ADC的工作原理如下:

1. 初始化:将所有的比特逼近单元初始化为0。

2. 逐位逼近:从最高位(MSB)开始,将DAC输出与输入信

号进行比较。

比较器的输出将根据输入信号与DAC输出的大

小关系确定当前比特的值,并将其存储到寄存器中。

3. 电容分离:根据当前比特的值,将电容连接到相应的电压源上。

如果比特为1,则将电容连接到高电压源,如果比特为0,则将电容连接到低电压源上。

4. 更新DAC输出:根据寄存器中存储的比特值,将DAC的

输出进行更新,以逼近输入信号的大小。

5. 重复以上步骤:对每个比特逼近单元重复执行2-4步,直到

逼近结束。

通过不断的逼近过程,SAR ADC可以在每个时钟周期中逼近

输入信号的值,并将其转换为二进制码输出。

由于它的结构相

对简单,且具有较高的转换精度和速度,SAR ADC被广泛应用于许多领域,如通信、音频和传感器接口等。

逐次逼近型ADC

理解逐次逼近寄存器型ADC:与其它类型ADC 的架构对比Jul 02, 2009摘要:逐次逼近寄存器型(SAR)模数转换器(ADC)占据着大部分的中等至高分辨率ADC市场。

SAR ADC的采样速率最高可达5Msps,分辨率为8位至18位。

SAR架构允许高性能、低功耗ADC采用小尺寸封装,适合对尺寸要求严格的系统。

本文说明了SAR ADC的工作原理,采用二进制搜索算法,对输入信号进行转换。

本文还给出了SAR ADC的核心架构,即电容式DAC和高速比较器。

最后,对SAR架构与流水线、闪速型以及Σ-Δ ADC进行了对比。

引言SAR ADC的架构尽管实现SAR ADC的方式千差万别,但其基本结构非常简单(见图1)。

模拟输入电压(V IN)由采样/保持电路保持。

为实现二进制搜索算法,N位寄存器首先设置在中间刻度(即:100 (00)MSB设置为1)。

这样,DAC输出(V DAC)被设为V REF/2,V REF是提供给ADC的基准电压。

然后,比较判断V IN是小于还是大于V DAC。

如果V IN大于V DAC,则比较器输出逻辑高电平或1,N位寄存器的MSB保持为1。

相反,如果V IN小于V DAC,则比较器输出逻辑低电平,N位寄存器的MSB清0。

随后,SAR控制逻辑移至下一位,并将该位设置为高电平,进行下一次比较。

这个过程一直持续到LSB。

上述操作结束后,也就完成了转换,N位转换结果储存在寄存器内。

图1. 简单的N位SAR ADC架构图2给出了一个4位转换示例,y轴(和图中的粗线)表示DAC的输出电压。

本例中,第一次比较表明V IN < V DAC。

所以,位3置为0。

然后DAC被置为01002,并执行第二次比较。

由于V IN > V DAC,位2保持为1。

DAC置为01102,执行第三次比较。

根据比较结果,位1置0,DAC又设置为01012,执行最后一次比较。

最后,由于V IN > V DAC,位0确定为1。

13位低功耗SAR-SS ADC的研究与设计

13位低功耗SAR-SS ADC的研究与设计13位低功耗SAR-SS ADC的研究与设计引言:随着智能化和物联网的快速发展,对于高分辨率、低功耗的模数转换器(ADC)的需求越来越迫切。

为了满足这一需求,我们进行了13位低功耗逐次逼近寄存器-逐次逼近调整(SAR-SS)ADC的研究与设计。

本文将介绍该ADC的原理、设计方法和性能评估。

一、SAR-SS ADC的原理SAR-SS ADC是一种常见的ADC结构,由逐次逼近寄存器(SAR)和逐次逼近调整(SS)两部分组成。

SAR负责比较电压信号,并通过二分搜索法来得到数字比特。

SS是一种在线的增益校准技术,旨在通过抵消模拟和数字电压的误差来提高ADC的精度。

二、ADC的设计方法1. 比特决策时间的优化为了提高ADC的速度,我们采用了并行比特决策的方法。

通过在每个比特之间引入校准间隙,并行比特决策可以减少比特间的决策时间,从而提高转换速度。

2. 低功耗设计技术为了降低功耗,我们采用了以下设计技术:a) 功耗管理技术:通过有效的电源管理策略,包括引入低功耗模式和限制功耗消耗,实现最低功耗设计。

b) 压缩编码技术:利用压缩编码技术对数据进行编码,从而减少功率消耗。

c) 快速启动技术:通过设计快速启动电路,减少ADC启动时间,从而降低功耗。

三、ADC的性能评估为了评估所设计的ADC的性能,我们进行了以下实验:1. 分辨率测试:通过输入不同幅度的信号,我们测试了ADC 的分辨率,并得到了13位的分辨率。

2. 功耗测试:我们测量了ADC在不同采样频率下的功耗,并且通过对比其他ADC的实验结果,证明了所设计的ADC具有较低的功耗。

3. 精度测试:通过与参考ADC进行比较,我们测试了所设计的ADC的精度。

结果表明,所设计的ADC具有较高的精度。

结论:本文研究了13位低功耗SAR-SS ADC的原理、设计方法和性能评估。

通过优化比特决策时间和采用低功耗设计技术,我们成功地设计了一款功耗低、分辨率高、精度优异的ADC。

简述SAR ADC 的基本操作

简述SAR ADC 的基本操作在要求采样率低于10 MSPS 的应用中,最常见的(模数转换器)之一是SAR (ADC)。

该(AD)C 非常适合需要8-16 位分辨率的应用。

SAR ADC 是最容易理解的模数转换器之一,一旦我们知道这种类型的ADC 的(工作原理),它的优缺点就很明显了。

SAR ADC 的基本操作基本逐次逼近(寄存器)模数转换器如下图所示:SAR ADC 为每个样本执行以下操作:(模拟)(信号)被采样并保持。

对于每一位,SAR 逻辑向(DAC)输出一个二进制代码,该代码取决于正在审查的当前位和已经近似的先前位。

(比较器)用于确定当前位的状态。

逼近所有位后,将在转换结束(EOC) 时输出数字逼近。

SAR 操作最好解释为二分搜索(算法)。

考虑下面显示的代码。

在此代码中,正在审查的当前位设置为1。

由此产生的二进制代码输出到DAC。

这与模拟输入进行比较。

如果从模拟输入中减去DAC 输出的结果小于0,则审查位设置为0。

%8−bit digital output is all ze(ros)digital output = zeros(1,8);%Normalised to one for examplereference voltage = 1;for i=1:8 %current output bit set to 1: digital output(i)=1; compare threshold= 0; %Output digital output in current form to DAC: for j=1:i compare threshold = compare threshold+digital output(j)*reference voltage/(2ˆj); end %Comparator compares (analog)input to DAC output: if (input voltage−compare threshold 如果我们考虑0.425 V 的模拟输入值和1 V 的参考电压的示例,我们可以将8 位ADC 的输出近似如下:将8 位输出的第一位设置为1,因此输出到DAC 为0.50.425 减去0.5 小于0,所以将输出的第一位设置为0将8 位输出的第二位设置为1,因此输出到DAC 为0.250.425 减去0.25 大于0,所以输出的第二位是1将8 位输出的第三位设置为1,因此输出到DAC 为0.3750.425 减去0.375 大于0,所以输出的第三位是 1 对所有8 位重复此过程,直到确定输出为:01101100从这个过程中可以明显看出,N 位SAR ADC 必须需要N 个(时钟)周期才能成功逼近输出。

采用SAR结构的8通道12位ADC设计

和复合 型 DA C,实现 了数字位 的 串行输 出。整体 电路采用 H PC S I E进行仿真 .转换速率 为 13 S S 3K P ,

转换 时 间为 7 1 。通 过 低 功 耗 设 计 , 作 电流 降 低 为 28 A。芯 片 基 于 06t BC .. 5t s 工 . m .. i MO 1 n i S工 艺 完成 版 图

D C、 次 逼 近 寄 存器 和 逻 辑 控 制 A 逐

一

基 金 项 目 : 国 家 自 然 科 学 基 金 ( 60476046), 教 育 部 博 士 学 科 点 基 金 ( 01 和 部 委 基 金 2005070 1 5)

( 1 0 0 0 0 DZ 1 0 5 4 8 1 2 5 0 6 ) 5 4 8 1 3 4 0 4 , 1 0 0 0 0 DZ 1 4

本 文基 于 上华 06. CMOS .1 Bi t n i

2 猛发展 , ADC在 便 携 式 设 备 上 的 应 体 系 结 构都 是 为 了满 足某 种 特 定 需 工艺 设 计 了一 个 8通道 l 位 串行 输 S ADC 出 ADC,转 换 核 心 电路 采 用 逐 次 逼 用 发 展 迅 速 ,正 逐 步 向高 速 、高精 求 的 纵 向市 场 而设 计 的 。 AR 度 和 低 功 耗 的方 向 发展 。 是采样 速率低于 5 P MS S的 中高 分 近 型 结 构 ,并 在 总 结 改 进 传 统 结 构

维普资讯

● 西 安 电 子科 技 大 学 微 电 子研 究 所 彭 新芒 杨银 堂 朱 樟 明

采用 S AR 结 构 的 8通 道 1 2位 ADC 设 计

摘 要 :本 文设 计 实现 了一 个 8 道 l 位 逐 次 逼 近 型 A C。转 换 器 内部 集 成 了 多 路复 用 器 、并 / 通 2 D 串转换 寄存 器

应用于逐次逼近型ADC的数字校准技术研究与实现

摘要模数转换器(Analog-to-Digital Converter,ADC)是实现连续模拟信号转换为离散数字信号必不可少的接口模块。

ADC种类较多,然而逐次逼近型模数转换器(Successive Approximation Rigister,SAR) ADC,因其结构简单、面积小、功耗低以及更适用于先进工艺的不断演进等独特优点,在便携式消费类电子产品、医疗器械设备、工业控制以及数字采集等领域得到广泛关注和应用。

在上述应用领域中,对SAR ADC的性能提出了更高的要求。

同时,随着纳米级CMOS工艺技术的不断发展,高性能模拟电路的设计愈加困难,因此,采用数字校准技术协助实现高性能的ADC,已经成为较为普遍的做法。

本文在现有研究的基础上,首先分析了SAR ADC的非理想因素,如寄生电容、电容失配等影响。

然后总结了目前常用的不同实现方式的SAR ADC数字校准技术,并分析了各自的优缺点。

通过分析,本文研究了两种数字校准方案协助实现高性能的SAR ADC,具体研究内容包括:第一,研究了一种12位1MS/s的前台数字自校准SAR ADC。

针对校准DAC以及回补校准码的算法做了改进。

为了降低面积和扩大校准范围,采用三段式结构的校准DAC校准主DAC中高6位的误差电压。

同时,将中间状态作为校准DAC的初始状态,简化误差测量逻辑控制过程。

另外,采用“双寄存器”预判断的方法,提高校准码的回补效率。

设计和实现的前台数字自校准SAR ADC在110nm CMOS工艺下,通过校准前后仿真对比验证,结果表明,该SAR ADC校准后,SNDR从校准前的49 dB提升到71.1dB,DNL/INL分别从校准前的-1/+21.250 LSB、-17.398/+10.152 LSB减小到-0.25/+0.5 LSB、-1.048/+0.792 LSB。

第二,研究了一种基于扰动信号注入的14位30MS/s后台数字校准SAR ADC。

16位sar adc数字校准算法及数字电路设计

16位sar adc数字校准算法及数字电路设计16位SAR ADC数字校准算法及数字电路设计1. 前言16位SAR ADC(Successive Approximation Register Analog-to-Digital Converter)是一种高精度、高速度的模数转换器,广泛应用于工业控制、医疗仪器、通信设备等领域。

数字校准算法和数字电路设计对于提高16位SAR ADC的性能至关重要。

2. SAR ADC工作原理SAR ADC是一种逐次逼近寄存器型模数转换器,其工作原理是通过逐步逼近对模拟输入信号进行量化。

SAR ADC将输入信号与一个DAC (数模转换器)的输出进行比较,得到一个比较结果,然后将这个比较结果送入一个寄存器中进行逐位逼近。

每次比较完成后,SAR ADC 会得到一个近似的数字输出,经过多次迭代后,得到最终的数字输出结果。

3. SAR ADC数字校准算法为了提高16位SAR ADC的精度和稳定性,数字校准算法至关重要。

数字校准算法主要包括零点和增益校准两个方面。

在零点校准中,通过降低输入失调和增益误差,减小偏差并消除误差。

在增益校准中,通过修正不稳定的增益和零点漂移,提高转换器的稳定性。

4. 数字电路设计16位SAR ADC的数字电路设计需要考虑多个方面,包括输入电路设计、时序分析、功耗优化等。

在输入电路设计中,需要考虑输入阻抗匹配、信号放大和滤波等问题。

时序分析则需要确保各个模块之间的数据传输和控制信号的正确性和稳定性。

另外,功耗优化也是数字电路设计的重要任务,需要合理布局电路结构、选择合适的工艺参数和优化布线等。

5. 个人观点和理解对于16位SAR ADC数字校准算法及数字电路设计,我认为数字校准算法是关键的技术之一,能有效提高16位SAR ADC的性能。

而在数字电路设计中,要考虑的因素很多,需要全面考虑各个方面的需求,并在设计中做出合理的权衡。

只有在数字校准算法和数字电路设计两个方面都做到精益求精,才能生产出高性能的16位SAR ADC。

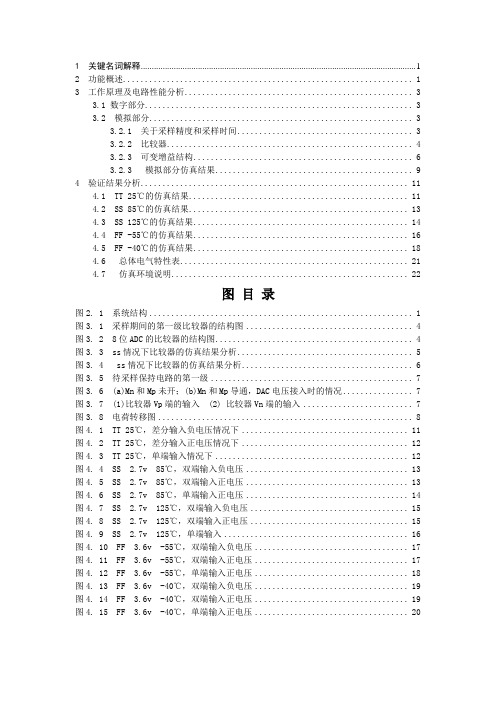

8位 SAR ADC设计说明书

1 关键名词解释 (1)2 功能概述 (1)3 工作原理及电路性能分析 (3)3.1 数字部分 (3)3.2 模拟部分 (3)3.2.1 关于采样精度和采样时间 (3)3.2.2 比较器 (4)3.2.3 可变增益结构 (6)3.2.3 模拟部分仿真结果 (9)4 验证结果分析 (11)4.1 TT 25℃的仿真结果 (11)4.2 SS 85℃的仿真结果 (13)4.3 SS 125℃的仿真结果 (14)4.4 FF -55℃的仿真结果 (16)4.5 FF -40℃的仿真结果 (18)4.6 总体电气特性表 (21)4.7 仿真环境说明 (22)图目录图2. 1 系统结构 (1)图3. 1 采样期间的第一级比较器的结构图 (4)图3. 2 8位ADC的比较器的结构图 (4)图3. 3 ss情况下比较器的仿真结果分析 (5)图3. 4 ss情况下比较器的仿真结果分析 (6)图3. 5 待采样保持电路的第一级 (7)图3. 6 (a)Mn和Mp未开;(b)Mn和Mp导通,DAC电压接入时的情况 (7)图3. 7 (1)比较器Vp端的输入 (2) 比较器Vn端的输入 (7)图3. 8 电荷转移图 (8)图4. 1 TT 25℃,差分输入负电压情况下 (11)图4. 2 TT 25℃,差分输入正电压情况下 (12)图4. 3 TT 25℃,单端输入情况下 (12)图4. 4 SS 2.7v 85℃,双端输入负电压 (13)图4. 5 SS 2.7v 85℃,双端输入正电压 (13)图4. 6 SS 2.7v 85℃,单端输入正电压 (14)图4. 7 SS 2.7v 125℃,双端输入负电压 (15)图4. 8 SS 2.7v 125℃,双端输入正电压 (15)图4. 9 SS 2.7v 125℃,单端输入 (16)图4. 10 FF 3.6v -55℃,双端输入负电压 (17)图4. 11 FF 3.6v -55℃,双端输入正电压 (17)图4. 12 FF 3.6v -55℃,单端输入正电压 (18)图4. 13 FF 3.6v -40℃,双端输入负电压 (19)图4. 14 FF 3.6v -40℃,双端输入正电压 (19)图4. 15 FF 3.6v -40℃,单端输入正电压 (20)表目录表3. 1 Gain=1时的仿真结果 (9)表3. 2 Gain=0.5时的仿真结果 (9)表3. 3 Gain=2时的仿真结果 (9)表3. 4 Gain=4时的仿真结果 (10)表4. 1 TT 25仿真结果参数 (12)表4. 2 SS 85℃仿真结果参数 (14)表4. 3 SS 125℃仿真结果参数 (16)表4. 4 FF -55℃仿真结果参数 (18)表4. 5 FF -40℃仿真结果参数 (20)表4. 6 原手册结果 (21)表4. 7 仿真结果汇总 (21)8位SAR ADC1 关键名词解释12位ADC的文档中已述2 功能概述图2.1 系统结构ADC2子系统包括一个8通道的可配置模拟多路开关(AMUX2),一个可编程增益放大器(PGA2)和一个500ksps、8 位分辨率的逐次逼近寄存器型ADC,该ADC 中集成了跟踪保持电路。

10bit_1MS-s超低功耗SAR_ADC设计

10bit_1MS-s超低功耗SAR_ADC设计随着物联网和移动设备的广泛应用,对于数字信号处理的需求越来越高。

其中,模数转换器(ADC)在将模拟信号转换为数字信号方面起着至关重要的作用。

本文将介绍一种名为10bit_1MS/s超低功耗SAR_ADC设计的新型ADC设计方案。

SAR_ADC(逐次逼近式寄存器型ADC)是一种常见的ADC 架构,具有高速、低功耗、小面积和较高的分辨率等优点。

然而,传统的SAR_ADC设计存在功耗较高的问题。

因此,本文提出了一种超低功耗的SAR_ADC设计方案。

首先,在电路设计方面,采用了低功耗的电流比较器和功耗优化的DAC电路。

电流比较器是ADC中功耗较大的部分之一,因此采用低功耗的电流比较器可以有效降低整个ADC的功耗。

同时,通过优化DAC电路,减少DAC电流和电压的泄漏,进一步降低功耗。

其次,在时钟设计方面,采用了一种自适应时钟调整技术。

传统的ADC设计中,时钟频率通常较高,功耗也相应增加。

而自适应时钟调整技术可以根据输入信号的变化来动态调整时钟频率,以达到降低功耗的目的。

此外,为了进一步降低功耗,本文还采用了多级功耗管理技术。

在不同的工作模式下,通过切换电路的供电电压和关闭不需要的模块,达到降低功耗的效果。

最后,在布线和布局方面,本文采用了优化的布线规则和布局设计。

通过减少线路的长度和交叉,降低信号的延迟和功耗。

经过仿真和实验验证,10bit_1MS/s超低功耗SAR_ADC设计方案在保持较高精度的同时,功耗显著降低。

与传统设计方案相比,功耗降低了30%以上,同时实现了较低的面积和较高的速度。

综上所述,10bit_1MS/s超低功耗SAR_ADC设计方案在电路设计、时钟设计、功耗管理和布线布局等方面进行了优化,实现了功耗的显著降低。

这对于满足物联网和移动设备对高性能和低功耗ADC的需求具有重要意义。

SAR方案ADC

SAR方案ADC随着科技的迅猛发展,模数转换器(ADC)的应用变得越来越广泛。

其中,采样率和分辨率是衡量ADC性能的两个重要指标。

在众多的ADC设计方案中,按需采样(SAR)方案因其简单性和低功耗而备受瞩目。

SAR(Successive Approximation Register)方案ADC是一种经典的ADC设计方案,它采用逐步逼近法来实现模拟信号与数字信号之间的转换。

在SAR方案ADC中,信号首先通过采样电路进行采样。

采样电路通常由采样保持电路和开关电容电路组成。

采样保持电路用于将输入信号保持在稳定的电平上,而开关电容电路则用于控制采样时刻和抽样时刻。

采样完毕后,采样保持电路会将采样保持电压传递给比较器。

比较器的作用是将采样保持电压与参考电压进行比较,产生一个比较结果。

如果采样保持电压大于参考电压,则比较结果为1;反之,则为0。

比较结果会被传输到SAR逐次逼近寄存器(SAR-ADC)中。

SAR-ADC包含一系列的比较器和数字逻辑电路,用于根据比较结果不断逼近模拟信号值。

具体来说,在每个逼近周期中,SAR逐次逼近寄存器会根据比较结果调整逼近电压,并将新的逼近电压与采样保持电压再次进行比较。

通过多次逼近,SAR-ADC能够逐渐逼近实际的模拟信号值,最终得到一个数字代码。

这个数字代码可以通过数模转换器(DAC)还原为对应的模拟信号值。

SAR方案ADC的优点之一是其高精度和高速度。

由于逼近过程是逐次进行的,每个逼近周期都可以产生一位输出。

因此,SAR-ADC能够以很高的速度完成转换过程。

此外,SAR-ADC对输入信号的要求相对较低,可以适应广泛的应用场景。

然而,SAR方案ADC也存在一些挑战。

首先,逐次逼近法需要进行多次比较和逼近操作,因此对电源噪音和栅极电压噪声非常敏感。

其次,随着分辨率的增加,逼近次数也会增加,造成转换速度的下降。

为了克服这些挑战,研究人员不断努力改进SAR方案ADC的性能。

例如,引入了校准电路来消除非线性误差;采用改进的比较器结构和运算放大器设计来提高精度和速度;优化布局和排线方式以减少噪声影响等。

10位10MHz自校准SAR_ADC设计

10位10MHz自校准SAR_ADC设计自校准是现代电子系统设计中的重要技术之一,它可以提高系统的稳定性和准确性。

而SAR_ADC(逐次逼近式寄存器型模数转换器)作为一种常用的模拟数字转换器,在许多应用中发挥着重要作用。

本文将介绍一种10位10MHz自校准SAR_ADC的设计。

首先,我们需要了解SAR_ADC的基本原理。

SAR_ADC是一种逐次逼近式模数转换器,它通过逐次调整比较器的参考电压和DAC(数模转换器)的输出来逼近输入信号的模拟电压。

在每次逼近过程中,比较器会将输入信号与参考电压进行比较,并将比较结果输入给逻辑电路。

逻辑电路会根据比较结果调整DAC 的输出,从而逼近输入信号的模拟电压。

最终,DAC的输出值就是输入信号的数字表示。

为了实现自校准,我们需要添加校准电路和控制逻辑。

校准电路可以根据已知的参考电压和已知的输入信号,通过比较器和DAC的输出,计算出比较器和DAC的误差,并将误差值送回控制逻辑。

控制逻辑会根据误差值调整比较器的参考电压和DAC 的输出,以校正比较器和DAC的误差。

通过多次校准过程,SAR_ADC的准确性和稳定性将得到显著提高。

在10位10MHz的设计中,关键是要保证高精度和高速率。

为了实现高精度,我们可以使用高精度的比较器和DAC,并增加比较器的位数。

为了实现高速率,我们可以优化控制逻辑和校准算法,使其能够在10MHz的采样率下完成校准和转换过程。

此外,我们还可以采用一些技术手段来进一步提高SAR_ADC的性能。

例如,我们可以使用电流平衡技术来降低比较器和DAC的误差,使用自适应校准算法来动态调整校准过程,以适应不同的工作条件。

同时,我们还可以使用电源抑制技术来降低电源噪声对转换精度的影响。

综上所述,10位10MHz自校准SAR_ADC的设计是一个复杂而关键的任务。

通过合理选择器件和优化设计,结合适当的校准算法和技术手段,我们可以实现高精度和高速率的SAR_ADC。

基于40_nm_CMOS工艺的高速SAR_ADC的设计_

图1 SAR ADC的基本架构最后当每一位都比较完成后,DAC的输出电压将收敛到与输入信号相差不超过1/2 LSB(1LSB=V FS/2N)的范围,比较器的每一位输出码组成最终的N位输出码。

本设计采用了非2进制冗余DAC技术、静态锁存比较器、基于锁存器的SAR逻辑控制电路,在CMOS工艺下实现了12 bit的高速SAR ADC的设计。

1 DAC的设计DAC为非二进制传统电容阵列,阵列基底小于2。

根据式(1),如果利用位电容来实现12位ADC,则基底至少为1.8772发生在量化编码为0111输入信号在此冗余范围终都能被准确地表示,应的冗余范围内,最终就能正确完成量化2 SRA ADC的工作原理在采样阶段,采用下极板采样的方式出端接共模电压V_CM图2 本设计的SAR ADC结构图图3 本设计中用到的静态锁存比较器图4 SAR逻辑结构图号V ip和V in,此时差分DAC输出端的电荷:(2)(3)为了减小采样开关的非理想效应,先将V CM开关断开,再将自举采样开关断开,完成对输入信号的采样。

采样完成后即进行第一次量化。

以差分DAC的P端为例,首先将上极板从共模电平V CM断开,然后将除MSB 电容外所有电容的下极板切换到V refb,MSB电容下极板切换到V refb,DAC建立完成即进行第一次比较,此时,上极板电荷:(4)互补DAC的N端的切换方式和P端相反,其切换后(5)可得第一次比较时(7)(8)其中定义模拟权重:假设第一次比较结果D12=1,即V X P<V X N,则P端D A C的M S B电容下极板接V r e f保持不变,将MSB-1电容从V refb切换到V refb,V XP=V CM-V ip+V reft · (ω12,p,a+ω11,p,a)+V refb · (1-ω12,p,a-ω11,p,a )。

互补DAC端MSB电容下极板接V reft保持不变,并将MSB-1电容下极板从V refb切换到V reft,V XN=V CM-V in+V refb ·(1-ω12,n,a-ω11,n,a )+V refb · (ω12,n,a+ω11,n,a)。

SAR型ADC原理简析

SAR 型ADC 原理简析

逐次逼近寄存器型(SAR)模拟数字转换器(ADC)是采样速率低

于5Msps (每秒百万次采样)的中等至高分辨率应用的常见结构。

SAR ADC 的分辨率一般为8 位至16 位,具有低功耗、小尺寸等特点。

这些特点使该类型ADC 具有很宽的应用范围,例如便携/电池供电仪表、笔输入量化器、工业控制和数据/信号采集等。

顾名思义,SAR ADC 实质上是实现一种二进制搜索算法。

所以,当内部电路运行在数兆赫兹(MHz)时,由于逐次逼近算法的缘故,ADC 采样速率仅是该数值的几分之一。

SAR ADC 的架构

尽管实现SAR ADC 的方式千差万别,但其基本结构非常简单(见图1)。

模拟输入电压(VIN)由采样/保持电路保持。

为实现二进制搜索算法,N 位寄存器首先设置在中间刻度(即:100.。

.00,MSB 设置为1)。

这样,DAC 输出(VDAC)被设为VREF/2,VREF 是提供给ADC 的基准电压。

然

后,比较判断VIN 是小于还是大于VDAC。

如果VIN 大于VDAC,则比较

器输出逻辑高电平或1,N 位寄存器的MSB 保持为1。

相反,如果VIN 小于VDAC,则比较器输出逻辑低电平,N 位寄存器的MSB 清0。

随后,SAR 控。

逐次逼近寄存器型ADC设计报告最新

逐次逼近寄存器型ADC设计报告组员(学号):王迪(********)高超(20083507)韩吉祥(20083506)曹天一(20083510)专业(年级):集成电路设计与集成系统课程名称:逐次逼近寄存器型ADC提交日期:一、组员分工:二、项目设计要求:设计一个12bit逐次逼近寄存器型模数转换器SAR ADC 三、项目参数要求:四、项目设计内容:1. 逐次逼近寄存器型模数转换器(SAR ADC)整体结构:2. 逐次逼近寄存器型模数转换器(SAR ADC)的特点及应用:特点:中级转换速度,低功耗,高精度,小尺寸应用:便携式仪表、笔输入量化器,工业控制和数据/信号采集器等3. 逐次逼近寄存器型模数转换器(SAR ADC)工作原理:SAR ADC其基本结构如图1所示,包括采样保持电路(S/H)、比较器(COMPARE)、数/模转换器(DAC)、逐次逼近寄存器(SAR REGISTER)和逻辑控制单元(SAR LOGIC)。

模拟输入电压V IN由采样保持电路采样并保持,为实现二进制搜索算法,首先由SAR LOGIC控制N位寄存器设置在中间刻度,即令最高有效位MSB为“1”电平而其余位均为“0”电平,此时数字模拟转换器DAC输出电压V DAC为0.5V REF,其中V REF为提供给ADC的基准电压。

由比较器对V IN 和V DAC进行比较,若V IN>V DAC,则比较器输出“1”电平,N位寄存器的MSB 保持“1”电平;反之,若V IN<V DAC,则比较器输出“0”电平,N位寄存器的MSB被置为“0”电平。

一次比较结束后,MSB被置为相应的电平,同时逻辑控制单元移至次高位并将其置“1”,其余位置“0”,进行下一次比较,直至最低有效位LSB比较完毕。

整个过程结束,即完成了一次模拟量到数字量的转换,N 位转换结果存储在寄存器内,并由此最终输出所转化模拟量的数字码。

4. 逐次逼近寄存器型模数转换器(SAR ADC)各子模块设计:子模块1:比较器(COMPARE)(1)电路结构:(给出电路结构图)(2)工作原理:电路为两级运算放大器,第一级是电流镜做负载的差分放大器。

SAR ADC 外部驱动电路设计流程

SAR ADC 外部驱动电路设计流程章节一:介绍SAR ADC外部驱动电路SAR ADC(Successive Approximation Register Analog-to-Digital Converter),顾名思义,是一种逐次逼近寄存器型的模拟信号到数字信号转换器。

SAR ADC要求输入信号是单端信号,因此在实际应用中需要添加外部驱动电路,将双端信号转换为单端信号。

本篇文章将详细介绍SAR ADC的外部驱动电路设计流程。

SAR ADC由一系列模拟电路和数字电路组成,其中外部驱动电路是连接模拟电路和输入信号的桥梁,同时承担着滤波、抗干扰等作用。

因此,优秀的SAR ADC外部驱动电路设计具有至关重要的作用。

章节二:SAR ADC外部驱动电路设计细节1.输入信号采集首先需要考虑的是如何采集输入信号。

通常采用差动信号放大器差分输入的方式,将双端信号转换为单端信号,并进行滤波处理。

在实际应用中,差动信号放大器的电源要求较高,一般采用电压稳压器电路来保证供电的稳定性。

2.滤波SAR ADC外部驱动电路的一个重要作用就是滤波,保证输入信号的质量。

常用的滤波电路有低通滤波、带通滤波、高通滤波等。

需要根据不同的应用场景选择合适的滤波电路。

3.抗干扰SAR ADC受到外界干扰时,很容易出现转换误差。

因此,在设计SAR ADC外部驱动电路时,需要考虑如何抗干扰。

常用的抗干扰电路有屏蔽电路、滤波电路、提高信噪比等。

4.缓冲SAR ADC通常具有较低的输入电阻和较高的输入电容。

因此在长距离传输时,需要考虑信号损失的问题。

这时,需要增加缓冲电路,将输入信号放大并保持稳定。

5.时序SAR ADC在转换过程中需要稳定的时序驱动。

外部驱动电路需要根据芯片的时序电气特性,在合适的时间点提供驱动信号。

同时,还需要考虑信号的延迟和同步问题。

章节三:SAR ADC外部驱动电路设计注意事项1.电源噪声SAR ADC的转换精度和稳定性对电源噪声比较敏感。

sar adc工作原理

sar adc工作原理SAR ADC,又称为逐次逼近型模数转换器(Successive Approximation Register ADC),是一种常见的模数转换器。

它的工作原理是通过对比输入信号和内部参考电压,逐步逼近地确定输入信号的数字表示。

SAR ADC的核心部件是逐次逼近寄存器(Successive Approximation Register)。

该寄存器由一系列电平切换电容和逻辑电路组成。

工作过程可以分为以下几个步骤:1. 存储参考电压:首先,将一个固定的参考电压值存储到逐次逼近寄存器中。

这个参考电压可以通过一个参考电压源提供。

2. 设置比较器:将输入信号与模拟开关电容相连接,并将比较器的反馈连接到逐次逼近寄存器的输出。

3. 初始化逼近寄存器:将逐次逼近寄存器的最高位设置为1,其他位设置为0。

这相当于给出了一个初始逼近量(initial approximation)。

4. 模拟-数字转换:开始逐步逼近过程。

从最高位开始,将逐次逼近寄存器的每一位按照顺序置为1,并将结果输入给比较器进行比较。

如果比较器输出高电平表示逼近值大于输入信号,反之,如果比较器输出低电平表示逼近值小于输入信号。

5. 更新逼近寄存器:根据比较器的输出结果,将逐次逼近寄存器的对应位更新为上一个逼近阶段的结果。

如果比较器输出高电平,表示逼近值大于输入信号,将对应位更新为0;如果比较器输出低电平,表示逼近值小于输入信号,将对应位保持为1。

6. 完成逼近:重复步骤4和步骤5,直到逐次逼近寄存器的所有位均被处理完。

此时,逐次逼近寄存器中存储的就是输入信号的数字表示。

SAR ADC具有如下特点:1. 快速的采样率:SAR ADC的工作速度很快,可以实现高采样率。

这是因为逼近过程只需要一个时钟周期完成,且每个时钟周期可以确定一位。

2. 相对较低的功耗:由于逼近过程是逐步进行的,每个步骤的时间较短,所以整个转换过程的功耗相对较低。

sar adc 原理

sar adc 原理SAR ADC原理简介SAR ADC(Successive Approximation Register Analog-to-Digital Converter)是一种常用的模数转换器,广泛应用于各种电子设备中。

它的工作原理基于逐次逼近,通过将输入信号与一系列数字比较器进行比较,逐步生成数字输出。

SAR ADC的基本结构包括比较器,逐次逼近寄存器(SAR)和数字电路。

比较器是SAR ADC的核心部件,用于将输入信号与参考电压进行比较。

逐次逼近寄存器(SAR)则是用于逐步逼近生成数字输出的关键部分。

数字电路用于控制SAR ADC的工作流程。

SAR ADC的工作流程如下:1. 首先,将待转换的模拟信号与参考电压进行比较。

比较器将输出一个比较结果,表示输入信号与参考电压的大小关系。

2. 根据比较结果,SAR将根据比较器的输出来更新逐次逼近寄存器(SAR)中的比特位。

逐次逼近寄存器(SAR)是一个n位的二进制寄存器,用于存储逐步逼近过程中的比特位。

3. 在逼近过程中,SAR ADC会根据比较器的输出结果逐步调整逐次逼近寄存器(SAR)中的比特位。

具体来说,它会从最高有效位(MSB)开始,逐个比特地进行逼近,直到逼近到最低有效位(LSB)。

4. 在每次逼近过程中,SAR ADC会将逐次逼近寄存器(SAR)中的比特位与参考电压进行比较,并根据比较结果来调整下一个比特位的值。

这个过程会一直进行,直到逼近到最低有效位(LSB)。

5. 最后,当逼近过程完成后,SAR ADC会将逐次逼近寄存器(SAR)中的比特位的值输出为数字信号。

这个数字信号就是SAR ADC的输出结果。

SAR ADC具有以下几个特点:1. 高精度:由于SAR ADC采用逐次逼近的方式进行转换,可以实现高精度的模拟到数字转换。

逐步逼近的过程可以逐渐减小误差,从而提高转换精度。

2. 快速转换速度:SAR ADC的转换速度比较快,适用于对转换速度要求较高的应用场景。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

0 引言

SAR ADC 是采样 速 率 低 于 5Msps 的 中 等 至 高 分辨率应用的常见结构,实质上是实现一种 二 进 制 搜索算 法[1-3]。 SAR ADC 的 逐 次 逼 近 寄 存 器 主 要 是依赖于移位寄存器的工作原理,如何优化 设 计 成 为低 功 耗 设 计 的 一 个 重 要 因 素[4]。 基 于 标 准 CMOS 工艺,通 过 结 构 研 究 来 提 高 速 度 和 分 辨 率、 优化 功 耗 面 积 等 指 标,是 ADC 的 重 要 研 究 方 向 之 一[5]。

图 3 带复位置位 D 触发器

图 3 中 的 D 触 发 器 是 由 4 个 传 输 门、2 个 或 门、2 个与非门 和 6 个 非 门 来 实 现 的,这 个 D 触 发 器中的传输门由两个反相时钟来控制,实现 下 降 沿 触发;其中 的 或 门 及 与 非 门 实 现 了 复 位 及 置 位 功 能,并且置位的优先级高 于 复 位 的 优 先 级。 D 触 发 器真值表如表 1 所示。

而控制电路部分要完成 Dp 和 Dn 差分信号及 AN20 等控制信号的 产 生,因 此 需 要 对 D 触 发 器 结 构进 行 些 许 改 动,即 需 要 两 种 D 触 发 器,如 图 4 所示。

数量。使用较少的数字逻辑单元,意味 着 开 关 功 耗 可以达到很小。虽然数字控制部分的动态功耗在 ADC 的功耗中不是主要部分,但使用较少的控制逻 辑可以把数字电路开关噪声降到很低,减 少 对 模 拟 部分的影响,对模拟部分的设计要求就可 以 更 低 一 些,对 降 低 模 拟 部 分 的 功 耗 起 到 一 定 的 辅 助 作 用[6] 。

若采用全定制的设计方法,对于一个 12 bits 的 逐次逼近寄存 器,约 需 要 24 个 D 触 发 器。 数 字 控 制电 路 部 分,AN20、AN30、Eoc _ en 等 6 个 控 制 信 号,大概 需 要 6 个 D 触 发 器 和 12 个 逻 辑 门 电 路。 也就是说,采 用 全 定 制 方 法 来 实 现 逐 次 逼 近 寄 存 器,总共约需要 30 个 D 触 发 器 和 12 个 逻 辑 门,相 比逻辑综合的实现方法,大大地减少了逻辑 单 元 的

表 1 D 触发器真值表

D

SN

RN

Q

QN

×

0

×

1

0

×

1

0

0

1

0

1

1

0

1

1

1

1

1

0

D 触发器真 值 表 表 明,只 要 置 位 SN 低 电 平 有 效,Q 端强制置位为 1;在置位 SN 无效,复位 RN 低 电平有效时,Q 端 清 零 复 位; 只 有 在 置 位 和 复 位 都 无效时,Q 端的输出等于 D 端输入,实现移位。

图 2 表 明 逐 次 逼 近 寄 存 器 的 主 要 信 号,分 别 如下:

Clk:SAR ADC 的工作时钟信号; Clear:清零信 号,转 换 开 始 前 将 所 有 寄 存 器 清 零 ,低 电 平 有 效 ; Vcomp :比 较 器 的 输 出 结 果 ,也 就 是 寄 存 器 要 保 存的数据; AN20、AN30:SAR ADC 中 DAC 的 模 拟 开 关 控 制信号; Dn0 ~ Dn12、Dp0 ~ Dp12:两 组 差 分 信 号,用 于 控制 DAC 中的电容极板; Eoc_en:一 次 转 换 完 成 时 的 指 示 信 号,低 电 平 有效; PD_lock:比较器中的锁存放大器的 工 作 信 号, 高电平有效; PD_pre:比较 器 中 前 置 放 大 器 的 工 作 信 号,高 电平有效; clear_iner:比 较 器 输 出 端 的 强 制 清 零 信 号 ; 最终的转换数据通过并串转换模块后以串行 方 式 输 出 ,并 且 要 保 证 输 出 数 据 与 时 钟 同 步 。

张少真1 ,李哲英2

(1. 北京交通大学 电子信息工程学院,北京 100044; 2. 北京联合大学 信息学院,北京 100101)

[摘 要] 逐次逼近寄存器( SAR registers) 协调 DAC( Digital-to-Analog Converter,数模转换器) 和 比较器共 同 工 作,完 成 逐 次 逼 近 逻 辑,在 SAR ADC ( Successive approximation A / D Converter,逐 次 逼近型模数转换器) 的 设 计 中 非 常 重 要。 设 计 了 一 个 应 用 于 5V 单 电 源 电 压、采 样 率 为 1MSPs、 12bits、低功耗 SAR ADC 中的逐次逼近寄存器。通过比较分 析 逻 辑 综 合 和 全 定 制 两 种 方 法,选 择 了 全 定 制 方 法 来 实 现 逐 次 逼 近 寄 存 器 ,实 现 功 耗 、面 积 的 最 佳 优 化 。 [关键词] 逐次逼近寄存器;逻辑综合;全定制;控制信号 [中图分类号] TP 332. 1 [文献标志码] A [文章编号] 1005-0310(2011)02-0015-05

2011 年 6 月 第 25 卷第 2 期总 84 期

北京联合大学学报(自然科学版) Journal of Beijing Union University( Natural Sciences)

Jun. 2011 Vol. 25 No次逼近寄存器的设计

SAR ADC 变 换 前,逐 次 逼 近 寄 存 器 要 全 部 清 零;变 换 开 始,要 将 逐 次 逼 近 寄 存 器 的 最 高 位 寄 存 器设置为 1,之后逐 次 逼 近 逻 辑 依 次 将 下 一 位 寄 存 器置为 1,直至 12 位数据完成转换。从转换的过程 来看,需要带复位置位的 D 触发器。如图 3 所示。

The Design of SAR Registers in SAR ADC

ZHANG Shao-zhen1 ,LI Zhe-ying2

(1. School of Electronic and Information Engineering,Beijing Jiaotong University,Beijing 100044,China; 2. College of Information,Beijing Union University,Beijing 100101,China)

2 逐次逼近寄存器的设计

逐次逼近寄存器及控制电路部分的输入输出 信号如图 2 所示。

图 2 逐次逼近寄存器信号图

图 1 逐次逼近寄存器的逻辑结构

根据 DC 综合报告 得 知,逐 次 逼 近 寄 存 器 调 用 了 39 个 D 触发 器 单 元 和 135 个 门 级 电 路 单 元,总 共 174 个数字 逻辑单元。根据 综 合 的 功 耗 报 告 得 知,电路功耗约为 3. 3 mW,泄漏功耗约为 0. 5 mW, 即逐 次 逼 近 寄 存 器 的 总 功 耗 为 3. 8 mW。 在 Encounter 工具中进行自动布局布线,版图面积设置为 280 μm × 580 μm 时,版图中单元密度为 52% 左右, 对于 CSMC 1P3M 0. 5 μm 工艺来说,只有 3 层金属 布线,当密度偏高时,容易出现走线冗长、散 热 不 均 等问题。显然,用逻辑综合的方法来实现 逐 次 逼 近 寄 存 器 ,功 耗 和 面 积 都 不 太 符 合 设 计 指 标 。

1 逐次逼近寄存器的实现

随着集成电路的发展,对于某些 设 计 可 以 采 用 EDA 技术,以硬件描述语言为逻辑描述的主要表达 方式,整个设 计 过 程 中 可 用 软 件 进 行 仿 真 与 验 证, 故 逻 辑 综 合 的 实 现 方 法 变 得 更 加 方 便[4]。 SAR

[收稿日期] 2011 - 04 - 19 [基金项目] 北京市教委项目( PHR〈IHLB〉20090513) ;国家自然基金项目( NSFC609976024) 。 [作者简介] 张 少 真 ( 1986—) ,女,河 北 衡 水 人,北 京 交 通 大 学 电 子 信 息 工 程 学 院 ,硕 士,主 要 研 究 方 向 为 混 合 信 号 集 成电路的设计。

parameter idle = 5'b00001; / / 上电复位 parameter setup = 5'b00010; / / 初始化状态 parameter sample = 5'b00100; / / 采样状态 parameter convert = 5'b01000; / / 转换状态 parameter adout = 5'b10000; / / 输出状态 通过 Modelsim 编 译、仿 真 及 DC 综 合,得 到 逐 次逼近寄存器的逻辑结构如图 1 所示。

16

北京联合大学学报(自然科学版)

2011 年 6 月

ADC 中的逐次逼近寄存器逻辑通过逻辑综合的方 法来 实 现,这 样 大 大 减 少 了 仿 真 及 版 图 设 计 的 时间。

SAR ADC 完成一次转换需要 18 个时钟周期, 分为初始化 ( 2 个 周 期 ) 、采 样 与 保 持 ( 3 个 周 期 ) 、 转换(12 个周期) 和输出 (1 个周期) 4 个状态。因 此,可以编 写 Verilog 代 码 通 过 有 限 状 态 机 来 实 现 逐 次 逼 近 逻 辑 ,设 置 的 状 态 代 码 如 下 :

第 25 卷第 2 期

张少真等:应用于 SAR ADC 中逐次逼近寄存器的设计

17

SAR ADC 中的逐次逼近寄存器是基于移位寄 存器和计数器来设计的,而移位寄存器和计 数 器 都 是基于 D 触 发 器 来 设 计 的[7],所 以 首 先 设 计 D 触 发器。 2. 1 D 触发器的设计

SAR ADC 中,比 较 器 在 时 钟 上 升 沿 将 比 较 结 果输 出,为 了 保 证 数 据 的 稳 定 性,所 以 逐 次 逼 近 寄 存器最好在时钟下降沿读取数据,因此需要 下 降 沿 触发的 D 触发器。