ARM内核种类.

ARM题库

ARM题库一、填空题1. 常见的ARM处理器内核有 ARM 7 、 ARM 9 和 ARM 11 等。

2. ARM处理器有两种状态,分别是 ARM 状态和 Thumb 状态。

3. 按总线所传送的信息类型,总线分为数据总线、地址总线和控制总线。

4. ADS 是一套用来开发ARM 处理器应用系统的开发工具包,用户可以用ADS 编辑、编译和调试C、C++以及汇编程序。

目前的版本为 ADSv1.2 。

5. 与逻辑运算规则:0 • 0= 0 ;0 • 1= 0 ; 1 • 0= 0 ; 1 • 1= 16. 或逻辑运算规则: 0 + 0= 0 ;0 +1= 1 ; 1 + 0= 1 ; 1 + 1= 1将2进制转换为16进制:(10011100101101001000) B = 。

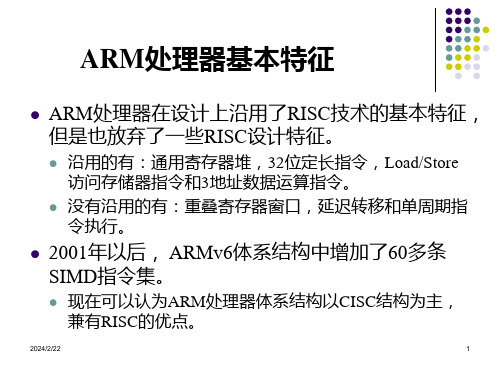

7.ARM 属于 RISC 架构。

8.ARM 指令集是 32 位宽,Thumb 指令集是 16 位宽。

9.ARM体系结构版本中V___4___版架构是目前应用最广的ARM体系架构,ARM7、___ ARM 9 ___都采用该架构。

10.ARM微处理器共有__37_个__32_ 位寄存器,其中_31___个为通用寄存器,____6__个为状态寄存器。

11.常用的嵌入式操作系统有嵌入室Linux 、 VxWorks 等。

12.ARM嵌入式系统主要由嵌入室硬件、嵌入室软件和开发工具构成。

13.复位后,ARM处理器处于 SVC 工作模式, ARM 状态。

14.S3C2410采用的核心处理器是 ARM920T 。

15.S3C2410 支持两种引导方式,分别是 Nor-Flash 启动方式、 Nand-Flash 启动方式。

16.GPIO的中文全称是通用输入输出端口。

17.ARM处理器有两种状态,分别是 ARM 和 Thumb 。

18.计算机结构分为哈佛体系结构和冯诺依曼体系结构。

19.ARM处理器支持的数据类型中,字节为 8 位、半字为 16 位、字为 32 位。

ARM处理器内核介绍

52v07 ARM普通处理器内核

TM

23

23

2.6 ARM片上总线

AMBA-Advanced Microcontroller Bus Architecture(先进 的微控制器总线体系结构)

AMBA总线定义3种规范

TM

测试芯片 ARM10200E

2

2

IP核、软核、硬核、固核

IP(Intellectual Property)就是常说的知识产权。IP定义为 用于ASIC、ASSP和PLD等当中,并且是预先设计好的电路模块。

IP核模块有行为(Behavior)、结构(Structure)和物理( Physical)三级不同程度的设计,对应描述功能行为的不同分 为三类,即软核(Soft IP Core)、完成结构描述的固核 ( Firm IP Core)和基于物理描述并经过工艺验证的硬核( Hard IP Core)。

52v07 ARM普通处理器内核

TM

18

18

ARM9TDMI 数据通道 (2)

结果 DINFWD

MU 逻辑

B 寄存器 Bank Imm BDATA 移位器

A

乘法器

ALU

PSR

ADATA

锁存

锁存

MU逻辑单元包含有:多路复用器,乘法器和桶形移位器

52v07 ARM普通处理器内核

TM

19

19

ARM9TDMI流水线的变化

52v07 ARM普通处理器内核

TM

16

16

ARM9TDMI

ARM简介及编程

ARM简介及编程1.ARM简介(摘录) ARM(Advanced RISC Machines)是微处理器行业的一家知名企业,设计了大量高性能、廉价、耗能低的RISC处理器、相关技术及软件。

技术具有性能高、成本低和能耗省的特点。

适用于多种领域,比如嵌入控制、消费/教育类多媒体、DSP和移动式应用等。

ARM将其技术授权给世界上许多著名的半导体、软件和OEM厂商,每个厂商得到的都是一套独一无二的ARM相关技术及服务。

利用这种合伙关系,ARM很快成为许多全球性RISC标准的缔造者。

目前,总共有30家半导体公司与ARM签订了硬件技术使用许可协议,其中包括Intel、IBM、LG半导体、NEC、SONY、菲利浦和国民半导体这样的大公司。

至于软件系统的合伙人,则包括微软、升阳和MRI等一系列知名公司。

ARM架构是面向低预算市场设计的第一款RISC微处理器。

2.产品介绍ARM提供一系列内核、体系扩展、微处理器和系统芯片方案。

由于所有产品均采用一个通用的软件体系,所以相同的软件可在所有产品中运行(理论上如此)。

典型的产品如下。

①CPU内核--ARM7:小型、快速、低能耗、集成式RISC内核,用于移动通信。

-- ARM7TDMI(Thumb):这是公司授权用户最多的一项产品,将ARM7指令集同Thumb 扩展组合在一起,以减少内存容量和系统成本。

同时,它还利用嵌入式ICE调试技术来简化系统设计,并用一个DSP增强扩展来改进性能。

该产品的典型用途是数字蜂窝电话和硬盘驱动器。

--ARM9TDMI:采用5阶段管道化ARM9内核,同时配备Thumb扩展、调试和Harvard 总线。

在生产工艺相同的情况下,性能可达ARM7TDMI的两倍之多。

常用于连网和顶置盒。

②体系扩展-- Thumb:以16位系统的成本,提供32位RISC性能,特别注意的是它所需的内存容量非常小。

③嵌入式ICE调试由于集成了类似于ICE的CPU内核调试技术,所以原型设计和系统芯片的调试得到了极大的简化。

ARM 内核SP,LR,PC寄存器

ARM 内核SP,LR,PC 寄存器

深入理解ARM 的这三个寄存器,对编程以及操作系统的移植都有很大的

裨益。

1、堆栈指针r13(SP):每一种异常模式都有其自己独立的r13,它通常指向异常模式所专用的堆栈,也就是说五种异常模式、非异常模式(用户模式和系统模式),都有各自独立的堆栈,用不同的堆栈指针来索引。

这样当ARM 进入异常模式的时候,程序就可以把一般通用寄存器压入堆栈,返回时

再出栈,保证了各种模式下程序的状态的完整性。

2、连接寄存器r14(LR):每种模式下r14 都有自身版组,它有两个特殊功能。

(1)保存子程序返回地址。

使用BL 或BLX 时,跳转指令自动把返回地址放入r14 中;子程序通过把r14 复制到PC 来实现返回,通常用下列指令之一:MOV PC, LR BX LR

通常子程序这样写,保证了子程序中还可以调用子程序。

stmfd sp!, {lr} ldmfd sp!, {pc}

(2)当异常发生时,异常模式的r14 用来保存异常返回地址,将r14 如栈可以处理嵌套中断。

3、程序计数器r15(PC):PC 是有读写限制的。

当没有超过读取限制的时候,读取的值是指令的地址加上8 个字节,由于ARM 指令总是以字对齐的,

故bit[1:0]总是00。

当用str 或stm 存储PC 的时候,偏移量有可能是8 或12 等其它值。

在V3 及以下版本中,写入bit[1:0]的值将被忽略,而在V4 及以上版

本写入r15 的bit[1:0]必须为00,否则后果不可预测。

tips:感谢大家的阅读,本文由我司收集整编。

仅供参阅!。

ARM架构——精选推荐

ARM架构(过去称作进阶精简指令集机器(Advanced RISC Machine),更早称作Acorn RISC Machine)是一个32位元精简指令集(RISC)中央处理器(processor)架构,其广泛地使用在许多嵌入式系统(embedded)设计。

由于节能的特点,ARM处理器非常适用于行动通讯领域,符合其主要设计目标为低耗电的特性。

在今日,A R M家族占了所有32位元嵌入式处理器75%的比例[1],使它成为占全世界最多数的32位元架构之一。

A R M处理器可以在很多消费性电子产品上看到,从可携式装置(P D A、移动电话、多媒体播放器、掌上型电玩,和计算机)到电脑周边设备(硬盘、桌上型路由器)甚至在导弹的弹载计算机等军用设施中都有他的存在。

在此家族中衍伸的重要产品还包括M a r v e l l的X S c a l e架构和德州仪器的O M A P系列。

编辑本段历史A R M的设计是A c o r n电脑公司(A c o r n C o m p u t e r s L t d)于1983年开始的开发计划。

这个团队由R o g e r W i l s o n和S t e v e F u r b e r带领,着手开发一种新架构,类似进阶的M O S T e c h n o l o g y 6502处理器。

A c o r n有一大堆建构在6502架构上的电脑,因此能设计出一颗类似的芯片即意味着对公司有很大的优势。

团队在1985年时开发出A R M1S a m p l e版,而首颗"真正"的产能型A R M2于次年量产。

A R M2具有32位的数据总线、26位的寻址空间,并提供64M b y t e的寻址范围与16个32-b i t的暂存器。

这些暂存器其中有一颗做为(w o r d大小)程式计数器,其前面6b i t s和后面2b i t s用来保存处理器状态标记(P r o c e s s o r S t a t u s F l a g s)。

ARM与STM简介

• ARM简介 • Cortex-M3内核 • STM32系列微处理器简介

ARM简介

• ARM(Advanced RISC Machine ),既 是一个公司的名字,也是对一类处理器的 通称。 • 是Байду номын сангаас个32位精简指令集(RISC)处理器架 构,其广泛地使用在许多嵌入式系统设计。 由于节能的特点,ARM处理器非常适用于 移动通信领域,符合其主要设计目标为低 成本、高性能、低耗电的特性。

• STM32系列分为:

• 入门级STM32 F0系列 • 超值型STM32 F100系列 • USB基本型STM32 F101系列 • 增强型STM32 F103系列 • 互联型STM32 F105/107系列 • 高性能型STM32 F2系列 • 内置DSP和FPU的高性能型STM32 F3/4系列

Cortex-M3内核

• Cortex-M3 内核是ARMv7-M体系结构,采 用了哈佛结构,拥有独立的指令总线和数 据总线,可以让取指与数据访问并行不悖。 • ARM公司在2004年推出了Cortex-M3 (CM3)内核,经过了近十年的市场积累, 目前意法半导体,NXP,东芝,ATMEL, 富士通,Luminary(已被TI收购)等诸多半 导体公司均推出了基于Cortex-M3的微控制 器产品。

ARM简介

• 2011年,ARM的客户报告了79亿ARM处理 器出货量,占有95%的智能手机,90%的 硬盘驱动器,40%的数字电视和机顶盒, 15%的单片机,和20%的移动电脑。在 2012年,微软与ARM科技生产了新的 Surface平板电脑,还有,AMD宣布它将于 2014年开始生产基于ARM核心的64位服务 器芯片。

Cortex-M3内核

ARM 内核寄存器 和 基本汇编语言讲解

ARM 内核寄存器和基本汇编语言讲解•一、ARM内核寄存器▪ 1.1 M3/M4内核寄存器▪ 1.2 A7内核寄存器▪ 1.3 ARM中的PC指针的值•二、ARM汇编语言▪ 2.1 ARM汇编基础▪ 2.2 汇编伪指令▪ 2.3 ARM汇编指令集•三、代码反汇编简析▪ 3.1 不同编译器的反汇编▪ 3.2 C 和汇编比较分析开头直接来看几个简单的汇编指令:MOV R0,R1MOV PC,R14上面的指令中使用了汇编MOV指令,但是其中的R0,R1,R14,PC分别是什么?哪来的?怎么用?要讲ARM 汇编语言,必须得先了解ARM的内核寄存器,内核处理所有的指令计算,都需要用到内核寄存器,所以ARM汇编里面指令大都是基于寄存器的操作。

文章前推荐韦东山老师的单片机核心视频,视频可以在韦东山老师官网里面找到:百问网ARM版本简单介绍:对于M3/M4而言:R13,栈指针(Stack Pointer)•R13寄存器中存放的是栈顶指针,M3/M4 的栈是向下生长的,入栈的时候地址是往下减少的。

•裸机程序不会用到PSP,只用到MSP,需要运行RTOS的时候才会用到PSP。

•堆栈主要是通过POP,PUSH指令来进行操作。

在执行PUSH 和 POP 操作时, SP 的地址寄存器,会自动调整。

R14 ,连接寄存器(Link Register)•LR 用于在调用子程序时存储返回地址。

例如,在使用BL(分支并连接,Branch and Link)指令时,就自动填充 LR 的值(执行函数调用的下一指令),进而在函数退出时,正确返回并执行下一指令。

如果函数中又调用了其他函数,那么LR将会被覆盖,所以需要先将LR寄存器入栈。

•保存子程序返回地址。

使用BL或BLX时,跳转指令自动把返回地址放入r14中;子程序通过把r14复制到PC来实现返回•当异常发生时,异常模式的r14用来保存异常返回地址,将r14如栈可以处理嵌套中断R15,程序计数器(Program Count)•在Cortex-M3中指令是3级流水线,出于对Thumb代码的兼容的考虑,读取pc时,会返回当前指令地址+4的值。

关于ARM的内核架构介绍

张凌001关于ARM的内核架构很多时候我们都会对M0,M0+,M3,M4,M7,arm7,arm9,CORTEX-A系列,或者说AVR,51,PIC等,一头雾水,只知道是架构,不知道具体是什么,有哪些不同?今天查了些资料,来解解惑,不是很详细,但对此有个大体了解。

咱先来当下最火的ARM吧1.ARMARM即以英国ARM(Advanced RISC Machines)公司的内核芯片作为CPU,同时附加其他外围功能的嵌入式开发板,用以评估内核芯片的功能和研发各科技类企业的产品.ARM 微处理器目前包括下面几个系列,以及其它厂商基于 ARM 体系结构的处理器,除了具有ARM 体系结构的共同特点以外,每一个系列的 ARM 微处理器都有各自的特点和应用领域。

- ARM7 系列- ARM9 系列- ARM9E 系列- ARM10E 系列- ARM11系列- Cortex 系列- SecurCore 系列- OptimoDE Data Engines- Intel的Xscale- Intel的StrongARM ARM11系列2. Cortex 系列32位RISCCPU开发领域中不断取得突破,其设计的微处理器结构已经从v3发展到现在的v7。

Cortex 系列处理器是基于ARMv7架构的,分为Cortex-M、Cortex-R和Cortex-A三类。

由于应用领域的不同,基于v7架构的Cortex处理器系列所采用的技术也不相同。

基于v7A的称为“Cortex-A系列。

高性能的Cortex-A15、可伸缩的Cortex-A9、经过市场验证的Cortex-A8处理器以及高效的Cortex-A7和Cortex-A5处理器均共享同一体系结构,因此具有完整的应用兼容性,支持传统的ARM、Thumb指令集和新增的高性能紧凑型Thumb-2指令集。

1Cortex-M系列Cortex-M系列又可分为Cortex-M0、Cortex-M0+、Cortex-M3、Cortex-M4;2Cortex-R系列Cortex-R系列分为Cortex-R4、Cortex-R5、Cortex-R7;3Cortex-A 系列Cortex-A系列分为Cortex-A5、Cortex-A7、Cortex-A8、Cortex-A9、Cortex-A15、Cortex-A50等 ,同样也就有了对应内核的Cortex-M0开发板、Cortex-A5开发板、Cortex-A8开发板、Cortex-A9开发板、Cortex-R4开发板等等。

arm架构分类

arm架构分类ARM架构是一种广泛使用的计算机处理器架构,常用于移动设备、嵌入式系统、服务器等领域。

根据不同的应用场景和需求,ARM架构可以分为以下几类:1. Cortex-A系列Cortex-A系列是ARM架构中最强大的处理器系列,主要用于高性能计算领域。

它们具有多核心、高频率和大缓存等特点,能够支持复杂的操作系统和应用程序。

常见的Cortex-A系列处理器包括Cortex-A7、Cortex-A9、Cortex-A15、Cortex-A53和Cortex-A72等。

2. Cortex-R系列Cortex-R系列是ARM架构中专门设计用于实时计算领域的处理器系列。

它们具有高度可靠性、低延迟和快速响应等特点,适合于控制系统、汽车电子和医疗设备等领域。

常见的Cortex-R系列处理器包括Cortex-R4、Cortex-R5和Cortex-R8等。

3. Cortex-M系列Cortex-M系列是ARM架构中专门设计用于微控制器领域的处理器系列。

它们具有低功耗、低成本和小尺寸等特点,适合于嵌入式系统、传感器和智能家居等领域。

常见的Cortex-M系列处理器包括Cortex-M0、Cortex-M3、Cortex-M4和Cortex-M7等。

4. Neoverse系列Neoverse系列是ARM架构中专门设计用于数据中心和云计算领域的处理器系列。

它们具有高度可扩展性、高效能和低功耗等特点,适合于大规模数据处理和分布式计算等场景。

常见的Neoverse系列处理器包括Neoverse N1和Neoverse V1等。

总之,ARM架构根据不同的应用场景和需求,设计了多个不同系列的处理器,以满足各种计算需求。

浅谈ARM-Cortex系列处理器之区别

浅谈ARM Cortex系列处理器之区别市面上ARM Cortex系列包括3个系列,包括ARM Cortex-A,ARM Cortex—R,ARM Cortex —M,Z这三种系列,并且每个系列又分多种子版本,每个子版本都有各自的特点。

很好的为设计人员提供非常广泛的具有可扩展性的性能选项,从而有机会在多种选项中选择最适合自身应用的内核,而非千篇一律的采用同一方案.其中,1,Cortex-A-面向性能密集型系统的应用处理器内核2, Cortex-R-面向实时应用的高性能内核3, Cortex-M-面向各类嵌入式应用的微控制器内核Cortex-A处理器为利用操作系统(例如Linux或者Android ,IOS)的设备提供了一系列解决方案,这些设备被用于各类应用,从低成本手持设备到智能手机、平板电脑、机顶盒以及企业网络设备等。

早期的Cortex-A系列处理器(A5、A7、A8、A9、A12、A15和A17)基于ARMv7-A架构。

每种内核都共享相同的功能集,例如NEON媒体处理引擎、Trustzone安全扩展、单精度和双精度浮点支持、以及对多种指令集(ARM、Thumb—2、Thumb、Jazelle 和DSP)的支持。

与此同时,这些处理器也具有极高的设计灵活性,能够提供所需的最佳性能和预期的功效.介绍过Cortex-A,下面介绍Cortex—R系列——衍生产品中体积最小的ARM处理器,这一点也最不为人所知。

Cortex—R处理器针对高性能实时应用,例如硬盘控制器(或固态驱动控制器)、企业中的网络设备和打印机、消费电子设备(例如蓝光播放器和媒体播放器)、以及汽车应用(例如安全气囊、制动系统和发动机管理)。

Cortex—R系列在某些方面与高端微控制器(MCU)类似,但是,针对的是比通常使用标准MCU的系统还要大型的系统。

例如,Cortex-R4就非常适合汽车应用.Cortex—R4主频可以高达600MHz(具有2。

ARM Cortex-M3 内核介绍

ARM Cortex-M3 内核介绍内核包含四部分:1.乘法器;2.控制逻辑;3.Thumb 指令译码器;4.内部接口CM3 内部包含元素介绍:1. DAP,调试访问接口,Debug Access Port。

Cortex‐M3 的调试系统基于ARM 最新的CoreSight 架构。

不同于以往的ARM 处理器,内核本身不再含有JTAG 接口。

取而代之的,是CPU 提供称为调试访问接口(DAP)的总线接口。

通过这个总线接口,可以访问芯片的寄存器,也可以访问系统存储器,甚至是在内核运行的时候访问!对此总线接口的使用,是由一个调试端口(DP)设备完成的。

DPs 不属于CM3 内核,但它们是在芯片的内部实现的。

目前可用的DPs 包括SWJ‐DP(既支持传统的JTAG 调试,也支持新的串行线调试协议),另一个SW‐DP 则去掉了对JTAG 的支持。

另外,也可以使用ARM CoreSignt 产品家族的JTAG‐DP 模块。

这下就有 3 个DPs 可以选了,芯片制造商可以从中选择一个,以提供具体的调试接口(通常都是选SWJ‐DP)。

2. ETM 的作用就是记录处理器做的事情并送到外面的调试器。

由于微控制器带有大量的片内存储器,因此不能简单地通过观察外部管脚来确定处理器核是如何运行的。

ETM 对深嵌入处理器内核提供了实时跟踪能力。

它向一个跟踪端口输出处理器执行的信息。

软件调试器允许使用JTAG 接口对ETM 进行配置并以用户易于理解的格式显示捕获到的跟踪信息。

ETM 直接连接到ARM 内核而不是主AMBA 系统总线。

3.NVIC 是Cortex-M3 处理器中一个完整的部分,它可以进行高度配置,为处理器提供出色的中断处理能力。

在NVIC 的标准执行中,它提供了一个非屏蔽中断(NMI)和32 个通用物理中断,这些中断带有8 级的抢占优先权。

NVIC可以通过综合选择配置为1 到240 个物理中断中的任何一个,并带有多达256。

arm架构_详谈ARM架构与ARM内核发展史

arm架构_详谈ARM架构与ARM内核发展史1、ARM架构与ARM内核1.1 ARM架构与内核简述⽬前为⽌,ARM总共发布8种架构:ARMv1、ARMv2、ARMv3、ARMv4、ARMv5、ARMv6、ARMv7 、ARMv8,这是ARM架构指令集的多个v版本。

基于不同的ARM架构可以设计出不同特点的内核处理器。

⽐如基于ARMv3架构设计出的处理器ARM6、ARM7,这两款处理器适⽤于不同的场景,硬件可能不同,但是架构指令集是⼀样的。

好⽐盖房⼦,刚开始因为⽔平低流⾏盖平房,这就是⼀种架构(ARMv5),然后这种平房架构你可以设计出⼀款独⽴卫⽣间的款式, 这叫ARM7内核。

然后其他⼈(芯⽚设计公司)想盖房⼦的就买你这个图纸去盖,接着过⼀段时间,有⼈觉得光独⽴卫⽣间还不够啊, 我还想有个⼩院⼦! 好吧,那ARM就满⾜你们的要求,出个带⼩院⼦的款式(ARM9)。

即ARMv1/2/3等是指令集的架构,ARM7/9等是基于架构设计出的内核处理器。

ARM的架构都是基于RISC指令集⽽设计的,内核是实现这⼀指令集的硬件架构的基础。

1.2 ARM各架构之间区别1.2.1 ARM版本Ⅰ:V1版架构该版架构只在原型机ARM1出现过,只有26位的寻址空间,没有⽤于商业产品。

其基本性能有:基本的数据处理指令(⽆乘法);基于字节、半字和字的Load/Store指令;转移指令,包括⼦程序调⽤及链接指令;供操作系统使⽤的软件中断指令SWI;寻址空间:64MB(226)。

1.2.2 ARM版本Ⅱ:V2版架构该版架构对V1版进⾏了扩展,例如ARM2和ARM3(V2a)架构。

包含了对32位乘法指令和协处理器指令的⽀持。

版本2a是版本2的变种,ARM3芯⽚采⽤了版本2a,是第⼀⽚采⽤⽚上Cache的ARM处理器。

同样为26位寻址空间,现在已经废弃不再使⽤。

V2版架构与版本V1相⽐,增加了以下功能:乘法和乘加指令;⽀持协处理器操作指令;快速中断模式;SWP/SWPB的最基本存储器与寄存器交换指令;寻址空间:64MB。

ARM内核全解析,从ARM7,ARM9到Cortex-A7,A8,A9,A12,A15到Cortex-A53,A57到Cortex-A72

ARM内核全解析,从ARM7,ARM9到Cortex-A7,A8,A9,A12,A15到Cortex-A53,A57到Cortex-A72ARM全新旗舰架构!Cortex-A72正式发布64位的ARMv8 Cortex-A57/A53刚刚开始普及,ARM已经将目光瞄向了更遥远的未来,2015-02-04宣布了下一代顶级核心,命名为“Cortex-A72”。

A72将会直接取代A57,定位高端市场。

具体的架构设计尚未公开,应该是第二代64位架构,而且作为一个大核心,依然支持big.LITTLE双架构组合,而搭配的小核心依然是A53。

看起来,ARM暂时不打算升级A53,因为此前已经宣称,A53将顺序执行架构做到了极致。

ARM还给出了一些关于A72模糊的性能、功耗指标,因为这显然更吸引人。

ARM宣称,A72最快会在2016年实现商用,初期采用台积电16nm FinFET制造工艺(三星肯定用自家的14nm FinFET),对比20nm工艺的A57核心,它的性能最多可以达到其大约1.8倍,而功耗会有着明显的下降。

再对比28nm工艺的A15,A72更是可以做到大约3.5倍的性能,同等负载下的功耗则降低75%。

而在大小核心双架构组合中,整体功耗还能继续降低40-60%。

目前,海思、联发科、瑞芯微等都已经购买了Cortex-A72的授权,但奇怪的是没有提及正焦头烂额的高通。

中国内地和台湾厂商越来越牛气了!ARM内核全解析,从ARM7,ARM9到Cortex-A7,A8,A9,A12,A15到Cortex-A53,A57前不久ARM正式宣布推出新款ARMv8架构的Cortex-A50处理器系列产品,以此来扩大ARM在高性能与低功耗领域的领先地位,进一步抢占移动终端市场份额。

Cortex-A50是继Cortex-A15之后的又一重量级产品,将会直接影响到主流PC市场的占有率。

围绕该话题,我们今天不妨总结一下近几年来手机端较为主流的ARM处理器。

ARM CORTEX-M3 内核架构理解归纳

在我看来,Cotex-M3内核的主要包括:嵌套向量中断控制器(NVIC),取值单元,指令译码器,算数逻辑单元(ALU),寄存器组,存储器映射(4GB统一编址各区域功能的划分与界定),对于开发者而言,其实主要关注的主要分为三大块:1、寄存器组2、地址功能划分映射3、中断机制(NVIC)。

1)寄存器组Cortex-M3内核共有19组32位寄存器:R0——R12(通用寄存器);低寄存器组R0——R732位Thumb-2指令与16位Thumb指令均可访问高寄存器组R8——R1232位Thumb-2指令与极少数16位Thumb指令可访问R13(堆栈指针寄存器);主堆栈寄存器MSP(main-SP)/进程堆栈寄存器PSP(Process-SP)同一时间只能使用其中一个。

MSP供操作系统内核及中断(异常)处理子程序使用,PSP只供用户的应用程序代码使用(详细使用详见3、嵌套向量中断控制器(NVIC)的总结)。

堆栈指针是4字节对齐的,故最低两位永远是00;R14(连接寄存器)用于存储程序返回的地址及PC的返回地址;R15(程序寄存器)指向当前程序执行的地址;2)特殊功能寄存器组xPSR(程序状态字寄存器组),32位,可分为三个寄存器分别进行访问,也可以PSR或xPSR 的名字直接组合访问。

应用程序PSR(APSR)中断号PSR(IPSR)执行PSR(EPSR)中断屏蔽寄存器PRIMASK 单一比特位,置位后,除NMI与硬fault外,其他中断都不响应;FAULTMASK 单一比特位,置位后,除NMI外,其他中断都不响应;BASEPRI 共有9位,中断号小于等于该寄存器设置值的中断都不响应;控制寄存器controlControl[0] 0决定特权级线程模式;1用户级线程模式;Control[1] 0主堆栈;1进程堆栈;控制寄存器只能在特权级模式下改写,handler模式永远是特权级,且只允许使用主堆栈MSP 复位后,处理器进入特权级+线程模式下;2、地址功能划分映射Cortex-m3是一个32位处理器,其地址总线、数据总线都是32位的,故可在4G的地址范围上资源寻址。

arm内核全解析_arm内核体系结构分类介绍

arm内核全解析_arm内核体系结构分类介绍ARM处理器是英国Acor n有限公司设计的低功耗成本的第一款RISC微处理器。

全称为Ad vanced RISC Machine。

ARM处理器本身是32位设计,但也配备16位指令集,一般来讲比等价32位代码节省达35%,却能保留32位系统的所有优势。

ARM内核特点ARM处理器为RISC芯片,其简单的结构使ARM内核非常小,这使得器件的功耗也非常低。

它具有经典RISC的特点:* 大的、统一的寄存器文件;* 简单的寻址模式;* 统一和固定长度的指令域,3地址指令格式,简化了指令的译码。

编译开销大,尽可能优化,采用三地址指令格式、较多寄存器和对称的指令格式便于生成优化代码;* 单周期操作,ARM指令系统中的指令只需要执行简单的和基本的操作,因此其执行过程在一个机器周期内完成;* 固定的32位长度指令,指令格式固定为32位长度,这样使指令译码结构简单,效率提高;* 采用指令流水线技术。

ARM内核体系结构ARM架构自诞生至今,已经发生了很大的演变,至今已定义了7种不同的版本:V1版架构:该架构只在原型机ARM1出现过,其基本性能包括基本的数据处理指令(无乘法)、字节、半字和字的Load/Store指令、转移指令,包括子程序调用及链接指令、软件中断指令、寻址空间64MB。

V2版架构:该版架构对V1版进行了扩展,如ARM2与ARM3(V2a版)架构,增加的功能包括乘法和乘加指令、支持协处理器操作指令、快速中断模式、SWP/SWPB的最基本存储器与寄存器交换指令、寻址空间64MB。

V3版架构:该版对ARM体系结构作了较大的改动,把寻址空间增至32位(4G B),增加了当前程序状态寄存器CPSR和程序状态保存寄存器 SPSR以便于异常处理。

增加了中止和未定义2种处理器模式。

ARM6就采用该版结构。

指令集变化包括增加了M RS/MSR指令,以访问新增的CPSR /SPSR寄存器、增加了从异常处理返回的指令功能。

5ARM体系结构

配备MMU和 最快 最高 Cache

合理

媒体播放器,产品举 例:MP3,机顶盒, iPOD,智能手机,

PAD

去除MMU, 较快 合理 备有Cache

较低

数字信号处理,产品 举例:汽车ABS系统, 路由器,交换机,航 电系统

没有存储子 系统,即不 含MMU。

5

体系结构版本V3

这个体系结构版本将寻址范围扩展到了32位。 当前程序状态信息由过去存于R15中移到一个 新的当前程序状态寄存器CPSR(Current Program Status Register)中。增加了程序状态 保存寄存器SPSR(Saved Program Status Registers),以便当异常出现时保留CPSR的 内容。增加了2个指令(MRS和MSR),允许 访问新的CPSR和SPSR寄存器。

ARM状态,运行32位的ARM指令集 Thumb状态,运行16位的Thumb指令集 在任何一种工作状态可以通过转移指令切换到另一种

工作状态。 ARM和Thumb之间的状态切换不影响处理器工作模式

和寄存器中的内容。 加电起动时处理器工作在ARM状态。

2024/2/22

12

指令集压缩

对于传统的微处理器体系结构,指令和数据具有同样 的宽度。 与16位体系结构相比,32位体系结构在操纵32位数 据时呈显了更高的性能,并可更有效地寻址更大的 空间。 一般来讲,16位体系结构比32位体系结构具有更高 的代码密度,但只有近似一半的性能。

提高了T变量中ARM/Thumb之间切换的效率; 让非T变量同T变量一样,使用相同的代码生成技 术。增加了一个前导零计数(count leading zeros) 指令,该指令允许更有效的整数除法和中断优先 程序;增加了软件断点指令;为协处理器设计者 增加了更多可选择指令;对由乘法指令如何设置 标志进行了定义。

arm的架构cortex-m处理器内核及功能介绍,嵌入式编程

arm的架构cortex-m处理器内核及功能介绍,嵌入

式编程

ARM的Cortex-M处理器内核是专为嵌入式系统设计的,该处理器具有低功耗、高效率、低成本的特点。

Cortex-M内核的主要功能包括以下几个方面:

1. 性能:

Cortex-M处理器内核可提供32位处理能力,并且采用了基于RISC的处理器架构,因此可以提供高性能和响应速度。

2. 低功耗:

Cortex-M内核具有优秀的功率管理功能,能够调整处理器的运行状态以降低功耗。

3. 实时性:

Cortex-M内核能够提供最佳的响应速度和实时性,使其非常适合实时控制、数据采集、检测等应用。

4. 低成本:

Cortex-M内核设计简单、成本低廉,因此比其它内核更适合量产及低成本的应用。

在嵌入式编程中,Cortex-M处理器内核的使用可以让设计者更方便地实现嵌入式系统的功能,提高代码的效率和可靠性。

同时,内核还支持多种标准接口和协议,如I2C、SPI等,方便开发者进行外设的控制和数据交换。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ST Micro STR91xF,包含Ethernet [2]

ARM968E-S

无高速缓存,TCMs

ARMv5TEJ

ARM926EJ-S

Jazelle DBX

可变动,TCMs, MMU

220 MIPS @ 200 MHz

移动电话:Sony Ericsson(K, W系列),Siemens和Benq(x65系列和新版的)

应用处理器,七级流水线

Zaurus SL-5600

PXA255

32KB/32KB, MMU

400 BogoMips @ 400 MHz

Gumstix,Palm Tungsten E2

PXA26x

可达400 MHz

Palm Tungsten T3

PXA27x

800 MIPS @ 624 MHz

HTCUniversal, Zaurus SL-C1000,3000,3100,3200, Dell Axim x30, x50,和x51系列

120 DMIPS @ 100MHz

Luminary Micro[3]微控制器家族

Cortex™-A系列-开放式操作系统的高性能处理器

Cortex应用程序处理器在高级工艺节点中可实现高达2GHz+标准频率的卓越性能,从而可支持下一代的移动Internet设备。这些处理器具有单核和多核种类,最多提供四个具有可选NEON™多媒体处理模块和高级浮点执行单元的处理单元。

Cortex

ARMv7-A

Cortex-A8

Application profile, VFP, NEON, Jazelle RCT, Thumb-2, 13-stage pipeline

可变动(L1+L2), MMU+TrustZone

up to 2000(2.0 DMIPS/MHz从600 MHz到超过1 GHz的速度)

ARMv5TE

ARM996HS

无振荡器处理器

无高速缓存,TCMs, MPU

ARM10E

ARMv5TE

ARM1020E

(VFP),六级流水线

32KB/32KB, MMU

ARM1022E

(VFP)

16KB/16KB, MMU

ARMv5TEJ

ARM1026EJ-S

Jazelle DBX

可变动,MMU or MPU

SIMD, Thumb-2, (VFP),九级流水线

可变动,MPU

ARMv6KZ

ARM1176JZ(F)-S

SIMD, Jazelle DBX, (VFP)

可变动,MMU+TrustZone

ARMv6K

ARM11 MPCore

1-4核对称多处理器,SIMD, Jazelle DBX, (VFP)

可变动,MMU

ARM内核种类

家族

架构

内核

特色

高速缓存(I/D)/MMU

常规MIPS于MHz

应用

ARM1

ARMv1

ARM1

无

ARM2

ARMv2

ARM2

Architecture 2加入了MUL(乘法)指令

无

4 MIPS @ 8MHz

Acorn Archimedes,Chessmachine

ARMv2a

ARM250

Integrated (完整的)MEMC (MMU),图像与IO处理器。Architecture2a加入了SWP和SWPB(置换)指令。

Acorn Risc PC 600,Apple Newton

ARM7TDMI

ARMv4T

ARM7TDMI(-S)

三级流水线

无

15 MIPS @ 16.8 MHz

Game Boy Advance,Nintendo DS,iPod

ARM710T

均为8KB, MMU

36 MIPS @ 40 MHz

Acorn Risc PC 700,Psion 5 series,Apple eMate 300

TexasInstruments OMAP3

ARMv7-R

Cortex-R4(F)

Embedded profile, (FPU)

可变动高速缓存,MMU可选配

600 DMIPS

Broadcomis a user

ARMv7-M

Cortex-M3

Microcontroller profile

无高速缓存,(MPU)

无,MEMC1a

7 MIPS @ 12MHz

Acorn Archimedes

ARM3

ARMv速缓存

均为4K

12 MIPS @ 25MHz

Acorn Archimedes

ARM6

ARMv3

ARM610

v3架构首创支援寻址32位的内存(针对26位)

均为4K

28 MIPS @ 33MHz

ARM922T

8KB/8KB, MMU

ARM940T

4KB/4KB, MPU

GP2X(第二颗内核)

ARM9E

ARMv5TE

ARM946E-S

可变动,tightly coupled memories, MPU

Nintendo DS,NokiaN-GageConexant 802.11 chips

ARM966E-S

XScale

ARMv5TE

80200/IOP310/IOP315

I/O处理器

80219

400/600MHz

Thecus N2100

IOP321

600BogoMips@ 600 MHz

Iyonix

IOP33x

IOP34x

1-2核,RAID加速器

32K/32K L1, 512K L2, MMU

PXA210/PXA250

NSLU2

IXP460/IXP465

ARM11

ARMv6

ARM1136J(F)-S

SIMD, Jazelle DBX, (VFP),八级流水线

可变动,MMU

?? @ 532-665MHz (i.MX31 SoC)

Nokia N93,Zune,Nokia N800

ARMv6T2

ARM1156T2(F)-S

ARM720T

均为8KB, MMU

60 MIPS @ 59.8 MHz

Zipit

ARM740T

MPU

ARMv5TEJ

ARM7EJ-S

Jazelle DBX

无

ARM9TDMI

ARMv4T

ARM9TDMI

五级流水线

无

ARM920T

16KB/16KB, MMU

200 MIPS @ 180 MHz

Armadillo,GP32,GP2X(第一颗内核), Tapwave Zodiac(Motorolai. MX1)

PXA800(E)F

Monahans

1000 MIPS @ 1.25 GHz

PXA900

Blackberry 8700, BlackberryPearl(8100)

IXC1100

Control Plane Processor

IXP2400/IXP2800

IXP2850

IXP2325/IXP2350

IXP42x