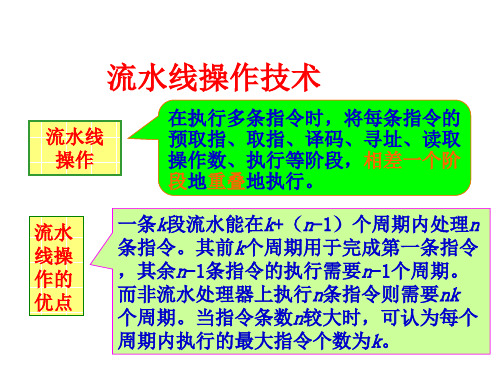

流水线操作技术

计算机流水线(Pipeline)技术

计算机流⽔线(Pipeline)技术流⽔线是现代RISC核⼼的⼀个重要设计,它极⼤地提⾼了性能。

对于⼀条具体的指令执⾏过程,通常可以分为五个部分:取指令,指令译码,取操作数,运算(ALU),写结果。

其中前三步⼀般由指令控制器完成,后两步则由运算器完成。

按照传统的⽅式,所有指令顺序执⾏,那么先是指令控制器⼯作,完成第⼀条指令的前三步,然后运算器⼯作,完成后两步,在指令控制器⼯作,完成第⼆条指令的前三步,在是运算器,完成第⼆条指令的后两部……很明显,当指令控制器⼯作是运算器基本上在休息,⽽当运算器在⼯作时指令控制器却在休息,造成了相当⼤的资源浪费。

解决⽅法很容易想到,当指令控制器完成了第⼀条指令的前三步后,直接开始第⼆条指令的操作,运算单元也是。

这样就形成了流⽔线系统,这是⼀条2级流⽔线。

如果是⼀个超标量系统,假设有三个指令控制单元和两个运算单元,那么就可以在完成了第⼀条指令的取址⼯作后直接开始第⼆条指令的取址,这时第⼀条指令在进⾏译码,然后第三条指令取址,第⼆条指令译码,第⼀条指令取操作数……这样就是⼀个5级流⽔线。

很显然,5级流⽔线的平均理论速度是不⽤流⽔线的4倍。

流⽔线系统最⼤限度地利⽤了CPU资源,使每个部件在每个时钟周期都⼯作,⼤⼤提⾼了效率。

但是,流⽔线有两个⾮常⼤的问题:相关和转移。

在⼀个流⽔线系统中,如果第⼆条指令需要⽤到第⼀条指令的结果,这种情况叫做相关。

以上⾯哪个5级流⽔线为例,当第⼆条指令需要取操作数时,第⼀条指令的运算还没有完成,如果这时第⼆条指令就去取操作数,就会得到错误的结果。

所以,这时整条流⽔线不得不停顿下来,等待第⼀条指令的完成。

这是很讨厌的问题,特别是对于⽐较长的流⽔线,⽐如20级,这种停顿通常要损失⼗⼏个时钟周期。

⽬前解决这个问题的⽅法是乱序执⾏。

乱序执⾏的原理是在两条相关指令中插⼊不相关的指令,使整条流⽔线顺畅。

⽐如上⾯的例⼦中,开始执⾏第⼀条指令后直接开始执⾏第三条指令(假设第三条指令不相关),然后才开始执⾏第⼆条指令,这样当第⼆条指令需要取操作数时第⼀条指令刚好完成,⽽且第三条指令也快要完成了,整条流⽔线不会停顿。

计算机系统结构第3章流水线技术

流水线调度

根据指令的依赖关系和资源可用性,动态调 度指令到不同的流水线阶段。

GPU设计中的流水线技术

线程级并行

通过划分线程块和线程束,实现线程级并行执行。

数据级并行

将数据划分为多个块,每个块在GPU的多个处理单元上并行处理。

指令级并行

通过指令调度和分支预测,实现指令级并行执行。

硬件资源共享

01

硬件资源共享是指流水线中的多个操作共享相同的硬件资源, 如寄存器、缓冲区等。

02

硬件资源共享能够提高资源利用率,减少硬件开销,降低成本。

需要注意的是,硬件资源。

流水线的性能指标

01

吞吐量

流水线每单位时间内完成的操作数 或任务数。

流水线调度

根据子任务的依赖关系和资源需求,动态调 度子任务到不同的计算节点。

THANKS

感谢观看

将执行结果写回寄 存器或内存。

02

流水线的工作原理

数据流驱动

1

数据流驱动是指流水线中的操作按照数据流动的 方向依次执行,每个操作在完成前需要等待前一 个操作的结果。

2

数据流驱动的优点是能够充分利用数据依赖关系, 减少等待时间,提高流水线的吞吐量。

3

需要注意的是,数据流驱动需要精确控制数据流 动的顺序,以避免出现数据相关和冒险问题。

调试和维护困难

由于流水线中各个阶段是并行处 理的,调试和维护可能会比串行 系统更加困难。

05

流水线技术的应用

CPU设计中的流水线技术

指令划分

将指令划分为多个阶段,每个阶段对应一个 功能单元,从而并行执行多个指令。

数据路径设计

高性能计算中的流水线技术分析(四)

高性能计算中的流水线技术分析近年来,计算机科学和技术领域发展迅猛,高性能计算成为了许多领域的研究热点。

在高性能计算中,流水线技术被广泛应用于提高计算机的性能和效率。

本文将重点分析高性能计算中的流水线技术,并探讨其优点和应用。

一、流水线技术的基本原理流水线技术是一种通过将任务拆分为多个子任务,并且这些子任务同时进行,以提高计算机的整体性能的方法。

其基本原理是将任务分解为多个子任务,并将这些子任务分别交由不同的硬件单元处理。

每个子任务的处理时间约等于一个硬件操作完成的时间,这样可以使得整个任务的完成时间明显缩短。

二、流水线技术的优点1. 提高计算机的吞吐量:流水线技术将一个任务分解为多个子任务,每个子任务由不同的硬件单元处理,使得不同任务的执行可以重叠,从而提高了计算机的吞吐量。

2. 增加计算机的并行性:流水线技术充分发挥了硬件单元的并行能力,使得不同的计算单元可以同时处理不同的任务,从而提高了计算机的并行性。

3. 提高计算机的资源利用率:流水线技术使得计算机的各个硬件单元可以在同一时刻处理不同的任务,减少了硬件资源的闲置时间,提高了计算机的资源利用率。

4. 减少任务延迟:流水线技术将任务拆解为多个子任务后,每个子任务可以立即开始执行,从而减少了任务的延迟时间。

三、流水线技术在高性能计算中的应用1. 高性能计算机的体系结构中广泛应用了流水线技术。

例如,在超级计算机中,将计算任务分解为多个子任务,并将这些子任务分别交由不同的处理单元处理,以提高计算机的整体性能和计算速度。

2. 流水线技术在图像和视频处理中也得到了广泛应用。

图像和视频处理通常需要对数据进行多次处理,而流水线技术可以将数据处理过程拆解为多个子任务,并采用不同的处理单元分别处理。

这样可以提高图像和视频处理的速度和效率。

3. 在大规模数据处理和分析中,流水线技术可以将数据处理过程拆解为多个子任务,不同的处理单元同时进行数据处理,从而加快数据处理和分析的速度。

3-2 流水线技术

IF

ID

IF

EX

MEM

WB

IF ID IF EX ID IF MEM EX ID IF WB MEM EX ID WB MEM EX

stall stall

3、控制冲突

由分支指令引起的延迟称为分支延迟。 分支指令在目标代码中出现的频度很高,性能 损失很大。

据统计,每3~4条指令就有一条是分支指令。 假设:分支指令出现的频度是30%, 流水线理想 CPI=1, 那么:流水线的实际 CPI = 1.9。系统性能损失将 近50%!

分支指令 分支目标指令 分支目标指令+1 分支目标指令+2 分支目标指令+3 IF ID IF EX MEM WB IF ID IF EX ID IF MEM EX ID IF WB MEM EX ID WB MEM EX

stall stall

简单处理分支指令:分支失败的情况

分支指令

分支后继指令 分支后继指令+1 分支后继指令+2 分支后继指令+3

将计算结果写入R1

6

7

8

9

MEM WB EX MEM ID IF EX ID IF

WB MEM WB EX MEM WB ID EX MEM

读R1

WB

(1)数据相关冲突的3种类型

根据指令读访问和写访问的顺序,可以将数据 冲突分为3种类型: 考虑两条指令i和j ,且i在j之前进入流水线, 可能发生的数据冲突有:

写后读冲突(RAW):在 i 写入之前,j 先去读。

j 读出的内容是错误的。这是最常见的一种数据

冲突,它对应于真数据相关。

数据相关冲突的3种类型

写后写冲突(WAW):在 i 写入之前,j 先写。最

流水线操作规程

流水线操作规程

《流水线操作规程》

1. 确保设备安全:在操作流水线之前,需要对设备进行检查,确保设备运行正常、无故障,并且符合安全操作标准。

2. 穿戴防护用具:操作人员需要穿戴好相应的防护用具,包括手套、安全鞋、护目镜等,以确保在操作过程中不受到伤害。

3. 精准操作:在操作流水线时,需要按照规程进行精准操作,不得随意更改操作流程或过程,以免引起不必要的事故发生。

4. 及时维护保养:在操作过程中,如果发现设备有异常情况,需要立即停止操作,通知维修人员进行维护保养。

5. 安全出产:在操作流水线期间,需保持清醒、注意力集中,严防操作失误,确保出产安全。

6. 管理监督:在操作流水线时,需要受到管理人员的监督和指导,严格按照规程进行操作,不得擅自做出决定。

7. 紧急处理:在发生紧急情况时,需要立即停止操作,按照紧急处理流程进行处理,并且通知相关人员和部门。

8. 记录填写:在操作结束后,需要对操作过程进行记录填写,包括设备运行情况、操作人员信息等,以便后续追溯和管理。

总之,《流水线操作规程》是对流水线操作的一系列规范和要求,确保在操作过程中能够安全高效地进行生产。

操作人员要严格遵守规程,不得擅自操作,以确保设备运行和人员安全。

计算机体系结构之流水线技术(ppt 125页)

张伟 计算机学院

大纲

1 概念定义 2 流水线分类 3 MIPS五级流水线 4 性能分析 5 流水线相关 6 高级流水线技术

1 概念定义

洗衣店的例子

A, B, C, D 均有一些衣物要 清洗,甩干,折叠

清洗要花30 分钟 甩干要用40 分钟 叠衣物也需要20 分钟

流水线输出端任务流出的顺序与输入端任务流 入的顺序相同。

异步流动流水线(乱序流水线):

流水线输出端任务流出的顺序与输入端任务流 入的顺序不同。

3 MIPS五级流水线

DLX(Dancing Links)

DLX 是一种简单的指令集(教学、简单芯片) 在不流水的情况下,如何实现DLX。

实现DLX指令的一种简单数据通路

4. 存储器访问周期MEM(Memory Access) 5. 写回周期WB(Write Back)

MIPS的简单实现

Instruction Fetch

Instr. Decode Reg. Fetch

Next PC

Next SEQ PC

4

RS1

RS2

Execute Addr. Calc

Zero?

RD

增加了向后传递IR和从MEM/WB.IR回送到通用寄存 器组的连接。

将对PC的修改移到了IF段,以便PC能及时地加 4,为取下一条指令做好准备。

2. 每一个流水段进行的操 作

IR[rs]=IR6..10 IR[rt]=IR11..15 IR[rd]=IR16..20

流水线的每个流水段的操作

将有效地址计算周期和执行周期合并为一个时钟周期,这

是因为MIPS指令集采用load/store结构,没有任何指令

需要同时进行数据有效地址的计算、转移目标地址的计算

高性能计算中的流水线技术分析(三)

在高性能计算中,流水线技术是一种重要的优化手段,可以提高计算效率和性能。

本文将从流水线技术的基本原理、流水线相关的问题以及流水线技术的应用等几个方面进行分析。

1. 流水线技术的基本原理流水线技术是将一项复杂的任务分解为多个子任务,并将它们分别在不同的处理阶段进行处理,从而实现并行计算。

流水线中的每个阶段都有专门的功能和任务,每个阶段的输出作为下一个阶段的输入,形成了一条流水线的运行模式。

流水线技术的基本原理是时间重叠和空间共享。

通过将一个任务划分为多个阶段,在每个阶段的同时进行处理,可以充分利用硬件资源,加快计算速度。

同时,由于每个阶段的处理结果会在下一个阶段使用,可以保持计算流程的连续性,提高整体性能。

2. 流水线相关的问题尽管流水线技术可以提高计算效率,但也存在一些问题需要解决。

首先是数据依赖性问题,即某个阶段的计算结果依赖于前面阶段的计算结果。

一旦前面的计算结果尚未完成,后续的计算就无法进行,从而导致流水线停顿,降低了整体性能。

此外,流水线中的每个阶段都需要有足够的处理时间,否则就会出现阶段饱和的情况。

而某些任务可能会引起阶段的处理时间不均匀,从而导致流水线的性能下降。

3. 流水线技术的应用流水线技术在高性能计算中有着广泛的应用,尤其是在图像处理、模拟计算、数据压缩等领域。

以图像处理为例,流水线可以将图像的不同处理任务划分为多个阶段,从而实现并行计算,提高图像处理的速度和效率。

此外,在模拟计算中,流水线技术可以将复杂的数值计算过程分解为多个阶段,并分别在不同的处理器上进行计算,从而实现并行计算,提高计算效率。

在数据压缩方面,流水线技术可以将压缩的不同处理步骤划分为多个阶段,每个阶段负责一个处理步骤,从而加快数据压缩的速度。

总之,流水线技术作为一种重要的优化手段,在高性能计算中发挥着重要作用。

通过合理地使用流水线技术,可以提高计算效率和性能,进而满足不同领域对计算速度和效率的需求。

对流水线技术的进一步研究和改进,有助于更好地发挥高性能计算的潜力,推动科学技术的发展。

纺织厂自动流水线操作规程

纺织厂自动流水线操作规程

《纺织厂自动流水线操作规程》

一、操作人员必须穿戴好工作服和安全帽,严格按照操作规程进行操作。

二、在操作前必须对设备进行周全的检查,确保设备良好无损。

如有异常情况需立即报告维修人员。

三、操作人员需对设备操作界面和控制台的功能进行熟悉,确保能熟练掌握相关操作技能。

四、操作时需将注意力集中在设备运行状态上,随时准备处理设备异常情况。

五、禁止随意改变设备设定参数,如需更改必须得到主管或技术人员的授权。

六、在操作自动流水线时,注意避免发生卡塞、阻塞等现象,确保生产线的顺畅运行。

七、对于设备的清洁和维护工作,操作人员需按照规定的程序和要求进行,不得擅自停止或改动设备。

八、在操作过程中如发现有异响、异味、异常振动等情况,需立即停机检查,排除故障后方可继续运行。

九、处理异常情况时需及时向主管或技术人员报告,并按照相关程序进行处理。

十、对于自动流水线的停机和开机操作,必须严格按照规定程序进行,避免因错误操作导致设备损坏或生产事故。

以上是关于纺织厂自动流水线操作规程的相关内容,操作人员必须严格遵守,确保设备的安全运行和生产工作的顺利进行。

如何利用流水线技术提高程序执行效率(十)

如何利用流水线技术提高程序执行效率随着科技的不断发展,程序执行效率成为了计算机工程师关注的重点。

而流水线技术作为一种能够提高程序执行效率的重要方法,被广泛应用于硬件设计和优化。

本文将介绍流水线技术以及如何利用流水线技术提高程序执行效率。

一、流水线技术的基本原理流水线技术是将任务分解成多个阶段,每个阶段只负责完成特定的子任务,然后将多个子任务串行执行,从而将整个任务加速完成的一种方法。

流水线技术的基本原理是将任务划分为多个子任务,并通过数据流向和控制信号来实现子任务之间的交互与协调。

通过流水线技术,计算机能够同时执行多个任务,从而提高了任务的并行度,加快了程序的执行速度。

二、流水线技术在程序执行效率中的应用1. 数据流水线在计算机中,许多任务都可以用数据流的形式来表示。

数据流水线是指将数据操作分成多个阶段,每个阶段负责特定的数据操作,并通过流水线寄存器将数据传递给下一个阶段进行处理。

通过数据流水线,可以同时进行多个数据操作,从而提高程序的执行效率。

例如,在图像处理任务中,可以将图像数据流水化处理,分成图像输入、图像滤波、图像变换等多个阶段,并通过数据流水线将图像数据传递给不同的阶段进行并行处理,从而加快图像处理的速度。

2. 指令流水线指令流水线是指将程序的执行划分为多个指令阶段,并通过流水线寄存器将指令传递给下一个阶段进行执行。

通过指令流水线,计算机能够同时执行多个指令,从而提高了指令的并行度,加快了程序的执行速度。

例如,在处理器中,可以将指令流水线划分为取指阶段、译码阶段、执行阶段、访存阶段和写回阶段等多个阶段,并通过流水线寄存器将指令传递给不同的阶段进行并行处理,从而加快程序的执行速度。

三、流水线技术在优化程序执行中的挑战然而,尽管流水线技术可以提高程序执行效率,但也面临着一些挑战。

首先,流水线技术对任务的划分和阶段之间的依赖关系有一定的要求,如果任务划分不合理或者阶段之间的依赖关系复杂,会导致流水线的效率降低。

流水线操作技术

发生流水线冲突的例子

数据 未准 备好 冲突

在流水线的寻址 阶段生成地址

冲突

数据未准备好

在流水线的执行 阶段进行写操作

解决 无等待周期问题

19

总线 冲突

在流水线的 发生流水线冲突的例子 执 行 阶 段 进

行写操作

冲突

同时利用E总线

读数阶段 将 常 数 10 写到AR1

解决

新冲突

数据未准备好

CPU自动地 将STM的写 操作延迟 一个周期

1

预取指P 取指F 译码D 寻址A 读取操作数R 执行X

流水线操作

在第一个机器 周 期 用 PC 中 的 内容加载PAB

在第二个机器周 期用读取到的指 令字加载PB。

第三个周期用PB的内容加载 指令寄存器IR,对IR内的指 令进行译码,产生执行指令 所需要的一系列控制信号。 2

流水线操作

预取指P 取指F 译码D 寻址A 读取操作数R 执行X

插入1个 所有其它存储指令 包括EXP

所有其它存储指令 令

SXM C16 FRCT OVM A 或B

在RPTB[D]前读 BRC

所有存储指令 包括SSXM和RSXM

修改累加器然后读 MMR

STM # lk,BRC

所有其它存储指令

ST # lk,BRC

MVDK Smem,BRC

MVMD MMR,BRC

利用前半周期 利用前半周期 利用后半周期 利用后半周期

14

CPU同时访问DARAM的同一存储器块就会发生时 序上的冲突的情况:

同时从同一存储器块中取指和取操作数(都在 前半个周期);

同时对同一存储器块进行写操作和读(第二个 数)操作(都在后半周期)。

如何利用流水线技术提高程序执行效率(一)

如何利用流水线技术提高程序执行效率1. 概述流水线技术是一种将任务划分成不同的阶段,并将每个阶段分配给不同的处理单元并行执行的方法。

在计算机领域中,流水线技术被广泛应用于提高程序的执行效率。

本文将探讨如何利用流水线技术提高程序执行效率的方法和技巧。

2. 流水线的基本原理流水线技术的基本原理是将一个复杂的任务划分为多个简单的子任务,并将每个子任务分配给不同的处理单元并行执行。

这样可以有效利用计算资源,提高任务的处理速度。

在计算机程序中,流水线的基本操作包括取指令、译码、执行和写回。

3. 任务划分的重要性在利用流水线技术提高程序执行效率时,任务的划分是至关重要的。

合理的任务划分可以使得各个子任务在流水线中能够高效地执行,并充分利用计算资源。

为了达到最佳的任务划分效果,需要对程序进行详细的分析和测试,了解各个子任务的执行时间和依赖关系,并根据这些信息进行任务划分的决策。

4. 数据冲突的处理在流水线中,由于不同的子任务的执行需要依赖之前的结果,导致可能出现数据冲突的情况。

数据冲突会导致流水线的停顿,降低程序的执行效率。

为了减少数据冲突的发生,可以采取一些措施,例如引入冲突检测机制、增加数据缓冲区、调整任务划分等方法。

通过合理的措施,可以最大程度地减少数据冲突的发生,提高程序执行效率。

5. 分支预测的优化在流水线中,分支指令对程序执行效率的影响非常大。

由于分支指令的执行结果不确定,很可能导致流水线的停顿和重新启动,从而降低程序的执行效率。

为了优化分支指令的执行,可以引入分支预测的技术。

分支预测通过分析程序的分支历史和模式,对分支指令的结果进行预测,从而减少流水线的停顿和重新启动,提高程序的执行效率。

6. 内外存数据传输的优化在一些计算密集型的程序中,频繁的内外存数据传输也是降低程序执行效率的因素之一。

为了优化数据传输,可以采用多级缓存、数据压缩和预取等技术。

多级缓存可以在处理器和内存之间增加一层缓存,将频繁使用的数据存放在缓存中,减少数据的传输时间。

流水线技术

流水线技术流水线技术是一种高效的生产工艺,能够大大提高生产效率和降低成本。

它被广泛应用于各种制造行业,如汽车制造、电子产品制造、食品加工等。

本文将对流水线技术的原理、优势和应用进行详细介绍。

一、流水线技术原理流水线技术的核心原理是将整个生产过程划分为若干个连续的独立工作站,每个工作站负责完成一项具体的任务或工序。

产品在流水线上按照固定的顺序经过各个工作站,每个工作站只需完成相应的工序,然后将产品传递给下一个工作站。

流水线技术的顺序流程可以按照产品的不同特性和工艺要求来设计。

有些产品需要按照指定的工序顺序进行处理,而有些产品则需要在流水线上经过多个不同的工作站进行加工,以达到最终的成品要求。

二、流水线技术的优势1. 提高生产效率:通过将生产过程进行细分并利用并行处理,流水线技术可以大大提高生产效率。

工作站之间的协调和衔接使得产品在不间断流动的情况下进行加工,从而减少了非价值增加的等待时间。

2. 降低生产成本:在流水线上,人力资源的利用更加高效,无需每个工人都掌握所有工序的技能,只需要专注于自己所负责的工序。

这不仅可以提高工人的专注度,还可以降低培训成本。

3. 简化管理:流水线技术可以将复杂的制造过程分解成若干个简单的工序,每个工序由专人负责,使得生产管理更加简化。

管理者只需监控整个流水线的运行情况和协调各个工序的衔接,而不需要详细了解每个具体工序的细节。

4. 质量可控性强:流水线上的每个工序都可以进行专门的检测和控制,确保产品在各个工序中的质量。

一旦出现质量问题,可以及时追溯到具体的工序和责任人,以便进行纠正和改进。

三、流水线技术的应用1. 汽车制造:汽车生产过程中各个工序的高度标准化和流程化使得流水线技术成为汽车制造的理想选择。

从焊接、涂装到总装,每个工作站都有专业的操作人员,确保汽车制造过程的高效和质量。

2. 电子产品制造:电子产品制造过程中需要经过多个工序,如组装、焊接、测试等。

流水线技术可以有效地管理这些工序,提高生产效率和保证产品质量。

第三章流水线技术.ppt

ExtOp

MemtoReg

ALUSelB

chapter3.3

3.1 流水线的基本概念

• 洗衣为例 • Ann, Brian, Cathy, Dave 每人进行洗衣的动作: wash, dry, and fold • washer需要 30 minutes • Dryer 需要 40 minutes • “Folder” 需要 20 minutes A B C D

– 45 ns/cycle x 1 CPI x 100 inst = 4500 ns

• 多周期机器

– 10 ns/cycle x 4.6 CPI (due to inst mix) x 100 inst = 4600 ns

• 理想流水线机器

– 10 ns/cycle x (1 CPI x 100 inst + 4 cycle drain) = 1040 ns

32

WrAdr 32 Din Dout

Ideal Memory

Rt 0 Rd

Reg File

busA A

32

2019/3/18

Mux

32

4 B

32

Mem Data Reg

0

1 Mux 0

Mux

1

32

1

2 3

32 32

<< 2

ALU Control

Imm 16

Extend

32

ALUOp

中国科学技术大学

• Step 2 step

ID - instruction decode and register fetch

– A <-- Regs[IR6..10] – B <-- Regs[IR11..16]

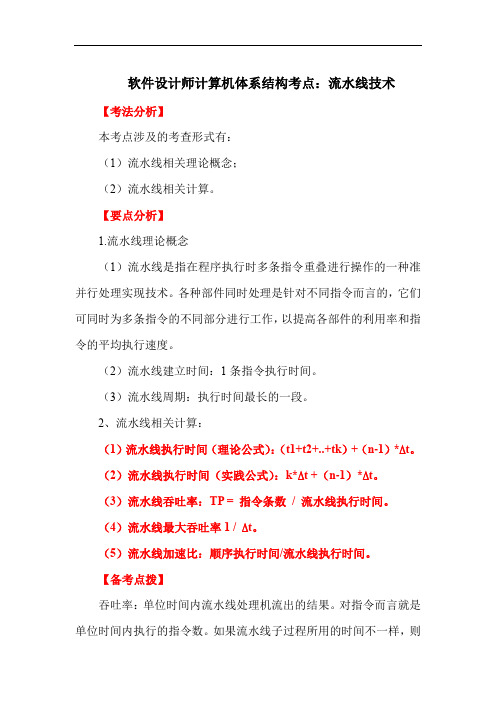

软件设计师计算机体系结构考点:流水线技术

软件设计师计算机体系结构考点:流水线技术【考法分析】本考点涉及的考查形式有:(1)流水线相关理论概念;(2)流水线相关计算。

【要点分析】1.流水线理论概念(1)流水线是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。

各种部件同时处理是针对不同指令而言的,它们可同时为多条指令的不同部分进行工作,以提高各部件的利用率和指令的平均执行速度。

(2)流水线建立时间:1条指令执行时间。

(3)流水线周期:执行时间最长的一段。

2、流水线相关计算:(1)流水线执行时间(理论公式):(t1+t2+..+tk)+(n-1)*∆t。

(2)流水线执行时间(实践公式):k*∆t +(n-1)*∆t。

(3)流水线吞吐率:TP = 指令条数/ 流水线执行时间。

(4)流水线最大吞吐率1 / ∆t。

(5)流水线加速比:顺序执行时间/流水线执行时间。

【备考点拨】吞吐率:单位时间内流水线处理机流出的结果。

对指令而言就是单位时间内执行的指令数。

如果流水线子过程所用的时间不一样,则吞吐率P应为(最长子过程的倒数)。

流水线开始工作,需要经过一段时间才能达到最大吞吐率。

【相关考题】1.下列关于流水线方式执行指令的叙述中,不正确的是()。

A.流水线方式可提高单条指令的执行速度B.流水线方式下可同时执行多条指令C.流水线方式提高了各部件的利用率D.流水线方式提高了系统的吞吐率2.流水线的吞吐率是指单位时间流水线处理的任务数,如果各段流水的操作时间不同,则流水线的吞吐率是()的倒数。

A. 最短流水段操作时间B. 各段流水的操作时间总和C. 最长流水段操作时间D. 流水段乘以最长流水段操作时间。

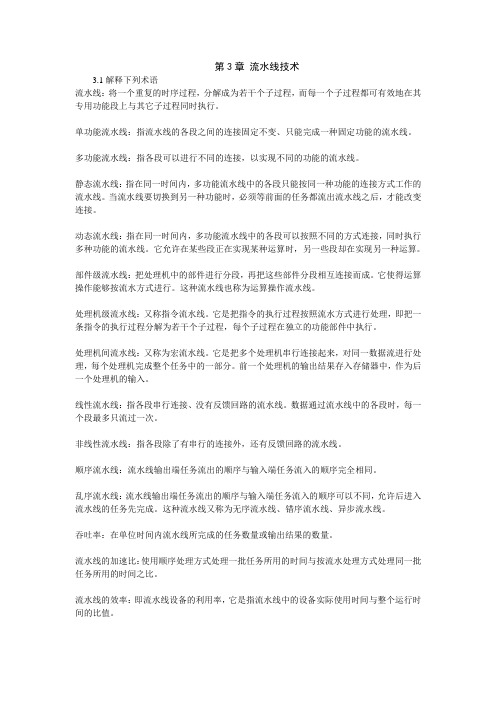

第三章 流水线技术

第3章流水线技术3.1解释下列术语流水线:将一个重复的时序过程,分解成为若干个子过程,而每一个子过程都可有效地在其专用功能段上与其它子过程同时执行。

单功能流水线:指流水线的各段之间的连接固定不变、只能完成一种固定功能的流水线。

多功能流水线:指各段可以进行不同的连接,以实现不同的功能的流水线。

静态流水线:指在同一时间内,多功能流水线中的各段只能按同一种功能的连接方式工作的流水线。

当流水线要切换到另一种功能时,必须等前面的任务都流出流水线之后,才能改变连接。

动态流水线:指在同一时间内,多功能流水线中的各段可以按照不同的方式连接,同时执行多种功能的流水线。

它允许在某些段正在实现某种运算时,另一些段却在实现另一种运算。

部件级流水线:把处理机中的部件进行分段,再把这些部件分段相互连接而成。

它使得运算操作能够按流水方式进行。

这种流水线也称为运算操作流水线。

处理机级流水线:又称指令流水线。

它是把指令的执行过程按照流水方式进行处理,即把一条指令的执行过程分解为若干个子过程,每个子过程在独立的功能部件中执行。

处理机间流水线:又称为宏流水线。

它是把多个处理机串行连接起来,对同一数据流进行处理,每个处理机完成整个任务中的一部分。

前一个处理机的输出结果存入存储器中,作为后一个处理机的输入。

线性流水线:指各段串行连接、没有反馈回路的流水线。

数据通过流水线中的各段时,每一个段最多只流过一次。

非线性流水线:指各段除了有串行的连接外,还有反馈回路的流水线。

顺序流水线:流水线输出端任务流出的顺序与输入端任务流入的顺序完全相同。

乱序流水线:流水线输出端任务流出的顺序与输入端任务流入的顺序可以不同,允许后进入流水线的任务先完成。

这种流水线又称为无序流水线、错序流水线、异步流水线。

吞吐率:在单位时间内流水线所完成的任务数量或输出结果的数量。

流水线的加速比:使用顺序处理方式处理一批任务所用的时间与按流水处理方式处理同一批任务所用的时间之比。

流水线技术 ppt课件

T P T 1 T 2 T K(n 1 ) M a x(T 1,T 2, T K )

▪K为流水线段数,Ti为第i段所需要的时间

❖指令流水线的吞吐率

单位时间内流水线所完成的指令数

n TP

kT (n 1)T

▪N为通过流水线的指令数 ▪T为指令流水线各个流水段的时间 ▪kT为指令流水线的填充时间

ADD R1, R2, R3 ; (R1) + (R2) → R3 OR R3, R2, R6 ; (R2) ^ (R3) → R6 SUB R3, R4, R5 ; (R4) - (R3) → R5

时钟周期 1 2 3 4

5

6

ADD IF ID EX —— WB

OR

IF ID EX —— WB

6

❖最大吞吐率

当流水线充满之后,理想情况下每个周期都有一条指令完成

1 T P max

T

❖最大吞吐率和实际吞吐率之间的关系

TPkT(n n1)Tkn n1T 11k 11TPm ax n

当n>>k时,TP≈TPmax

❖MIPS与吞吐率

TPMIPS106

MIPS:单位时间内所完成的指令数

7

❖加速比

时钟周期 1 2 3 4 5

6

7

8

指令1 IF ID EX MEM WB

指令2

IF ID EX MEM WB

指令3

IF ID EX MEM WB

指令4

IF ID EX MEM WB

13

❖争用同一个硬件资源,又称资源相关、冲突

时钟周期 1 2 3 4

5

6

7

8

指令1 Ik时,Sp≈k 增加流水线深度可以提高加速比

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第十一讲流水线操作技术

一、流水线操作

二、延迟分支转移的流水线图

三、条件招待指令的流水线图:

四、双寻址存储器的流水线冲突

五、流水线的冲突问题

指令字、单字指令、双字指令、多字指令:

指令字:表征指令的二进制代码,由操作码和操作数组成

单字指令:由16位二进制代码表示的指令(1个字)

双字指令:由32位二进制代码表示的指令(2个字)

多字指令:由n*16位二进制代码表示的指令(n个字)

说明:

1)执行一条单字指令至少需要1个指令周期(6个机器周期)

2)执行一条双字至少指令需要2个指令周期

3)程序执行时只能依次取出一个指令字,不能同时取出两个指令字

1)一般在一条指令中操作码占8位,其余为操作数位

2)若操作数不超过8位则为单字指令,否则为双字指令或多字指令3)立即数寻址为单字(立即数为3、5、8位),双字(9、16位)4)绝对地址寻址为双字指令

5)累加器寻址为单字(*ARx)或双字(#lk)指令

6)直接寻址为单字指令

7)间接寻址为单字指令

9)存储器映象寄存器寻址为单字指令

10)堆栈寻址为单字指令

双操作数间接寻址的指令格式:单字指令

机器周期、指令周期、

1个机器周期

1个指令周期

基于流水线的存储器访问:

二、延迟分支转移的流水线图:

取出要转移的

地址完成转移

知道要转移得到转移的地址将要转移的地址加载PAB

执行转移只需2个周期

实现转移

浪费2个周期

开始执行转移

实际使用4个周期

1)被冲洗掉的两个单周期指令并不占用转移后指令的执行阶段,它们刚好是在各级错开的。

2)在6级流水线中执行双字分支转移转移指令必须要4个机器(即4个指令周期)周期才能完成,在满流水线中执行相当于只占用2个指令周期(机器周期),另外2个周期可用于完成两条单周期指令或一条双周期指令的执行。

3)采用延迟分支转移指令可利用转移指令后的两个周期,即在延迟分支转移指令后安排两条单周期或一条双周期指令,该指令不能是分支或重

复指令。

4)具有延迟操作功能的指令有:

BD FBD BACCD FBACCD BANZD CALLD CALLD FCALLD FCALLD RETD FRETD RETED FRETED RETFD FRETD CCD RCD

例3-9 在完成R=(x+y)*z操作后转移至next r的程序段有两种编写方式:

利用普通分支转移指令B

LD @ x , A

ADD @ y , A

STL A , @ s

LD @ s , T

MPY @ z , A

STL A , @ R

B next

共8个指令字,10个指令周期利用延迟分支转移指令BD LD @ x , A

ADD @ y , A

STL A , @ s

LD @ s , T

BD next

MPY @ z , A

STL A , @ R

共8个指令字,8个指令周期

利用普通分支转移指令B LD @ x , A ADD @ y , A

STL A , @ s

LD @ s , T MPY @ z , A

STL A , @ R

B next

共8个指令字,10个指令周期LD @ x , A

ADD @ y , A

STL A , @ s

LD @ s , T

MPY @ z , A

STL A , @ R

B next

完成转移

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

LD @ x , A

ADD @ y , A

STL A , @ s

LD @ s , T

MPY @ z , A

STL A , @ R

BD next

完成转移

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

利用延迟分支转移指令BD LD @ x , A ADD @ y , A STL A , @ s LD @ s , T BD next MPY @ z , A STL A , @ R 共8个指令字,8个指令周期

三、条件招待指令的流水线图:

条件招待指令:XC n , cond [ , cond , [ ,cond ]]

求解条件决定后面

指令是否执行

1)条件执行指令是一条单字单周期指令,比条件跳转指令快。

2)条件在XC指令进入执行阶段的前两个周期已经求解出来,如果在这之后到执行前改变条件(如发生中断),将会造成无法预期的结果,所以要尽国避免在XC指令执行前两个周

期改变所规定的条件。

四、双寻址存储器的流水线冲突:

1。

C54x片内的双寻址存储器(DARAM)分成若干独立的存储器块,允许CPU在单个周期内对其进行两次访问,包括三种情况:

1)在单周期内允许同时访问DARAM的不同块,不会带来时序上的冲突;

2)当流水线中的一条指令访问某一存储器块时,允许流水线中处于同一级的另一条指令访问另一存储器块,不会带来时序上的冲突;

3)允许处于流水线不同级上的两条指令同时访问同一个存储器块,不会带来时序上的冲突。

2。

CPU能够在单周期内对DARAM进行两次访问,是利用一次访问中对前、后半个周期分时进行的缘故,具体为:

对PAB/PB取指利用前半周期

对DAB/DB读取第一个数据利用前半周期

对CAB/CB读取每二个数据利用后半周期

对EAB/EB将数据写存储器利用后半周期

3)如果CPU同时访问DARAM的同存储器块时就会发生时序上的冲突:

1)同时从同一存储器块取指和取操作数(都有在前半个周期)

2)同时对同存储器块进行写操作和读第二个操作数(都在后半个周期)

上述两种冲突CPU将通过自动插入一个空闲周期或将写操作延迟一个周期的办法解决。

Dual-Access Memory and the Pipeline DARAM Blocks

Half-Cycle Accesses to Dual-Access Memory

读*AR2

五、流水线的冲突问题:

1。

冲突存在方面:

1)同时访问同一存储器空间的冲突;

2)读、写同一存储器单元在时序上的颠倒,导致读数错误。

2。

对流水线冲突的解决方法:

1)插入等待周期(人工插入、编译时自动插入)

自动插入只能解决明显的同时访存冲突

隐含的时序错乱只能人工插入

2)编程序时全理安排指令的先后顺序

3)用C语言编写程序

4)对其内容不经常变动的存储器映象寄存器早安排初始化的写操作 5)利用等待周期插入所需的等待周期

五、解决流水线冲突的例子:

1。

采用保护性写操作解决流水线冲突

STM A , AR1

LD *AR1 , B

W N

写到AR1将AR1中数据放DAB 时序错乱,AR1中内容

还没有来得及改变STM #lk , AR1LD *AR1 , B

W #lk N

保护性写操作,立即译码后马上写到AR1,(写提前一周期)双字指令

隐含周期

采用保护性写操作使写AR1提前一周

期,改用双字指令插入一隐含周期,

则读AR1延迟一周期,结果W 比N 早

一周期

2。

通过插入NOP 解决流水线冲突:STLM A , AR0W #10

W W STM #10 , AR1

LD *AR1 , B 双字指令单字指令单字指令自动插入等待周期解决

N

写AR1

读AR1放DAB 存在时序错乱问题STLM A , AR0

STM #10 , AR1NOP LD *AR1 , B W

W

N

通过插入一空操作

使读AR1延迟一周

期,在写AR1之后

3。

用等待周期表解决流水线冲突问题:

根据指令特点查等待周期表得到所需插入的空操作个数自已看书。