MOS电容器.ppt

MOS概述及应用PPT课件

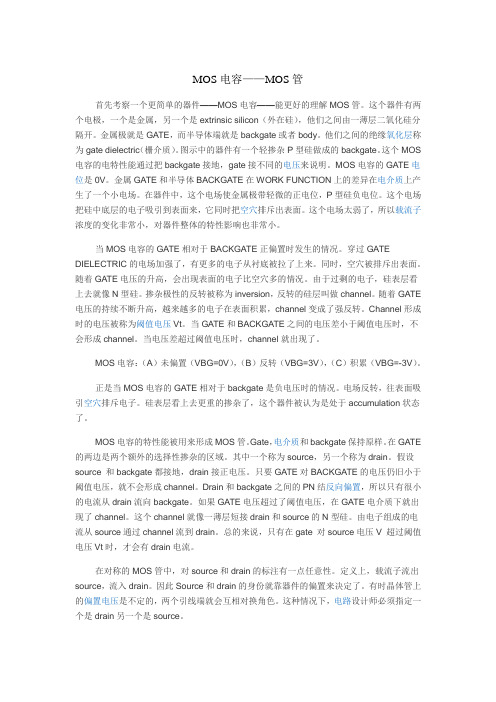

*

(5)、控制器中的MOS经常“坏掉”,到底是什么原因? 1. 控制器温度过高,将功率管“烧”坏,打开控制器可以看到功率管上面的塑封体被烧化了.这主要是控制器长期在大电流下运行造成的,可能是MOS与散热片上的螺丝未拧紧导致散热不良。连接MOS的螺丝和塑料粒子也容易变形烧坏,可以在塑料粒子和螺丝之间再垫上金属平垫片和弹簧垫片,保证塑料粒子被压紧,同时散热性能也会好点。 2.另外,控制器软件和硬件保护做的又不到位,还有驱动电路与功率管不匹配都会导致这种问题。建议客户将样品寄给我们,以便匹配; 3. 电机本身设计的不好。这点从相对地波形容易看出。如果相对地波形不是梯形波,而是有明显的电压突变现象,就会使dV/dt过大,也会导致MOS管易坏,这点建议电机厂修改电机。

*

垂直导电MOSFET

根据栅氧槽形状,可分成VMOS、UMOS、TMOS、DMOS等

*

1001M导电结构

1001纵向剖面图

*

MOS主要应用范围

高压MOS: 1、 PC电源:2N60、4N60、10N60 2、节能灯:830(5A500V)、840(8A500V)、 3、 电子镇流器:830、840、5N50; 4、 充电器、笔记本适配器:1N60、2N60、4N60、5N60、6N60、7N60、8N60、10N60; 低压MOS: 5、 电动工具:60N06、; 6、 电动车: 1001、1808 ; 7、 锂电池保护:8205; 8、 UPS:1001、1707;

MOS动态参数

*

MOS参数中英文对照表

*

MOS动态参数

gfs---正向跨导 。表示栅源电压UGS — 对漏极电流ID的控制能力,即漏极电流ID变化量与栅源电压UGS变化量的比值. dv/dt---电压上升率(控制器电路参数) 由于MOSFET的封装电感和线路的杂散电感的存在,在MOSFET反向恢复电流Irr突然关断时,MOSFET上的电压Vds会出现振铃,导致Vds超过MOSFET的BVDSS从而发生雪崩现象。 若MOSFET的米勒电容Cgd 偏大的同时且VTH又偏小,则MOSFET在关闭的瞬间,将在GS端感应出电压(与dv/dt、Cgd、Cgs、RG相关),若该电压大于VTH,则将导致Cdv/dt感应导通。

《mos管工作原理》ppt课件

用一个箭头表示一个mos管,箭头的一端是源极(s),另一端是漏极(d) ,中间是控制极(g)。

Mos管的开关原理

导通状态

当在控制极上加正电压时,氧化层下方的半导体层中的电子被排斥,形成一条从 源极到漏极的导电通道,电流可以通过这个通道流动。

关断状态

当在控制极上加负电压时,氧化层下方的半导体层中的电子被吸引,导电通道被 切断,电流无法通过。

《Mos管工作原理》ppt课件

2023-10-27

contents

目录

• Mos管简介 • Mos管的结构与原理 • Mos管的特性与参数 • Mos管的驱动与控制 • Mos管的应用实例 • Mos管的未来发展与趋势 • 总结与展望

01

Mos管简介

Mos管的概念

Mos管是金属氧化物半导体管的缩写,是一种具有极高开关 速度和低功耗的半导体器件。

Mos管在马达驱动中的应用

1 2

直流马达驱动

Mos管在直流马达驱动中作为开关器件,通过 控制电流的方向和大小来驱动马达运转。

步进马达驱动

步进马达驱动中,Mos管作为开关器件,控制 电流的方向和大小来驱动马达运转。

3

伺服马达驱动

伺服马达驱动中,Mos管作为开关器件,控制 电流的方向和大小来驱动马达运转。

集成元件控制电路

02

使用集成元件(如运算放大器、比较器等)构成开关控制电路

。

数字信号控制电路

03

使用数字信号(如TTL、CMOS等)构成开关控制电路。

Mos管的保护电路

过电压保护电路

当Mos管承受过电压时,保护电路可以保护Mos管不被损坏。

过电流保护电路

当Mos管承受过电流时,保护电路可以保护Mos管不被损坏。

MOS管电路工作原理和详解优质PPT课件

小提示: MOS管中的寄生二极管方向是关键。

电路符号

小结:“MOS管用作开关时在电路中的连接方法”

NMOS管:

D极接输入; S极接输出。

PMOS管:

S极接输入; D极接输出。

输出端

S极

G极

N沟道

输入端

S极

G极

P沟道

D极

输入端

导通时

D极

输出端

导通时

电路符号

反证:

看看我们常见的NMOS管4816:

请注意:不论NMOS管还是PMOS管,上述PIN脚的确定方法都是一样的。

假如MOS管表面磨损,或是无法辨认PIN1的标记圆点,你可以用什么 方法确认PIN1脚,以及G极,D极和S极? 拿出万用表,试试吧!

实物

再来看看相似的DFN封装MOS管:

外形上来看,DNF封装的MOS管仍旧有8个脚,但已经变成贴片形式, 节约了高度,散热性能更好些。 但其PIN脚极性还是一样排列。

实物

最后,3PIN脚的MOS管: (1)SOT-23

3

D

G

S

1

2

PIN1为G极;PIN2为S极;PIN3为D极。

图纸习惯

但请大家特别注意:主板上标示的PIN1与PIN2脚与此刚好颠倒了。

主板图纸上也是如此。 而且,似乎作为一种错误的习惯被保持了下来。

另外一种3PIN脚的MOS管: (2)TO-252

电路符号

19V

Adapter

BAT 12V

Q1 Q2 隔离

19V 3. 适配器+电池

问题:如果不用Q2隔离,同时插上适配器和电池会怎样?

现象是: 大电流。 当然这只有在维修稳压电源上才可以看到:电流直接达到 稳压电源的最大值6A以上,短路灯狂闪。

MOS电容

MOS电容——MOS管首先考察一个更简单的器件——MOS电容——能更好的理解MOS管。

这个器件有两个电极,一个是金属,另一个是extrinsic silicon(外在硅),他们之间由一薄层二氧化硅分隔开。

金属极就是GATE,而半导体端就是backgate或者body。

他们之间的绝缘氧化层称为gate dielectric(栅介质)。

图示中的器件有一个轻掺杂P型硅做成的backgate。

这个MOS 电容的电特性能通过把backgate接地,gate接不同的电压来说明。

MOS电容的GATE电位是0V。

金属GATE和半导体BACKGATE在WORK FUNCTION上的差异在电介质上产生了一个小电场。

在器件中,这个电场使金属极带轻微的正电位,P型硅负电位。

这个电场把硅中底层的电子吸引到表面来,它同时把空穴排斥出表面。

这个电场太弱了,所以载流子浓度的变化非常小,对器件整体的特性影响也非常小。

当MOS电容的GATE相对于BACKGATE正偏置时发生的情况。

穿过GATE DIELECTRIC的电场加强了,有更多的电子从衬底被拉了上来。

同时,空穴被排斥出表面。

随着GATE电压的升高,会出现表面的电子比空穴多的情况。

由于过剩的电子,硅表层看上去就像N型硅。

掺杂极性的反转被称为inversion,反转的硅层叫做channel。

随着GATE 电压的持续不断升高,越来越多的电子在表面积累,channel变成了强反转。

Channel形成时的电压被称为阈值电压Vt。

当GATE和BACKGATE之间的电压差小于阈值电压时,不会形成channel。

当电压差超过阈值电压时,channel就出现了。

MOS电容:(A)未偏置(VBG=0V),(B)反转(VBG=3V),(C)积累(VBG=-3V)。

正是当MOS电容的GATE相对于backgate是负电压时的情况。

电场反转,往表面吸引空穴排斥电子。

硅表层看上去更重的掺杂了,这个器件被认为是处于accumulation状态了。

22 第六章 6.2 理想MOS电容器

+

Physics of Semiconductor Devices

耗尽区归一化电容为:

归一化电容随外加偏压的增加而减小

Physics of Semiconductor Devices

耗尽区归一化电容随外加偏压的变化关系 (归一化电容随外加偏压的增加而减小)

Physics of Semiconductor Devices

physicssemiconductordevicesphysicssemiconductordevicesphysicssemiconductordevices高频条件下归一化电容极小值与半导体掺杂浓度和氧化层厚度的关系正比厚度正比掺杂浓度physicssemiconductordevicesphysicssemiconductordevicesphysicssemiconductordevices在接近强反型区如果测量电容的信号频率比较低耗尽层中电子空穴对的产生与复合过程能跟得上信号的变化这时反型层中的电子电荷的变化屏蔽了信号电场dq对表面电容的贡献是主要的而耗尽层的宽度和电荷q基本上不变

Physics of Semiconductor Devices 归 一 化 电 容

积累区的C-V特性

MOS电容积累区的C-V特性

Physics of Semiconductor Devices

2. 平带情况(VG=0)

VG=0时,φS=0,能带是平直的,称为平带情 况 在平带附近,空间电荷区中:

4. 反型区(VG>0)

实际证明,出现反型层以后的电容C与测量频率有很大关 系,所谓电容C与测量频率有关,就是与交变信号电压的 频率有关。

测量方法:

在测量电容 C 时,在MOS 系统上施加有直流偏压 VG,然后 在VG之上再加小信号的交变电压,使电荷QM变化,从而测

模拟cmos集成电路设计拉扎维MOS器件物理基础PPT课件

第23页/共61页

跨导gm

VGS对IDS的控制能力 IDS对VGS变化的灵敏度

gm ID VGS VDS cons tant

• 直流关系式-I/V特性 • 交流关系式-小信号电路中的参数

第6页/共61页

MOS管简化模型

简化模型——开关 由VG控制的一个开关

第7页/共61页

MOS管的结构

Bulk(body)

源漏在物理结构上是完全对称的,靠什么区分开?

提供载流子的端口为源,收集载流子的端口为漏

最重要的工作区域?

受VG控制的沟道区

• 小信号模型 • 信号相对于偏置工作点而言比较小、不会显著影响偏置工作点时用该模型简化计算 • 由gm、 gmb、rO等构成低频小信号模型,高频时还需加上 CGS等寄生电容、寄生电阻(接触孔电阻、 导电层电阻等)

沟道电荷的产生

当VG大到一定 程度时,表面势 使电子从源流向 沟道区 VTH定义为表面电 子浓度等于衬底 多子浓度时的VG

第12页/共61页

阈值电压

0 栅与衬底功函数差

COX

OX

TOX

常通过沟道注入把VTH0调节到合适值 工艺确定后,VTH0就固定了,设计者无法改变

第13页/共61页

I/V特性-沟道随VDS的变化

第3页/共61页

掌握器件物理知识的必要性

• 数字电路设计师一般不需要进入器件内部,只把它当开关用即可 • AIC设计师必须进入器件内部,具备器件物理知识

• MOS管是AIC的基本元件 • MOS管的电特性与器件内部的物理机制密切相关,设计时需将两者结

22 第六章 62 理想MOS电容器讲解

1. 积累区(VG<0)

Physics of Semiconductor Devices

当MOS电容器的金属电极上加有较大的负偏压时,能带明显向 上弯曲,在表面造成多数载流子空穴的大量积累;只要表面势

φS稍有变化,就会引起表面空间电荷QS的很大变化;所以,半

导体表面电容比较大,可以忽略不计。MOS系统的电容基本上 等于绝缘体电容C0。

Physics of Semiconductor Devices

两个电容串联后,总电容变小,且其数值主要由较小的一个电 容所决定,因为大部分电压都降落在较小的电容上。

MOS电容的等效电路

C/C0称为系统的归一化电容

VG

C0 CS

对于理想MOS系统:

Physics of Semiconductor Devices

MOS电容积累区的C-V特性

2. 平带情况(VG=0)

Physics of Semiconductor Devices

VG=0时,φS=0,能带是平直的,称为平带情 况 在平带附近,空间电荷区中:

由空穴的过剩或欠缺引起的电荷密度:

在平带附近,׀φ<<׀VT。上式进行指数项展开,且只保留前两项:

空间电荷与表面 势符号相反

平带情况下半导体表面的小信号电容(微分电容):

在杂质饱和电离的情况下: 归一化平带电容:

Physics of Semiconductor Devices

正比掺杂浓度 正比厚度

理想MOS的归一化平带电容随杂质浓度和氧化层厚度的关系

3. 耗尽区(VG>0)

耗尽区:

Physics of Semiconductor Devices

Physics of Semiconductor Devices

MOS电容器及MOSFET资料PPT教案

。因为N A

ni

exp

q B kT

,由

半导体表面

EC

ΨS

qNAW 2 2 s

qS

q

S0

Eg

q B

Ei

EF

可得

Ψs

inv

2Ψ B

2kT q

ln

NA ni

氧化层

x

半导体

EV

上式表明需要一个电势 ΨB将能带弯曲至表面本征的条件( Ei=EF);接着能带还需要再弯曲一个qΨB,以使表面达到强反 型的状态。

VT

QS Co

ΨS

inv

qN AWm Co

ΨS

inv

2 sqN A Co

2Ψ B

2Ψ B

第13页/共17页

14

一旦强反型发生,总电容将保持在最小值,此时有Cj=εs/Wm

Cmin

d

ox ox s

Wm

Co V

一理想MOS电容器的典型电容-电 压特性如右图所示,包含耗尽近似

Co d Cj

VT

Cmin

仿照单边n+-p结空间电荷区结论,表面势Ψs为

ΨS

qNAW 2

2 s

其中NA为半导体掺杂浓度,W为半导体耗尽区宽度,εs为半导体介电 常数。

第8页/共17页

9

当Ψs>ΨB,表面发生反型。需要一个判据来判断强反型的起点 。在此之后则反型层中的电荷变得相当显著。

表面电子浓度等于衬底杂质浓度是一个简单的判据,即ns=NA

MOS电容器及MOSFET资料

会计学

1

本章内容

理想的MOS电 容器

SiO2-Si MOS电 容器

MOSFET基第本1页/共原17页 理

第4讲 MOS管的电容和讲解

VGS<0

B

堆积状态的等效电容

主要的电容Cgb串联了一个较大的电阻

G

Cgs

Cgb

Cgd

gnd

耗尽状态

VGS不是足够“负”,也不是足够“正”,栅氧化层下 方自由电子或空穴浓度都很低,下极板情况复杂,电容 随电压变化。 +

B S VGS G 少量数目电子 D

FOXP+Fra bibliotekFOX

N+ 耗尽层

N+ 耗尽层与栅氧 化电容C串联

Cgd 漏

Cdb 栅 Csb Cgb Cgs 体

源

任何两极之间存在电容

作为电容使用的MOS管特性

R R

v S

G B D

v

C

在没有好的多晶电容的工艺中,常使用MOS管(栅) 作为电容。

堆积状态

当VGS<0时,空穴被吸附(堆积)到栅氧化层下 方,相当于电容的一个极板(另一个极板为多晶)。

S Cgs FOX P+ FOX N+ Ldiff P衬底 衬底电阻 堆积的空穴 + Cgd G D Cgd N+ Ldiff FOX

PMOS管输入输出特性曲线

阈值电压测量

有多种工程定义:本课程采用“输入特性曲线斜 率变化最大的点对应的电压”。

输出特性曲线

VGS=5V

线性区 饱和区

VGS=4V

VGS=3V

VGS=2V VGS=1V

线性区和饱和区的实验划分方法

线性区 饱和区

统一为:输出特性曲线中斜率变化最大的点。

一些概念问题

Cox

TOX是栅氧化层厚度

ox

TOX

栅极电容与MOS管的WL乘积成正比

chapt7 MOS电容-清华大学半导体物理

MOSFET是现代数字集成电路的核心器件。

MOSFET剖面图•MOSFET与半导体表面及半导体-绝缘层界面性质密切相关。

•MOSFET的核心部分是MOS(MIS)结构。

2半导体表面以及半导体-绝缘层界面性质;表面电场效应(是MOSFEF工作的基础);MOS结构C-V特性。

4由于晶格周期性在表面处中断而出现的局(定)域于表面附近的电子态——表面态禁带中的电子态数等于表面原子数,表面原子面密度∼1015/cm 2,所以表面能级准连续地分布在禁带中。

总之,表面态起因于周期场在表面处中断;空间上定域于晶体表面;能级位于禁带中。

7.1.1 表面态§7.1 半导体表面和Si -SiO 2界面界面性质。

量级;离子。

界面态起源于界面处的。

界面态和表面态性质相似:位于Si-SiO101214151617达到最大且基本不变;19变化引起数量很大的2122V。

FB2324包括两部分:;V不很大s很小。

27对交流小信号ΔVQ n完全跟上ΔV g变化。

32scC-V是非平衡的瞬态特性333435若栅压V g 为一由V 1(积累)到V 2(强反型)的阶跃电压,则V =V 2下电容随时间的变化曲线称为MOS 电容的C -t 特性。

由MOS 电容的C -t 特性可求耗尽层少子寿命τ和表面复合速度S 。

,取“−”号,取“+”号i FB归一化平带电容与氧化层厚度及衬底掺杂浓度的关系。

MOS管电路工作原理及详解PPT课件

我找到的一种解释是:

人们在使用笔记本电脑时,经常会同时插上适配器和电池。如果遇到

电网停电,笔记本会自动切换到电池12V供电。这个时候适配器虽然不再

供电,但仍相连在笔记本上。

如果没有Q1隔离,12V电压会直接进入适配器内部的输出电路,有可能

烧毁适配器。 这一解释自己没有做过验证,大家可以讨论一下对与错。

A

B

方法1:加入一个二级管

A

精选PPT课件

B

22

电路符号

方法2:加入MOS管

A

B

此处MOS管实现的功能就是:隔离作用。

所以,所谓的MOS管的隔离作用,其实质也就是实现电路 的单向导通,它就相当于一个二级管。

但在电路中我们常用隔离MOS,是因为: 使用二级管,导通时会有压降,会损失一些电压。而使用 MOS管做隔离,在正向导通时,在控制极加合适的电压,可以 让MOS管饱和导通,这样通过电流时几乎不产生压降。

以上MOS开关实现的是信号切换(高低电平切换)。 再来看个MOS开关实现电压通断的例子吧。

截止

0V

0V

由+1.5V_SUS产生+1.5V电路(1)

精选PPT课件

12

电路符号

MOS开关实现电压通断的例子:

导通

+1.5V

+15V

由+1.5V_SUS产生+1.5V电路(2)

精选PPT课件

13

电路符号

看过前面的例子,你能总结出“MOS管用做开关时在电路 中的连接方法”吗?

精选PPT课件

36

实物

再来看看相似的DFN封装MOS管:

外形上来看,DNF封装的MOS管仍旧有8个脚,但已经变成贴片形式, 节约了高度,散热性能更好些。 但其PIN脚极性还是一样排列。

《MOS存储器》PPT课件

(2)动态DRAM,利用电容来存储信息,需刷新.

优点:存储单元的元件数少,单元面积小,功耗低,适

合大规模集成;

缺点:需要复杂的刷新电路,对时序有严格要求,速度

比静态慢.

精选课件ppt

3

4.顺序存取存储器SAM(sequential access memory)

非随机存取的,存取次序受到限制: (1)先进先出存储器FIFO(first-in first-out ); (2)后进先出存储器LIFO(last-in first-out ); (3)移位寄存器(shift register); (4)按内容存取存储器(contents-addressable memory,CAM).

C S :电荷转移比

C S C BL

C S 一般为0.05PF CBL约为1PF,电荷转移比一般在

1%-10%之间.△V≈250m精v选课件ppt

9

讨论: ① △V很小,要有灵敏放大器; ②转移比要尽量大,在小面积得到尽可能大的电容是设计关

键; ③读取过程是“破坏性”的,CS中的电荷量发生了变化,读

• 谁也不连接,称为浮栅

• 2 因为有浮栅,跨导↓,VT ↑(相比普通MOS管) • 3 VT可以改变,即可以编程。当在源与栅漏之间加

15~20V的编程电压时,DS方向强电场会引发雪崩效应, 电子获得足够的能量(>3.2ev),借助VGS而穿过SiO2 进入浮栅。所以浮栅晶体管也称为浮栅雪崩注入MOS 管(floating gate avalanche-injection MOS transistor-FAMOS)

N+

N+

p

字线

位线

SiO2

W

公共电容

MOS电容PPT课件

弱 反 型 特征点VMG

• 在特征点处,硅衬底的表面处于本征硅的情形下 • 当能带的弯曲大于它时,禁带中央Ei线在某一点会穿过费米能级,使得费米

能级相较于离开价带顶的距离而言更接近于导带底 • 这意味着电子(P型衬底中的少子)的浓度大于硅表面空穴的浓度——在表

面产生了一个反型层

费米能级的变化表 示了什么?

第子)来自于热产生的电子-空穴对。 • 由于热产生是一个很缓慢的过程,电子无法快速的响应栅压的改变。 • 因此当栅信号的频率高于100Hz时,所描述的这种电容的增加无法观察到。 • 高频电容由所能达到的最大耗尽层宽度决定。

第15页/共33页

能带图

为什么要介绍MOS电容?

•随机存储器RAM的电荷存储元件 •频繁的应用于线性电路和数字电路中 •现代电子器件MOSFET,就是建立在MOS的 基础之上

第1页/共33页

集成电路结构

栅氧

为什么有P+?

场氧

氧化层的厚度为什 么不一样?

第2页/共33页

C-V曲线

第3页/共33页

剖面图 能带图

VG VFB 0

有效栅压

第4页/共33页

qs ——表面势

• 硅衬底中的能带弯曲量 • 是MOS电容特性中一个非常重要的 参数 • 表面势是相对于硅衬底的体势能的 一个参考能级 • 注意与功函数的区别!

第5页/共33页

积累模式

• 在积累模式,表面势的改变相较于栅压的改变量是可以被忽略的 • 这意味着栅压的任何变化的绝大部分都会穿过氧化层 • 电容等于栅氧电容,与栅压独立。

N型衬底的MOS电容阈值电压:

2 sqND

Cox

VT VFB 2 F 2 F

第24页/共33页

集成电路设计.pptx

MOS管有源电阻器

IDS I

I

VGS V VTP

DI

O

S

+

G+

G

V -

V-

O

I

S

D

VTN V VGS

IDS

(a)

(b)

MOS有源电阻及其I-V曲线

第23页/共66页

晶体管有源寄生电阻

双极晶体管集电区电阻 集成电路中集电区电阻Rc要比分立管的大。Rc的增大 会影响高频特性和开关性能。

第2页/共66页

Tox

N+

P

sio2

金 属

NP金s+io属2

纵向结构

横向结构

MOS 电容电容量

Cox=

Aε0 εsio2

Tox

Tox: 薄氧化层厚度;A: 薄氧化层上 金属电极的面积。

一般在集成电路中Tox 不能做的太薄,所以要想提高电容量,只能增加面积。 N+层为 了减小串联电阻及防止表面出现耗尽层。

集成电路中要制作一个30 pF的MOS电容器, 所用面积相当于25个晶体管的面积。

第3页/共66页

MOS电容 N+

SiO2 P+

AL

N+ N-epi

P-SUB

Al P+

第4页/共66页

❖ PN结电容 在PN结反偏时的势垒电容构成的电容器

❖ PN结电容与 MOS电容的数量级相当。

+

-

N+

P

N

外

P衬

第39页/共66页

第40页/共66页

CMOS反 相器工作 原理

输入端高电平时:

平带电压 mos电容

平带电压 mos电容

平带电压MOS电容是指在MOS(金属氧化物半导体)结构中的

电容器,其工作状态下电压保持平稳不变。

MOS电容是一种基本的电子器件,由金属电极、氧化物绝缘层

和半导体基底组成。

它的主要作用是存储电荷和调节电压。

在平带

电压条件下,MOS电容的工作模式是稳定的,电压保持不变。

从物理角度来看,MOS电容的工作原理是通过在金属电极和半

导体基底之间施加电压,形成氧化物绝缘层中的电场。

这个电场会

吸引或排斥电荷,从而改变电容器中的电荷分布。

当施加的电压保

持不变时,MOS电容的电荷分布也将保持稳定,因此称为平带电压。

MOS电容在集成电路中广泛应用,特别是在数字电路和模拟电

路中。

在数字电路中,MOS电容通常用于存储和传输二进制信息。

在模拟电路中,MOS电容可以用作滤波器、振荡器和放大器等功能

的关键组成部分。

此外,MOS电容还具有一些特殊的性质和应用。

例如,它可以

用于制作可调谐电容器,通过改变施加的电压来调节电容值。

这在

射频电路和通信系统中非常有用。

总结起来,平带电压MOS电容是一种能够在稳定电压条件下工作的电子器件,通过施加电压在氧化物绝缘层中形成电场,实现电荷的存储和调节。

它在集成电路中具有广泛的应用,是数字电路和模拟电路中重要的组成部分。

《第五章MOS器件》PPT课件

• 对于MOSFET来说,最令人关注的是反型的 表面状态。当栅偏压VG 0时,P型半导 体表面的电子浓度将大于空穴浓度,形成 与原来半导体导电类型相反的N型导电层, 它不是因掺杂而形成的,而是由于外加电 压产生电场而在原P型半导体表面感应出来 的,故称为感应反型层。这一反型层与P型 衬底之间被耗尽层隔开,它是MOSFET的导 电沟道,是器件是否正常工作的关键。反 型层与衬底间的P-N结常称为感应结。

电荷。单位为C/cm2。 QGQS 0

• 由于Q0是不变的,因此

2021/4/27

实用文档

15

中国科学技术大学物理系微电子专业

6、半导体表面状态

2021/4/27

实用文档

16

积累:

电荷分布 QS

中国科学技术大学物理系微电子专业

积累情况下能带图及电荷分布

-d

x

Qm

EiEF

PP nie

kT

E(X) 电场分布 靠近氧化层的半导体表面

形成空穴积累

x

2021/4/27

实用文档

17

耗尽:

Vg>0

EF

2021/4/27

中国科学技术大学物理系微电子专业

Ec

Ei EF E

v

(x) Qm

电荷分布

wx -d

电场分布

QscqNAW

E(X)

实用文档

x

18

强反型:

中国科学技术大学物理系微电子专业

2021/4/27

np nieEFEik T

实用文档

氧化物陷阱电荷Qot:和SiO2的缺陷有关,分布在SiO2 层内,和工艺过程有关的Qot可以通过低温退火除掉 大部分。

可动离子电荷Qm:如Na+等碱金属离子,在高温和高 压下工作时,它们可以在氧化层内移动。因此,在

MOS电容器.ppt

inversion regime

Vfb

0 Vt

Vg

Qinv

slope = Cox

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 5-15

5.6 MOS CV Characteristics C dQg dQs dVg dVg

Qinv

accumulation depletion

(b)

Vfb

Vt

inversion

Vg

slope = Cox

Qacc

slope = Cox

(c)

Vfb

Vt

Vg

accumulation depletion

inversion

Qs

accumulation depletion

regime

regime

C-V Meter

MOS Capacitor

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 5-16

5.6 MOS CV Characteristics

Qs

aSiO

V

dep---le---ti---on---la---y---er--- 2

charge, Q dep

P-Si body

qVox

qs

Ec

qVg Ec, Ef

-- --

Ef Ev

Wdep depletion

region Ev

M

OS

Vox

Qs Cox

Qdep Cox

第二章MOS器件物理基础2-4

MOS管的器件电容(1)

电容分为以下几类:

(1)栅与沟道之间的栅氧电容C1=WLCox,Cox为单位面积栅氧电容εox/tox; (2)衬底和沟道之间的耗尽层电容 C2 WL q si N sub 4 F (3)多晶硅与源和漏交叠产生的交叠电容C3和C4。

由于是环状的电场线, C3与C4不能简单地写成WdCox,需通过更复杂的 计算才能得到,且它的值与衬底偏置有关。

C j C j 0 1 VR B m

VR:通过PN结的反偏电压 Cj0:PN结在零偏时的结电容(与衬底浓度有关) ΦB :漏源区与衬底间PN结的内建电势

m:底面电容的梯度因子,一般取介于0.3与0.4间的数

MOS管的器件电容(3)

计算图示两种结构中源和漏的结电容

对于图a: CD B CSB WEC j 2(W E)C jsw

C表示栅极输入电容,该电容正比于WLCox 。

gm mCv gs g m vgs f m 2C

n fm (VGS VTH ) 2 2L

MOS管的最高工作频率与沟道长度的平方成反比,因此,减小MOS管 的沟道长度能很显著地提高工作频率 。 例如,MOS管L=0.25μm时,工作频率约40GHz,若L缩小到0.1μm时,工 作频率可达118GHz,说明深亚微米MOS器件可以满足射频电路的要求。

D

MOS管的电容随栅源电压的变化-截止区

漏源之间不存在沟道,则:

栅源、栅漏之间的电容为: CGD CGS CovW Cov:单位宽度的交叠电容。 栅与衬底间的电容为栅氧电容与耗尽区电容之间的串 联:

G

CGD

CDB

B

CGS

C SB CGB S

CCD工作原理有图片ppt课件

CCD工作过程的第三步是信号电荷包的转移, 就是将所收集起来的电荷包从一个像元转移到下 一个像元,直到全部电荷包输出完成的过程。

信号电荷的存储(示意图)

UG < Uth 时

+UG

UG > Uth 时

+UG

入射光

e-

e-

e-

e-

e-

+Uth

e- 势阱

ee-

MOS电容 器

入射光

e- e- e- e-

e-

e-

+Uth

e-

势阱

e-

MOS电容

器

为了规范事业单位聘用关系,建立和 完善适 应社会 主义市 场经济 体制的 事业单 位工作 人员聘 用制度 ,保障 用人单 位和职 工的合 法权益

光学系统Βιβλιοθήκη CCD图像处理为了规范事业单位聘用关系,建立和 完善适 应社会 主义市 场经济 体制的 事业单 位工作 人员聘 用制度 ,保障 用人单 位和职 工的合 法权益

CCD的最基本单元

MOS电容器是构成CCD 的最基本单元是,它是 金属—氧化物—半导体 (MOS)器件中结构最 为简单的。

金属电极 氧化物

入射光

e-

e-

e-

e- e-

e- e光生电子

金属电极 氧化物

半导体

MOS电容器

为了规范事业单位聘用关系,建立和 完善适 应社会 主义市 场经济 体制的 事业单 位工作 人员聘 用制度 ,保障 用人单 位和职 工的合 法权益

2、信号电荷的存储

CCD工作过程的第二步是信号电荷的收集, 就是将入射光子激励出的电荷收集起来成为信 号电荷包的过程。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Modern Semiconductor Devices for InteTgorax =te2d0Cnimrcuits (C. Hu)

Slide 5-10

ody

ody

5.5 Strong Inversion–Beyond Threshold

Vg > Vt

Wdep Wdmax

2 s 2B

qNa

Chapter 5 MOS Capacitor

MOS: Metal-Oxide-Semiconductor

Vg metal

Si body

gate SiO2

Vg

gate

SiO2

N+

N+

P-body

MOS capacitor

MOS transistor

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

A=B, and C = D

st

A D qVg = qVt Ec,Ef

Ec

C =qB

B

Ei Ef

Ev

st

2B

2

kT q

ln

Na ni

Ev M

OS

qB

Eg 2

(E f

Ev ) |bulk

kT q

ln

Nv ni

kT q

ln

Nv Na

kT q

Байду номын сангаас

ln

Na ni

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 5-9

Threshold Voltage

Tox = 20nm

Vt(V), P+gate/N-body

Vt(V), N+gate/P-body

Body Doping Density (cm-3)

Vt Vfb 2B

qNsu(ba)2 s 2 B

Cox

+ for P-body, – for N-body

accumulation.

S

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 5-4

5.2 Surface Accumulation

Vg <Vt

Gauss’s Law

Vox Vg V fb Vox Qacc / Cox

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 5-2

5.1 Flat-band Condition and Flat-band Voltage

E0

cSiO

=0.95

2

eV

Ec

qg 3.1 eV

3.1 eV cSi q s= cSi + (Ec–Ef)

Slide 5-8

Threshold Voltage

Vg Vfb φs Vox

At threshold,

st

2B

2

kT q

ln

Na ni

Vox

qNa 2 s 2B

Cox

Vt Vg at threshold Vfb 2B

qNa 2 s 2B

Cox

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

=4.05eV

Ec, Ef Ev

qVfb N+ -poly-Si

9 eV

Ec

Ef Ev P-body

The band is flat at

E0 : Vacuum level E0 – Ef : Work function E0 – Ec : Electron affinity Si/SiO2 energy barrier

Qacc Cox (Vg V fb )

Vox Qs / Cox

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 5-5

5.3 Surface Depletion ( Vg > Vfb )

gate

++++++

SiO

4.8 eV

Ev SiO2

the flat band voltage.

V fb g s

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 5-3

5.2 Surface Accumulation

3.1eV

Ec ,Ef Ev

Slide 5-1

Chapter 5 MOS Capacitor

Ec

N+polysilicon SiO2

P-Silicon body

Ef , Ec Ev

Gate

Ec Ef

Ev

Si Body

Ev

This energy-band diagram for Vg = 0 is not the simplest one.

Vg > Vt

gate

++++++++++

SiO2

Cox

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 5-6

5.3 Surface Depletion

Vg Vfb s Vox Vfb s

qNa 2 s s

Cox

This equation can be solved to yield s .

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 5-7

5.4 Threshold Condition and Threshold Voltage

Threshold (of inversion): ns = Na , or (Ec–Ef)surface= (Ef – Ev)bulk , or

V

dep---le---ti---on---la---y---er--- 2

charge, Q dep

P-Si body

qVox

qs

Ec

qVg Ec, Ef

-- --

Ef Ev

Wdep depletion

region Ev

M

OS

Vox

Qs Cox

Qdep Cox

qNaWdep Cox

qNa 2 s s

qVg

MO

Make Vg < Vfb

Vox

Vg V fb s Vox

s : surface potential, band

E0

bending

Vox: voltage across the oxide

q s Ec

Ef

s is negligible when

Ev

the surface is in