利用拨码开关控制液晶显示器进行ASIC字符显示

字符显示器的显示控制过程

字符显示器的显示控制过程关键词:字符图5.4 中的内容包括两大部分,顶端3个方框给出的是显示存储器VRAM,字符发生器(ROM器件),和一个用于提供视频信号的移位寄存器,在PC机系统中,这些内容被放到显示卡中,并由主机CPU 控制。

这一部分的功能,是依据当前被显示字符在屏幕上的位置为地址,到显示存储器中找出被显示字符的ASCII编码,再用字符的ASCII 编码和电子束所处的字符的点阵行位置为地址,到字符发生器中读出该字符的点阵行数据,接下来,把字符的点阵行数据送到移位寄存器中,通过逐位移位操作,在移位寄存器的移位输出端得到的就是被显示内容的显示点的控制信号,送到CRT的栅级实现对屏幕象素的显示控制。

图5.4 中的下面(在方框内)部分,是显示器的扫描控制逻辑,它是显示器设备本身的重要组成部分,其功能是控制电子束重复扫描整个显示屏幕。

这是一个产生多种时序控制信号的部件,其驱动源来自一个点振荡器,它以一定频率提供连续的脉冲信号,每个脉冲周期对应一个象素的显示过程,故它的输出既用作为产生视频信号的移位寄存器的移位控制信号,又用于驱动扫描控制逻辑按照扫描的时序要求,提供不同频率关系的时序控制信号,包括在屏幕上一个点阵行中区分字符分界控制信号(由点计数器提供),正在显示的字符位置控制信号及点阵行扫描结束及水平回扫(电子束从屏幕最右侧回到最左侧的过程)控制信号(由水平地址计数器提供);还包括用于区分字符行和行间距的控制信号(由光栅地址计数器提供),正在显示的字符行位置控制信号及"场"扫描结束及垂直回扫(电子束从屏幕最右下角回到最左上角的过程)控制信号(由垂直地址计数器提供);该图表示的是分辨率为720%350的例子,每行显示80个字符,一屏显示25行,故每个字符在屏幕上占据9%14个点阵(象素)位置,这样一个区域被称为一个字符窗口,点计数器中的9和行计数器中的14,就是用于确定字符窗口大小的。

AIS系统键盘显示模块功能要求

AIS系统键盘显示模块功能要求一、模块构成本模块由MUP A TMEGA128、键盘控制电路HD7279、液晶显示控制模块、485接口电路MAX1490、存储器IS61C1024、时钟电路DS1302、复位电路MAX6320P等组成。

由ATMEGA128的UART0和MAX1490构成与主机通信链路,完成数据通信。

HD7279完成键盘输入功能。

液晶显示控制模块完成显示功能(文字和图形显示)。

时钟电路是在与主机通信前(或无法从主机获取其满意的数据前)提供时间数据。

二、通信功能要求与主机通信是通过ATMEGA128的UART0和485接口电路MAX1490完成的(波特率暂定为115K bit/s)。

1.输入数据输入的数据主要有:接收到的数据、各模块的状态消息、告警信息、电台发出的数据、打包前的动态数据(GPS和传感器数据/秒)、消息确认消息、串口测试、串口测试确认消息、查询区域参数消息应答、查询历史数据信息应答等。

2.输出数据输出的数据主要有:显示单元状态报告、手工设置区域数据、手工设置电台参数、各类短消息、设置静态信息、手工设置动态消息、手工设置位置消息、查询区域参数消息、查询历史数据信息、状态查询消息、消息确认消息、串口测试、串口测试确认消息、重新启动电台消息、主机复位消息等。

3.各输入输出数据格式参见信息列表。

三、控制功能要求使键盘显示模块能可靠、连续、安全、有效地运行。

确保通信、显示、键盘各分模块有机地运行。

1.初始化功能2.看门狗功能3.安全处理功能1)通信失败处理2)UTC丢失处理3)键盘错误处理4)显示错误处理5)SRAM错误处理6)FLASH错误处理7)时钟校正处理8)键盘输入数据校正9)通信输入数据校正处理4.数据存储处理5.通信中断处理6.通信输入数据处理7.键盘中断处理8.键盘输入命令处理9.液晶显示处理10.四、显示功能要求液晶显示控制模块完成显示功能(文字和图形显示,菜单操作)。

利用键盘控制液晶显示器进行ASCII字符显示

5.设计成果形式及要求:

提交内容:课程设计说明书(VHDL程序、仿真过程及结果要在设计说明书详细说明)。

基本要求:编写的程序可以在实验箱内正常工作,满足任务书的设计要求。

6.工作计划及进度:

2009年6月15日~6月21日查阅资料,熟悉任务要求,理解设计原理

2.VHDL源程序及内部原理图。

3.该设计可以在实验箱上正常工作并演示。

课程设计任务书

4.主要参考文献:

1.侯伯计.西安:西安电子科技大学出版社,1999

2.求是科技.CPLD/FPGA应用开发技术与工程实践.北京:人民邮电出版社,2005

3.罗苑棠.CPLD/FPGA常用模块与综合系统设计实例精讲.北京:电子工业出版社,2007

中北大学

课程设计任务书

2008/2009学年第二学期

学院:

电子与计算机科学技术学院

专业:

微电子学

学生姓名:

徐鹏飞

学号:

0606024132

课程设计题目:

利用键盘控制液晶显示器进行ASCII字符显示

起迄日期:

2009年6月15日至2009年7月11日

课程设计地点:

电子科学与技术专业实验室

指导教师:

沈三民

2009年6月22日~6月28日熟悉实验箱相关模块,进行方案设计

2009年6月29日~7月5日逻辑程序设计,时序仿真与调试

2009年7月6日~7月9日实验箱功能验证

2009年7月10日~7月11日设计答辩与考核

系主任审查意见:

签字:

年月日

系主任:

任勇峰

下达任务书日期:2009年6月15日

彩色TFT液晶显示控制电路设计及其ASIC实现

彩色TFT液晶显示控制电路设计及其ASIC实现陈学峰,周荣政,洪志良(复旦大学微电子学系集成电路设计实验室,上海200433)摘要:介绍了一种用于高级型数码相机的彩色TFT液晶显示控制电路的设计。

文中首先简单给出了控制电路的设计要求,然后重点介绍电路中各模块的设计以及FPGA验证。

整个电路作为数码相机专用集成电路芯片的一部分采用TSMC 0.25mm SAGETM工艺进行了ASIC实现。

关键词:彩色TFT液晶显示器;数码相机;图像显示;ASIC中图分类号:TN873+93; TN402 文献标识码: A 文章编号:1003-353X(2003)05-0070-051引言通过彩色液晶显示器(LCD)取景是数码相机优于传统相机的重要特性之一,它解决了使用取景框取景带来的各种不便,而且可以在拍摄现场用液晶显示器回放刚拍的相片来查看拍摄效果[1],从而决定是否留下这张照片,这样能使摄影者更好地控制照片的质量。

所以用液晶显示器进行取景和回放是数码相机两大必不可少的功能。

同时液晶显示器还用来显示菜单,提供良好的人机交互界面。

目前市场上出售的数码相机使用的液晶显示器都是彩色TFT液晶显示器,这种液晶显示器解决了一般液晶显示器中相邻像素串扰的现象[2],所以可用来显示真正的活动图像。

数码相机专用集成电路芯片中的液晶显示控制电路主要实现的功能是向液晶显示模块(LCM)和数模转换器提供所有必需的控制时序信号,同时接受来自系统的YCbCr格式的图像数据,然后进行色空间变换将图像转化成RGB格式,接着按照一定的顺序以每个像素一种颜色的方式向片外DAC输出图像数据。

2系统结构与设计要求图1给出了我们设计的数码相机系统芯片中有关LCD显示部分的示意图。

根据设计数码相机专用集成电路芯片的系统要求,液晶显示控制电路可用来控制多种规格的液晶显示模块,从6万多像素到20多万像素。

此电路有两种工作模式:取景模式和回放模式,分别显示动态和静态图像。

LCD液晶TS12864-3显示器使用入门

lcd液晶ts12864-3显示器使用入门2007年08月19日星期日07:54 P.M.LCD液晶TS12864-3显示器使用入门液晶显示器以其微功耗、体积小、显示内容丰富、超薄轻巧的诸多优点,在袖珍式仪表和低功耗应用系统中得到越来越广泛的应用。

随着科技的发展,液晶显示模块的应用前景将更加广阔。

液晶显示(LCD)大体分为笔段型、字符型、点阵图形型等几大类。

本文将介绍点阵图形型带汉字库的液晶显示器。

ts12864-3液晶显示模块是采用控制芯片ST7920来控制显示的。

该显示器能够使用串口和并口两种接线方式。

并口可以选择4线和8线两种。

ST7920是台湾矽创电子公司生产的中文图形控制芯片,它是一种内置128*64-12汉字图形点阵的液晶显示控制模块,用于显示汉字及图形。

该芯片共内置8192个中文汉字(16*16点阵)、128个字符的ASCII字符库(8*16点阵)及64*256点阵显示RAM(GDRAM).为了能够简单、有效地显示汉字和图形,该模块内部设计有2MB的中文字型CGROM和64*256点阵的GDRAM绘图区域;同时,该模块还提供有4组可编程控制的16*16点阵造字空间;除此之外,为了适应多种微处理器和单片机接口的需要,该模块还提供了4位并行、8位并行、2线串行以及3线串行等多种接口方式。

DDRAM为数据显示用的RAM(Data DisplayRAM,简称DDRAM),用以存放要LCD显示的数据,只要将标准的ASCII码放入DDRAM,内部控制线路就会自动将数据传送到显示器上,并显示出该ASCII码对应的字符。

CGROM为字符产生器ROM(Character GeneratorROM,简称CGORM),它存储了192个5×7的点阵字型,但只能读出不能写入。

CGRAM为字型、字符产生器的RAM(CharacterGenerator RAM,简称CGRAM),可供使用者存储特殊造型的造型码,CGRAM最多可存8个造型。

字符型液晶LCD1602显示技术

void lcd_displaystr(unsigned char x,unsigned char y,unsigned char code *str) { //x 表示行,y 表示该行的位置(也就是列)

switch(x) {

case 0: write_lcd_command(0x80+y); break; case 1: write_lcd_command(0xc0+y); break;

if(P2_0==0) { mode++; if(mode>=4) mode=0; write_lcd_command(0x01); //清屏 }

while(P2_0==0); } switch(mode)

{ case 0x00:

lcd_displaystr(0,0x00," Study by MCS51 "); lcd_displaystr(1,0x00," Come On Baby! "); break; case 0x01: lcd_displaystr(0,0x00," Welcome To Use "); lcd_displaystr(1,0x00,""); break; case 0x02: lcd_displaystr(0,0x00," QQ:289994918 "); lcd_displaystr(1,0x00,"TEL:07732996883"); break; case 0x03: for(i=0;i<32;i++)

液晶显示器的程序设计

液晶显示器的程序设计液晶显示器的程序设计1. 简介液晶显示器是一种广泛应用于电子产品中的显示设备,它采用液晶材料来控制光的透过与阻碍,从而实现图像的显示。

在液晶显示器的程序设计中,需要考虑到控制面板设计、显示控制和用户交互等多个方面。

本文将介绍液晶显示器的程序设计的基本原理和常用技术。

2. 控制面板设计液晶显示器的控制面板是用户与显示器进行交互的重要界面,在程序设计中需要考虑到用户操作的便捷性和人机交互的友好性。

一般来说,控制面板设计需要包括以下几个方面:- 显示设置:用户可以通过菜单或按钮调整亮度、对比度、色彩和分辨率等显示参数。

- 输入设置:用户可以通过键盘、触摸屏或遥控器等输入设备进行文字输入、选择和确认等操作。

- 定时设置:用户可以通过控制面板设置自动休眠或定时开关机等功能。

在程序设计中,需要根据具体的液晶显示器型号和控制面板设计要求,使用合适的编程语言和开发工具实现控制面板的功能。

3. 显示控制液晶显示器的显示控制是液晶显示器程序设计的核心部分,主要涉及到图像的、渲染和刷新等操作。

在液晶显示器的程序设计中,常用的显示控制技术包括:- 显示驱动:显示驱动是控制液晶显示器的关键技术之一,它通过对每个像素点的电压控制,实现像素点的开关和亮度控制。

常见的显示驱动技术包括平面显示驱动和亚像素驱动等。

- 图像处理:图像处理是指对输入的图像信号进行处理和优化的技术,常用的图像处理算法包括缩放、旋转、滤波和色彩转换等。

- 反射和背光控制:液晶显示器可以通过反射和背光控制实现图像的显示和亮度调节。

反射控制是通过光的反射和折射原理实现的,背光控制则是通过背后的灯光源来照亮液晶显示屏。

在液晶显示器的程序设计中,需要根据具体的应用需求和硬件平台,选择合适的显示控制技术并实现相应的软件模块。

4. 用户交互用户交互是液晶显示器程序设计中不可忽视的一个重要方面。

用户交互可以通过按钮、触摸屏或遥控器等方式实现。

在液晶显示器的程序设计中,需要考虑以下几点:- 按钮事件处理:在液晶显示器的控制面板上,通过按钮可以实现一系列操作,如菜单导航、页面切换和参数调整等。

FPGA键盘控制液晶显示器进行汉字显示课程设计

中北大学课程设计说明书学生姓名:学号:0906024129学院:电子与计算机科学技术学院专业:微电子学题目:利用键盘控制液晶显示器进行汉字显示指导教师:崔永俊职称:副教授2012年6月22日目录1、课程设计目的 (2)2、课程设计内容和要求 (2)2.1、设计内容 (2)2.2、设计要求 (2)3、设计方案及实现情况 (2)3.1、设计思路 (2)3.2、工作原理及框图 (2)3.3、各模块功能描述 (5)3.4、仿真结果 (12)3.5、实验箱验证情况 (14)4、课程设计总结 (16)5、参考文献 (17)1、课程设计目的:1.学习操作数字电路设计实验开发系统,掌握液晶显示器的工作原理及应用。

2.掌握组合逻辑电路、时序逻辑电路的设计方法。

3.学习掌握可编程器件设计的全过程。

2、课程设计内容和要求:2.1、设计内容:利用键盘控制液晶显示器进行汉字显示。

2.2、设计要求:1.学习掌握键盘控制模块、液晶显示模块的工作原理及应用;2.熟练掌握VHDL编程语言,编写键盘控制模块的控制逻辑;3.仿真所编写的程序,模拟验证所编写的模块功能;4.下载程序到芯片中,硬件验证所设置的功能,能够实现汉字显示;5.整理设计内容,编写设计说明书。

3、设计方案及实现情况:3.1、设计思路:利用键盘进行控制液晶显示汉字,将整个工作划分模块:键盘控制模块和液晶显示模块。

键盘控制模块中,利用0—7八个数字键,编程使其按下一个键,显示一个汉字,最终显示“中北大学李青洙”,而7键用于清屏,可以反复按键显示。

液晶显示模块中,将键盘译码后的地址送到芯片上,计数过程中,分别用汉字的高低区位码送到输出端,使其显示汉字。

3.2、工作原理及框图:本设计主要包含两个模块,键盘控制模块和液晶显示模块。

而键盘模块中还包含几个主要问题:消抖问题、键盘扫描原理、键盘译码问题。

液晶显示模块包括液晶显示原理。

1.消抖问题:由于机械触点的弹性振动,按键在按下时不会马上稳定地接通而在弹起时也不能一下子完全地断开,因而在按键闭合和断开的瞬间均会出现一连串的抖动,这称为按键的抖动干扰,其产生的波形如图3.2.1所示,当按键按下时会产生前沿抖动,当按键弹起时会产生后沿抖动,一般机械触点式按键在状态输出时抖动的时间为10~100ms。

LCD字符型液晶显示器控制

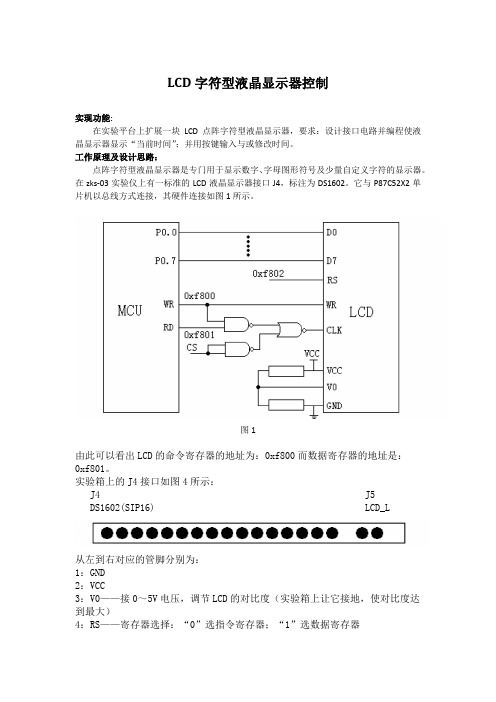

LCD字符型液晶显示器控制实现功能:在实验平台上扩展一块LCD点阵字符型液晶显示器,要求:设计接口电路并编程使液晶显示器显示“当前时间”;并用按键输入与或修改时间。

工作原理及设计思路:点阵字符型液晶显示器是专门用于显示数字、字母图形符号及少量自定义字符的显示器。

在zks-03实验仪上有一标准的LCD液晶显示器接口J4,标注为DS1602。

它与P87C52X2单片机以总线方式连接,其硬件连接如图1所示。

图1由此可以看出LCD的命令寄存器的地址为:0xf800而数据寄存器的地址是:0xf801。

实验箱上的J4接口如图4所示:J4 J5DS1602(SIP16) LCD_L从左到右对应的管脚分别为:1:GND2:VCC3:V0——接0~5V电压,调节LCD的对比度(实验箱上让它接地,使对比度达到最大)4:RS——寄存器选择:“0”选指令寄存器;“1”选数据寄存器5:R/W——“1”读操作;“0”写操作6:EN——使能信号7~14:DB0~DB7——八位双向数据信号线15~16:LCD背光电源将液晶显示器与J4接口对应连接好,编写读写程序,便对液晶显示器进行控制。

电路仿真程序#include<reg52.h>#define uint unsigned int#define uchar unsigned charuchar a,miao,shi,fen,ri,yue,nian,week,flag,temp,key1n; #define yh 0x80 //第一行的初始位置#define er 0x80+0x40 //第二行初始位置//sbit cs1=P3^7;//sbit ledk=P2^5;sbit dula=P2^6;sbit wela=P2^7;sbit wr=P1^1;sbit rs=P1^0;sbit en=P2^5;sbit SCLK=P2^1; // 6 P1.1sbit IO=P2^0; // 7 P1.0sbit RST=P2^4; //时钟5 P1.2sbit ACC0=ACC^0;sbit ACC7=ACC^7;sbit key=P3^7;sbit key1=P3^0;sbit key2=P3^1;sbit key3=P3^2;uchar code tab1[]={"2009- - THU"};uchar code tab2[]={" : : "};void delay(uint xms)//延时函数{uint x,y;for(x=xms;x>0;x--)for(y=110;y>0;y--);}/******************液晶写入************************/ write_1602com(uchar com)//液晶写入指令函数{rs=0;//置为写入命令P0=com;//送入数据delay(1);en=1;//拉高使能端delay(1);en=0;//完成高脉冲}write_1602dat(uchar dat){rs=1;//置为写入数据P0=dat;//送入数据delay(1);en=1;delay(1);en=0;}/*********************over***********************//********************ds1302****************************/ void write_byte(uchar dat){ACC=dat;RST=1;for(a=8;a>0;a--){IO=ACC0;SCLK=0;SCLK=1;ACC=ACC>>1;}}uchar read_byte(){RST=1;for(a=8;a>0;a--){ACC7=IO;SCLK=1;SCLK=0;ACC=ACC>>1;}return (ACC);}void write_1302(uchar add,uchar dat){RST=0;SCLK=0;RST=1;write_byte(add);write_byte(dat);SCLK=1;RST=0;}uchar read_1302(uchar add){uchar temp;RST=0;SCLK=0;RST=1;write_byte(add);temp=read_byte();SCLK=1;RST=0;return(temp);}uchar BCD_Decimal(uchar bcd){uchar Decimal;Decimal=bcd>>4;return(Decimal=Decimal*10+(bcd&=0x0F)); }void ds1302_init(){RST=0;SCLK=0;write_1302(0x80,miao|0x00);//允许写}void write_sfm(uchar add,uchar dat)//写时分秒{uchar gw,sw;gw=dat%10;sw=dat/10;write_1602com(er+add);write_1602dat(0x30+sw);write_1602dat(0x30+gw);}void write_nyr(uchar add,uchar dat){uchar gw,sw;gw=dat%10;sw=dat/10;write_1602com(yh+add);write_1602dat(0x30+sw);write_1602dat(0x30+gw);}void write_week(uchar week)//写星期函数{write_1602com(yh+0x0d);switch(week){case 1:write_1602dat('M');//delay(5);write_1602dat('O');//delay(5);write_1602dat('N');break;case 2:write_1602dat('T');//delay(5);write_1602dat('U');//delay(5);write_1602dat('E');break;case 3:write_1602dat('W');//delay(5);write_1602dat('E');//delay(5);write_1602dat('D');break;case 4:write_1602dat('T');//delay(5);write_1602dat('H');//delay(5);write_1602dat('U');break;case 5:write_1602dat('F');//delay(5);write_1602dat('R');//delay(5);write_1602dat('I');break;case 6:write_1602dat('S');//delay(5);write_1602dat('T');//delay(5);write_1602dat('A');break;case 7:write_1602dat('S');//delay(5);write_1602dat('U');//delay(5);write_1602dat('N');break;}}lcd_init()//液晶初始化函数{ wr=0;write_1602com(0x38);//设置液晶工作模式write_1602com(0x0c);//开显示不显示光标write_1602com(0x06);//整屏不移动,指针加一write_1602com(0x01);write_1602com(yh+2);//字符写入的位置for(a=0;a<14;a++){write_1602dat(tab1[a]);//delay(3);}write_1602com(er+4);for(a=0;a<8;a++){write_1602dat(tab2[a]);//delay(3);}}void keyscan(){key=0;if(key1==0)//key1为功能键{delay(5);if(key1==0){while(!key1);key1n++;if(key1n==9)key1n=1;switch(key1n){case 1: TR0=0;//关闭定时器//TR1=0;write_1602com(er+0x0b);//写入光标位置write_1602com(0x0f);//设置光标为闪烁temp=(miao)/10*16+(miao)%10;write_1302(0x8e,0x00);write_1302(0x80,0x80|temp);//miaowrite_1302(0x8e,0x80);break;case 2: write_1602com(er+8);//fen//write_1602com(0x0f);break;case 3: write_1602com(er+5);//shi//write_1602com(0x0f);break;case 4: write_1602com(yh+0x0f);//week//write_1602com(0x0f);break;case 5: write_1602com(yh+0x0b);//ri//write_1602com(0x0f);break;case 6: write_1602com(yh+0x08);//yue//write_1602com(0x0f);break;case 7: write_1602com(yh+0x05);//nian//write_1602com(0x0f);break;case 8:write_1602com(0x0c);//设置光标不闪烁TR0=1;//打开定时器temp=(miao)/10*16+(miao)%10;write_1302(0x8e,0x00);write_1302(0x80,0x00|temp);//miaowrite_1302(0x8e,0x80);break;}}}if(key1n!=0)//当key1按下以下。

单片机是怎样在液晶上显示字符的

单片机是怎样在液晶上显示字符的液晶(LCD)是如何显示的1.线段的显示点阵图形式液晶由M 行×N 列个显示单元组成,假设LCD 显示屏有64行,每行有128 列,每8 列对应1 个字节的8 个位,即每行由16 字节,共16×8=128 个点组成,屏上64×16 个显示单元和显示RAM 区1024 个字节相对应,每一字节的内容和屏上相应位置的亮暗对应。

例如屏的第一行的亮暗由RAM 区的000H~00FH 的16 个字节的内容决定,当(000)=FFH 时,则屏的左上角显示一条短亮线,长度为8 个点;当(3FFH)=FFH 时,则屏的右下角显示一短亮线;当(000H)=FFH,(001H)=00H,(002H)=FFH,(003H)=00H,…(00EH)=FFH,(00FH)=00H 时,则在屏的顶部显示一条由8 段亮线和8 条暗线组成的虚线。

这就是LCD 显示的基本意思。

2.字符的显示当用LCD 显示一个字符时就较复杂了,因为一个字符由6×8 或8×8 点阵组成,即要找到和屏上某几个位置对应的显示RAM区的8 个字节,并且要使每个字节的不同的位为‘1’,其它的为‘0’,为‘1’的点亮,为‘0’的点暗,这样一来就组成某个字符。

但对于内带字符发生器的控制器(如T6963C)来说,显示字符就比较简单了,可让控制器工作在文本方式,根据在LCD 上开始显示的行列号及每行的列数找出显示RAM 对应的地址,设立光标,在此送上该字符对应的代码即可。

3.汉字的显示汉字的显示一般采用图形方式,事先从微机中提取要显示的汉字的点阵码,每个汉字占32 字节,分左右两半部,各占16 字节,左边为1、3、5…,右边为2、4、6…, 根据在LCD 上开始显示的行列号及每行的列数可找出显示RAM 对应的地址,设立光标,送上要显示的汉字的第一个字节,光标位置加1,送第二字节,换行按列对齐,送第三字节…直到32 字节显示完就可在LCD 上得到一个完整的汉字。

利用键盘控制点阵进行ASIC字符显示

目录1、课程设计的目的 (2)2、课程设计内容和要求 (2)2.1 设计内容 (2)2.2 设计要求 (2)3、设计方案及实现情况 (2)3.1 设计思路 (2)3.2 工作原理及框图 (2)3.3 各功能模块描述 (6)3.4 仿真结果 (13)3. 5 实验箱验证情况 (14)4、课程设计总结 (17)4.1 自上而下的设计思想 (17)4.2 课程设计实验心得 (17)5、参考文献 (18)1、课程设计目的(1)学习操作数字电路设计实验开发系统,掌握点阵显示模块的工作原理及应用。

(2)掌握组合逻辑电路、时序逻辑电路的设计方法。

(3)学习掌握可编程器件设计的全过程。

2、课程设计内容和要求:2.1、设计内容(1)键盘扫描模块实现对键盘的扫描控制。

(2)编写控制点阵的程序,实现对点阵时序的控制,使点阵能够正常工作。

(3)添加其他功能模块,协调两个主模块更好地进行工作。

2.2、设计要求(1)学习掌握键盘控制模块、点阵显示模块的工作原理及应用;(2)熟练掌握VHDL编程语言,编写键盘控制模块的控制逻辑;(3)仿真所编写的程序,模拟验证所编写的模块功能;(4)下载程序到芯片中,硬件验证所设置的功能,能够实现字符显示;(5)整理设计内容,编写设计说明书。

3、设计方案及实现情况3.1、设计思路通过对键盘的控制来显示字符的输出,采用模块化的设计思想,对于不同的功能用不同的程序模块来实现。

基于这种设计思想,对本次课程设计题目分为以下几个模块:时序产生电路模块、键盘与点阵扫描电路模块、键盘译码模块、显示模块(此模块对应产生列字符扫描信号). 工作概况如下:当按下键盘后,键盘扫描到对应的输出信号,然后进行第一次译码,接着把译码结果传递给xiansi 模块,xianshi模块根据译码结果产生对应的列字符扫描信号,从而进行输出。

3.2、工作原理及框图1、键盘译码电路键盘中的按键可分为数字键和功能键。

数字键主要用来输入数字,但从上述内容发现,键盘所产生的输出KIN3~KIN0无法拿来直接使用;另外不同的数字按键也担负不同的功能,因此必须由键盘译码电路来规划某个按键的输出形式,以便执行相应的动作。

字符液晶显示器

字符型液晶显示器

字符型LCD1602的应用 四、字符型 的应用

12/51

5、控制方式

通过CPU来控制 来控制LCD模块,方式十分简单,LCD模块其 模块, 通过 来控制 模块 方式十分简单, 模块其 内部可以看成有两组寄存器,一个为指令寄存器, 内部可以看成有两组寄存器,一个为指令寄存器,一个为数 据寄存器, 引脚来控制。 据寄存器,由DI引脚来控制。 引脚来控制 所有对指令寄存器或数据寄存器的存取均需检查LCD内 内 所有对指令寄存器或数据寄存器的存取均需检查 部的忙碌标志( ),此标志用来告知 部的忙碌标志(Busy Flag),此标志用来告知 ),此标志用来告知LCD内部正 内部正 在工作,不允许接收任何的控制命令。 在工作,不允许接收任何的控制命令。而此位的检查可以令 DI=0时,读取 来加以判断,当此位为 时,才可以写入指 来加以判断, 时 读取D7来加以判断 当此位为0时 令寄存器或数据寄存器。 令寄存器或数据寄存器。

1/51

字符型液晶显示器

字符型液晶显示器

字符型点阵式LCD简介 一、字符型点阵式 简介

字符型点阵LCD是专门用于显示数字0~9 、大小写英 文字符、图形符号及少量自定义符号的液晶显示器。其内 部带有显示字符的字库,大多数还能由人工根据需要编码 一些字符。 这里介绍的字符型液晶模块 是一种用5x7点阵图形来显示字符 点阵图形来显示字符 是一种用 的液晶显示器。 的液晶显示器。 将以16*2字符型液晶显示模块RT1602C为例,详细介绍字符型晶显示模 块的应用技术。

LCD 插座的引脚 编号与显示器的 接线端子相对应; 接线端子相对应; LCD 的 I/O 选通 信号 CE 由译码器 的输出 Y6、读写 、 信号 RD 、 WR 经 过 一 片 74HC00 完成。 完成。

利用键盘控制液晶显示器.

中北大学课程设计说明书学生姓名:毛雪娇学号:0706024101学院: 电子与计算机科学技术学院专业: 微电子学题目: 利用键盘控制液晶显示器进行汉字显示指导教师:王红亮职称: 讲师2010 年 6 月 25 日目录1. 课程设计目的 (2)2. 课程设计内容和要求 (2)2.1、设计内容 (2)2.2、设计要求 (2)3、设计方案及实现情况 (2)3.1、设计思路 (2)3.2、工作原理及框图 (3)3.3、各模块功能描述 (6)3.4、仿真结果 (14)3.5、实验箱验证情况 (14)4、课程设计总结 (15)5、参考文献 (16)1、课程设计目的(1)学习操作数字电路设计实验开发系统,掌握液晶显示器的工作原理及应用。

(2)掌握组合逻辑电路、时序逻辑电路的设计方法。

(3)学习掌握可编程器件设计的全过程。

2、课程设计内容和要求2.1、设计内容利用VHDL语言进行编程,使键盘控制液晶显示器进行汉字的显示。

2.2、设计要求1.学习掌握键盘控制模块、液晶显示模块的工作原理及应用;2. 熟练掌握VHDL编程语言,编写键盘控制模块的控制逻辑;3. 仿真所编写的程序,模拟验证所编写的模块功能;4. 下载程序到芯片中,硬件验证所设置的功能,能够实现汉字显示;5. 整理设计内容,编写设计说明书。

3、设计方案及实现情况3.1、设计思路利用process进程语句进行不同功能的实现,主要有分频,消抖,键盘扫描,键盘译码,数据存储模块,控制液晶显示器,主要是键盘模块和液晶模块,键盘主要是扫描信号,当其扫描到一个信号时,向液晶显示器发出一个该信号对应的地址信号,液晶显示器接收到该地址信号后,输出相应的数据,该数据为用户要其显示的汉字的区位码。

当按键分别为“1”、“2”、“3”、“4”、“5”、“6”时,液晶显示器显示的汉字分别为“中”、“北”、“大”、“学”、“春”、“天”。

3.2、工作原理及框图1.矩阵式键盘矩阵式键盘又叫行列式键盘,是用I/O口线组成的行、列矩阵结构,在每根行线与列线的交叉处,二线不直接相通而是通过一个按键跨接接通。

利用拨码开关控制液晶显示器进行ASIC字符显示

目录1.课程设计目的 (2)2.课程设计内容和要求 (2)2.1 设计内容 (2)2.2 设计要求 (2)3.设计方案及实现情况 (2)3.1 设计思路 (2)3.2 工作原理及框图 (3)3.3 各模块功能描述 (3)3.4 仿真结果 (10)3.5 实验箱验证情况 (10)4.课程设计总结 (12)5.参考文献 (13)6.附录:液晶显示器简介 (13)1、课程设计目的(1)学习操作数字电路设计实验开发系统,掌握液晶显示器的工作原理及应用。

(2)掌握组合逻辑电路、时序逻辑电路的设计方法。

(3)学习掌握可编程器件设计的全过程。

2、课程设计内容和要求:2.1、设计内容用VHDL语言编写程序,利用拔码开头控制液晶显示器进行ASIC字符显示。

2.2、设计要求(1)学习掌握拔码开头控制模块、液晶显示模块的工作原理及应用;(2)熟练掌握VHDL编程语言,编写键盘控制模块的控制逻辑;(3)仿真所编写的程序,模拟验证所编写的模块功能;(4)下载程序到芯片中,硬件验证所设置的功能,能够实现ASIC字符的显示;(5)整理设计内容,编写设计说明书.3、设计方案及实现情况3.1、设计思路运用VHDL语言进行各个模块的程序编写,该设计共有四个模块分别为:拨码模块;消抖模块;译码模块;显示模块.整个、模块共有四个单元电路组成为:图1图1 原理图3.2、工作原理及框图译码消抖液晶显示拨码控制图2 系统电路原理图3.3、各模块功能描述(1)拨码模块程序代码为:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity bm1 isport(rst:in std_logic;xd: in std_logic;clk: in std_logic;xdout: out std_logic );end bm1;architecture a of bm1 issignal count:integer range 0 to 100;beginprocess(clk,rst,xd)beginif(rst='0')thencount<=0;xdout<='0';elsif(clk'event and clk='1')thenif(count=5)thencount<=0;xdout<=not xd;elsecount<=count+1;end if;end if;end process;end a;(2)消抖模块程序代码为:Library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity xd isport(aj:in std_logic;rst:in std_logic;ajout:out std_logic_vector(4 downto 0) );end xd;architecture ajwork of xd issignal q: std_logic;signal count : std_logic_vector(4 downto 0); beginq<=aj when rst='1'else '0';process(q,rst)beginif(rst='0')thencount<="00000";elsif q'event and q='1' thenif count="11111" thencount<="00000";elsecount<=count+1;end if;end if;ajout<=count;end process;end ajwork;(3)译码模块程序代码为:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity ym1 isport(ym:in std_logic_vector(4 downto 0); Y:out std_logic_vector(7 downto 0)); end ym1;architecture yima_arch of ym1 issignal a:std_logic_vector(4 downto 0); begina<=ym;Y<="01000001" when ( a="00000" ) else"01000010" when ( a="00001" ) else"01000011" when ( a="00010" ) else"01000100" when ( a="00011" ) else"01000101" when ( a="00100" ) else"00100001" when ( a="00101" ) else "00100011" when ( a="00110" ) else "00100100" when ( a="00111" ) else "00100101" when ( a="01000" ) else "00100110" when ( a="01001" ) else "00100111" when ( a="01010" ) else "00101000" when ( a="01011" ) else "00101001" when ( a="01100" ) else "00101010" when ( a="01101" ) else "00101011" when ( a="01110" ) else "00101100" when ( a="01111" ) else "00101101" when ( a="10000" ) else "00101110" when ( a="10001" ) else "00101111" when ( a="10010" ) else "00110000" when ( a="10011" ) else "00110001" when ( a="10100" ) else "00110010" when ( a="10101" ) else "00110011" when ( a="10110" ) else "00110100" when ( a="10111" ) else "00110101" when ( a="11000" ) else "00110110" when ( a="11001" ) else "00110111" when ( a="11010" ) else "00111000" when ( a="11011" ) else "00111001" when ( a="11100" ) else "00111010" when ( a="11101" ) else "00111011" when ( a="11110" ) else "00111100" when ( a="11111" ) else "00110000";end yima_arch;(4)显示模块程序代码为:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY lcd ISPORT( busy :IN STD_LOGIC;clk_fsm :IN STD_LOGIC;db_ascii :IN STD_LOGIC_VECTOR(7 DOWNTO 0);req :OUT STD_LOGIC;db :OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END lcd;ARCHITECTURE rtl OF lcd ISSIGNAL ready : STD_LOGIC;TYPE state IS (CMD_SEND,XX_SEND,YY_SEND,ASCII_SEND); SIGNAL current_state : state;--SIGNAL db_send: std_logic_vector(7 downto 0);BEGINPROCESS(clk_fsm,busy,ready,db_ascii)variable cnt1: std_logic_vector(2 downto 0);BEGIN--db_send<=db_ascii;IF rising_edge(clk_fsm) THENCASE current_state ISWHEN CMD_SEND =>IF busy='0' THENIF ready='1' THENcurrent_state <= XX_SEND;ready <= '0';ELSEdb <= "11111001";--F1req <= '1';ready <= '0';END IF;ELSEreq <= '0';ready <= '1';current_state <= CMD_SEND;END IF;WHEN XX_SEND =>IF busy='0' THENIF ready='1' THENcurrent_state <= YY_SEND;ready <= '0';ELSEdb <= "00001001";--07req <= '1';ready <= '0';END IF;ELSEreq <= '0';ready <= '1';current_state <= XX_SEND;END IF;WHEN YY_SEND =>IF busy='0' THENIF ready='1' THENcurrent_state <= ASCII_SEND;ready <= '0';ELSEdb <= "00000010";--02req <= '1';ready <= '0';END IF;ELSEreq <= '0';ready <='1';current_state <= YY_SEND;END IF;WHEN ASCII_SEND =>IF busy='0' THENIF ready='1' THENcurrent_state <= CMD_SEND;ready <= '0';ELSEdb <=db_ascii;req <= '1';ready <= '0';END IF;ELSEreq <= '0';ready <= '1';current_state <= ASCII_SEND;END IF;END CASE;END IF;END PROCESS;END rtl;3.4、仿真结果(1)液晶显示器仿真结果: 当BUSY信号有效时(BUSY=‘1’),停止输出地址信号;当液晶模块处于空闲状态(BUSY=‘0’)时,输出地址信号。

计算机科学技术:微型计算机考试答案二

计算机科学技术:微型计算机考试答案二1、单选(江南博哥)从计算机的工作原理上来说,计算机的本质功能就是()。

A、数据运算B、图形图像处理C、音频处理D、视频处理答案:A2、多选 8086CPU响应硬中断NMI和INTR时,相同的条件是()。

A.允许中断B.当前指令执行结束C.CPU工作在最大模式下D.不处于DMA操作期间答案:B,D3、单选即能保存单帧(静态)图像,又能保存多帧(动态)图像的文件格式是()。

A、jpgB、gifC、psdD、bmp答案:B4、问答?如图所示,将8255的C端口接8个发光二极管,使这8个发光二极管依次亮灭,其中74LS138译码器与地址总线已经连接正确。

答案:(1)C口端口地址为多少?控制口端口地址为多少?(2)按位置位/复位字0FH含义是什么?(3)试编写实现8个发光二极管循环亮灭的程序。

(已知有一个延时1秒的子程序,其入口地址为DELAY1S)。

(1)C口端口地址为3EAH,控制口端口地址为3EBH。

(2)按位置位/复位字0FH含义是将PC7置1。

(3)5、问答题论述8086CPU的最小方式和最大方式的区别。

答案:8086CPU的最小方式和最大方式的区别是:最小方式,MN/MX接+5V(MX 为低电平),用于构成小型单处理机系统,支持系统工作的器件:(1)时钟发生器,8284A,(2)总线锁存器,74LS373,(3)总线收发器,74LS245,控制信号由CPU提供。

最大方式,MN/MX接地(MX为低电平),用于构成多处理机和协处理机系统,支持系统工作的器件:(1)时钟发生器,8284A,(2)总线锁存器,74LS373,(3)总线收发器,74LS245,(4)总线控制芯片,8288,控制信号由8288提供。

6、单选串行传送的波特率是指单元时间内传送()数据的位数。

A.二进制B.八进制C.十进制D.十六进制答案:A7、填空题半导体存储器从读写性能上分()和()。

单片机课程设计——字符液晶显示器

目录1课程设计的目的与要求 (1)1.1课程设计目的: (1)1.2课程设计要求: (1)1.3知识点链接 (1)2 系统硬件设计及说明 (3)2.1硬件设计思想 (3)2.2主要元器件介绍 (3)2.3硬件功能电路电路图 (4)2.4 核心芯片 AT89C51的介绍 (5)2.5 MSP430单片机的介绍 (6)3系统软件设计 (6)3.1程序及程序描述 (6)3.2程序流程图 (10)3.3功能演示 (11)4总结 (12)5 参考文献 (12)1课程设计的目的与要求1.1课程设计目的:1巩固和加深对单片机原理和接口技术知识的理解;2培养根据课题需要选学参考书籍、查阅手册和文献资料的能力;3学会方案论证的比较方法,拓宽知识,初步掌握工程设计的基本方法;4掌握常用仪器、仪表的正确使用方法,学会软、硬件的设计和调试方法;5能按课程设计的要求编写课程设计报告,能正确反映设计和实验成果,能用计算机绘制电路图和流程图。

1.2课程设计要求:单片机控制LCD1602液晶显示器滚动显示字符1.3功能简介:1、内容:利用LCD1602液晶显示器滚动显示字符' ZHU NI YI SHENG PING AN'2、目标:(1)掌握单片机控制LCD1602液晶显示器显示字符技术,包括程序设计和电路设计,本任务的效果是让LCD1602液晶显示器滚动显示字符' ZHU NI YI SHENG PING AN'。

(2)用PROTEUS进行电路设计和实时仿真3、知识点链接(1)数字符LCD 模块是一种专用显示字符、数字或符号的液晶显示模块。

这种模块每一个符号由5×7、5×8 或5×11 的点阵像素排列组成的,字符间隔为一个点距,行间隔为一个行距,模块本身附有显示驱动控制电路,可以与单片机的I/O 口线直接连接,使用方便。

目前广泛使用的字符LCD 模块其显示驱动控制电路多是HD44780 或兼容品,其接口信号、操作指令相同。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

中北大学课程设计说明书学生姓名:甘世伟学号:04学院: 电子与计算机科学技术学院专业: 微电子学题目: 利用拨码开关控制液晶显示器进行ASIC字符显示指导教师:王红亮职称: 讲师2010 年 6 月 25 日目录表—1:OCMJ2X8(128X32)引脚说明....................- 12 -硬件接口 ..................................................................................................................................................................... - 13 -四、电性能参数 ......................................................................................................................................................... - 13 -1)表—1模块时间参数表.........................- 13 -2)表—2模块主要电气参数表.......................- 14 -用户命令 ..................................................................................................................................................................... - 14 -外型尺寸图(图11) .............................................................................................................................................. - 15 -6.附录:液晶显示器简介 (13)1、课程设计目的(1)学习操作数字电路设计实验开发系统,掌握液晶显示器的工作原理及应用。

(2)掌握组合逻辑电路、时序逻辑电路的设计方法。

(3)学习掌握可编程器件设计的全过程。

2、课程设计内容和要求:、设计内容用VHDL语言编写程序,利用拔码开头控制液晶显示器进行ASIC字符显示。

、设计要求(1)学习掌握拔码开头控制模块、液晶显示模块的工作原理及应用;(2)熟练掌握VHDL编程语言,编写键盘控制模块的控制逻辑;(3)仿真所编写的程序,模拟验证所编写的模块功能;(4)下载程序到芯片中,硬件验证所设置的功能,能够实现ASIC字符的显示;(5)整理设计内容,编写设计说明书.3、设计方案及实现情况、设计思路运用VHDL语言进行各个模块的程序编写,该设计共有四个模块分别为:拨码模块;消抖模块;译码模块;显示模块.整个、模块共有四个单元电路组成为:图1图1 原理图、工作原理及框图图2 系统电路原理图、各模块功能描述(1)拨码模块程序代码为:library ieee;use bm1 isport(rst:in std_logic;译码消抖液晶显示拨码控制xd: in std_logic;clk: in std_logic;xdout: out std_logic );end bm1;architecture a of bm1 issignal count:integer range 0 to 100; beginprocess(clk,rst,xd)beginif(rst='0')thencount<=0;xdout<='0';elsif(clk'event and clk='1')thenif(count=5)thencount<=0;xdout<=not xd;elsecount<=count+1;end if;end if;end process;end a;(2)消抖模块程序代码为:Library ieee;use xd isport(aj:in std_logic;rst:in std_logic;ajout:out std_logic_vector(4 downto 0)end xd;architecture ajwork of xd issignal q: std_logic;signal count : std_logic_vector(4 downto 0); beginq<=aj when rst='1'else '0';process(q,rst)beginif(rst='0')thencount<="00000";elsif q'event and q='1' thenif count="11111" thencount<="00000";elsecount<=count+1;end if;end if;ajout<=count;end process;end ajwork;(3)译码模块程序代码为:library ieee;use ym1 isport(ym:in std_logic_vector(4 downto 0);Y:out std_logic_vector(7 downto 0));end ym1;architecture yima_arch of ym1 issignal a:std_logic_vector(4 downto 0);beginY<="01000001" when ( a="00000" ) else "01000010" when ( a="00001" ) else "01000011" when ( a="00010" ) else "01000100" when ( a="00011" ) else "01000101" when ( a="00100" ) else "00100001" when ( a="00101" ) else "00100011" when ( a="00110" ) else "00100100" when ( a="00111" ) else "00100101" when ( a="01000" ) else "00100110" when ( a="01001" ) else "00100111" when ( a="01010" ) else "00101000" when ( a="01011" ) else "00101001" when ( a="01100" ) else "00101010" when ( a="01101" ) else "00101011" when ( a="01110" ) else "00101100" when ( a="01111" ) else "00101101" when ( a="10000" ) else "00101110" when ( a="10001" ) else "00101111" when ( a="10010" ) else "00110000" when ( a="10011" ) else "00110001" when ( a="10100" ) else "00110010" when ( a="10101" ) else "00110011" when ( a="10110" ) else "00110100" when ( a="10111" ) else "00110101" when ( a="11000" ) else "00110110" when ( a="11001" ) else "00110111" when ( a="11010" ) else "00111000" when ( a="11011" ) else "00111001" when ( a="11100" ) else"00111010" when ( a="11101" ) else"00111011" when ( a="11110" ) else"00111100" when ( a="11111" ) else"00110000";end yima_arch;(4)显示模块程序代码为:LIBRARY IEEE;USE lcd ISPORT( busy :IN STD_LOGIC;clk_fsm :IN STD_LOGIC;db_ascii :IN STD_LOGIC_VECTOR(7 DOWNTO 0);req :OUT STD_LOGIC;db :OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END lcd;ARCHITECTURE rtl OF lcd ISSIGNAL ready : STD_LOGIC;TYPE state IS (CMD_SEND,XX_SEND,YY_SEND,ASCII_SEND); SIGNAL current_state : state;--SIGNAL db_send: std_logic_vector(7 downto 0);BEGINPROCESS(clk_fsm,busy,ready,db_ascii)variable cnt1: std_logic_vector(2 downto 0);BEGIN--db_send<=db_ascii;IF rising_edge(clk_fsm) THENCASE current_state ISWHEN CMD_SEND =>IF busy='0' THENIF ready='1' THENcurrent_state <= XX_SEND;ready <= '0';ELSEdb <= "";--F1req <= '1';ready <= '0';END IF;ELSEreq <= '0';ready <= '1';current_state <= CMD_SEND;END IF;WHEN XX_SEND =>IF busy='0' THENIF ready='1' THENcurrent_state <= YY_SEND;ready <= '0';ELSEdb <= "00001001";--07req <= '1';ready <= '0';END IF;ELSEreq <= '0';ready <= '1';current_state <= XX_SEND;END IF;WHEN YY_SEND =>IF busy='0' THENIF ready='1' THENcurrent_state <= ASCII_SEND;ready <= '0';ELSEdb <= "00000010";--02req <= '1';ready <= '0';END IF;ELSEreq <= '0';ready <='1';current_state <= YY_SEND;END IF;WHEN ASCII_SEND =>IF busy='0' THENIF ready='1' THENcurrent_state <= CMD_SEND;ready <= '0';ELSEdb <=db_ascii;req <= '1';ready <= '0';END IF;ELSEreq <= '0';ready <= '1';current_state <= ASCII_SEND;END IF;END CASE;END IF;END PROCESS;END rtl;、仿真结果(1)液晶显示器仿真结果: 当BUSY信号有效时(BUSY=‘1’),停止输出地址信号;当液晶模块处于空闲状态(BUSY=‘0’)时,输出地址信号。