十年相伴 共创经典 Discuz!系列经典产品回顾6页word文档

十年相伴 共创经典 Discuz!系列经典产品回顾

《站长》杂志第28期内容推介十年相伴共创经典Discuz!系列经典产品回顾站长朋友们,是否还记得Discuz! 官网那些5年前的老ID旧面孔?是否还记得曾经的Discuz! 1.0 、Discuz! 1.0 和Discuz! 5.5“长”得什么模样?在过去的十年里,senz在站长的陪伴下一路走来,推出了数款经典产品,成为社区动力,引领社区潮流发展。

在即将迎来senz十周年之际,《站长》杂志特别回首过去十年来的数款经典Discuz! 产品,以及那些始终陪伴左右的站长朋友,谨以对更多陪伴Discuz! 、支持Discuz! 的站长们表示由衷的感激。

Discuz! 1.0 ——Discuz! 起点站大C在开发Discuz! 1.0 的时候,一定不会想到之后商业化的Discuz! 1.0 、免费开源的Discuz! 4.0 、以及现在“跨界融合”的Discuz! X 系列;Discuz! 1.0 的各项功能、模板也可能是Discuz! 系列中最简陋的,最朴素的,但没有它,也就没有后来的数个经典产品。

所以,Discuz! 1.0 就像是Discuz! 系类产品的“起点站”和“加油站”一样,不断的激励着Discuz! 的后续产品一步步的改进、创新,引领社区发展潮流。

许多的草根站长,不也是这样一步步发展起来的吗?许多业已取得成功的站长,在初建社区的时候,也未曾想过能取得今天的人气与盈利,只是抱着许三多“不抛弃、不放弃”的信念从小做大,根据市场需求逐步改进自己的产品,一步步走向了成功。

这种“从小到大”、“坚持不放弃”、“以市场为导向”的理念不仅是说Discuz! 1.0 ,也同样适用于社区。

Discuz! 2.0 ——商业化从技术角度说,Discuz! 2.0 并不是一款完全成熟的产品,主要原因在于一些BUG的存在,而且这些BUG并未得到官方的及时修复;但在社区产品贫乏的年代,这些BUG毫不影响Discuz! 2.0 作为一款实用、市场急需的社区产品而深受用户认可;从Discuz! 2.0 开始,Discuz! 进行商业化转型,大C(戴志康)决定收费,以几千元一套的价格出售Discuz! 1.0 。

2011CBC New Colloction产品文案

缤纷色彩“水墨”登场闻香识人春夏香薰引领淡雅风潮早春伊始,国际时装T台上水彩元素轻盈飘逸,吐露春天的气息。

缤纷春夏,Chesapeake Bay Candle®(千诗碧可)香薰系列在寻找芳香的旅途中,惊喜地发现天然清新的植物精华与水族生物的盎然生机为我们带来一幅简约而富有创造力的水墨画卷,清新柠檬、热烈番石榴、提神桉叶、优雅茉莉、魅惑柚木、清透晨海,缤纷水墨系列每一款自然元素为我们调配香氛找到了最佳嗅觉灵感,现在,我们带您一起享受大自然的滋养,释放身心,与芬芳一路随行。

Chesapeake Bay Candle®(千诗碧可)缤纷水墨系列甄选纯正自然的六种高质香氛,陪伴于您每一次的感官之旅。

竹香桉叶带来令人放松的SPA体验,清新提神;清透的海风与新鲜的樱草温润完美呈现晨海薄雾带来的自然惬意;苍翠的马鞭草与清爽柠檬香草共同打造舒心的愉悦香氛;优雅的纯白茉莉与柠檬薄荷相得益彰,让人提升了对自然的感受力、对季节的敏锐度;来自热带高纤维水果番石榴与岛兰繁茂景象的浑然交融,缔造了番石榴香型热烈的生活激情;琥珀和柚木温暖魅惑精华,呈现简约优雅气质。

Chesapeake Bay Candle®(千诗碧可)缤纷水墨系列家居挥发精油提炼美国优质天然植物精油,可产生负离子,舒缓精神。

藤条蔓延出来的浓郁高香跟您一起徜徉心灵的旅途,选一个温暖的午后,静静默读一本喜爱的小说,夕阳西下,心灵的滋养似乎余兴未了。

色彩的水墨艺术,高香的氛围熏陶,如果你也愿意相信这世界因你的改变而更美,那么,请启动你所有的感官,你的世界因此而变得更加绚烂阳光。

可用于办公桌的点缀;卧室客厅的家装家居;沐浴时的身心平衡;抑或是高级会所、五星级酒店等高档场所的薰香点缀,在时空中享受水墨香薰独特的优雅气息。

瓶装采用高级橡皮漆质地,丝般柔滑的舒适手感,显露非凡气质,尊显水墨香薰的高雅格调。

C hesapeake Bay Candle®(千诗碧可)缤纷水墨系列熏香陶瓷球取自天然火山石,同时融入美国优质植物精油,可产生负离子及氧气,舒缓精神。

艾默生动环监控新产品及系统介绍

报警模块

根据预设规则,实时 监测环境参数,发现 异常及时报警。

数据流程与处理逻辑

数据采集

01 通过传感器网络实时采集环境

参数数据。

数据传输

02 将采集的数据通过安全通道传

输到数据中心。

数据处理

03 对原始数据进行清洗、转换、

压缩等处理,以便于后续分析 。

数据存储

04 将处理后的数据存储在高性能

数据库中,保证数据的可用性 和持久性。

使用操作指南

熟悉操作界面

在操作前,先熟悉设备的操作界面和各项功 能键的作用。

定期维护

定期对设备进行维护保养,保持设备处于良 好状态,延长使用寿命。

正确操作

按照操作手册的指示,正确操作设备,避免 误操作导致设备损坏或数据丢失。

故障处理

遇到故障时,及时联系售后服务人员进行处 理,不要自行拆卸或修理设备。

阅读安装手册

仔细阅读产品安装手册, 了解设备的安装步骤、接 线方式及调试方法。

调试过程注意事项

安全第一

在调试过程中,务必注意安全, 遵守相关安全操作规程,防止触

电、短路等事故发生。

逐步调试

按照调试手册的步骤,逐步进行调 试,确保每一步都正确无误。

记录调试数据

在调试过程中,详细记录各项参数 和数据,以便后续分析和优化。

模块化设计

各功能模块相互独立,便于维护和升 级。

各模块功能介绍

数据采集模块

负责实时采集各种传 感器数据,如温度、 湿度、压力等。

数据处理模块

对采集的数据进行清 洗、压缩、加密等处 理,保证数据的安全 性和准确性。

数据存储模块

采用高性能数据库, 实现海量数据的存储 和快速查询。

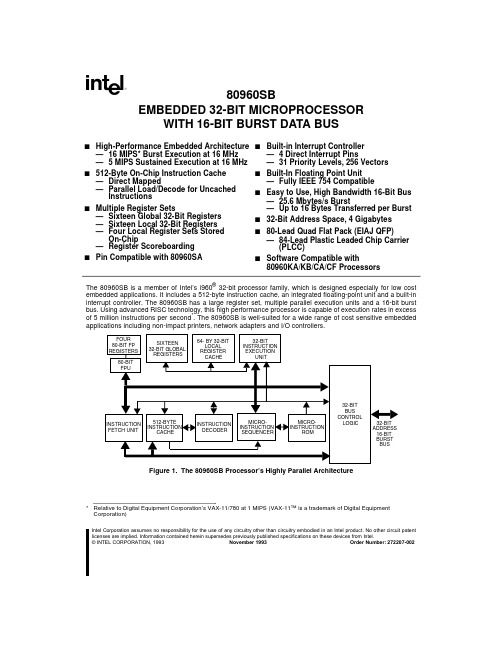

80960SB资料

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied. Information contained herein supersedes previously published specifications on these devices from Intel.© INTEL CORPORATION, 1993November 1993Order Number: 272207-00280960SBEMBEDDED 32-BIT MICROPROCESSORWITH 16-BIT BURST DATA BUSThe 80960SB is a member of Intel’s i960® 32-bit processor family, which is designed especially for low cost embedded applications. It includes a 512-byte instruction cache, an integrated floating-point unit and a built-in interrupt controller. The 80960SB has a large register set, multiple parallel execution units and a 16-bit burst bus. Using advanced RISC technology, this high performance processor is capable of execution rates in excess of 5 million instructions per second *. The 80960SB is well-suited for a wide range of cost sensitive embedded applications including non-impact printers, network adapters and I/O controllers.Figure 1. The 80960SB Processor’s Highly Parallel Architecture*Relative to Digital Equipment Corporation’s VAX-11/780 at 1 MIPS (VAX-11™ is a trademark of Digital Equipment Corporation)s High-Performance Embedded Architecture —16 MIPS* Burst Execution at 16 MHz — 5 MIPS Sustained Execution at 16 MHzs 512-Byte On-Chip Instruction Cache—Direct Mapped —Parallel Load/Decode for Uncached Instructionss Multiple Register Sets—Sixteen Global 32-Bit Registers —Sixteen Local 32-Bit Registers —Four Local Register Sets Stored On-Chip —Register Scoreboardings Pin Compatible with 80960SA s Built-in Interrupt Controller — 4 Direct Interrupt Pins —31 Priority Levels, 256 Vectors s Built-In Floating Point Unit —Fully IEEE 754 Compatible s Easy to Use, High Bandwidth 16-Bit Bus —25.6 Mbytes/s Burst —Up to 16 Bytes Transferred per Burst s 32-Bit Address Space, 4 Gigabytes s 80-Lead Quad Flat Pack (EIAJ QFP)—84-Lead Plastic Leaded Chip Carrier (PLCC)s Software Compatible with80960KA/KB/CA/CF ProcessorsINSTRUCTION FETCH UNIT 512-BYTE INSTRUCTION CACHE INSTRUCTION DECODER MICRO-INSTRUCTION SEQUENCER MICRO-INSTRUCTION ROM 32-BIT BUS CONTROL LOGIC 32-BIT INSTRUCTION EXECUTION UNIT64- BY 32-BIT LOCAL REGISTER CACHE SIXTEEN 32-BIT GLOBAL REGISTERS 32-BIT ADDRESS16-BIT BURST BUSFOUR80-BIT FPREGISTERS80-BITFPUiiCONTENTS PAGE1.0 THE i960® PROCESSOR (1)1.1 Key Performance Features (2)1.1.1 Memory Space And Addressing Modes (4)1.1.2 Data Types (4)1.1.3 Large Register Set (4)1.1.4 Multiple Register Sets (5)1.1.5 Instruction Cache (5)1.1.6 Register Scoreboarding (5)1.1.7 Floating-Point Arithmetic (6)1.1.8 High Bandwidth Bus (6)1.1.9 Interrupt Handling (7)1.1.10 Debug Features (7)1.1.11 Fault Detection (7)1.1.12 Built-in T estability (7)1.1.13 CHMOS (7)2.0 ELECTRICAL SPECIFICATIONS (11)2.1 Power and Grounding (11)2.2 Power Decoupling Recommendations (11)2.3 Connection Recommendations (11)2.4 Characteristic Curves (11)2.5 T est Load Circuit (13)2.6 ABSOLUTE MAXIMUM RATINGS* (14)2.7 DC Characteristics (14)2.8 AC Specifications (15)3.0 MECHANICAL DATA (20)3.1 Packaging (20)3.2 Pin Assignment (20)3.3 Pinout (22)3.4 Package Thermal Specifications (26)4.0 WAVEFORMS (27)5.0 REVISION HISTORY ................................................................................................................................3380960SBEMBEDDED 32-BIT MICROPROCESSORWITH 16-BIT BURST DATA BUSiiiLIST OF FIGURESPAGE Figure 1The 80960SB Processor’s Highly Parallel Architecture ................................................................0Figure 280960SB Programming Environment ...........................................................................................1Figure 3Instruction Formats ......................................................................................................................4Figure 4Multiple Register Sets Are Stored On-Chip ..................................................................................6Figure 5Connection Recommendation for LOCK ....................................................................................11Figure 6Typical Supply Current vs. Case T emperature ...........................................................................12Figure 7Typical Current vs. Frequency (Room T emp) .............................................................................12Figure 8Typical Current vs. Frequency (Hot T emp) .................................................................................13Figure 9Capacitive Derating Curve .........................................................................................................13Figure 10Test Load Circuit for Three-State Output Pins ............................................................................13Figure 11Drive Levels and Timing Relationships for 80960SB Signals .....................................................15Figure 12Processor Clock Pulse (CLK2) ...................................................................................................18Figure 13RESET Signal Timing .................................................................................................................18Figure 14HOLD Timing ..............................................................................................................................19Figure 1580-Lead EIAJ Quad Flat Pack (QFP) Package ..........................................................................20Figure 1684-Lead Plastic Leaded Chip Carrier (PLCC) Package .............................................................21Figure 17Non-Burst Read and Write T ransactions Without Wait States ....................................................27Figure 18Quad Word Burst Read T ransaction With 1, 0, 0, 0, 0, 0, 0, 0 Wait States ................................28Figure 19Burst Write T ransaction With 2, 1, 1, 1 Wait States (6-8 Bytes T ransferred) ..............................29Figure 20Accesses Generated by Quad Word Read Bus Request, Misaligned One Byte from Quad Word Boundary 1, 0, 0, 0, 0, 0, 0, 0 Wait States 30Figure 21Interrupt Acknowledge Cycle ......................................................................................................31Figure 22Cold Reset Waveform ................................................................................................................32LIST OF TABLESTable 180960SB Instruction Set ..............................................................................................................3Table 2Memory Addressing Modes .........................................................................................................4Table 3Sample Floating-Point Execution Times (µs) at 16 MHz ..............................................................6Table 480960SB Pin Description: Bus Signals ........................................................................................8Table 580960SB Pin Description: Support Signals ................................................................................10Table 6DC Characteristics .....................................................................................................................14Table 780960SB AC Characteristics (10 MHz) ......................................................................................16Table 880960SB AC Characteristics (16 MHz) ......................................................................................17Table 980960SB QFP Pinout — In Pin Order ........................................................................................22Table 1080960SB QFP Pinout — In Signal Order ...................................................................................23Table 1180960SB PLCC Pinout — In Pin Order ......................................................................................24Table 1280960SB PLCC Pinout — In Signal Order .................................................................................25Table 1380960SB QFP Package Thermal Characteristics ......................................................................26Table 1480960SB PLCC Package Thermal Characteristics .. (26)180960SB1.0THE i960® PROCESSORThe 80960SB is a member of the 32-bit architecturefrom Intel known as the i960 processor family. Thesemicroprocessors were especially designed to servethe needs of embedded applications. The embeddedmarket includes applications as diverse as industrialautomation, avionics, image processing, graphicsand networking. These types of applications requirehigh integration, low power consumption, quickinterrupt response times and high performance.Since time to market is critical, embedded micropro-cessors need to be easy to use in both hardware and software designs.All members of the i960 processor family share a common core architecture which utilizes RISC technology so that, except for special functions, the family members are object-code compatible. Each new processor in the family adds its own special set of functions to the core to satisfy the needs of a specific application or range of applications in theembedded market.Figure 2. 80960SB Programming EnvironmentSIXTEEN 32-BIT GLOBAL REGISTERS SIXTEEN 32-BIT LOCAL REGISTERS g0g15r0r15 FOUR 80-BIT CONTROL REGISTERSFLOATING POINT REGISTERS ARCHITECTURALLYDEFINEDDATA STRUCTURESFFFF FFFFHINSTRUCTIONSTREAMINSTRUCTIONEXECUTIONPROCESSOR STATEREGISTERSINSTRUCTION POINTERARITHMETIC CONTROLSPROCESS CONTROLSTRACE CONTROLS ADDRESS SPACELOAD STORE0000 0000H INSTRUCTIONCACHE FETCH280960SB1.1Key Performance FeaturesThe 80960SB architecture is based on the mostrecent advances in microprocessor technology andis grounded in Intel’s long experience in the designand manufacture of embedded microprocessors.Many features contribute to the 80960SB’s excep-tional performance:rge Register Set. Having a large number ofregisters reduces the number of times that aprocessor needs to access memory. Moderncompilers can take advantage of this feature tooptimize execution speed. For maximum flexi-bility, the 80960SB provides thirty-two 32-bitregisters and four 80-bit floating point registers.(See Figure 2.)2.Fast Instruction Execution. Simple functionsmake up the bulk of instructions in mostprograms so that execution speed can beimproved by ensuring that these core instruc-tions are executed as quickly as possible. Themost frequently executed instructions — suchas register-register moves, add/subtract,logical operations and shifts — execute in oneto two cycles. (Table 1 contains a list of instruc-tions.)3.Load/Store Architecture. One way to improveexecution speed is to reduce the number oftimes that the processor must access memoryto perform an operation. As with otherprocessors based on RISC technology, the80960SB has a Load/Store architecture. Assuch, only the LOAD and STORE instructionsreference memory; all other instructionsoperate on registers. This type of architecturesimplifies instruction decoding and is used incombination with other techniques to increaseparallelism.4.Simple Instruction Formats. All instructionsin the 80960SB are 32 bits long and must bealigned on word boundaries. This alignmentmakes it possible to eliminate the instructionalignment stage in the pipeline. T o simplify theinstruction decoder, there are only fiveinstruction formats; each instruction uses onlyone format. (See Figure 3.)5.Overlapped Instruction Execution. Load operations allow execution of subsequent instructions to continue before the data has been returned from memory, so that these instructions can overlap the load. The 80960SB manages this process transparently to software through the use of a register score-board. Conditional instructions also make use of a scoreboard so that subsequent unrelated instructions may be executed while the condi-tional instruction is pending.6.Integer Execution Optimization. When the result of an arithmetic execution is used as an operand in a subsequent calculation, the value is sent immediately to its destination register.At the same time, the value is put on a bypass path to the ALU, thereby saving the time that otherwise would be required to retrieve the value for the next operation.7.Bandwidth Optimizations. The 80960SB gets optimal use of its memory bus bandwidth because the bus is tuned for use with the on-chip instruction cache: instruction cache line size matches the maximum burst size for instruction fetches. The 80960SB automatically fetches four words in a burst and stores them directly in the cache. Due to the size of the cache and the fact that it is continually filled in anticipation of needed instructions in the program flow, the 80960SB is relatively insen-sitive to memory wait states. The benefit is that the 80960SB delivers outstanding performance even with a low cost memory system.8.Cache Bypass. If a cache miss occurs, the processor fetches the needed instruction then sends it on to the instruction decoder at the same time it updates the cache. Thus, no extra time is spent to load and read the cache.380960SBTable 1. 80960SB Instruction Set Data MovementArithmetic Logical Bit and Bit Field LoadStoreMoveLoad Address Add Subtract Multiply DivideRemainderModuloShiftExtended MultiplyExtended Divide And Not And And Not Or Exclusive Or Not Or Or Not Nor Exclusive NorNotNandRotateSet Bit Clear Bit Not Bit Check Bit Alter Bit Scan For Bit Scan Over Bit Extract ModifyComparisonBranch Call/Return Fault CompareConditional CompareCompare and IncrementCompare and DecrementUnconditional Branch Conditional Branch Compare and Branch Call Call Extended Call System Return Branch and Link Conditional Fault Synchronize Faults DebugMiscellaneous Decimal Floating Point Modify Trace ControlsMarkForce Mark Atomic Add Atomic Modify Flush Local RegistersModify ArithmeticControlsScan Byte for EqualTest Condition Code Move Add with Carry Subtract with Carry Move Real Scale Round Square Root Sine Cosine TangentArctangentLogLog BinaryLog NaturalExponentClassifyCopy Real ExtendedCompareSynchronousConversion Synchronous LoadSynchronous Move Convert Real to Integer Convert Integer to Real480960SB Figure 3. Instruction FormatsControl Compare andBranchRegister toRegister Memory Access---ShortMemory Access---Long Opcode DisplacementOpcode Displacement Reg/Lit Reg M DisplacementOpcode Opcode Opcode Reg Reg Reg Reg/Lit Base Base M Modes Mode Ext’d Op Reg/LitX Offset Scale xx Offset1.1.1Memory Space And Addressing Modes The 80960SB offers a linear programmingenvironment so that all programs running on theprocessor are contained in a single address space.Maximum address space size is 4Gigabytes (232bytes).For ease of use the 80960SB has a small number ofaddressing modes, but includes all those necessaryto ensure efficient execution of high-level languagessuch as C.Table 2 lists the memory addressingmodes.Table 2. Memory Addressing Modes•12-Bit Offset •32-Bit Offset •Register-Indirect •Register + 12-Bit Offset •Register + 32-Bit Offset •Register + (Index-Register x Scale-Factor)•Register x Scale Factor + 32-Bit Displacement •Register + (Index-Register x Scale-Factor) +32-Bit Displacement Scale-Factor is 1, 2, 4, 8 or 161.1.2Data TypesThe 80960SB recognizes the following data types:Numeric:•8-, 16-, 32- and 64-bit ordinals •8-, 16-, 32- and 64-bit integers •32-, 64- and 80-bit real numbers Non-Numeric:•Bit •Bit Field •T riple Word (96 bits)•Quad-Word (128 bits)1.1.3Large Register Set The 80960SB programming environment includes a large number of registers. In fact, 32 registers are available at any time. The availability of this many registers greatly reduces the number of memory accesses required to perform algorithms, which leads to greater instruction processing speed.There are two types of general-purpose register:local and global. The global registers consist ofsixteen 32-bit registers (g0 though g15) and four580960SB 80-bit registers (fp0 through fp3). These registersperform the same function as the general-purposeregisters provided in other popular microprocessors.The term global refers to the fact that these registersretain their contents across procedure calls.The local registers, on the other hand, are procedurespecific. For each procedure call, the 80960SBallocates 16 local registers (r0 through r15). Eachlocal register is 32 bits wide. Any register can also beused for single or double-precision floating-pointoperations; the 80-bit floating-point registers areprovided for extended precision.1.1.4Multiple Register SetsTo further increase the efficiency of the register set,multiple sets of local registers are stored on-chip(See Figure 4). This cache holds up to four localregister frames, which means that up to threeprocedure calls can be made without having toaccess the procedure stack resident in memory.Although programs may have procedure calls nestedmany calls deep, a program typically oscillates backand forth between only two to three levels. As aresult, with four stack frames in the cache, the proba-bility of having a free frame available on the cachewhen a call is made is very high. In fact, runs ofrepresentative C-language programs show that 80%of the calls are handled without needing to accessmemory.If four or more procedures are active and a newprocedure is called, the 80960SB moves the oldestlocal register set in the stack-frame cache to aprocedure stack in memory to make room for a newset of registers. Global register g15 is the framepointer (FP) to the procedure stack.Global and floating point registers are not exchangedon a procedure call, but retain their contents, makingthem available to all procedures for fast parameterpassing.1.1.5Instruction CacheTo further reduce memory accesses, the 80960SBincludes a 512-byte on-chip instruction cache. Theinstruction cache is based on the concept of localityof reference; most programs are not usuallyexecuted in a steady stream but consist of manybranches, loops and procedure calls that lead to jumping back and forth in the same small section of code. Thus, by maintaining a block of instructions in cache, the number of memory references required to read instructions into the processor is greatly reduced.T o load the instruction cache, instructions are fetched in 16-byte blocks; up to four instructions can be fetched at one time. An efficient prefetch algorithm increases the probability that an instruction will already be in the cache when it is needed.Code for small loops often fits entirely within the cache, leading to a great increase in processing speed since further memory references might not be necessary until the program exits the loop. Similarly,when calling short procedures, the code for the calling procedure is likely to remain in the cache so it will be there on the procedure’s return.1.1.6Register Scoreboarding The instruction decoder is optimized in several ways.One optimization method is the ability to overlap instructions by using register scoreboarding.Register scoreboarding occurs when a LOAD moves a variable from memory into a register. When the instruction initiates, a scoreboard bit on the target register is set. Once the register is loaded, the bit is reset. In between, any reference to the register contents is accompanied by a test of the scoreboard bit to ensure that the load has completed before processing continues. Since the processor does not need to wait for the LOAD to complete, it can execute additional instructions placed between the LOAD and the instruction that uses the register contents, as shown in the following example:ld data_2, r4ld data_2, r5Unrelated instruction Unrelated instruction add r4, r5, r6In essence, the two unrelated instructions between LOAD and ADD are executed “for free” (i.e., take no apparent time to execute) because they are executed while the register is being loaded. Up to three load instructions can be pending at one time with three corresponding scoreboard bits set. By exploiting this feature, system programmers and compiler writers have a useful tool for optimizing execution speed.680960SB Figure 4. Multiple Register Sets Are Stored On-Chipr 15r 0310ONE OF FOUR LOCAL REGISTER SETS REGISTER CACHE LOCAL REGISTER SET1.1.7Floating-Point Arithmetic In the 80960SB, floating-point arithmetic has been made an integral part of the architecture. Having the floating-point unit integrated on chip provides two advantages. First, it improves the performance of the chip for floating-point applications, since no additional bus overhead is associated with floating-point calculations, thereby leaving more time for other bus operations such as I/O. Second, the cost of using floating-point operations is reduced because a separate coprocessor chip is not required.The 80960SB floating-point (real-number) data types include single-precision (32-bit), double-precision (64-bit) and extended precision (80-bit) floating-point numbers. Any registers may be used to executefloating-point operations.The processor provides hardware support for bothmandatory and recommended portions of IEEEStandard 754 for floating-point arithmetic, includingall arithmetic, exponential, logarithmic and othertranscendental functions.T able 3 shows executiontimes for some representative instructions.1.1.8 High Bandwidth Bus The 80960SB CPU resides on a high-bandwidthaddress/data bus. The bus provides a direct commu-nication path between the processor and the memory and I/O subsystem interfaces. The processor uses the bus to fetch instructions,manipulate memory and respond to interrupts. Bus features include:•16-bit data path multiplexed onto the lower bits of the 32-bit address path •Eight 16-bit half-word burst capability which allows transfers from 1 to 16 bytes at a time •High bandwidth reads and writes with25.6MBytes/s burst (at 16 MHz)Table 4 defines bus signal names and functions;Table 5 defines other component-support signalssuch as interrupt lines.Table 3. Sample Floating-Point Execution Times(µs) at 16 MHzFunction32-Bit 64-Bit Add0.60.8Subtract0.60.8Multiply1.12.0Divide2.0 4.5Square Root5.86.1Arctangent15.820.5Exponent17.719.5Sine23.825.9Cosine 23.825.9780960SB1.1.9Interrupt Handling The 80960SB can be interrupted in one of two ways:by the activation of one of four interrupt pins or by sending a message on the processor’s data bus.The 80960SB is unusual in that it automatically handles interrupts on a priority basis and can keep track of pending interrupts through its on-chip interrupt controller. Two of the interrupt pins can be configured to provide 8259A-style handshaking for expansion beyond four interrupt lines.1.1.10Debug FeaturesThe 80960SB has built-in debug capabilities. There are two types of breakpoints and six trace modes.Debug features are controlled by two internal 32-bit registers, the Process-Controls Word and the T race-Controls Word. By setting bits in these control words,a software debug monitor can closely control how the processor responds during program execution.The 80960SB provides two hardware breakpoint registers on-chip which, by using a special command, can be set to any value. When the instruction pointer matches either breakpoint register value, the breakpoint handling routine is automati-cally called.The 80960SB also provides software breakpoints through the use of two instructions: MARK and FMARK. These can be placed at any point in a program and cause the processor to halt execution at that point and call the breakpoint handling routine.The breakpoint mechanism is easy to use and provides a powerful debugging tool.Tracing is available for instructions (single step execution), calls and returns and branching. Each trace type may be enabled separately by a special debug instruction. In each case, the 80960SB executes the instruction first and then calls a trace handling routine (usually part of a software debug monitor). Further program execution is halted until the routine completes, at which time execution resumes at the next instruction. The 80960SB’s tracing mechanisms, implemented completely in hardware, greatly simplify the task of software test and debug.1.1.11Fault DetectionThe 80960SB has an automatic mechanism to handle faults. Fault types include floating point,trace and arithmetic faults. When the processor detects a fault, it automatically calls the appropriate fault handling routine and saves the current instruction pointer and necessary state information to make efficient recovery possible. Like interrupt handling routines, fault handling routines are usually written to meet the needs of specific applications and are often included as part of the operating system or kernel.For each of the fault types, there are numerous subtypes that provide specific information about a fault. For example, a floating point fault may have the subtype set to an Overflow or Zero-Divide fault.The fault handler can use this specific information to respond correctly to the fault.1.1.12Built-in TestabilityUpon reset, the 80960SB automatically conducts an exhaustive internal test of its major blocks of logic.Then, before executing its first instruction, it does a zero check sum on the first eight words in memory to ensure that the memory image was programmed correctly. If a problem is discovered at any point during the self-test, the 80960SB asserts its and will not begin program execution. Self test takes approximately 47,000 cycles to complete.System manufacturers can use the 80960SB’s self-test feature during incoming parts inspection. No special diagnostic programs need to be written. The test is both thorough and fast. The self-test capability helps ensure that defective parts are discovered before systems are shipped and, once in the field,the self-test makes it easier to distinguish between problems caused by processor failure and problems resulting from other causes.1.1.13CHMOSThe 80960SB is fabricated using Intel’s CHMOS IV (Complementary High Speed Metal Oxide Semicon-ductor) process. The 80960SB is available at 10MHz in the QFP package and at 10and 16 MHz in the PLCC package.880960SBTable 4. 80960SB Pin Description: Bus Signals (Sheet 1 of 2)NAME TYPE DESCRIPTIONCLK2I SYSTEM CLOCK provides the fundamental timing for 80960SB systems. It is divided by two inside the 80960SB to generate the internal processor clock.A31:16O T.S.ADDRESS BUS carries the upper 16 bits of the 32-bit physical address to memory. It is valid throughout the burst cycle; no latch is required.AD15:1, D0I/O T.S.ADDRESS/DATA BUS carries the low order 32-bit addresses and 16-bit data to and from memory. AD15:4 must be latched since the cycle following the address cycle carries data on the bus.A3:1O T.S.ADDRESS BUS carries the word addresses of the 32-bit address to memory. These three bits are incremented during a burst access indicating the next word address of the burst access. Note that A3:1 are duplicated with AD3:1 during the address cycle.ALEO T.S.ADDRESS LATCH ENABLE indicates the transfer of a physical address.ALE is asserted during a T a cycle and deasserted before the beginning of the T d state. It is active HIGH and floats to a high impedance state during a hold cycle (T h ).AS O T.S.ADDRESS STATUS indicates an address state.AS is asserted every T a state and deasserted during the following T d state.AS is driven HIGH during reset.W/R O T.S.WRITE/READ specifies, during a T a cycle, whether the operation is a write or read. It is latched on-chip and remains valid during T d cycles.DENO T.S.DATA ENABLE is asserted during T d cycles and indicates transfer of data on the AD lines. The AD lines should not be driven by an external source unless DEN is asserted. When DEN is asserted, outputs from the previous cycle are guaranteed to be three-stated. In addition,DEN deasserted indicates inputs have been captured; therefore input hold times can be disregarded.DEN is driven HIGH during reset.DT/RO T.S.DATA TRANSMIT / RECEIVE indicates the direction of data transfer to and from the bus. It is low during T a and T d cycles for a read or interrupt acknowledgment; it is high during T a and T d cycles for a write. DT/R never changes state when DEN is asserted. DT/R is driven HIGH during reset.READY IREADY indicates that data on AD lines can be sampled or removed. If READY is not asserted during a T d cycle, the T d cycle is extended to the next cycle by inserting a wait state (T w ).I/O = Input/Output, O = Output, I = Input, O.D. = Open Drain, T.S. = Three-state。

tuedo 产品介绍

BEA TUXEDO标准选件近几年来,以交易中间件为框架基础的三层客户机/服务器模式已被广泛证实为建立开放式关键业务应用系统的最佳环境。

这种模式的成功使用已为许多国际大型企业在应用的开发和部署方面节省了大量的时间和金钱。

三层客户机/服务器模式的核心概念是利用交易中间件将应用的业务逻辑、表示逻辑和数据分为三个不同的处理层,从而使其应用系统不但具备了大型机系统稳定、安全和处理能力高等特性,同时拥有开放式系统成本低、可扩展性强、开发周期短等优点。

而交易中间件作为构造三层结构应用系统的基础平台,提供了以下两个主要功能:负责客户机和服务器间的联接和通讯;提供一个三层结构应用开发和运行的平台。

交易中间件提供一个基础的框架去帮助你建立、运行和管理一个三层客户机/服务器模式的应用,使你不需要从零做起,大大缩短了应用开发的时间,提高了应用开发的成功率。

根据Standish Group的调查报告,采用一个成熟的交易中间件产品能够为应用开发节省25%-50%的时间。

而通过自己去开发应用里中间件功能的项目,有90%以上以失败告终。

一个优秀的交易中间件应具备以下六个条件:(1) 成熟、稳定、可靠(2) 很强的产品生命力(3) 完整、高质量的功能(4) 优秀的性能(5) 开放、遵循标准(6) 简单、易用而TUXEDO就是一个具备了以上所有条件的优秀的中间件产品。

本节将对TUXEDO进行介绍,包括以下内容:1 BEA TUXEDO的技术特色2 BEA TUXEDO的核心系统组成3TUXEDO技术详述3.1高速数据甬道3.2 目录服务的实现3.3 通讯服务3.4 负载平衡3.5 优先级3.6 伸缩性与动态配置的支持3.7 故障恢复与稳固的运行环境3.8 安全性3.9 交易完整性与分布式事务处理3.10 支持多种数据类型和字段控制语言3.11 管理3.12 网络调度与通讯失败的自动恢复3.13 提供5种API3.14 支持字符界面的开发3.15 对远程安装,设置的支持4 国际化5 与数据库的连接6 开发工具7 跨平台支持8 互连性9 典型开发过程简介10 节省费用1. BEA TUXEDO的技术特点(1) 最成熟、稳定、可靠的开放平台交易中间件产品∙16年的历史,世界第一个开放平台交易中间件产品∙数千个大型客户,数百万个前端用户,每天处理数亿笔交易∙在全球交易中间件市场(包括WAS)上占据了46%的市场占有率,包括主机平台,开放系统等等,而第二名的IBM只占据了9%(来自IDC1999报告)(2) 最强生命力的开放平台交易中间件产品●以开放为本,BEA TUXEDO出身于开放系统的化身—UNIX,从其基础体系结构上就是开放的,目的是支持所有开放的系统资源。

2BizBox产品介绍

终端架构图

----移动库房、便捷精确

“先进先出”,降低损耗

----移动库房、便捷精确

根据物料旳有关信息,系统自动按“先进先出”旳原 则提醒发料,可降低物料旳自然损耗,提升物料利用 率和产品质量。

移动商务、迅速响应

---- 2BizBox产品简介、特点

▲ 2BizBox可经过网络实现企业于分企业、在外出差人员及 客户和供给商旳实时交流,降低了因时间、空间限制所产 生旳成本,提升了办公效率及客户满意度。

2BizBox为企业排忧解难,其“权限+角色+顾客”旳顾客管理模 式,可在不影响业务流程旳情况下,让顾客便捷、安全地操作系 统,并最大程度地保护企业机密。

权限分配细致灵活,支持“最小权限原则”,最大程度保护企业 采用操作日志管理,做到有据可查 主要数据自动备份,降低数据安全风险

最小权限,最大保护

目的:以服务中国市场 中石油、中石化、中海油----战略合作伙伴 上海、山东、荆州----分企业 Pete Seitz----总裁 曾获《友谊奖》、《编钟奖》等荣誉

企业简介

赛瓦软件(Serva Software)

美国德克萨斯州 Wichita Falls ---- 总部 中国研发中心 ---- 上海 业界领先旳企业管理软件和电信组件提供商 关键产品 ---- 2BizBox,是面对生产制造型企业旳集成化企业

项目研发质量可控

----根据原则、严控质量

权威部门经过产品质量问题旳根源分析,发觉54%旳 质量问题源自研发阶段,对研发活动实施质量管理也 已经得到企业旳充分认可。

2BizBox系统严格按照ISO质量体系原则对研发过程 进行控制,可帮助企业构建能很好支撑企业关键业务 运作旳研发质量管理体系。

企业推介手册

企业推介手册适之宝•枕工坊连锁机构中国•青岛敦化路39号电话:0532— 81117555SUITBO 适之宝 好枕头 好睡眠 枕工坊这是创业星光闪耀的时代我们关注市场我们助力成长我们祝您成就事业辉煌您思虑良久您考察诸多在万千项目中您与我们牵手好枕头带来好颈椎好颈椎助力好睡眠10 年连锁运营经验10 年专注睡眠健康10周年行业巨献“3S量体定枕”有您的参与,我们一起走向更远顺应时代发展紧跟睡眠产业睡眠产业是个全新的新新产业,在欧美发达国家,已经渐成规模,而在中国却是个全新的产业。

像互联网在发展伊始不被注意一样,睡眠产业的发展也在逐步走向认知的过程中。

随着时代进步、科技发展,国人物质文化生活水平的提高,在一般性的生理、生活需求满足的前提下,消费品市场的需求日趋发生细分性的变化,日益加快的生活节奏,将中国传统的“朝9 晚5”的生活规律划上句号,随之而来的亚健康侵蚀着国人的健康。

2010 年,据世界卫生组织对14 个国家15 个基地两万余名在基层医疗就诊病人的调查,发现有27%的人有睡眠问题。

而中国睡眠研究会公布的最新睡眠调查结果则显示,我国成年人睡眠障碍发生率为38.2%,高于国外发达国家的失眠发生率。

金融危机爆发后,上海、广州、深圳等都市人群失眠比例增加两成以上,而有睡眠障碍人群比例更是多达近四成。

睡眠成为整个国人亚健康中的头号敌人,伴随对于睡眠的各种保健与治疗,睡眠行业正逐步崛起为一个新兴的超速发展的行业,据不完全统计,其整个市场的潜在价值,预计达到年度1200 亿元的消费格局。

伴随睡眠产业的发展,各种助眠的器具与药物风行一时,而真正人性化的帮助国人进入深度睡眠,改善国人睡眠质量的产品少之又少,适之宝枕工坊以“好枕头好睡眠”的企业宗旨,立足10 年枕头制造经验,联合睡眠专家,“ 10 年一剑”终成行业引领品牌。

在睡眠行业发展的同时,国人居室摆设的趋势也从“客厅文化”逐步转向“卧室文化”。

以前买一套沙发可以花几万,但自己每天都要睡八小时的床却不舍得花费几千元,现在人们则更加关注自己,几万甚至几十万一套的寝具开始被市场所接受。

“十年相伴 真情回馈”客服节

“十年相伴真情回馈”2015年客服节活动总公司运营中心总公司市场部2015年4月目录❖意义篇❖介绍篇❖操作篇❖资源篇A2015年客服节意义篇(一)活动主题2007年真情服务相伴永远2011年维护客户信息完善客户保障2008年欢喜迎奥运服务到永远2012年服务无小事诚信你我他2009年合众伴你行服务暖人心2013年服务无小事关爱你我他2010年你体验我承诺2014年分享合众共赢好礼(二)活动背景1.第九届客服节继续打造公司优质服务品牌;2.公司十周年真情回馈新、老客户;3.母亲节、儿童节、父亲节三节贯穿活动期间;4.合众高材生教育金保障计划即将上市。

(三)活动意义提升品牌形象(对公司来讲)强化服务意识(对员工来讲)做好客户积累(对员工来讲)弘扬传统孝道(对社会来讲)(四)活动宗旨让客户愿意玩(评星、抽奖)让队伍愿意讲(话题多易讲)让公司愿意送(验证更真实)让内外勤互动(树标杆创收)B2015年客服节介绍篇(一)活动时间2015年5月1日-2015年6月30日(二)活动内容线下活动:惠民服务、忠诚客户大回馈服务1.免息复效服务2.永久失效保单恢复效力服务3.补发保单免工本费服务4.合众有缘人服务5.惊喜送好礼线上活动:评选“十周年服务明星”(官网刊登服务明星)“种爱心结孝心”幸运大抽奖(全民抽奖、忠诚客户回馈)(三)活动流程图营销员邀请客户、非客户参与十周年客服节活动非客户客户线下活动:惠民服务、忠诚客户大回馈免息复效;永久失效保单恢复效力;补发保单免工本费;合众有缘人(非客户可参与);惊喜送好礼。

线上活动:评选“十周年服务明星”合众官网刊登评选结果线上活动:“种爱心结孝心”抽奖活动全民送好礼(参与抽奖中手机、魔豆);忠诚客户大回馈(参与抽奖中手机);营销员送“魔豆”拜访客户;各级营业单位举办客服节联谊活动。

(四)活动说明活动期间,针对因未按时缴费导致保单暂时失去效力的保单免息进行恢复效力的回馈。

免息复效线下活动:惠民服务、忠诚客户大回馈永久失效保单恢复效力针对因未按时缴费导致保单永久失效的年金险保单客户,推出“核保通过后补足未缴保费及利息,即可恢复保单效力”的优惠举措,具体细则参照客服中心通告。

Discuz!《中文版授权协议》

Discuz!X2.5 简体中文UTF8 版20120901中文版授权协议适用于中文用户版权所有(c) 2001-2012,北京康盛新创科技有限责任公司保留所有权利。

感谢您选择康盛产品。

希望我们的努力能为您提供一个高效快速、强大的站点解决方案,和强大的社区论坛解决方案。

康盛公司网址为,产品官方讨论区网址为。

用户须知:本协议是您与康盛公司之间关于您使用康盛公司提供的各种软件产品及服务的法律协议。

无论您是个人或组织、盈利与否、用途如何(包括以学习和研究为目的),均需仔细阅读本协议,包括免除或者限制康盛责任的免责条款及对您的权利限制。

请您审阅并接受或不接受本服务条款。

如您不同意本服务条款及/或康盛随时对其的修改,您应不使用或主动取消康盛公司提供的康盛产品。

否则,您的任何对康盛产品中的相关服务的注册、登陆、下载、查看等使用行为将被视为您对本服务条款全部的完全接受,包括接受康盛对服务条款随时所做的任何修改。

本服务条款一旦发生变更, 康盛将在网页上公布修改内容。

修改后的服务条款一旦在网站管理后台上公布即有效代替原来的服务条款。

您可随时登陆康盛官方论坛查阅最新版服务条款。

如果您选择接受本条款,即表示您同意接受协议各项条件的约束。

如果您不同意本服务条款,则不能获得使用本服务的权利。

您若有违反本条款规定,康盛公司有权随时中止或终止您对康盛产品的使用资格并保留追究相关法律责任的权利。

在理解、同意、并遵守本协议的全部条款后,方可开始使用康盛产品。

您可能与康盛公司直接签订另一书面协议,以补充或者取代本协议的全部或者任何部分。

康盛拥有本软件的全部知识产权。

本软件只供许可协议,并非出售。

康盛只允许您在遵守本协议各项条款的情况下复制、下载、安装、使用或者以其他方式受益于本软件的功能或者知识产权。

I. 协议许可的权利您可以在完全遵守本许可协议的基础上,将本软件应用于非商业用途,而不必支付软件版权许可费用。

您可以在协议规定的约束和限制范围内修改康盛产品源代码(如果被提供的话)或界面风格以适应您的网站要求。

EZUC+产品介绍-V2-2014

飞腾4G 给力EZUC+赞云(中国)软件有限公司 华中区 Brice.su 2014赞云剪影赞云剪影赞云集团为大中国知名系统商,拥有10多 赞云集团为大中国知名系统商 拥有10多 年的经营历史,市场重点在于提供企业多 元化云端商务方案 拥有数十项得奖与专 元化云端商务方案,拥有数十项得奖与专 利产品,以及五十多个行业数百家知名的 企业客户。

企业客户开启新页 创就不凡历 史 一 刀 难 分 敌 友 罗 盘 千 转 境 由 心 生北 京企业伙伴 互动专家广 州上 海台 北 无 锡百业齐赞 云端首选EZUC+的简介EZUC+帮助企业推动下一个进步的环节产品概要EZUC+(易之讯)是赞云集团的新一代统一通信(UC)产品,具备 许多划时代创新技术可以应用在各行各业在线商务方案。

EZUC+同时也是赞云云通信产品系列的核心平台,可以支持与 是赞 通 产 列 核 以支 呼叫中心、社交网、以及多种云端商务应用的在线互动 。

EZUC+的开发是基于赞云研发团队超过十年在电信(telecom) 与信息(datacom)相关领域的专研的成果 拥有许多大型客户 与信息(datacom)相关领域的专研的成果,拥有许多大型客户 建置实例以及专利技术。

以企业为中心,以人为本设计EZUC+专注于企业与人的沟通 核心是“企业”和“个人”而不是“设备” 每位用户都有一个识别ID 可以链接多种设备 多个号 可以链接多种设备与多个号码以人为中心的整合通讯资源管理整合通讯资源管理: UC Resource Management 整合通讯簿多渠道多媒体通讯统一拨号方案一点即通轻松整合社交媒体通讯簿分类群组设定通讯与通知方式全球节费整合通讯与在线会议远距跨区节费通讯与在线会议台北/上海/北京三方跨部门在线会议跨区节费客户联络:ex.台北拨上海客户随时随地任何装置的UC端点沟通IP Phone、Desktop/Web UC Client、/Smart Phone/Pad APP在线实时讨论、开会通知确认在线马上加入会议讨论邀请开会通知,确认参加UC端点自动通知进入会议多媒体在线同步工具有效沟通()()整合通讯(VoIP/IM)与同步数据(桌面分享、电子白板)视讯面对面沟通主管实时管理监控与报表主管远距沟通管理节费分析报表整合沟通讯息监控分析员工各种管道所有讯息均可纪录监控有效地监控提升企业沟通与信息安全性5 Any微客电话客微客服电话客服客企系统客网页客服企业系统客服EZUC+ 移动性的统一通信移动性的统通信EZ UC+手机APPEZ UC+ 桌面版EZ UC+ EZ UC+网页版/Pad网页版/Pad客户SIPSIP 电话四种终端随心沟通创造企业完美云通信体验电脑电话手机平板在家里在大巴上在高铁上在咖啡馆里在高铁在机场在宾馆里机在办公室在会议室EZUC+ 部署架构:简单统海量的端方案IDC hosted简单,统一,海量的云端方案Enterprise:VPN routerSIPnetworkEZUC+ Client:SIP Phone, PC/Notebook, Android, Apple iOSEZUC+ 网络实施拓扑图(方案一:单纯公司内线通话 方案 单纯公司内线通话)EZUC+ 网络实施拓扑图(方案二 全云端机房内外线部署) (方案二:全云端机房内外线部署)EZUC+ 网络实施拓扑图(方案三 本地PSTN外线 云端内线 (不考虑现有设备连接)) (方案三:本地PSTN外线+云端内线交换机集成:Avaya & EZUC+ 整合架构可以透过云端部署方式支持异地办公室的同步作业 (via TLS):TLSEZUC+安全的网络架构Firewall/NAT Firewall/NATOffice AEZUC+ CloudVPN/TLS T Tunnel lAP因特网Office BVPN/TLS TunnelAPEZUC+的定位和特色赞云CESS 产品全景图EZUC+ 是划时代的统一通信产品EZUC+产品定位与竞争分析 产 定位 竞争功能概要/分类/特色 (符号表示 - V: 有 X:没有 NA:未知) 厂牌/产品名 最后一公里连结 最后 公里连结 交换 统 统一 即时 主要用户 机 通信 消息 CTI:计算机电话整 社交网,互联网,云端服务企业 企业 企业 企业 企业 企业 个人 个人 个人 个人 个人云端伺服能力 V (公私有云) NA NA X V (公私有云) X V (公有云) V (公有云) V (公有云) V (公有云) V (公有云)BlissCloud/EZUC+ Cisco / Various Avaya / Aura & IPO Siemens IMO Microsoft Lync Microsoft Skype Tencent / WebChat Tencent / QQ NetEase / YiXin Navar / LINE说明:V V V V X X X X X X XV V V V V V X X X X XV X X X V V V V V V V合 V (EZcomm)V V X X X X X X X XV (EZSocial, EZPhone, EZCloud) X X X X X X X X X X呼叫中心/ 客服系统 一体机 V (EZiPCC) X X X X X X X X X X模块化 服务 V X X X NA NA NA NA NA NA NA1.PBX(交换机):企业内部电话连接设备用来串接员工固话机与传真机 2.UC(统一通信):企业内部统一电信设备用来串接电话与多媒体设备 3.IM(实时通信):互联网与移动互联网上的个人化统一沟通平台,特别是可以用来进行文字聊天、文件传输、数据分享等功能 4.最后一公里连结:是为更为广义UC定义可以整合其他方案(包括PBX,IM,企业应用系统,云端服务) 5.云服务能力:该方案可以采用公有云或者虚拟私有云方式布署 6.呼叫中心一体机方案:系指具备交换机与固话机,交互式语音应答(IVR-InteractiveVoiceResponse),自动话务分配(ACD-AutoCallDistribution), CTI支持下的自动弹屏与软电话,话务员话术脚本,质量保证的录音系统EZUC+下载地址IOS下载 直接在APP Store上搜索EZUC+即可 直接在APPStore上搜索EZUC+即可 安卓版下载地址链接 /zh cn/download.html /zh-cn/download.html 二维码扫描企业进阶号:UCDEMO网络好声音 ‧ 精彩说不完EZUC+带来的价值❶❷ * * ❸❹ ❺❻ EZUC+应用场景应用场景一 大中型劳密企业、厂区通信特点 信特 人数较多,劳动性密集。

年会总结工作汇报PPT

分析明年可能面临的市场、竞争、技术等挑战。

3

应对措施制定

针对预测的挑战,制定相应的应对措施和预案。

组织架构调整和人力资源配置计划

组织架构调整

根据明年战略需求,对组织架构进行优化和调整。

人力资源配置计划

根据新的组织架构,制定明年人力资源配置计划。

培训和发展计划

为确保员工适应新的组织架构和岗位要求,制定培训和发展计划。

GN

WENKU

KEEP VIEW

年会总结工作汇报

REPORTING

ONE

2023-2026

WENKU DESIGN

WENKU DESIGN

CATALOGUE

目 录

• 工作回顾与成果展示 • 团队建设与文化培育 • 内部管理优化及运营效率提升 • 市场拓展与合作伙伴关系维护 • 明年发展规划与目标设定 • 感谢致辞与展望未来

推进信息化管理系统建设,实现业务流程线上化、数据化。

培训与推广

组织员工培训,提高系统使用熟练度,推动系统在全公司的广泛应 用。

数据安全与隐私保护

加强系统安全防护和数据隐私保护,确保公司业务数据安全。

节能减排、绿色环保实践案例

能源管理与节能措施

01

实施能源管理计划,推广节能设备和技术,降低能耗成本。

期待未来辉煌

展望公司未来发展前景,期待公司在全体员工的共同努力下,创造更加辉煌的业 绩。

WENKU DESIGN

WENKU DESIGN

WENKU

KEEP VIEW

感谢观看

THANKS

REPORTING

END

2023-2026

WENKU DESIGN

WENKU DESIGN

品味重回MD,这些事

品味重回MD,这些事《品味重回MD ,这些事》------------------- 写在前⾯筹备这篇⽂章,我准备了很久,也很⽤⼼,这是我第⼆次写测评。

上次关于walkman回顾,这次侧重Mini Disc,算是⼀路⾛来,对⾃⼰接触过的MD来⼀次总结回顾,现在我还保持着对MD,这种⼩众“古董”随声听的喜爱。

加⼊论坛时间不长,这篇测评⽂章算是送给论坛烧友们的⼀份礼物吧,从⽂字到图⽚,⾃⼰亲⼿包办。

对于⾃⼰接触过,收藏的机器,还是本着尽量客观公平的感受去测评,但也只是笔者⼩编我的⼀家之⾔,欢迎⼤伙,拍砖指正。

(好的测评,顶顶更茁壮,拍拍更健康!)--------------------⼴告⼴告:要是⼤伙觉得⽂章写得还可以,多顶多留⾔,最好能帮忙升级精华帖,⼩编就灰常灰常感谢⼤家了!-------------------我的MD情节:其实和⼤伙差不多,上学时,第⼀次见别⼈的MD,什么羡慕啊,觉得声⾳很惊艳啊,⾼科技啊,价格很贵啊之类的。

当时的EJ 打头的CD wakman的圆始魅⼒,棒形线控也同样给我留下了深刻的印象。

上学时候也买过很多电⼦书,《新潮电⼦》之类的。

最喜欢⼝袋数码这个栏⽬,相信⼤伙也都不陌⽣。

04年还出了本随声听专辑增刊,很喜欢这本书。

⼀直保存到现在。

偶尔翻翻,很怀旧,很实⽤。

本来列了⽬录,但真正开写了,会有些变动,但⼤致差不多,现在就开始正⽂,⼤伙⼀起MD的怀旧之旅~(注:现在有的机⼦我就上图⽚,曾今拥有的就不上图⽚,只⽂字叙述了)----------------------------------------------⼩⼆,给客官敬⾹茶~ --------------------------------------------------正⽂注释: 1⼩编不去从⾳质的⾓度测评,⽽是从个⼈听感的⾓度主观描述,尽量做到严谨,客观。

2由于排版原因,⽂字在前,图⽚在后,请读者穿插阅读,图⽂并茂更富乐趣。

86架构指令集

字符串操作指令集

MOVSB,MOVSW,MOVSD

功能: 字符串传送指令

语法: MOVSB MOVSW MOVSD

标志位: 无

CMPSB,CMPSW,CMPSD

功能: 字符串比较指令

语法: CMPSB CMPSW CMPSD

标志位: C,P,Z,S,O

SCASB,SCASW

LOOPE(Z)

地址 LOOPNE(Z) 地址

标志位: 无

CALL,RET

功能: 子程序调用,返回指令

语法: CALL 地址 RET RET n

标志位: 无

INT,IRET

功能: 中断调用及返回指令

语法: INT n IRET

标志位: 在执行INT时,CPU会自动将标志寄存器的值入栈,在执行IRET时则会将堆栈中的标志值弹回寄存器

O: OVERFLOW,O=1时成立

P: PARITY,P=1时成立

PE: PARITY EVEN,P=1时成立

PO: PARITY ODD,P=0时成立

S: SIGN,S=1时成立

Z: ZERO,Z=1时成立

LOOP

功能: 循环指令集

语法: LOOP 地址

标志位: 依指令S而定

影响标志: C,P,A,Z,S,O

SUB,SBB

功能:减法指令

语法: SUB OP1,OP2 SBB OP1,OP2

格式: SUB r1,r2 SUB r,m SUB m,r SUB r,data SUB m,data

影响标志: C,P,A,Z,S,O

INC,DEC

功能: 把OP的值加一或减一

帝豪集团画册文案

帝豪集团画册文案一、封面、封底、封2、封3二、扉页:十年磨砺,十年拼搏;十年精益求精,打造帝豪集团品牌,奠定帝豪集团百年基业!三、集团概述篇(Group Profile):A人才荟萃,凝心聚力!这里,汇聚了真才实干之精英;这里,集聚了团结奋进之力量;这里,凝聚了创新发展之决心。

B忆,“帝豪”往昔峥嵘岁月,挥斥方遒;思,“帝豪”今朝硕果,豪情满怀;期,“帝豪”未来光辉,龙骧虎步。

四、集团产业篇(Group Industry):多元产业,各领风骚酒店格调奢华,服务细腻,彰显豪华高雅气派;房地产超然景致堪赞欢,让您尽享尊贵生活的从容;金融业和其它文化产业扬帆奋进,同心协力,打造帝豪传奇!(1)房地产业(Real Estate Industry)东莞市碧湖花园房地产有限公司Dongguan Avon Park Real Estate Co., LTD(2)酒店业(Hotel Industry)I帝豪国际酒店管理有限公司Royal International Hotel Management Co., LTDII帝豪花园酒店(五星)Royal Garden Hotel(Five-star)III帝豪假日酒店(五星)Royal Holiday Hotel(Five-star)(3)金融业(Financial Industry)I东莞市永正信用担保有限公司Dongguan Yongzheng Credit Guarantee Co., LTDII东莞市恒光实业投资有限公司Dongguan Hengguang Industrial Investment Co., LTDIII东莞市裕华实业投资有限公司Dongguan Yuhua Industrial Investment Co., LTD(4)其它产业(Other industry)I东莞市常安物业管理有限公司Dongguan Changan Property Management Co., LTDII东莞市永正创意产业园有限公司Dongguan Yongzheng Creative Industry Park Co., LTDIII东莞市永正贸易有限公司Dongguan Yongzheng Trade Co., LTD五、集团文化篇(Group Culture):孟子曰:“仁者爱人,有礼者敬人。

产品介绍宣传彩页Word(模板)

XXXXX公司XXX-XX产品介绍彩页

PLACE YOUR TEXT HERE

XX公司产品介绍

修改完成后建议转化为PDF文件使用

iOS 下载安装步骤

1、使用微信扫描该二维码,并在iPhone 中的Safari 中打开。

2、点击安装,在弹出的对话框选择同意。

3、在设置——通用——设备管理中信任企业证书。

技术特点 技术特点一 技术特点一,技术特点一。

技术特点一,技术特点一。

技术特点二 技术特点一。

描述产品特点 技术特点一。

描述产品特点 技术特点一,描述产品特点 技术特点 技术特点一。

描述产品特点 技术特点一。

描述产品特点

2018-产品历程

•此处添加详细文本描述,建议与标题相关并符合整体语言风格,语言描述尽量简洁生动。

2017-产品历程

•此处添加详细文本描述,建议与标题相关并符合整体语言风格,语言描述尽量简洁生动。

2016-产品历程

•此处添加详细文本描述,建议与标题相关并符合整体语言风格,语言描述尽量简洁生动。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《站长》杂志第28期内容推介

十年相伴共创经典 Discuz!系列经典产品回顾

站长朋友们,是否还记得Discuz! 官网那些5年前的老ID旧面孔?

是否还记得曾经的Discuz! 1.0 、Discuz! 1.0 和Discuz! 5.5“长”得什么模样?在过去的十年里,Comsenz在站长的陪伴下一路走来,推出了数款经典产品,成为社区动力,引领社区潮流发展。

在即将迎来Comsenz十周年之际,《站长》杂志特别回首过去十年来的数款经典Discuz! 产品,以及那些始终陪伴左右的站长朋友,谨以对更多陪伴Discuz! 、支持Discuz! 的站长们表示由衷的感激。

Discuz! 1.0 ——Discuz! 起点站

大C在开发Discuz! 1.0 的时候,一定不会想到之后商业化的Discuz!

1.0 、免费开源的Discuz! 4.0 、以及现在“跨界融合”的Discuz! X 系列;Discuz! 1.0 的各项功能、模板也可能是Discuz! 系列中最简陋的,最朴素的,但没有它,也就没有后来的数个经典产品。

所以,Discuz! 1.0 就像是Discuz! 系类产品的“起点站”和“加油站”一样,不断的激励着Discuz! 的后续产品一步步的改进、创新,引领社区发展潮流。

许多的草根站长,不也是这样一步步发展起来的吗?许多业已取得成功的站长,在初建社区的时候,也未曾想过能取得今天的人气与盈利,只是抱着许三多“不抛弃、不放弃”的信念从小做大,根据市场需求逐步改

进自己的产品,一步步走向了成功。

这种“从小到大”、“坚持不放弃”、“以市场为导向”的理念不仅是说Discuz! 1.0 ,也同样适用于社区。

Discuz! 2.0 ——商业化

从技术角度说,Discuz! 2.0 并不是一款完全成熟的产品,主要原因在于一些BUG的存在,而且这些BUG并未得到官方的及时修复;但在社区产品贫乏的年代,这些BUG毫不影响Discuz! 2.0 作为一款实用、市场急需的社区产品而深受用户认可;从Discuz! 2.0 开始,Discuz! 进行商业化转型,大C(戴志康)决定收费,以几千元一套的价格出售Discuz! 1.0 。

渊源:这里面有2个小插曲,第一个是关于大C的。

当Discuz! 被800多个社区使用后,大C决定以500元一套的定价来销售,可是市场并不买账,一套产品也没卖出去。

面对这种情况,大C破釜沉舟,干脆将售价提高了4倍变成2000元。

后来,真有一位香港用户表示愿意付费购买这个软件,加上二次开发一共支付了3000元,紧接着付费购买的人越来越多,大C赚到了第一桶金50万元。

第2个小插曲是关于Discuz! 2.0 以及freediscuz的。

正是因为Discuz! 2.0 的收费,以及不提供免费的客户支持,许多社区用户的BUG 得不到解决。

这时候有3个人发现了潜在的市场需求,他们建立了一个freediscuz的社区,力求每天至少解决Discuz! 2.0 的2个BUG,很快得到了Discuz! 用户的欢迎;可以说,freediscuz是官方最早的第三方支持团队,这名团队的成员之一现在已经是Comsenz的首席科学家。

Discuz! 2.5 ——简洁、易扩展

Dicuz! 2.5拥有诸多的特点,其架构稳定、安全,综合了以往Dicuz! 版本的技术精华,而且简洁、扩展性强。

Discuz! 2.5 不仅仅是一款简单的社区软件,更是一款“简洁”的建站工具。

形象点说:站长可以用Discuz!

2.5 随意改造、开发出另外一款社区产品,站长甚至可以在Discuz! 2.5 的基础上改装出一个款CMS系统出来。

Discuz! 2.5 将简单做到了极致,也把拓展性与想象力做到了千万种可能。

渊源:Dicuz! 2.5的真实版本号应该是Discuz! 3.12。

而之所以版

本号被命名为“2.5”是因为它的“免费”属性。

Dicuz! 从2.0版本之后开始商业化,所有版本都开始收费;而freediscuz也从最初的“解决BUG”发展到为用户提供“免费版”的Discuz! 。

大C在发布了Discuz! 3.12

商业版后,将这个版本的核心代码提供给freediscuz,用于升级免费版本的Discuz! 1.0 。

但是出于保护商业版的原因,这款产品虽然功能上和3.12一样强大甚至超越3.12,但是命名要比商业版低,所以命名为2.5。

Discuz! 4.0 ——免费、开源

伴随着Discuz! 4.0 的发布,戴志康和Comsenz迎来了新的发展契机,随着风险投资资金的引入,给了Discuz! 更广阔的市场空间以及更具想象力的发展方向,戴志康决定将收费了3年的Discuz! 正式开源、免费。

2005年12月12日,这绝对是一个值得纪念的日子,戴志康在这一天宣布万年免费宣言《Discuz!宣言》,决定Discuz! 免费开源一万年不变。

从这一天开始,Discuz! 以及Comsenz乘上了发展的快班车。

渊源:其实很多站长朋友在评论自己最喜欢的Discuz! 经典版本时,关于4.0与4.1有很大的分歧。

有的站长喜欢4.0,有的站长更喜欢4.1。

是什么小小的改动引起如此大的分歧呢?答案是一个内置的“奇虎搜索”。

对于这款搜索工具来说,有的站长需要,认为是丰富了论坛的功能;但有的站长执着于Discuz! 1.0 时代的“简单”,崇尚简单、专一的社区产品;其实2种观点没有对错,只代表站长个人观点,但毫无疑问的是,Discuz! 4.0 和Discuz! 4.1同样经典。

Discuz! 5.0 ——门户、博客

时间发展到了2006年,这时候“博客”概念开始兴起,大大小小的专业博客网站兴起,门户网站也大力推广自己的博客,康盛创想也推出了自己的专业博客软件X-Space 个人空间。

Discuz! 5.0 也同样融入了“博客”的概念,在当时的市场环境下,Discuz! 是唯一拥有“个人空间”的社区。

由“博客”衍生出来的不仅仅是“空间”,还有发帖形式的变化。

出于用户自我展示的需要,开发人员首次在Discuz! 5.0 中推出了“特殊贴”概念,用户可以发布商品贴、活动贴等等。

在5.0之前,用户只能发两种普通帖子:内容贴和投票贴。

Discuz! 6.0 ——模板经典

可以说,Discuz! 6.0 是站长最喜欢的一款产品之一,至今仍旧有许多BBS社区停留在这款产品或继续选择这款产品,在站长心目中,Discuz!

6.0 可以称得上是永远的经典。

而之所以如此多的站长喜欢Discuz! 6.0 ,除了其简单、稳定和安全外,风格模板也是用户喜欢它的重要原因之一。

一方面,Discuz! 发展到6.0,已经发展了7年,Discuz!的开发工程师们不断打磨Discuz!,其各项功能已经渐趋完善;另一方面,UI设计师们通

过数个版本的经验,已经深谙用户心理,对他们喜欢的颜色、风格、布局进行了细致入微的把握,从而推出了大家都相对认可的产品。

渊源:2004年的Discuz! 4.0 和 2007年的Discuz! 6.0 ,虽然只

有3年的差距,但却经过了互联网带宽的飞速增长。

如果说2004年大家

上网速度还如蜗牛一般时,到了2007年就像兔子了。

2004年的Discuz! 不能有太多图片展示,太多颜色、风格、布局上的搭配,因为速度与效率第一;而到了2007年,随着“带宽”的解放,Discuz! 的UI设计师们终于

把自己多年积累的经验以及丰富的创意酣畅淋致的表达在Discuz! 6.0 的模板之中了。

Discuz! 7.0 ——社交化、年轻化

中国互联网经过十多年的发展,逐步呈现社交化、年轻化趋势。

Discuz!

7.0 应时代之需而生。

为了适应互联网的和网民群体的发展变化(年轻网

民越来越多),Comsenz精准把握时代脉搏,推出了Discuz! 7.0 这样一

款年轻化、社交化、时尚化的产品,更多模板,更炫风格,更多展示,更符合年轻网民使用。

《站长》杂志介绍:

《站长》杂志是由康盛创想(Comsenz)出品的一本面向站长群体的精神读物。

自2008年3月以落伍者论坛站长“拒绝游泳的鱼”为封面人物成功发布首刊,《站长》杂志迄今为止已经发行28期。

十年相伴共创经典 Discuz!系列经典产品回顾

希望以上资料对你有所帮助,附励志名言3条:

1、理想的路总是为有信心的人预备着。

2、最可怕的敌人,就是没有坚强的信念。

——罗曼·罗兰

3、人生就像爬坡,要一步一步来。

——丁玲。