1_VHDL修改Quartus自己产生的testbench

Quartus-II调用modelsim仿真方法

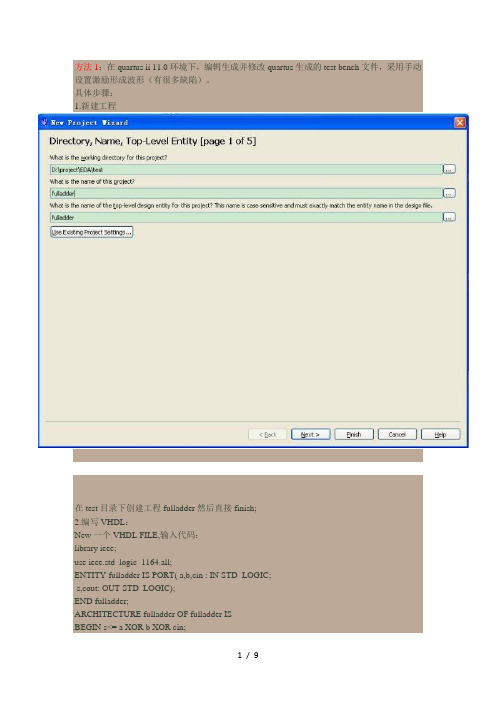

方法1:在quartus ii 11.0环境下,编辑生成并修改quartus生成的test bench文件,采用手动设置激励形成波形(有很多缺陷)。

具体步骤:1.新建工程在test目录下创建工程fulladder然后直接finish;2.编写VHDL:New一个VHDL FILE,输入代码:library ieee;use ieee.std_logic_1164.all;ENTITY fulladder IS PORT( a,b,cin : IN STD_LOGIC;s,cout: OUT STD_LOGIC);END fulladder;ARCHITECTURE fulladder OF fulladder ISBEGIN s<= a XOR b XOR cin;cout <=(a AND b) OR (a AND cin) OR (b AND cin);END fulladder;保存在test目录下,文件名为默认fulladder。

3. 在Quartes II 11.0界面菜单栏中选择 Tools-->options选项卡中选中EDA tool options,在该选项卡中下面的ModelSim-Altera一项指定安装路径为(如d:/Altera/11.0/modelsim_ae/win32aloem)4.在Quartes II 11.0界面菜单栏中选择Assignments->Settings。

选中该界面下EDA Tool settings中的Simulation一项;Tool name中选择ModelSim-Altera;Format for output netlist中选择开发语言的类型VHDL或其它,如图:然后点击APPLY应用和OK。

5.设置完成后,编译工程:在Quartus II 11.0界面菜单栏中选择菜单栏选择Processing-->start Compilation,等待编译,无错后会在test目录下生成simulation目录,执行下一步。

AD6 中VHDL设计及创建Testbench参考

VHDL语言设计参考VHDL是一种用于数字系统行为级描述的编程语言。

VHDL具备了许多适合于电子器件行为级描述的特性,无论是简单的逻辑门电路还是复杂的微处理器或用户自定制的器件。

从而,VHDL满足电路行为中电气特征(诸如信号上升/下降时间、门延迟和功能)的精确描述。

并且利用VHDL仿真模型可以搭建更大的可仿真电路。

VHDL还是一种通用的可编程语言,就如同利用高级语言在计算机上编写复杂的设计程序,VHDL允许输入复杂电子电路的行为级设计,并实现自动电路综合或系统仿真。

同时,VHDL也不同于高级语言,采用并发事件设计(即在执行阶段内,每个语句行为是并行执行的);这一特性取决于硬件电路设计上固有的并行执行的特性。

VHDL最重要的应用之一就是设计电路的执行规范,语法规则与Testbench相一致。

Testbench是用于验证电路在时间上行为级描述的。

在任何时候,Testbench都将作为VHDL 设计项目的一个组成部分。

注:符号 <=为付值操作符,表示将符号右边的数值给符号左边的变量;一个完整的VHDL设计项目至少要包含一个实体(entity)和结构体(architecture)定义。

对于一个大型设计,通常需要定义多个实体/结构对并且将他们连接在一起形成一个完整的电路。

实体定义用于描述电路的输入/输出端口;结构体定义是VHDL设计中最小的组成单元。

在仿真或综合执行前,每个实体必须被相对应结构体封装。

在结构体中描述了实际的功能。

实体定义entity comp_name isport(in_port : in bit_vector(7 downto 0); out_port : out bit);end comp_name;结构体定义:architecture comp_name of entity_name isbegin<conditional assignment>;end comp_name;注:关键字process用来封装复杂的顺序逻辑设计;VHDL语言中的数据类型:VHDL设计中实际由5种设计单元类型构成:实体、结构体、程序包、程序包体和配置。

VHDL——如何写简单的testbench

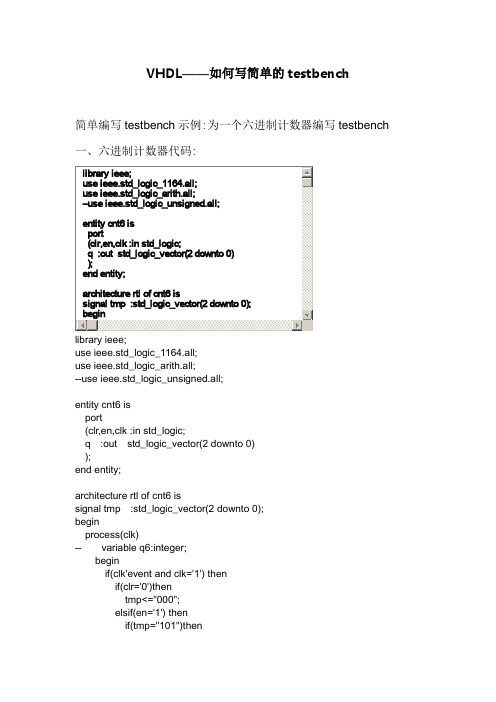

use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;--use ieee.std_logic_unsigned.all;entity cnt6 isport(clr,en,clk :in std_logic;q :out std_logic_vector(2 downto 0) );end entity;architecture rtl of cnt6 issignal tmp :std_logic_vector(2 downto 0); beginprocess(clk)-- variable q6:integer;beginif(clk'event and clk='1') thenif(clr='0')thentmp<="000";elsif(en='1') thenif(tmp="101")thentmp<="000";elsetmp<=unsigned(tmp)+'1';end if;end if;end if;q<=tmp;-- qa<=q(0);-- qb<=q(1);-- qc<=q(2);end process;end rtl;二、六进制计数器testbench的代码signal en :std_logic:='0';signal clk :std_logic:='0';signal q :std_logic_vector(2 downto 0);constant clk_period :time :=20 ns;begininstant:cnt6 port map(clk=>clk,en=>en,clr=>clr,q=>q);clk_gen:processbeginwait for clk_period/2;clk<='1';wait for clk_period/2;clk<='0';end process;clr_gen:processbeginclr<='0';wait for 30 ns;clr<='1';wait;end process;en_gen:processbeginen<='0';wait for 50ns;en<='1';wait;end process;end rtl;--测试平台文件(testbench)的基本结构library ieee;use ieee.std_logic_1164.all;entity test_bench is --测试平台文件的空实体(不需要端口定义) end test_bench;architecture tb_behavior of test_bench iscomponent entity_under_test --被测试元件的声明port(list-of-ports-theri-types-and-modes);end component;begininstantiation:entity_under_test port map(port-associations);process() --产生时钟信号……end process;process() --产生激励源……end process;end tb_behavior;------------------------------------------------------------------- --简单计数程序源码library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_unsigned.all;entity sim_counter isport(clk :in std_logic;reset :in std_logic;count :out std_logic_vector(3 downto 0));end entity;architecture behavioral of sim_counter issignal temp :std_logic_vector(3 downto 0);beginprocess(clk,reset)beginif reset='1' thentemp<="0000";elsif clk'event and clk='1' thentemp<=temp+1;end if;end process;count<=temp;end behavioral;------------------------------------------------------------------- --简单计数程序,测试文件代码(testbench)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.numeric_std.all;entity counter_tb_vhd is --测试平台实体end counter_tb_vhd;architecture behavior of counter_tb_vhd is--被测试元件(DUT)的声明component sim_counterport(clk :in std_logic;reset :in std_logic;count :out std_logic_vector(3 downto 0));end component;--输入信号signal clk:std_logic:='0';signal reset :std_logic:='0';--输出信号signal count :std_logic_vector(3 downto 0);constant clk_period :time :=20 ns; --时钟周期的定义begindut:sim_counter port map(clk=>clk,reset=>reset,counter=>counter);clk_gen:processbeginclk='1';wait for clk_period/2;clk='0';wait for clk_period/2;end process;tb:process --激励信号beginwait for 20 ns;reset<='1';wait for 20 ns;reset<='0';wait for 200 ns;wait; --will wait forever;end process;end;--激励信号的产生方式--1.以一定的离散时间间隔产生激励信号的波形--2.基于实体的状态产生激励信号,也就是说基于实体的输出响应产生激励信号--两种常用的复位信号--1.周期性的激励信号,如时钟--2.时序变化的激励型号,如复位--eg.产生不对称时钟信号w_clk<='0' after period/4 when w_clk='1' else'1' after 3*period/4 when w_clk='0' else'0';--eg.产生堆成时钟信号,process语句clk_gen1:processconstan clk_period := 40 ns;beginclk='1';wait for clk_period/2;clk='0';wait for clk_period/2;end process;四、如果自己不想写这些testbench的这些固定格式,可以在quartus 里自动生成testbench文件的模板,然后往里面写信号就行了步骤:processing->start->start test bench template write这里需要注意的是要在仿真选项里选择一个仿真工具,然后才会生成testbench自动生成的testbench模板格式如下:-- Copyright (C) 1991-2008 Altera Corporation-- Your use of Altera Corporation's design tools, logic functions-- and other software and tools, and its AMPP partner logic-- functions, and any output files from any of the foregoing-- (including device programming or simulation files), and any-- associated documentation or information are expressly subject-- to the terms and conditions of the Altera Program License-- Subscription Agreement, Altera MegaCore Function License-- Agreement, or other applicable license agreement, including,-- without limitation, that your use is for the sole purpose of-- programming logic devices manufactured by Altera and sold by-- Altera or its authorized distributors. Please refer to the-- applicable agreement for further details.-- ***************************************************************************-- This file contains a Vhdl test bench template that is freely editable to-- suit user's needs .Comments are provided in each section to help the user -- fill out necessary details.-- ***************************************************************************-- Generated on "03/13/2011 20:05:04"-- Vhdl Test Bench template for design : cnt6---- Simulation tool : ModelSim (VHDL)--LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY cnt6_vhd_tst ISEND cnt6_vhd_tst;ARCHITECTURE cnt6_arch OF cnt6_vhd_tst IS-- constants-- signalsSIGNAL clk : STD_LOGIC;SIGNAL clr : STD_LOGIC;SIGNAL en : STD_LOGIC;SIGNAL q : STD_LOGIC_VECTOR(2 DOWNTO 0);COMPONENT cnt6PORT (clk : IN STD_LOGIC;clr : IN STD_LOGIC;en : IN STD_LOGIC;q : OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END COMPONENT;BEGINi1 : cnt6PORT MAP (-- list connections between master ports and signalsclk => clk,clr => clr,en => en,q => q);init : PROCESS-- variable declarationsBEGIN-- code that executes only onceWAIT;END PROCESS init;always : PROCESS-- optional sensitivity list-- ( )-- variable declarationsBEGIN-- code executes for every event on sensitivity list WAIT;END PROCESS always;END cnt6_arch;。

test bench 教程

最近项目上要用到FPGA,之前用的一直是verilog,后面换成了VHDL。

对ISE一窍不通啊,研究了一些testbench文件的编写,record一下。

借用一下博文/lovelink/item/ff34ce9b12f45988581461ac的话。

首先对TESTBENCH作一个形象一些的比喻吧,它就象是一个面包板(做过电路实验吧),他对外没有任何接口,但它要向要插在他上面的器件提供接口,这样才能正确的插入,还有它必须对插在它上面的器件提供正常的信号。

当然在它上面还必须要有这个器件。

这时就完成了一个TESTBENCH。

应该大概明白了其中的意思了吧。

好了,根据上面的比喻我们可以非常明确的知道一个TESTBENCH要写一些什么东西,首先它对外无接口,所以它的实体部分是空的。

在它上面要有相应的器件,所以在它的结构体中要申明我们要测试的器件,也就是component的申明。

还有就是它要对器件提供接口,所以它的结构体应该提供一些信号,并且要对这些信号进行正确的测试赋值。

当然还要进行一些插入工作,就是信号的对应工作。

这样一个TESTBENCH就完成了。

原理很简单的,应该很容易明白。

不过在真正的测试中可能不会用太多的这种方式吧,应该会选用测试向量吧,这个的准确性更高一些。

不过怎么样写测试向量,这到是一个有大学问的东西,因为当我们的管脚很多的时候,测试的向量数目是要心指数增长的,当然不可能把所有的情况都测试完成了,只有是测试其中的一部分,这儿怎么样写出有代表性的一组测试向量是很有学问的,应该说是研究的热点吧。

几个testbench要用到的重要语句:(1)wait:无限等待,表示永远挂起,对于汉语wait语句的进程来说,进程在一开始执行一次后面就不执行了;(2)wait on 信号表:敏感信号等待语句,等待敏感信号表中的信号发生变化才执行;(3)wait until 表达式:条件等待语句,当条件表达式中所含的信号发生了变化,并为true时,进程才脱离等待状态;(4)wait for 时间表达式:此语句中声明了一个时间段,从从执行到当前的wait语句开始,只要这个时间段内,进程处于等待状态,超过这段时间,进程自动恢复执行该等待语句的下一条语句。

基于quartus ii11.0的modelsim仿真

Quartus自从9.0版本以后就没有自带仿真工具。

需要进行仿真要另外安装仿真工具。

下面就以altera-modelsim6.6d 版本介绍一个简单的VHDL语言编写的程序的仿真步骤。

Quartus 工具为11.0版本。

1).新建一个工程。

以与非门为例。

打开quartus11.0工具栏的file->new->New Quartus II Project.点击OK。

点Next创建工程文件夹,如andnotgate。

输入工程名称。

点Next先别管它,点Next选择芯片型号,因为是只是仿真,可以随便选。

或者默认。

点Next.选择仿真工具,这里选择ModelSim-Altera.点Next.点Finish。

新建了一个工程。

2).向新建工程添加VHDL源文件File->new->VHDL File->OK编写源程序:library ieee;use ieee.std_logic_1164.all;entity andnotgate isport(a,b:in std_logic;c:out std_logic);end entity andnotgate;architecture rt1 of andnotgate is beginc<=not(a and b);end rt1;保存源程序在新建的工程中File->save as保存。

编译源文件:点击Start compilation编译成功。

3).利用modelsim进行波形仿真要进行仿真必须先创建一个testbench的仿真激励文件。

testbench文件的编写可以利用软件提供的模板进行修改。

生成testbench模板processing->start->start test bench template writer->OK打开新生成的testbench模板。

在新建工程里的simulation->modelsim里的后缀为.vht的文件。

VHDL--Quartus-II调用Modelsim进行仿真只是分享

VHDL ----- Quartus II(11.1版本)调用Modelsim进行仿真之前仿真一直是用Quartus II自带的“Vector Waveform File”,但因其功能有限,在老师的推荐下接触了Modelsim,捣腾了一段时间之后总算有所收获了。

在查资料的过程中,发现好多二者联合的讲解都是用Verilog语言写的例子,而VHDL很少。

以下是我总结的用VHDL 语言的具体步骤以及要注意的细节~~坎坷的路就略过了,直接展示成果。

例子是‘八位七段数码管的动态扫描显示’一.用Quartus II 进行VHDL语言编译1.首先建立工程File->New project Wizard(第三个图标)填入所建工程的目录以及名称,注意稍后的源程序中实体名必须和这里的名称相同。

填好后单击finish,然后单击yes。

2.新建VHDL源程序文件File->New->VHDL File->OK将程序写进去(这里只讲步骤,不讲源程序的写法)注意:程序中的实体名必须和之前建工程时所命名的文件名相同!然后保存一下,不用改动,直接单击保存。

快捷键按钮在界面中上方的红色倒三角,显示编译成功之后关闭编译报告。

4.设备设置具体的实验器件根据提供的实验板设定Assignment->Device4.引脚分配Assignment->Pin Planner在Location下的方格中填入对应的硬件引脚,也是根据实验板而定6.引脚分配好之后再次编译一下,使分配的引脚起作用。

一、调用Modelsim1、设置仿真工具为Modelsim-alteraTool->Options->EDA Tool Options,在Modelsim-Altera后面的地址改为Modelsim-Altera.exe在你电脑中的位置,然后点击OK。

2、写TestBench文件,这里使用Quartus II生成的模板Processing->start->Start TestBench Template Writer,显示成功后关闭生成报告。

1 ModelSim的使用与Testbench的编写

重温了基本的Quartus操作和语法后,需要对手头的工作进行仿真验证,Quartus 9.x自带的Vector Waveform已经淘汰掉了,必须用 ModelSim进行仿真。

现在就开始一步步入手ModelSim,并通过与Quartus无缝衔接实现仿真。

本文使用了ModelSim10.0c + QuartusII 10.0,其他版本基本雷同,请自行研究。

源程序如下:module add(mclk,rst_n,a_in,b_in,c_out);input mclk, rst_n;input[7:0] a_in, b_in;output[8:0] c_out;reg[8:0] c_out;always@(posedge mclk, negedge rst_n)beginif(!rst_n)c_out <= 9'h0;elsec_out <= a_in + b_in;endendmodule请建立工程,将源程序编译通过.1.设置第三方EDA工具在Tools -> Options中设置ModelSim的安装路径,注意要设置到win32文件夹(64位软件对应的就是win64)。

建立一个工程(依然以加法器为例)。

在Assignments -> Settings中设置仿真工具为ModelSim。

这样Quartus就能无缝调用ModelSim了。

当然也可以在建立工程的时候就设置仿真工具。

2.编写Testbench说到Testbench,你可以叫它Testbench,或者Testbenches,但不是Test Bench。

说起来,就连Quartus也没注意这个问题,至于原因嘛参见Common Mistakes In Technical Texts一文。

文章中还列举了些别的错误用语,包括Flip-flop不能写成Flipflop,等等。

文章链接:/papers/Technical_Text_Mistakes.pdf我们可以通过Quartus自动生成一个Testbench的模板,选择Processing -> Start -> Start Test Bench Template Writer,等待完成后,在导航栏中打开刚才生成的Testbench,默认是保存在simulation\modelsim文件夹下的.vt格式文件。

quartus软件使用及VHDL语言

南理工紫金学院

EDA 设计流程

设计输入

原理图,VHDL语言

项目编译

功能和时序仿真

配置下载

硬件测试

南理工紫金学院

使用软件简介 QuartusⅡ是Altera公司提供的软件。在QuartusⅡ上 可以完成设计输入、元件适配、时序仿真和功能仿真、编 程下载整个流程。

主要特点

1. QuartusⅡ支持和其它公司所提供的 EDA工具接口。

3 最后以end结束结构体部分。

南理工紫金学院

逻辑运算符

And(与), Or(或), Not(非), Nand(与非), Nor(或非), Xor(异或), Xnor (同或)。

能进行逻辑运算的数据类型: bit、bit_vector 、 boolean std_logic 、std_logic_vector

南理工紫金学院

设计输入

新建工程向导

Quartus 使用流程

南理工紫金学院

设计输入

Quartus 使用流程

为工程和顶层文件命名

工作库

工程名

工程的顶层设计实体名, 名字一定要和设计文件中 的实体名匹配,可以和工程 名不一致

任何一项设计都是一项工程,都必须为此工程建立一个放置 与此工程相关的所有设计文件的文件夹,此文件夹被默认为工作 库(work library) ,一般不同的设计项目最好放在不同的文件 夹中,而同一工程的所有文件都必须放在同一文件夹中。

EDA技术有很大不同: 1)采用硬件描述语言作为设计输入。 2)库(Library)的引入。 3)设计文档的管理。 4)强大的系统建模、电路仿真功能。 5)适用于高效率大规模系统设计的自

顶向下设计方案。 6)全方位地利用计算机自动设计、仿 真和测试技术。 7)对设计者的硬件知识和硬件经验要 求低。 8)高速性能好。 9)纯硬件系统的高可靠性。

VHDL Test bench文件的三种生成方式

VHDL TestBench基础TestBench的主要目标Test bench(TB)是一种VHDL代码,目的在于验证HDL模型的功能是否正确。

Test bench是电路规格的一部分,其主要目标是:∙实例化UUT(Unit Under Test, UUT),以前版本也叫DUT(Design Under Test) ∙为UUT产生激励波形∙产生参考输出,并将UUT的输出与参考输出进行比较∙提供测试通过或失败的指示TestBench产生激励的三种方式响应可以在test bench中产生,也可以通过文件进行存储,以备后用。

常用的产生TB的三种方法为:∙直接在testbench中产生∙从矢量中读入∙从单独的激励文件中读入比较流行的做法是使用matlab产生激励文件,由testbench读入该激励文件并将激励馈送到UUT,UUT产生的相应输出以文件的形式存储,由matlab读取并与理想的响应作比较。

1. 简单的TestBench简单的testbench只适合于相对比较简单的设计。

如图1-1所示,在testbench 中只是简单的实例化了一个UUT,激励在testbench中产生,这种方式的testbench 可重用性差。

示意图如下。

UUT tb_adder.vhd代码:仿真结果2. 具有独立激励源的test bench将激励源作为一个文件在test bench中进行实例化,比较适合于具有复杂输入和简单输出的设计,激励源可以是一个实体或者一个进程之类的。

例如下图中adder的输入激励是在一个单独的实体counter中产生的。

激励源tb_counter.vhd代码test bench中的实例化代码(将tb_counter实例化)仿真结果3. 使用TextIO的testbench当设计的输入输出都比较复杂时,尤其是在做复杂的算法仿真时,需要产生多种形式的激励输入,还要对仿真结果输出做复杂的分析时,使用TextIO的test bench具有最高的效率。

(完整版)实例解读Testbench编写方法

实例解读Testbench编写方法前言:在进行quartusII设计时,不少人刚开始觉得仿真极其不方便,还需要编写测试文件,浪费时间精力。

不过小编想告诉大家,其实testbench编写很容易学,不外乎wait for 语句的堆叠就可以了,至于高深的用法,对一般程序都涉及不到,没必要弄得那么复杂。

下面看看实例吧,将详细说明testbench的编写:我们可以通过Quartus自动生成一个Testbench的模板,选择Processing —〉 Start -〉Start Test Bench Template Writer,等待完成后打开刚才生成的Testbench,默认是保存在sim ulation\modelsim文件夹下的.vt格式文件.打开vt文件后可以看到Quartus已经为我们完成了一些基本工作,包括端口部分的代码和接口变量的声明,我们要做的就是在这个做好的模具里添加我们需要的测试代码.一个最基本的Testbench包含三个部分,信号定义、模块接口和功能代码.‘timescale 1ns/ 1ps表示仿真的单位时间为1ns,精度为1ps.想要进行仿真首先要规定时间单位,而且最好在Testbench里面统一规定时间单位,而不要在工程代码里定义,因为不同的模块如果时间单位不同可能会为仿真带来一些问题,而timescale本身对综合也就是实际电路没有影响。

其实Testbench本身可以看做一个模块或者设备(本例中的模块名为add_vlg_tst),和你自己编写的模块进行通信。

通过Testbench模块向待测模块输出信号作为激励,同时接收从待测模块输出的信号来查看结果.因此,在待测模块中的reg型信号在Testbench中就变成了wire,待测模块中的wire型信号在Testb ench中则对应为reg型。

那么inout怎么办呢,inout型信号也要设成wire,同时要用一个reg型信号作为输出寄存器,同时设置一个三态门,由一个使能信号控制,如:assign inout_sig = out_en ? out_reg : 1’bz;处理完接口和声明之后,需要自己设置一些激励信号,激励信号的内容就是肯能会输入到待测模块中的波形.下面我们就来写一个简单的测试程序.实例:60进制计数器源代码:library ieee;use ieee.std_logic_1164。

与matlab联合仿真的VHDLtestbench的编写

与matlab联合仿真的VHDLtestbench的编写首先用matlab 生成测试数据,用*.TXT文件保存,方法如下:fid = fopen('myfile.txt', 'wt'); %%fid 为文件指针变量fprintf(fid, %8.0f, 'test_data') %%写文件命令,%8.0f把数据的存储成的格式,'test_data'生成的数据,用来测试。

fclose(fid); %%关闭文件,防止文件变改或者破坏编写波形测试文件本人用的是xilinx公司提供的ise12.1软件,在新建文件中选择vhdl bench文件类型,关联上自己所要仿真的文件,就会自动生产vhdl bench文件,在这个文件中加入自己的激励就行了。

联合测试应该在library 中把textio程序包包括,就是在文件的刚开始添加LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;--自动生成的use textio.all; --添加现在介绍一下textio程序包1 TEXTIO介绍TEXTIO 是VHDL 标准库STD 中的一个程序包(Package)。

在该包中定义了三个类型:LINE 类型、TEXT类型以及SIDE 类型。

另外,还有一个子类型(subtype)WIDTH。

此外,在该程序包中还定义了一些访问文件所必须的过程(Procedure)。

1.1 类型定义(1)type LINE is access string定义了LINE 为存取类型的变量,它表示该变量是指向字符串的指针,它是TEXTIO 中所有操作的基本单元。

读文件时,先按行(LINE)读出一行数据,再对LINE 操作来读取各种数据类型的数据;写文件时,先将各种的数据类型组合成LINE,再将LINE 写入文件。

在用户使用时,必须注意只有变量才可以是存取类型,而信号则不能是存取类型。

Modelsim 仿真方法总结

Modelsim 仿真方法总结Modeling 仿真工具是Model公司开发的。

它支持Verilog、VHDL以及他们的混合仿真。

Modelsim各版本的使用方法大体一致,Modelsim仿真主要分为前仿真和后仿真。

下面来具体介绍modelsim的仿真方法,涉及quartus-modelsim联合(使用)仿真的差异会特别提示。

前仿真与后仿真说明1.1 前仿真前仿真也称为功能仿真、行为仿真。

旨在验证电路的功能是否符合设计要求,其特点是不考虑延迟(包括门延迟与线延迟),主要验证电路与理想情况是否一致。

前仿真需要用到RTL级代码(由源代码经过综合后产生)与Testbench。

1.2)后仿真后仿真也称为时序仿真或者布局布线仿真。

是指在电路已经映射到特定的工艺环境以后,综合考虑门延迟与线延迟的影响,验证电路在一定的时序条件下是否存在时序违规以及能否满足设计构想的过程。

需要用到的文件是——从布局布线结果中抽象出来的门级网表、testbench和后缀名为sdo或者sdf的标准时延文件。

注:扩展名为sdo和sdf的标准时延文件包含门延迟与实际布线延迟,能较好的反应芯片的实际工作情况。

二)modelsim仿真主要有以下几个步骤:(1)建立库并映射库到物理目录;(2)编译源代码(包括Testbench);(3)执行仿真;解释:①库:modelsim中有两类仿真库。

一种是工作库,默认名为work;另一种是资源库。

Work库中存放当前工程下所有已经编译过的文件,所以编译前一定要建立一个work 库。

资源库存放work库中已经编译文件所要调用的资源,这样的资源可能有很多,它们被存放在不同的资源库内。

(例如要想对综合在cyclone芯片中的设计做后仿真,就需要有一个名为cyclone_ver的资源库。

)映射库用于将已经预编译好的文件所在目录映射为一个modelsim可识别的库。

(此即是为仿真库建立一个逻辑映像的行为过程,后面会提到,在modelsim中新建库时,create a new library and a logical mapping to it或a map to an existing libraryd的提示)上述三个步骤是大的框架,前仿真和后仿真均是按照这个框架进行的,建立modelsim工程对前后仿真来说都不是必须的。

testbench 的编写及使用方法思考与体会

【导言】1. 什么是 testbench?2. testbench 的作用和优势【testbench 编写】3. testbench 编写的基本步骤4. testbench 编写的注意事项5. testbench 编写过程中的实际问题与解决方法【testbench 使用方法】6. testbench 的使用流程7. testbench 的结果分析和验证8. testbench 使用过程中的常见错误及解决办法【结语】9. testbench 的编写与使用思考10. testbench 的未来发展预期【导言】1. 什么是 testbench?Testbench 是指在数字电路设计中对被测电路模块进行验证的仿真测试工具。

它是一种独立的模块化设计,用于测试另一个模块或芯片的功能和性能。

在数字电路设计中,testbench 是非常重要的工具,可以帮助设计人员验证电路的正确性和稳定性。

2. testbench 的作用和优势testbench 主要用于验证设计的功能和性能是否符合预期,并且检测是否有潜在的bug存在。

它可以模拟各种工作条件和异常情况,帮助设计人员有效地发现和解决问题。

testbench 的优势在于能够大大提高验证的效率和准确性,节省了大量的人力和时间成本。

【testbench 编写】3. testbench 编写的基本步骤要编写一个高质量的 testbench,需要遵循以下基本步骤:(1)分析被测电路的功能和接口,确定测试的重点和目标;(2)编写测试数据生成模块,包括设计测试用例和对输入信号进行生成;(3)编写时序控制模块,用于控制测试数据的输入和时序顺序;(4)编写仿真结果分析模块,用于对仿真结果进行验证和分析;(5)整合以上模块,编写完整的 testbench。

4. testbench 编写的注意事项在编写 testbench 的过程中,需要注意以下几点:(1)保证测试用例的全面性和充分性,覆盖各种工作条件和异常情况;(2)时序控制模块的设计要符合被测电路的时序要求,保证测试数据的输入顺序和时序正确;(3)仿真结果分析模块要设计完善,能够对仿真结果进行准确的验证和分析;(4)编写的 testbench 要符合规范,可读性强,方便他人理解和维护。

(verilog和vhdl)Testbench编程指南

(verilog和vhdl)Testbench编程指南TestBench编程指南如今数字设计的规模变得越来越庞大,设计的复杂程度也越来越高,这就使得设计的验证变得越来越困难,而且费时费力。

为了应对这种挑战,验证工程师依靠各种验证工具和方法。

对于大型设计,如几百万门的设计,通常采用一整套正式的验证工具。

然而,对于小一些的设计,设计工程师发现往往采用带TestBench的HDL仿真工具是最好的途径。

TestBench已经变成验证高级语言设计的一种标准的方法。

通常,TestBench执行以下任务:z例化设计,使其可测试(DUT-design under test);z通过将测试向量应用到模型来仿真例化后的可测试的设计;z将结果输出到终端,或者输出波形窗口;z将真实的结果和期望的结果进行比较;一般,TestBench采用工业标准的VHDL或者Verilog硬件描述语言来编写。

TestBench调用功能设计,然后仿真。

复杂的测试文件执行附加功能――例如,他们包含逻辑以决定合适的设计激励或者比较真实的结果和期望的结果。

以下章节将讨论一个组织良好的测试文件的组成,以及例举了一个带有自检的测试文件(自动将真实的结果和预期的结果进行比较)。

下图是一个标准的HDL验证的流程。

自从测试文件可以用VHDL或者Verilog编写以来,测试验证流程就可以在平台和供应商的工具交叉进行。

同时,由于VHDL和Verilog都是标准的公用的语言,所以用VHDL或者是Verilog描述的验证可以很简单的被再使用。

图1. HDL验证流程测试文件构成:测试文件可以采用VHDL或者Verilog语言编写。

由于测试文件只是用来仿真的,他们就不被用于综合的RTL语言子集的语法所约束。

相反,所有行为结构都可以被使用。

这样,测试文件可以被写的更通用,更易于维护。

所有的测试文件都包含以下基本内容,如表1。

如上所属,测试文件经常同时包含附加功能,如结果的可视化显示和内建错误检测。

quartus 怎么打开testbench

1、打开quartus ii,Tools菜单下Options项,General中EDA Tool Options,指定Modelsim 的路径,比如C:\altera\11.0\modelsim_ae\win32aloem,或者

C:\altera\Modelsimse10.0b\win64

2、设计好quartus下的工程后,Processing菜单栏下Start项右侧展开选择“Start TestBench Templates Writer”,就会创建一个testbench的模版。

在此基础上修改你所需要的testbench

3、testbench设计完后,Assignments菜单下Setting项,左侧栏中找到EDA Tool Settings 下的Simulation,在右侧Simulation的设置框中,选择Tool name,到“MoreEDA Netlist Writer Settings”中,选择“Compile test bench,点击右侧的“Test Benches”,”New“,把testbench文件的module名填入top level项(11.0下;9.0下三项都要补齐,第三项是例化名)。

在下面的“Test bench files”中指定你的testbench,模板文件默认是在simulation--modelsim 中,后缀是.vt,“Add”进来,一路OK。

4、仿真时,“Tools”菜单下“Run EDA Simulation Tool”右侧展开,第一个为功能仿真,第二个为时序仿真。

For Quartus&ModelSim:程序以及对应的testbench

通过查找“啊啊n”可以快速定位某一个程序啊啊1###########空调温度控制器#####################module temp_ctrl(clock,temp_high,temp_low,too_hot,too_cold,just_right,heat,cool); input clock;input temp_high,temp_low;output too_hot,too_cold,just_right;output heat,cool; //对应加热和制冷两种操作reg heat,cool;reg [2:0] state; //共有三种状态通过0位1位2位的值为1来区别assign too_hot=state[0]; //assign是分配的意思assign too_cold=state[1];assign just_right=state[2];//parameterHOT=3'b0_0_1, //对应state[0]第0位值为1COLD=3'b0_1_0,OK=3'b1_0_0;always@(posedge clock)begincase(state) //case(*) -- default -- endcaseOK: //一种状态可能向另外两种转变if() begin end和elseif() begin end然后“else;”if(temp_high==1&&temp_low==0)beginstate<=HOT;heat<=0;cool<=1;endelse if(temp_high==0&&temp_low==1)beginstate<=COLD;heat<=1;cool<=0;endelse;HOT:if(temp_high==0&&temp_low==1)beginstate<=COLD;heat<=1;cool<=0;endelse if(temp_high==0&&temp_low==0)beginstate<=OK;heat<=0;cool<=0;endelse;COLD:if(temp_high==1&&temp_low==0)beginstate<=HOT;heat<=0;cool<=1;endelse if(temp_high==0&&temp_low==0)beginstate<=OK;heat<=0;cool<=0;endelse;default:;endcaseendinitial //用于定义初始状态beginstate<=OK;heat<=0;cool<=0;endendmodule###################################### 对应的testbench程序//其实很短module testreg clk;reg high,low;wire hot,cold,ok;wire heat,cool;parameter DELAY=100;temp_ctrl m(clk,high,low,hot,cold,ok,heat,cool); //例化。

VHDL TestBench基础系列之一

VHDL TestBench基础系列之一

Testbench,就是测试平台的意思,具体概念就多不介绍了,相信略懂FPGA的人都知道。

一般来说,Testbench使用工业标准VHDL或者Verilog HDL语言来描述。

简单的Testbench通过调用用户设计的功能模块,然后进行仿真。

较为复杂的Testbench还包括一些其他的功能,比如包含特定的激励向量或者进行实际输出与期望输出的比较等。

如图所示是一个标准的HDL验证流程,图中表达了上述的Testbench功能。

TestBench的主要目标是:

实例化DUT-Design Under Test

为DUT产生激励波形

产生参考输出,并将DUT的输出与参考输出进行比较

提供测试通过或失败的指示

TestBench产生激励的三种方式:

直接在testbench中产生

从矢量中读入

从单独的激励文件中读入

比较流行的做法是使用matlab产生激励文件,由testbench读入该激励文件并将激励馈送到DUT,DUT产生的相应输出以文件的形式存储,由matlab读取并与理想的响应作比较。

由于测试文件只是在仿真时使用,因此在综合中对RTL语言的语法限制在测试文件中并不存在。

相反地,测试文件可以编写得更加通俗,所有的行为结构语法都可以使用,使之更加容易理解。

所有的测试文件都包含了如表7.1所示的结构。

测试文件的共同结构

好了,Testbench就写到这里,但没有结束,实践是检验真理的唯一标准,下一次将结合Modelsim,以可视化的方式继续探讨Testbench,深入了解仿真的意义。

QUARTUSII操作修改

一、新建工程

双击QuartusII软件启动坐标,即可启动QuartusII软件,启动界 面如下:

新建一个 项目时, 点击file->

new project wizard…,

出现以下 一个对是需要你指定 项目保存的路径,支持含中文字符的路径,第 二行是需要你为这个项目取一个名称,第三行 是需要你为这个项目的顶层实体取个名字,这 三个设定好后,点击“next”,出现下面一个界 面:

2-1. 设计含异步清 0 和同步时钟使能 的加法计数器

(1) 实验目的:学习计数器的设计和仿真, 进一步熟悉VHDL设计技术。 (2) 实验内容:在QuartusⅡ上对例2.1进行编 辑、编译和仿真。说明例中各语句的作用,详 细描述该示例的功能特点,给出其所有信号的 仿真波形。 (3) 实验报告:根据实验内容写出实验报告, 包括实验目的、程序设计注释、编译仿真波形 和分析结果。

点击进入下一界面点击完成选择vhdlfile点击进入编辑界面输入文本文件输入文本文件保存文件注意保存的文件名要和文本的实体名一致注意保存的文件名要和文本的实体名一致启动编译编译成功建立仿真文件设置仿真时间区域并进行波形文件存盘选择file中的saveas设置仿真结束时间设置仿真结束时间设置仿真结束时间为100us在空白处双击鼠标左键在空白处双击鼠标左键选择选择nodefinder点击list选择需要的信号选择需要的信号接下来分别对各输入端口进行设置完成之后单击保存文件按钮进行保存

实验2.2 实验

7段数码显示译码器设计 段数码显示译码器设计

LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL ; ENTITY DECL7S IS PORT ( A : IN STD_LOGIC_VECTOR(3 DOWNTO 0); LED7S : OUT STD_LOGIC_VECTOR(6 DOWNTO 0) ) ; END ; ARCHITECTURE one OF DECL7S IS BEGIN PROCESS( A ) BEGIN CASE A IS WHEN "0000" => LED7S <= "0111111" ; WHEN "0001" => LED7S <= "0000110" ; WHEN "0010" => LED7S <= "1011011" ; WHEN "0011" => LED7S <= "1001111" ; WHEN "0100" => LED7S <= "1100110" ; WHEN "0101" => LED7S <= "1101101" ; WHEN "0110" => LED7S <= "1111101" ; WHEN "0111" => LED7S <= "0000111" ; WHEN "1000" => LED7S <= "1111111" ; WHEN "1001" => LED7S <= "1101111" ; WHEN "1010" => LED7S <= "1110111" ; WHEN "1011" => LED7S <= "1111100" ; WHEN "1100" => LED7S <= "0111001" ; WHEN "1101" => LED7S <= "1011110" ; WHEN "1110" => LED7S <= "1111001" ; WHEN "1111" => LED7S <= "1110001" ; WHEN OTHERS => NULL ; END CASE ; END PROCESS ; END ;