实验三_基于Quartus_II的流水灯设计仿真(新)

流水灯在Proteus下的仿真实现

流水灯在Proteus下的仿真实现重庆邮电大学微处理器与嵌入式系统设计课程实验报告实验名称:流水灯在Proteus下的仿真实现学期:2014-2015学年第2学期班级:学号:学生姓名:任课教师:实验教室:二〇一五年〇四月十四日【实验名称】流水灯在proteus下的仿真实现实验要求:1、基本要求:4个流水灯循环闪烁,1、3、2、4流水灯交替闪烁;2、扩展要求:8个流水灯依次闪烁,1、3、5、7、2、4、6、8流水灯交替闪烁,流水灯逐渐亮1、1-2、1-3、1-4、1-5、1-6、1-7、1-8。

实验目的:1、熟悉proteus 软件,了解proteus 软件的结构组成和功能,掌握 Proteus软件在单片机仿真中的应用,为开发、调试单片机应用系统做准备;2、熟练掌握 isis 环境中电路图的绘制;3、熟悉keil c51软件的程序设计方法;4、掌握keil c51软件与proteus软件联合仿真调试的方法。

实验方法:1、通过proteus软件绘制出由单片机和LED构成的仿真电路;2、通过keil软件编写控制单片机并点亮LED的程序;3、将keil生成的hex文件导入proteus中的单片机中,实现仿真。

4、观察仿真现象。

实验步骤:1、打开软件:双击ISIS 7 Professional 图标,随后就进入了 Proteus ISIS 集成环境。

2、添加元器件:单击pick from libraries,通过搜索栏搜索所需元件(如:AT89C52、LED),根据元件预览区域的显示,双击所需元件,元件则出现在原理图编辑环境的元件列表区。

用同样方法找出原理图所需全部元件。

3、放置元器件:在元件列表区单击所需放置的元件,将鼠标置于图形编辑窗口该对象的欲放位置,单击鼠标左键,该对象完成放置。

同样方法放置原理图所需全部元件。

4、放置电源和地:选择terminal mode选择电源和地,以放置元器件相同的放法放置电源和地。

流水灯(电路和汇编)-Proteus和Keil仿真演示实例知识讲解

流水灯(电路和汇编)-P r o t e u s和K e i l仿真演示实例示例要求:在80C51单片机的P2口连接8个发光二极管指示灯,编程实现流水灯的控制,轮流点亮指示灯。

在KEIL 51中编程序,形成HEX文件;在PROTEUS中设计硬件,下载HEX文件,运行看结果。

第1篇:PROTEUS电路设计1、打开PROTEUS的ISIS软件,如图1所示。

新建电路图文件,将文件保存到E:\projectio (新建文件夹projectio)下面,文件基本名为io,扩展名默认。

选择元图1 ISIS窗口图2、在component mode模式下单击选择元件按钮P,打开元件选择对话框,如图2所示。

图2 元件选择窗口在元件选择对话框的keywords窗口中输入元件关键字可换搜索元件,找到元件后,双击元件则可选中元件,添加元件到图3的device列表栏。

在这里依次添加元件单片机80C51、电阻RES、电容CAP、按键BUTTON、晶振CRYSTAL、发光二极管LED-RED,如图3所示。

图3 添加元件的device列表栏3、选择devices元件列表中的元件放到工作窗口,注意放置在工作窗口合适的位置,在元件放置时可对元件进行移动、旋转等操作;如图4所示。

电源(POWER)与地(GROUND):(右键-放置-终端里选)。

图4 放置元件图4、连接导线,如图5所示。

连接后存盘。

图5 连接元件图5、在Keil软件中设计软件程序,形成HEX文件(具体过程见第2篇Keil软件编程)。

保存软件项目到电路文件相同的文件夹E:\projectio下。

6、在PROTEUS电路图中,单击单片机80C51芯片,选中,再次单击打开单片机80C51的属性对话框,在属性对话框中的program file框中选择下载到80C51芯片中的程序。

这里是同一个文件夹下面的shili.hex文件。

如图6所示。

图6 下载程序到单片机7、单击仿真运行按钮play,运行程序。

实验三基于QuartusII的流水灯设计仿真

实验收获与体会

理论与实践相结合

通过本次实验,我们将数字电路设计与FPGA应用开发的理论知识与实践相结合,加深了对理论知识的理解,提高了 实际操作能力。

团队合作的重要性

在实验过程中,我们小组成员之间进行了充分的讨论和交流,共同解决问题。这使我们深刻体会到团队合作在解决问 题中的重要性。

不断探索与创新

03 通过设计实现流水灯,培养数字电路设计能力。

实验背景

FPGA(现场可编程门阵列)是一种可编artus II是Altera公司推出的一款FPGA开发软件,提供了完整的FPGA设计流程, 包括设计输入、综合、布局布线、仿真和下载等。

Verilog是一种硬件描述语言,用于描述数字电路的行为和结构,广泛应用于FPGA 设计和ASIC设计领域。

高度集成

Quartus II软件集成了设计、编译、仿真和编程等所有必要 的工具,方便用户进行FPGA开发。

高效编译

Quartus II软件采用了高效的编译算法,能够快速将设计转 换为FPGA可执行的配置文件。

灵活设计

Quartus II软件支持多种硬件描述语言,如VHDL和Verilog, 以及多种设计约束格式,方便用户进行灵活的设计。

03 流水灯设计原理

流水灯简介

01

流水灯是一种常见的LED显示设 备,通过控制LED灯的亮灭顺序 和时间间隔,实现动态的视觉效 果。

02

流水灯通常由多个LED灯珠组成 ,按照一定的顺序排列在一条线 上,通过控制每个LED灯的亮灭 状态,形成连续的视觉效果。

流水灯工作原理

流水灯的工作原理主要是通过控 制每个LED灯的亮灭状态和时间 间隔,实现动态的视觉效果。

控制每个LED灯的亮灭状态通常 是通过微控制器或数字逻辑电路 实现的,时间间隔则通过程序控

实验三基于QaurtusII的流水灯设计仿真

实验内容和目标

加深对数字电路和FPGA原理的理解; 提高分析和解决问题的能力。

02

QuartusII软件简介

QuartusII软件概述

01

Quartus II是Intel公司推出的一款综合性FPGA/CPLD开发软 件

02

支持原理图、VHDL、Verilog等多种设计输入形式

掌握VHDL语言的编程方法

VHDL是一种硬件描述语言,用于描述数字电路和系统的结构和行为。本实验将通过编写 VHDL程序来实现流水灯的设计,帮助学生掌握VHDL语言的编程方法和技巧。

加深对数字电路和FPGA原理的理解

通过本实验的实践操作,学生可以更加深入地理解数字电路和FPGA的原理和工作方式, 提高分析和解决问题的能力。

时序控制

流水灯的时序控制是关键,通过设定一定的时间间隔,控制每个LED灯的亮灭 状态,从而实现灯光的流动。这通常通过微控制器或FPGA等可编程逻辑器件实 现。

数字电路基础

流水灯的设计涉及到数字电路的基本知识,如逻辑门、触发器、 计数器等。这些电路元件用于实现LED灯的驱动和控制逻辑。

硬件描述语言(HDL)实现

03

Project"添加源文件,包括VHDL或Verilog代码文件。

编译工程并生成仿真波形

01

在QuartusII软件中,选择"Processing"->"Start"->"Start Analysis & Synthesis"开始编译工程。

02

编译完成后,选择"Tools"->"RTL Viewer"可以查看RTL级 电路图。

多功能流水灯实验报告

多功能流水灯实验报告第一篇:多功能流水灯实验报告课程设计报告设计课题:多功能流水灯专业班级:学生姓名:指导教师:设计时间:题目多功能流水灯一、课程设计目的1、掌握数字系统的设计方法和测试方法。

二、课程设计题目(问题)描述和要求设计一个四模式三路彩灯(红、绿、黄三种颜色)显示系统。

该系统的显示模式由外部输入Z、Y控制,要求开机自动置入初态后便按规定模式循环运行。

设各路彩灯均为8个(红灯序号为r1-r8,绿灯序号为g1-g8,黄灯序号为y1-y8),各模式规定如下: XY=00时,系统的显示模式在以下六个节拍间循环:第一节拍,依次点亮奇号红灯(r1亮→r1、r3亮→r1、r3、r5亮→r1、r3、r5、r7亮),其余灯均灭。

第二节拍,依次点亮偶号红灯,其余灯均灭。

第三节拍,依次点亮奇号绿灯,其余灯均灭。

第四节拍,依次点亮偶号绿灯,其余灯均灭。

第五节拍,依次点亮奇号黄灯,其余灯均灭。

第六节拍,依次点亮偶号黄灯,其余灯均灭。

XY=01时,系统的显示在第一、二节拍间循环。

XY=10时,系统的显示在第三、四节拍间循环。

XY=11时,系统的显示在第五、六节拍间循环。

三、系统分析与设计根据课程设计题目问题描述和要求,完成:主要器件:绘制电路原理图:确定选用的元件及其封装形式,完善电路。

原理图设计过程:进行电子电路设计时,首先要有一个设计方案,而将电路设计方案表达出来的最好方法就是画出清晰、正确的电路原理图。

根据设计需要选择出元器件,并把所选用的元器件和相互之间的连接关系明确地列出,直观地表达出设计概念。

电路原理图的基本组成是电子元器件符号和连接导线,电子元器件符号包含了该元器件的功能,连接导线则包含了元器件的电气连接信息,所以电路原理图设计的质量好坏直接影响到PCB印制电路板的设计质量。

绘制原理图的两大原则:首先应该保证整个电路原理图的连线正确,信号流向清晰,便于阅读分析和修改;其次应该做到元器件的整体布局合理、美观、实用。

FPGA入门系列实验教程——流水灯

FPGA入门系列实验教程——LED流水灯1.实验任务让实验板上的8个LED实现流水灯的功能。

通过这个实验,进一步掌握采用计数与判断的方式来实现分频的Verilog HDL的编程方法以及移位运算符的使用。

2.实验环境硬件实验环境为艾米电子工作室型号EP2C8Q208C8增强版开发套件。

软件实验环境为Quartus II8.1开发软件。

3.实验原理流水灯,顾名思义就是让LED象水一样的点亮。

如果把流水做慢动作播放,可以想象到其实就是移动,即:把水块不断地向同一方向移动,而原来的水块保持不动,就形成了流水。

同样,如果使得最左边的灯先亮;然后,通过移位,在其右侧的灯,由左向右依次点亮,而已经亮的灯又不灭,便形成了向右的流水灯。

初始状态时,8个灯都不亮。

每来一个时钟脉冲CLK,计数器就加1。

每当判断出计数器中的数值达到25000000时,就会点亮一个灯,并进行移位。

FPGA输出的数据就应该首先是10000000,隔1秒钟变成11000000……一直变化到11111111,这样,依次点亮所有的灯,就形成了流水灯。

而当8个灯都点亮时,需要一个操作使得所有的灯恢复为初始状态,即:灯都不亮。

然后,再一次流水即可。

如果是右移位,就出现向右流水的现象;反之,向左流水。

4.实验程序module ledwater(clk,led);//模块名及端口参数output[7:0]led;//输出端口定义input clk;//输入端口定义,50M时钟reg[8:0]led_out;//变量led_out定义为寄存器型reg[8:0]led_out1;//变量led_out1定义为寄存器型reg[25:0]buffer;//中间变量buffer定义为寄存器型always@(posedge clk)beginbuffer=buffer+1;if(buffer==26'd2*******)//判别buffer数值为25000000时,做输出处理beginled_out=led_out<<1;//led向左移位,空闲位自动添0补位if(led_out==9'b000000000)led_out=9'b111111111;led_out1=~led_out;//取反输出endendassign led=led_out1[7:0];endmodule5.实验步骤(1)建立新工程项目:打开Quartus II软件,进入集成开发环境,点击File→New project wizard建立一个工程项目ledwater。

实验三_基于Quartus_II的流水灯设计仿真(新).

2

三、实验原理

………………………………

流水灯是一种效果灯光,它通过按固定的规律将LED 点亮或熄灭

上图给出了一种简单的流水灯状态变化示意图,用逻 辑电路控制8个LED灯,始终保持7亮1暗,在脉冲信 号CP的推动下循环流动;

将灯亮用1表示,灯灭用0表示;

3

1.二进制译码器结合计数器实现

QuartusII软件可到实验中心网站上下载,要注意它 的破解步骤。

10

一、准备

1、使用QuartusII软件之前,请确保软件已正常破解

若启动QuartusII时看到如下注册请求界面,则说明软件尚 未注册许可,需要进行认证后才能正常使用:

11

在开始菜单\运行中输入命令:cmd,打开MS-DOS命令窗; 在命令窗中输入: ipconfig/all,回车后即列出本机物理地

(3)选择仿真器和综合器类型(默认“None”为选 择QuartusII自带的);

(4)选择目标芯片(开发板上的芯片类型); (5)工具设置,默认为都不选择,可直接跳过; (6)完成创建。 工程建立后,若需要新增设计文件,可以通过菜单

项Project /Add_Remove……在工程中添加新建立的 设计文件,也可以删除不需要的设计文件。编译时 将按此选项卡中列出的文件处理。

完成画线连接操作

鼠标放到端点处,会自动变为小十字形,按下左键 拖动到目标处,释放后即完成本次画线操作

若要画折线,在转折处单击一次左键,继续拖动即 可;

为INPUT、OUTPUT端口命名:双击该输出端口, 在弹出的窗口中输入名称即可。

28

完整的计数译码8位流水灯参考逻辑图

29

四、全程编译

流水灯(电路和汇编)-Proteus和Keil仿真演示实例

示例要求:在80C51单片机的P2 口连接8个发光二极管指示灯,编程实现流水灯的控制,轮流点亮指示灯。

在KEIL 51中编程序,形成HEX文件;在PROTEUS中设计硬件,下载HEX文件,运行看结果。

第1 篇: PROTEUS电路设计1、打开PROTEUS的ISIS软件,如图1所示。

新建电路图文件,将文件保存到E:\projectio (新建文件夹projectio)下面,文件基本名为io,扩展名默认。

图1 ISIS窗口图2、在component mode模式下单击选择元件按钮P,打开元件选择对话框,如图2所示。

图2元件选择窗口Root sheet 1IF在元件选择对话框的 keywords 窗口中输入元件关键字可换搜索元件,找到元件后,双击元件则可选中元 件,添加元件到图3的device 列表栏。

在这里依次添加元件单片机 80C51、电阻RES 、电容CAP 、按键BUTTON 、晶振CRYSTAL 、发光二极管 LED-RED ,如图3所示。

3、选择devices 元件列表中的元件放到工作窗口, 注意放置在工作窗口合适的位置,在元件放置时可对元件进4所示。

电源(POWER )与地(GROUND ):(右键-放置-终端里选)。

Fil* JJi ** Edit Ts< Vetixn 肆紛h 命af” U 俺峙 Litrsrv 1 也Svct K*lp国W;踞輕丨==■■-!□] x|行移动、旋转等操作;如图 图3添加元件的device 列表栏配輔證 S I?) K I S E I EIF記汨益器心 呼Tn •冒l-H-一 -4、连接导线,如图5所示。

连接后存盘。

Pile V] ew Edit l^els Dess EHScfirct Betur Latr KT ?" IflEwlute Svster M<lp|D I ^S 虚id 旨3|[囱書]舟 命迫旦塹口|]叭c x %e.^z z■ ■狀 ]ls tnsi iasH.^10^71^连接元件图5、 在Keil 软件中设计软件程序,形成 HEX 文件(具体过程见第 2篇Keil 软件编程)。

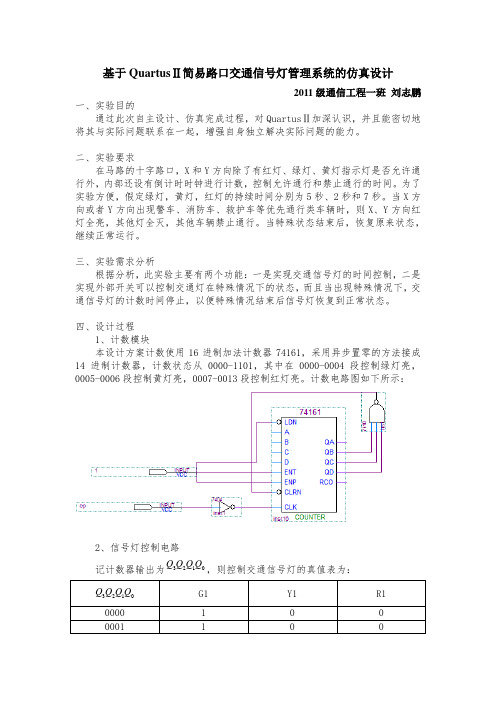

基于QuartusⅡ简易路口交通信号灯管理系统的仿真设计

基于QuartusⅡ简易路口交通信号灯管理系统的仿真设计2011级通信工程一班刘志鹏一、实验目的通过此次自主设计、仿真完成过程,对QuartusⅡ加深认识,并且能密切地将其与实际问题联系在一起,增强自身独立解决实际问题的能力。

二、实验要求在马路的十字路口,X和Y方向除了有红灯、绿灯、黄灯指示灯是否允许通行外,内部还设有倒计时时钟进行计数,控制允许通行和禁止通行的时间。

为了实验方便,假定绿灯,黄灯,红灯的持续时间分别为5秒、2秒和7秒。

当X 方向或者Y方向出现警车、消防车、救护车等优先通行类车辆时,则X、Y方向红灯全亮,其他灯全灭,其他车辆禁止通行。

当特殊状态结束后,恢复原来状态,继续正常运行。

三、实验需求分析根据分析,此实验主要有两个功能:一是实现交通信号灯的时间控制,二是实现外部开关可以控制交通灯在特殊情况下的状态,而且当出现特殊情况下,交通信号灯的计数时间停止,以便特殊情况结束后信号灯恢复到正常状态。

四、设计过程1、计数模块本设计方案计数使用16进制加法计数器74161,采用异步置零的方法接成14进制计数器,计数状态从0000-1101,其中在0000-0004段控制绿灯亮,0005-0006段控制黄灯亮,0007-0013段控制红灯亮。

计数电路图如下所示:2、信号灯控制电路 记计数器输出为123Q Q Q Q ,则控制交通信号灯的真值表为:123Q Q Q QG1 Y1 R1 0000 1 0 0 0001 1 0 0 0010 1 0 0 0011 1 0 0 0100 1 0 0 0101 0 1 0 0110 0 1 0 0111 0 0 1 1000 0 0 1 1001 0 0 1 101011011 0 0 1 1100 0 0 1 1101 01经过整理化简状态方程,得到:230123Q Q Q Q Q Q G +=01230123Q Q Q Q Q Q Q Q Y +=01233Q Q Q Q Q R +=使用 Quartus Ⅱ仿真控制电路,得到图如下:同理可得G2、Y2、R2的真值表,状态方程和电路连接情况略,计算方式与上面类似。

(完整word版)基于单片机仿真软件proteus的流水灯实验报告

单片机原理》实验报告题目:流水灯设计姓名:刘伟学号:1042157110专业:10 计科特色班院系:信息工程学院指导老师:史先桂完成时间:2014 年 4 月19 日安徽新华学院教务处制一、实验目的1、熟练掌握单片机仿真软件proteus 使用方法和注意事项。

2、了解简单单片机应用系统的设计方法。

3、帮助学生养成良好实验习惯。

二、实验内容单片机仿真软件proteus 上实现8个发光LED “流水”的现象,实现两个流水灯情况:1、先奇数灯亮,再偶数灯亮;2、实现流水灯从两边向中间亮,再从中间到两边亮。

并通过编写程序控制流水现象。

三、实验说明依照实验的硬件电路原理,在单片机仿真软件proteus 上进行硬件电路的模拟,然后进行实验。

在发光二极管两次点亮的间隔中加延时程序,让每次点亮停留一段时间,像这样人眼就可以看到“流水” 的现象。

四、实验环境硬件:pc 机;软件:单片机仿真软件proteus。

五、实验原理图六、实验参考程序#include<reg52.h>#include<intrins.h>void delay_ms(int n){int i,j;for(i=0;i<n;i++)for(j=0;j<110;j++);void main(){int i, num; unsigned char p1; unsigned char p0, p; while(1) {for(i=0; i<3; i++) // 间隔500ms 先奇数亮再偶数亮,循环三次{P1=0xaa; P0=p1; delay_ms(500);// 延时n 毫秒P1=0x55;P0=p1; delay_ms(500);}p1= 0xfe;num=3;while(num-- > 0) // 一个灯上下循环三?{ for(i=0; i<8; i++) {P0=p1; delay_ms(100); p1=_cror_(p1,1);}}//两个分别从两边往中间流动三?p1= 0xfe;p0= 0x7f;num=3;while(num-- > 0){for(i=0; i<4; i++) //让LED 灯从两边向中间点亮{p1=_crol_(p1,1);p0=_cror_(p0,1); p=p1&p0;delay_ms(100);P1=p;P0=p;// p1= 0xef;p0= 0xf7;num=3;while(num-- > 0){for(i=0; i<4; i++){p1=_crol_(p1,1);p0=_cror_(p0,1); p=p1&p0; delay_ms(100);P1=p;P0=p;}}//8 个全部闪烁3 次? num=3;while(num-- > 0){p1=0;delay_ms(500);p1=1; delay_ms(500);}break;}}模拟演示图:1)模拟单片机的偶数灯亮2)模拟单片机的奇数灯亮3)模拟单片机流水灯从两边到中间亮4)模拟单片机流水灯从中间到两边亮。

QUARTUSII软件开放性实验报告材料

开放性实验报告专业:电子信息工程班级: *电信*班姓名:学号:指导老师:实验一:流水灯一.实验内容利用QUARTUSII软件,构建NIOSII软核系统,编写程序,实现实验箱上LED灯的流水功能。

二.实验原理通过提前设定NIOSII软核处理器的相关寄存器,控制led 的IO 口的高低电平输出及响应间隔时间,从而改变LED的亮灭并达到流水灯效果。

三.实验步骤1.硬件设计(1).构建NIOSII软核NIOSII软核处理器包括cpu,sdram控制器,串行flash控制器,jtag_uart,sysid,pio端口。

(2).PLL模块的构建实验箱的板载有源晶振频率为50MHZ,NIOSII及SDRAM需要100MHZ 的时钟源,因此需要用PLL模块进行倍频。

PLL模块的配置如图所示:输入时钟频率为50MHZ输出时钟c0为输入时钟的2倍频输出时钟c1为输入时钟的2倍频,相位偏移-75度,为SDRAM 提供工作时钟PLL模块:(3).系统连线及引脚分配qsf文件中的引脚分配:set_location_assignment PIN_AF21 -to sdram_addr[0] set_location_assignment PIN_AE20 -to sdram_addr[1] set_location_assignment PIN_AF20 -to sdram_addr[2] set_location_assignment PIN_AE19 -to sdram_addr[3] set_location_assignment PIN_B20 -to sdram_addr[4] set_location_assignment PIN_A21 -to sdram_addr[5] set_location_assignment PIN_B21 -to sdram_addr[6] set_location_assignment PIN_A22 -to sdram_addr[7] set_location_assignment PIN_B22 -to sdram_addr[8] set_location_assignment PIN_A23 -to sdram_addr[9] set_location_assignment PIN_AE21 -to sdram_addr[10] set_location_assignment PIN_B23 -to sdram_addr[11] set_location_assignment PIN_B24 -to sdram_addr[12] set_location_assignment PIN_AE22 -to sdram_ba[0]set_location_assignment PIN_AF22 -to sdram_ba[1] set_location_assignment PIN_AE24 -to sdram_cas_n set_location_assignment PIN_B25 -to sdram_ckeset_location_assignment PIN_AF23 -to sdram_cs_n set_location_assignment PIN_AD25 -to sdram_dq[0] set_location_assignment PIN_AC25 -to sdram_dq[1] set_location_assignment PIN_AC26 -to sdram_dq[2] set_location_assignment PIN_AB25 -to sdram_dq[3] set_location_assignment PIN_AB26 -to sdram_dq[4] set_location_assignment PIN_AA25 -to sdram_dq[5] set_location_assignment PIN_AA26 -to sdram_dq[6] set_location_assignment PIN_Y25 -to sdram_dq[7] set_location_assignment PIN_W26 -to sdram_dq[8] set_location_assignment PIN_V25 -to sdram_dq[9] set_location_assignment PIN_V26 -to sdram_dq[10] set_location_assignment PIN_U25 -to sdram_dq[11] set_location_assignment PIN_U26 -to sdram_dq[12] set_location_assignment PIN_T25 -to sdram_dq[13] set_location_assignment PIN_R25 -to sdram_dq[14] set_location_assignment PIN_P24 -to sdram_dq[15] set_location_assignment PIN_N24 -to sdram_dq[16] set_location_assignment PIN_M25 -to sdram_dq[17] set_location_assignment PIN_L25 -to sdram_dq[18] set_location_assignment PIN_K26 -to sdram_dq[19] set_location_assignment PIN_K25 -to sdram_dq[20] set_location_assignment PIN_J26 -to sdram_dq[21] set_location_assignment PIN_J25 -to sdram_dq[22] set_location_assignment PIN_H26 -to sdram_dq[23] set_location_assignment PIN_G25 -to sdram_dq[24] set_location_assignment PIN_F26 -to sdram_dq[25] set_location_assignment PIN_F25 -to sdram_dq[26] set_location_assignment PIN_E26 -to sdram_dq[27] set_location_assignment PIN_E25 -to sdram_dq[28] set_location_assignment PIN_D26 -to sdram_dq[29] set_location_assignment PIN_D25 -to sdram_dq[30] set_location_assignment PIN_C25 -to sdram_dq[31] set_location_assignment PIN_Y26 -to sdram_dqm[0] set_location_assignment PIN_W25 -to sdram_dqm[1] set_location_assignment PIN_H25 -to sdram_dqm[2] set_location_assignment PIN_G26 -to sdram_dqm[3] set_location_assignment PIN_AE23 -to sdram_ras_n set_location_assignment PIN_AE25 -to sdram_we_n set_location_assignment PIN_F21 -to clk_sdram2.软件设计system.h文件中关于PIO_LED的宏定义#define PIO_LED_NAME "/dev/pio_LED"#define PIO_LED_TYPE "altera_avalon_pio"#define PIO_LED_BASE 0x00001800#define PIO_LED_SPAN 16#define PIO_LED_DO_TEST_BENCH_WIRING 0#define PIO_LED_DRIVEN_SIM_VALUE 0#define PIO_LED_HAS_TRI 0#define PIO_LED_HAS_OUT 1#define PIO_LED_HAS_IN 0#define PIO_LED_CAPTURE 0#define PIO_LED_DATA_WIDTH 8#define PIO_LED_RESET_VALUE 0#define PIO_LED_EDGE_TYPE "NONE"#define PIO_LED_IRQ_TYPE "NONE"#define PIO_LED_BIT_CLEARING_EDGE_REGISTER 0#define PIO_LED_BIT_MODIFYING_OUTPUT_REGISTER 0#define PIO_LED_FREQ 100000000#define ALT_MODULE_CLASS_pio_LED altera_avalon_pio利用system.h文件编写sopc.h,通过操作结构体PIO_STR完成对PIO_寄存器的操作。

实验3 流水灯原理图设计

实验3 流水灯原理图设计

实验目的

1.掌握在Quartus II利用原理图设计时序电路的方法;

2.复习原理图文件建立、编辑、编译、保存的操作,复习软件仿真的方法。

实验原理

流水灯的原理图为:

输入端为时钟端clk,输出端为Q1、Q2和Q3。

实验步骤

(1)新建一个原理图文件,文件名为lsd.bdf,保存在文件夹lsd中。

(2)在图形文件中添加元件,在路径.. \altera\quartus90\libraries\primitives\logic中,调入或非门元件nor2,在路径.. \altera\quartus90\libraries\primitives\others调入触发器元件dff。

添加输入和输出端口,连接好元件。

(3)建立工程lsd,工程的顶层文件为lsd.bdf,工程包含文件lsd.bdf,目标芯片为EP1C6Q240C8。

(4)编译。

(4)建立波形文件lsd.wvf,调入输入信号clk和输出

信号Q1、Q2、Q3;利用按钮输入时钟波形,时钟的周期设置为20~30ns。

(5)仿真,画出波形图,要标明时间刻度。

实验三 基于Quartus II流水灯的设计仿真共39页

31、只有永远躺在泥坑里的人,才不会再掉进坑里。——黑格尔 32、希望的灯一旦熄灭,生活刹那间变成了一片黑暗。——普列姆昌德 33、希望是人生的乳母。——科策布 34、形成天才的决定因素应该是勤奋。——郭沫若 35、学到很多东西的诀窍,就是一下子不要学很多。——洛克

实验三 基于Quartus II流水灯的设计 仿真

11、用道德的示范来造就一个人,显然比用法律来约束他更有价值。—— 希腊

12、法律是无私的,对谁都一视同仁。在每件事上,她都不徇私情。许的事 情。——弗劳德

14、法律是为了保护无辜而制定的。——爱略特 15、像房子一样,法律和法律都是相互依存的。——伯克

fpga流水灯实验报告

竭诚为您提供优质文档/双击可除fpga流水灯实验报告篇一:vhdl流水灯课程设计报告院系:姓名:学号:课程设计名称:指导老师:时间:摘要VhDL的特点应用VhDL进行系统设计,有以下几方面的特点。

(一)功能强大VhDL具有功能强大的语言结构。

它可以用明确的代码描述复杂的控制逻辑设计。

并且具有多层次的设计描述功能,支持设计库和可重复使用的元件生成。

VhDL是一种设计、仿真和综合的标准硬件描述语言。

(二)可移植性VhDL语言是一个标准语言,其设计描述可以为不同的eDA工具支持。

它可以从一个仿真工具移植到另一个仿真工具,从一个综合工具移植到另一个综合工具,从一个工作平台移植到另一个工作平台。

此外,通过更换库再重新综合很容易移植为AsIc设计。

(三)独立性VhDL的硬件描述与具体的工艺技术和硬件结构无关。

设计者可以不懂硬件的结构,也不必管最终设计实现的目标器件是什么,而进行独立的设计。

程序设计的硬件目标器件有广阔的选择范围,可以是各系列的cpLD、FpgA及各种门阵列器件。

(四)可操作性由于VhDL具有类属描述语句和子程序调用等功能,对于已完成的设计,在不改变源程序的条件下,只需改变端口类属参量或函数,就能轻易地改变设计的规模和结构。

(五)灵活性VhDL最初是作为一种仿真标准格式出现的,有着丰富的仿真语句和库函数。

使其在任何大系统的设计中,随时可对设计进行仿真模拟。

所以,即使在远离门级的高层次(即使设计尚未完成时),设计者就能够对整个工程设计的结构和功能的可行性进行查验,并做出决策。

VhDL的设计结构VhDL描述数字电路系统设计的行为、功能、输入和输出。

它在语法上与现代编程语言相似,但包含了许多与硬件有特殊关系的结构。

VhDL将一个设计称为一个实体entity(元件、电路或者系统),并且将它分成外部的可见部分(实体名、连接)和内部的隐藏部分(实体算法、实现)。

当定义了一个设计的实体之后,其他实体可以利用该实体,也可以开发一个实体库。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

该步骤可单击“Next”直接跳过

20

5、完成!

工程创建完毕,在工程管理器界 面出现所选用的器件系列、器件 名及工程文件名“CycloneII”;

单击“Finish”,完成工程创建

21

综上所述,创建工程时的几个步骤如下

(1)指定工程所在的工作库文件夹、工程名及设计 实体名;

(2)将设计文件加入工程中,若无设计文件直接跳 过;

四、实验内容和要求

1.设计一个计数译码型流水灯的逻辑电路并完成仿真测试, 电路采用8灯结构,8个灯按7亮1暗的规律循环流动,步骤要求 如下:

(1)在Quartus II软件环境下,采用原理图方式,完成逻辑电 路设计。

(2)启动全程编译,若存在严重的逻辑问题编译时会报错,修 改直至电路无误;

址physiccal address; 用写字板或记事本打开本机QuartusII软件实际安装目录下

的license.dat文件。如C:\Altera\ license.dat 使用“全部替换”功能将其中的所有的Host ID替换为本机

实际的物理地址即完成破解。 (替换时需注意不能插入空格并去掉符号“-” )

34

3、设置仿真时间长度

默认为1us,这里将其设置为100us

35

4、设置仿真时间周期

默认为10ns,由于竞争冒险的存 在,在仿真时信号波形和大量毛 刺混叠在一起,影响仿真结果 因此,这里设置为500ns

36

5、编辑输入端口信号

窗口缩放(左键放 大,右键缩小)

已编辑好的时钟波形

选中CP后,点击 此符号,直接编 辑周期脉冲信号

选中后,右键放大,左键缩小

32

1、建立波形矢量文件(左图),并进行保存; 2、添加引脚节点

33

添加引脚节点(续)

在Filter下选择“Pins: unassigned”,再单击 “List”,列出引脚端口

”

在Nodes Found下方的列 表下选择所列出 的端口,将其拖 放到波形文件的 引脚编辑区

4、窗口缩放工具 选中后,右键放大,左键缩小

5、窗口全屏显示,按“ESC”退出

其余工具按钮不常用, 这里不介绍

注意:使用窗口缩放工具按钮后,请切换回画线及选择

工具按钮,才能对绘图进行编辑。

27

从符号库中调出JKFF、74138、VCC、GND、 INPUT、OUTPUT等符号/端口,排放整齐;

6

计数译码型流水灯参考设计 1、异步模八计数器设计(在QuartusII中画图)

由JK→T’构成异步模八计数器为74LS138产生连续变化的 地址信号;

f1为连续脉冲CP,为便于视觉观察,输入频率一般应为110Hz;

Q2、Q1、Q0分别接到74138的地址端A2、A1、A0;

7

2、译码器应用(在QuartusII中进行图形设计)

设置完毕后单击“Next”

18

3、器件选择

选择FPGA器件所 属系列

选择FPGA器件型号

设置完毕后单击“Next”

实验开发板所使用的器件为ALtera公司Cyclone系列(Family) 的EP1C3T144C8(Avaliable devices)

19

4、EDA 工具设置

选择第三方EDA工具(如 ModelSim、Synplify等) 这里不需要,都不打勾

37

6、启动时序仿真

低电平看做灯灭, 高电平看做灯亮。

窄尖峰为冒险引起, 不影响逻辑功能。

分析波形可见,与74LS138功能真值表一致,结果正确 38

完成上一个仿真后,请自行设计移存型流水灯,并进 行仿真验证。

希望大家通过本次实验,上手并熟练掌握QuartusII 的使用。

上图中,选择第二项:Block Diagram/Schematic File, 点击ok后即得如下界面:

工程文件名

绘图辅助工具

原理图编辑区

24

3、调用参数化元件(内置元件)

在绘图区双击鼠标左键,即弹出添加元件的窗口

点击“+”号可展 开查看查看库中 所有的元件/端口

在此输入已知的 元件名,可以快 速地调出元件/端 口并预览

双击错误信息,可以定位到错误所在处,改正后再次进 行编译直至排除所有错误;

编译成功后,会弹出编译报告,显示相关编译信息。

31

五、时序仿真

工程编译完成后,设计结果是否满足设计要求,可 以通过时序仿真来分析;

时序仿真主要包含如下的设置步骤:

打开波形编辑器;

顺 设置仿真时间区域;

Q2、Q1、Q0接三个JK触发器的Q端输出,接收 前端计数器输出的地址信号;

Y0、Y1、……Y7与实验板上的LED灯进行连接 (在QuartusII下进行引脚锁定),观察流水现象;

8

五、实验步骤

1. 通过QuartusII建立一个新项目; 2. 建立项目时选Cyclone系列(family)的目标器件

(3)新建波形激励文件并配置测试端口,合理设置仿真时间长 度及仿真时钟周期;

(4)启动仿真。仿真运行完毕后会生成报告波形。分析仿真波 形的特征,印证设计目标,是否达到预期设计。

2.设计一个移存型流水灯的逻辑电路并完成仿真测试,电路 采用8灯结构,8个灯按1亮7暗的规律循环流动。

设计的步骤要求同上。

14

3、常用工具栏

扩展控制按钮

编译报告

若QuartusII界面上 To reset views:

一些默认的按钮被 关闭,影响使用,

1.Tools Customize Toolbars Reset All

可按右边的操作步 2.Restart Quartus II

骤来复原

15

二、在QuartusII6.0环境下建立工程 工程创建时的准备工作

保存文件并关闭,重启Quartus,注册请求界面已消失。

12

若注册请求界 面还未消失

请按左图选择

在下图中重设 文件指向路径

2、Quartus II 6.0主界面操作环境

1、Project Navigator(工程管理器) 2、Status window(状态窗口)

2、Message window(信息窗口)

2.移位寄存器构成顺序脉冲发生器实现

移位寄存器构成顺序脉冲发生器可用来控制LED灯按 照设计的顺序节拍进行变化,从而实现流水效果。

74LS194是双向4位移位寄存器,为了控制8个灯,可 以将2片74LS194级联后构成8位顺序脉冲发生器

Q0 Q1 Q2 Q3 M1

Q0 Q1 Q2 Q3 M1

QuartusII软件可到实验中心网站上下载,要注意它 的破解步骤。

10

一、准备

1、使用QuartusII软件之前,请确保软件已正常破解

若启动QuartusII时看到如下注册请求界面,则说明软件尚 未注册许可,需要进行认证后才能正常使用:

11

在开始菜单\运行中输入命令:cmd,打开MS-DOS命令窗; 在命令窗中输入: ipconfig/all,回车后即列出本机物理地

22

三、在QuartusII6.0工程下建立设计文件

1、在File菜单下点击“New”,即弹出新建文件窗口

选此后单击OK

QuartusII支持原理图输入、VHDL语言输入等多种设计输入方式, 后面以原理图输入(Block Diagram/Schematic File)为例介绍23

2、建立原理图设计文件

实验三:基于QuartusII原理 图的流水灯设计及仿真

一、实验目的

掌握EDA集成工具软件Quartus II的使用; 了解基于PLD的EDA设计流程; 熟悉使用QuartusII原理图方式进行数字逻辑电路设计

的方法; 熟练掌握使用QuartusII对逻辑电路进行仿真。

二、实验设备

计算机

2

三、实验原理

………………………………

流水灯是一种效果灯光,它通过按固定的规律将LED 点亮或熄灭

上图给出了一种简单的流水灯状态变化示意图,用逻 辑电路控制8个LED灯,始终保持7亮1暗,在脉冲信 号CP的推动下循环流动;

将灯亮用1表示,灯灭用0表示;

3

1.二进制译码器结合计数器实现

使用八进制计数器产生74LS138地址端所需的8个地址 信号,将计数输出Q0、Q1、Q2分别接入74LS138的 A0、A1、A2,为计数器提供低频连续脉冲CP,即可 在74LS138的8个输出端获得流水灯的连续状态输出

Q0 A0

CP

8进制 Q1 A1 3-8线

计数器 Q2 A2 译码器

八进制计数器可以通过将3个JK或D触发器 先组成T’触发器,然后再级联为异步计数器

在下拉菜单“Processing” 中选择“Start Compilation”,启动全程编 译

编译完成后的 信息报告窗口

30

关于全程编译

启动全程编译:

选择Processing/Start Compilation,自动完成分析、排错、 综合、适配、汇编及时序分析的全过程。

编译过程中,错误信息通过下方的信息栏指示(红色字 体)。

(3)选择仿真器和综合器类型(默认“None”为选 择QuartusII自带的);

(4)选择目标芯片(开发板上的芯片类型); (5)工具设置,默认为都不选择,可直接跳过; (6)完成创建。 工程建立后,若需要新增设计文件,可以通过菜单

项Project /Add_Remove……在工程中添加新建立的 设计文件,也可以删除不需要的设计文件。编译时 将按此选项卡中列出的文件处理。

QuartusII通过“工程(Project)”来管理设计文 件,必须为此工程创建一个放置与此工程相关的 所有设计文件的文件夹;