FPGA设计与应用 分频器设计实验

FPGA实验设计报告—广东技术师范学院

实验报告课程名称:FPGA设计及应用实验项目:FPGA设计实验时间:2014.12.8-2014.12.31实验班级:12应用师3班总份数:共 5 份指导教师:李豪彦电子与信息学院工业中心504 实验室二〇〇四年十二月十七日广东技术师范学院实验报告学院: 电信学院 专业: 应用电子技术教育 班级: 12应用师3班 成绩: 姓名: 张文斌 学号: 2012045344209 组别:组员:实验地点: 工业中心实验日期:指导教师签名:实验 (一) 项目名称: D 分 频 器设计一、实验目的1.学习分频器的设计,进一步了解、熟悉和掌握FPGA 开发软件Quartus II 的使用方法2.学习Verilog HDL 和VHDL 的编程方法二、实验内容编写一个分频器的Verilog 代码和VHDL 代码并仿真。

三、实验原理在数字电路中, 时钟信号的分频是很常见的电路。

分频器除了可以对时钟信号频率做除以二的计算外,分频器同时很类似涟波计数器。

涟波计数器是计数器的一种,它属于异步设计。

因为触发器并非皆由同一个时钟信号同步操作,所以它非常节省电路面积。

本实验要设一个带选择的分频时钟D[7:0]用于选择是几分频。

D 分频器设原理框图如图1所示:图1.D 分频器原理框图预习情况操作情况 考勤情况 数据处理情况四、实验步骤1.新建工程,取名为DVF,如下图2所示。

图2 新建工程DVF2.新建VHDL设计文件,选择“File|New ”,在New 对话框中选择Device Design Files下的VHDL File,单击OK,完成新建设计文件。

3.在新建设计文件中输入VHDL程序。

4.生成“Symbol ”文件,新建“Block Diagram/Schematic File”文件,在文件中添加刚刚生成的“Symbol ”以及输入输出管脚,最后完整的系统顶层模块图如图 3 所示。

图3 DVF 顶层模块图5.保存文件,使用qsf或者tcl 进行管脚分配。

基于FPGA的奇偶分频器的设计与实现

内蒙古科技大学本科生毕业设计说明书(毕业论文)题目:基于FPGA的奇偶分频器的设计与实现学生姓名:学号:专业:电子信息工程班级:电信10-1班指导教师:基于FPGA的奇偶分频器的设计与实现摘要分频器作为一种最基本的数字电路,广泛的应用在各种复杂的逻辑电路设计中,对于FPGA芯片来说,虽然能用自带的锁相环来产生一部分我们所需的频率,但是,用VHDL语言实现分频能从同一时钟较为方便、快捷的生成多个所需要的频率,同时能够实现信号的同步,因此,分频器的应用非常广泛。

本设计应用软件为开发平台,运用VHDL语言编程实现整数的奇偶分频的设计,在本设计中实现了0、2、4、6、8、10、12、14偶数的整数分频器设计和1、3、5、7、9、11、13、15奇数的整数分频器设计。

通过仿真结果,验证了设计的正确性。

关键词:FPGA;分频器;VHDL语言;Quartus ⅡDesign and implementation of FPGA-based parity dividerAbstractDivider as a basic digital circuits, widely used in a variety of complex logic circuit design, the FPGA chip, although able to own a part of our phase-locked loop to produce the desired frequency, but using VHDL language divide from the same clock frequency is more convenient and efficient to generate multiple needs, while able to achieve synchronization signal, and therefore, the divider is widely used.The design of application software development platform, the use of VHDL language programming odd integer divider design, the design is implemented in an even integer divider 0,2,4,6,8,10,12,14 design and 1,3,5,7,9,11,13,15 odd integer divider design. The simulation results verify the correctness of the design.Key words: FPGA; divider; VHDL language;Quartus Ⅱ目录摘要 (I)Abstract...................................................................................................................... I I 第一章绪论. (1)1.1 课题来源 (1)1.2 选题的意义和目的 (2)1.3 课题研究现状 (3)1.4 本文组织结构 (4)第二章EDA技术 (6)2.1 FPGA技术 (6)2.2 Quartus Ⅱ软件简介 (7)2.3 VHDL语言 (8)2.3.1 VHDL简介 (8)2.3.2 VHDL特点 (9)2.3.3 VHDL组成 (10)第三章奇偶分频器设计与仿真 (12)3.1 偶数分频 (12)3.1.1 原理分析 (12)3.1.2 设计与仿真 (12)3.2 奇数分频 (17)3.2.1 原理分析 (17)3.2.2 设计与仿真 (18)第四章系统设计 (23)4.1 设计的任务 (23)4.2 系统设计 (23)4.3 其余模块设计 (27)4.3.1 encoder_12模块 (27)4.3.2 mux21模块 (29)4.3.3 数码管显示驱动模块 (30)第五章下载与测试 (35)5.1 BTYG-EDA实验概述 (35)5.2 BTYG-EDA实验开发系统特点 (35)5.3 引脚分配 (35)5.4 验证 (36)第六章结论与展望 (37)6.1 结论 (37)6.2 展望 (37)参考文献 (39)致谢 (40)第一章绪论1.1课题来源分频器作为数字系统设计中一类重要的电子电路,在数字电路的迅速发展历程中,通常要运用分频器来实现设计中希望获取的时钟频率。

基于FPGA分频器的研究与设计

基于FPGA分频器的设计摘要:分频器是数字系统设计中的基本电路,在复杂数字逻辑电路设计中,根据不同设计的需要,会遇到偶数分频、奇数分频、半整数分频等,有时要求等占空比,也有要求非等占空比。

在同一个设计中有时要求多种形式的分频,通常由计数器或计数器的级联构成各种形式的偶数分频和奇数分频,实现较为简单,但是对半整数分频实现较为困难。

设计师希望有一种比较方便实用的设计方法,根据情况的需要,在实验室就能设计分频器并且可以马上检测使用,只需要更改频率系数而不修改其他器件或是电路板。

因此,本文利用verilog硬件描述语言,通过开发平台,使用FPGA,设计了一种能满足上述情况的通用分频器。

只要在分频器的输入端输入相应的分频系数,就可以得到所需的频率。

关键词:分频器;偶数;奇数;半整数;分频系数;FPGASeparate frequency inverter based on FPGA designAbstract:Points are the frequency of an digital system design, the basic circuit in complex digital logic circuit design, according to different design needs, will meet even points frequency, an odd number of points frequency, half integer points frequency etc, sometimes require 390v, such as the request 390v. In the same design sometimes require multiple forms of points frequency, usually by a counter or counter cascade constitute various forms of the frequency and the odd points even points, to achieve comparatively simple frequency, but half-and-half integer points frequency division frequency realize more difficult. Designers hope to have a more convenient and practical design methods, according to the needs of the laboratory condition, can design points frequency device and can immediately detection using, only need to change frequency coefficients and not modify other device or circuit board. Therefore, this paper use verilog hardware description language, through the development platform, use the FPGA, design a kind of can meet the above situation of practical points frequency device. As long as the frequency of an in points corresponding points input input frequency coefficients, can get frequency required.Keywords: Points, frequency, manometers, Even, Odd, Half an integer, Points frequency coefficients, FPGA目录第一章绪论 (1)1.1 FPGA简介 (1)1.2 选题的意义和目的 (2)1.3 国内外应用现状及研究现状 (3)1.3.1 应用现状 (3)1.3.2 研究现状 (4)1.4 本文组织结构 (5)第二章几类分频器的设计及其分频原理 (7)2.1 偶数倍分频 (7)2.1.1 分频原理 (7)2.1.2 软件简介 (7)2.1.3 软件仿真 (7)2.2 奇数倍分频 (9)2.2.1 分频原理 (9)2.2.2 软件仿真 (10)2.3 半整数分频 (12)2.4 小数分频器 (13)2.4.1 积分分频器 (13)2.4.2 累加器分频 (14)2.4.3 小数分频器的应用 (15)2.5 本章小结 (17)第三章通用分频器的设计 (18)3.1 设计方案 (18)3.1.1 设计方案一 (18)3.1.2 设计方案二 (18)3.2 系统设计 (19)3.2.1 电路工作流程图及部分程序 (20)3.2.2时钟输出流程图及部分程序 (23)3.3 通用分频器的应用 (25)3.3.1 等占空比的奇数分频器 (25)3.3.2 任意占空比的奇、偶数分频 (25)3.3.3 等占空比的偶数分频器 (26)3.3.4 半整数分频器 (26)3.4 本章小结 (26)结论 (27)致谢 (28)参考文献 (29)第一章绪论1.1 FPGA简介FPGA是现场可编程门阵列的简称,是可编程逻辑器件(PLD)问世以来的第四代产品,适合于时序、组合等逻辑电路的应用。

基于CPLD-FPGA的多功能分频器的设计与实现

基于CPLD/FPGA的多功能分频器的设计与实现

引言

分频器在CPLD/FPGA 设计中使用频率比较高,尽管目前大部分设计中采用芯片厂家集成的锁相环资源,但是对于要求奇数倍分频(如3、5 等)、小数倍(如2.5、3.5 等)分频、占空比50%的应用场合却往往不能满足要求。

硬件工程师希望有一种灵活的设计方法,根据需要,在实验室就能设计分频器并马上投

入使用,更改频率时无需改动原器件或电路板,只需重新编程,在数分钟内即可完成。

为此本文基于CPLD/FPGA 用原理图和VHDL 语言混合设计实现了一多功能通用分频器。

分频原理

偶数倍(2N)分频

使用一模N 计数器模块即可实现,即每当模N 计数器上升沿从0 开始计数至N 时,输出时钟进行翻转,同时给计数器一复位信号使之从0 开始重新计数,以此循环即可。

偶数倍分频原理示意图见图1。

奇数倍(2N+1)分频

(1)占空比为X/(2N+1)或(2N+1-X)/(2N+1)分频,用模(2N+1)计数器模块可以实现。

取0 至2N 之间一数值X(0 X2N),当计数器时钟上升沿从0 开始计数到X 值时输出时钟翻转一次,在计数器继续计数达到2N+1 时,输出时钟再次翻转并对计数器置一复位信号,使之从0 开始重新计数,即可实现。

(2)占空比为50%的分频,设计思想如下:基于(1)中占空比为非50%的输出时钟在输入时钟的上升沿触发翻转;若在同一个输入时钟周期内,此计数器

的两次输出时钟翻转分别在与(1)中对应的下降沿触发翻转,输出的时钟与。

基于FPGA的分频器设计研究

FPGA结课论文学院:专业:班级:姓名:目录1、引言 (3)2、2N分频器的设计 (3)3、任意整数N分频器的设计 (4)4、半整数分频器设计 (5)5、由分频方法直接获得秒脉冲的设计方法 (6)6、总结 (7)基于FPGA的分频器设计)1 引言分频器是数字系统中常用来对某个给定时钟的频率进行再分频,以得到所需之各种信号频率的常用基本电路之一。

广泛应用于工业控制中的变频需要,电声技术的转化等。

基于FPGA 实现的分频电路一般有两种方法:一是使用FPGA 芯片内部提供的锁相环电路,如 ALTERA 提供的 PLL(Phase Locked Loop),Xilinx 提供的 DLL(Delay Locked Loop);二是使用硬件描述语言,如VHDL、Verilog HDL 等。

使用锁相环电路有许多优点,如可以实现倍频、相位偏移、占空比可调等。

但 FPGA 提供的锁相环个数极为有限,不能灵活满足使用要求。

而用硬件描述语言实现的分频电路消耗不多的逻辑单元就可以实现对时钟的操作,具有成本低、灵活可编程等优点。

2 2N分频器的设计分频系数为2N的分频器的实现最简单,可采用二进制加或减法计数器的设计来实现。

计数器可直接从Altera公司提供的宏功能模块LPM中调用,也可文本输入或原理图输入方式构成。

以一个4bit的二进制加法计数器为例进行分析说明。

以原理图输入方式设计四位二进制加法计数器如图1所示,经编译、时序模拟后得到仿真波形如图2所示:图1 四位二进制加法计数器图2 四位二进制加法计数器仿真波形从仿真波形可以看出分别由Q0、Q1、Q2、Q3得到的脉冲波形频率正是时钟信号CP的1/2、1/4、1/8和1/16。

亦即分频系数是2、4、8和16。

假设FPGA的CP所接石英晶体是20MHz,则不同引脚所得到的频率分别为10 MHz、5 MHz、2.5 MHz和1.25 MHz。

由上讨论推广可知,N位二进制计数器输出端的每一位输出信号其占空比为50%,从低到高排列分频系数正好为21、22、23、24……。

基于FPGA的小数分频器的设计与实现

基于FPGA的小数分频器的设计与实现【摘要】本文首先分析了现有小数分频器的优缺点,在此基础上提出了一种改进型小数分频器的设计方法。

同时结合VHDL文本输入和原理图输入方式,在FPGA开发平台上进行了电路设计,最后利用EDA设计软件QuartusII对其可行性进行了仿真验证。

仿真结果表明:通过对参数的设置,该方案可实现等占空比的任意小数分频。

【关键词】FPGA;仿真;VHDL引言分频器是控制类电路中常用的模块之一。

在实际应用中,设计人员常常需要将一个基准频率通过加、减、乘、除简单的四则运算进行频率合成,以满足不同的电路需求。

常见的偶数分频、奇数分频等成整数关系的频率合成实现相对比较容易。

但在某些的情况下,这种成整数关系的分频技术无法解决频率调整间隔过大的缺点,在此情况下本文提出了一种基于FPGA的小数分频的设计方法。

一般情况下,小数分频器包括半整数分频器和非半整数分频器。

对于半整数分频器我们在《基于FPGA 的通用数控分频器的设计与实现》[1]中有过详细介绍。

本文主要介绍非半整数分频器的设计和实现,并在FPGA开发平台上,结合VHDL文本输入和原理图输入方式进行了电路设计,同时利用EDA开发软件QuartusII对其可行性进行仿真验证。

仿真结果表明:该方法实现的小数分频,具有精度高、转化速度快、资源消耗低,可编程等优点,同时克服了小数分频中等占空比不易实现的问题。

1.几种常见小数分频器假设分频系数为K,输入频率为fin,输出频率为fout,则有:(1)其中:K>1当分频系数为小数时,则K可以表示为:(2)或:(3)其中,M、N、N1、N2均为正整数,且。

1.1 用BCD比例乘法器4527实现对于公式(2),可以利用十进制BCD比例乘法器的加法级联来实现[4]。

如图1所示,为两个4527 BCD比例乘法器的级联。

CLOCK端输入基准频率信号fin。

A、B、C、D四个端口是置数端,用以控制比例乘法器输出脉冲序列的个数。

FPGA实验报告7__1HZ分频器

Lab 7 1HZ分频器设计集成1101班1.实验目的熟悉用Quartus编译Verilog语言的方法。

掌握用Verilog HDL 语言描述分频器的方法。

学会FPGA I/O引脚分配和实现过程。

2.实验内容a)使用Verilog语言实现分频器。

b)得到仿真波形。

c)使用DE0开发板下载。

3.代码分析输入50MHZ时钟信号CP和控制信号CR,输出Q,Q有两种状态:0和1。

用reg型变量CT实现计数,当CT=25M时,Q翻转,实现把50MHZ 信号转变成1HZ的功能。

module fenpin (CP,CR,Q);input CP,CR;output Q;reg [31:0] CT;reg Q;always @(posedge CP or negedge CR)beginif (~CR) CT<=32'd0;else if (CT>=32'd2*******)beginCT<=32'd0;Q=~Q;endelse CT<=CT+1'd1;endendmodule4.实验步骤(1)打开Quartus9.1软件,选择“File=>New Project Wizard”,在弹出的窗口中输入项目的名称和存储位置。

(2)单击两次Next后,选择实验板的具体型号。

(3)在“File=>New”的窗口中选择建立Verilog文件。

(4)单击OK后,在Quartus窗口的右方看到该文件,写入代码后选择“File=>Save”,将文件保存在与项目文件同样的位置即可。

然后可以看到如下状态:(5)选择“Processing=》Start Compilation”开始编译,编译通过后可以查看生成的Report。

(6)选择“file->new->vector waveeform file”生成波形图,设置波形。

(7)选择“processing-》generate functional simulation netlist”,再选择“processing=》Start simulation”,生成波形。

实验5指导书 基于FPGA的分频器的设计

实验5 基于FPGA的分频器设计预习内容阅读《电工电子实验教程》第6.6节中触发器及时序逻辑电路的内容。

预先学习Quartus II软件的使用方法。

预习实验的内容,自拟实验步骤和数据表格,选择使用器件,完成电路设计,画出原理电路,手写预习报告。

一、实验目的1.了解EDA软件在电子设计当中的重要作用。

2.熟悉并掌握Quartus II开发软件的基本使用方法。

3.运用图解法设计分频器电路,并进行电路仿真。

二、知识要点FPGA(Field-Programmable Gate Array)是一种可编程器件,即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA主要生产厂商有:Altera、Xilinx、Actel、Lattice。

FPGA的开发软件包括Altera公司的Quartus II、Xilinx 公司的ISE、Lattice 公司的isplever Base。

Quartus II是Altera公司的第四代可编程逻辑器件集成开发环境,提供从设计输入到器件编程的全部功能。

Quartus II可以产生并识别EDIF网表文件、VHDL网表文件和Verilog HDL网表文件,为其它EDA工具提供了方便的接口;可以在Quartus II集成环境中自动运行其它EDA工具。

利用Quartus II软件的开发流程可概括为以下几步:设计输入、设计编译、设计定时分析、设计仿真和器件编程。

用户通过开发软件提供的设计工具实现自己的电路设计以及相应的配置,当用户通过仿真验证结论后,便可把设计下载至FPGA中,实现设定功能。

三、实验内容设计一个分频电路(使用74LS161和必要的门电路)。

要求得到8分频(输出频率为输入频率的八分之一)信号和32分频信号。

基于FPGA的通用数控分频器的设计与实现

基于FPGA的通用数控分频器的设计与实现【摘要】本文首先介绍了各种分频器的实现原理,并在FPGA开发平台上通过VHDL文本输入和原理图输入相结合的方式,编程给出了仿真结果。

最后通过对各种分频的分析,利用层次化设计思想,综合设计出了一种基于FPGA的通用数控分频器,通过对可控端口的调节就能够实现不同倍数及占空比的分频器。

【关键词】FPGA;分频器;VHDL1.引言分频器是数字系统中非常重要的模块之一,被广泛应用于各种控制电路中。

在实际中,设计人员往往需要将一个标准的频率源通过分频技术以满足不同的需求。

常见的分频形式主要有:偶数分频、奇数分频、半整数分频、小数分频、分数分频。

在某些严格的情况下,还有占空比的要求。

其中非等占空比的偶数分频器和奇数分频器其实现比较容易,但对于半整数分频器和占空比为50%的奇数分频器实现比较困难。

本文首先介绍了各种分频器的实现原理,并结合VHDL硬件描述语言对其进行了仿真,最后提出一个可控的通用分频器的设计方法,该方法可实现任意分频,资源消耗低,具有可编程等优点。

2.偶数分频器偶数分频器比较简单,即利用计数器对需要分频的原始时钟信号进行计数翻转。

例如:要进行M=2N(N为自然数)分频,当计数值为0~k-1时,输出高电平,当计数值为k-1~2N-1时输出低电平,同时计数值复位,如此循环可实现任意占空比的偶数分频,其中M和k为预置数,可根据分频倍数和占空比的要求进行置数。

如图1所示,当k=N时,即可实现占空比为50%的偶数分频[1]。

图1 占空比为50%的4分频仿真结果图2 占空比为50%的5分频仿真结果3.奇数分频器任意占空比的奇数分频器的实现,其原理与偶数分频器类似。

但对于占空比为50%的任意奇数次分频却无法用上述相同的方法实现。

下面介绍一种常用的实现方法[4]。

实现原理:采用两个不同的边沿触发器(一个在上升沿和一个在下降沿)来实现,其细节在于实现1/2个原始时钟周期的时间差。

FPGA实验报告整理版.doc

目录实验一分频器实验三 ADC0809 模数转换实验实验二七段数码管扫描显示实验四双向移位寄存器实验一分频器一、实验目的1.学习分频器的设计,进一步了解、熟悉和掌握FPGA开发软件Quartus II 的使用方法2.学习Verilog HDL 和VHDL的编程方法3.学会使用Vector Wave功能仿真4.掌握使用多种方法分配管脚二、实验内容编写一个分频器的Verilog 代码和VHDL代码并仿真,编译下载验证三、实验原理在数字电路中,时钟信号的分频是很常见的电路。

分频器除了可以对时钟信号频率做除以二的计算外,分频器同时很类似涟波计数器。

涟波计数器是计数器的一种,它属于异步设计。

因为触发器并非皆由同一个时钟信号同步操作,所以它非常节省电路面积。

本实验要设一个带选择的分频时钟,SEL[1:0]用于选择是几分频。

分频器设原理框图如图1所示:图1 分频器原理图从原理图中可见,核心板的时钟是50MHz ,通过sel[1:0]选择分频数,00:不分频;01:12.5M分频;10:25M四分频;11:50M分频。

采用SW1 ‐SW2 设置分频值,SW3 复位。

LED1为时钟的输出,通过调整SW1 、SW2 ,可以得到不同的闪烁频率。

引脚分配情况如表1所示表1 引脚分布情况四、实验步骤1.新建工程,取名为frediv ,如下图2所示。

图2 新建工程2.新建VHDL设计文件,选择“File|New ”,在New 对话框中选择Device Design Files下的VHDL File,单击OK,完成新建设计文件。

3.在新建设计文件中输入VHDL程序。

4.生成“Symbol ”文件,新建“Block Diagram/Schematic File”文件,在文件中添加刚刚生成的“Symbol ”以及输入输出管脚,最后完整的系统顶层模块图如图3 所示。

图3 顶层模块图5.保存文件,使用qsf或者tcl 进行管脚分配(相应的文件在本工程里面都可以找到)。

基于FPGA的分频器设计

基于FPGA的分频器设计FPGA(Field-Programmable Gate Array)是一种可编程逻辑设备,它可以在设计过程中根据需求进行编程和配置,实现不同的功能。

在FPGA中实现分频器是一个常见的应用,本文将介绍基于FPGA的分频器设计。

1.分频器的原理分频器用于将输入信号的频率减小到所需的频率。

它包含一个计数器和一个比较器。

计数器根据一个时钟信号进行计数,当达到一个预设值时,比较器会产生一个输出信号,作为分频器的输出。

在FPGA中实现分频器,首先需要选择适当的时钟源作为输入信号。

FPGA通常有一个高频时钟源,我们可以利用这个时钟源生成所需的低频信号。

3.设计步骤(1)确定时钟源:选择一个合适的高频时钟信号作为输入信号。

(2)选择分频器类型:根据需求选择分频器的类型,常见的有可控分频器和固定分频器。

(3)设置分频值:根据需要将输入信号的频率降低到所需的频率,设置分频值。

(4)设置计数器:在FPGA中,使用计数器来实现分频器。

根据所需的分频值,设置计数器的初始值和比较值。

(5)设计比较器:比较器用于判断计数器是否达到比较值,如果达到则产生一个输出信号。

(6)输出信号:比较器产生的输出信号作为分频器的输出信号,可以将其连接到需要的模块或引脚。

4.分频器设计实例下面以一个简单的可控分频器为例进行分频器的设计。

假设需要将输入信号的频率分频为输入频率的1/8,即输入频率为100MHz,输出频率为12.5MHz。

根据步骤,我们可以选择一个100MHz的时钟源作为输入信号。

然后,设置分频值为8,计数器的初始值为0,比较值为7(8-1)。

接下来,在FPGA中使用一个8位计数器来实现分频器。

计数器的输出连接到一个8位比较器,比较器的输出即为分频器的输出信号。

最后,将输出信号连接到需要的模块或引脚,以完成分频器的设计。

5.总结本文介绍了基于FPGA的分频器设计。

分频器是将输入信号的频率降低到所需频率的设备,可通过在FPGA中实现计数器和比较器来完成。

浙大fpga实验一 简单分频器的设计

实验报告课程名称: FPGA 应用 指导老师: 成绩:实验名称: 简单分频器的设计 实验类型: 同组学生姓名:一、实验目的和要求(必填) 二、实验内容和原理(必填)三、主要仪器设备(必填) 四、操作方法和实验步骤五、实验数据记录和处理 六、实验结果与分析(必填)七、讨论、心得一、 实验目的1. 熟悉Xilinx ISE 软件,学会设计、仿真、综合和下载2. 熟悉实验板电路设定的方法二、 实验内容根据实验板上晶振的输入频率50MHz ,如果直接用这么高的时钟频率来驱动LED 的闪烁,人眼将无法分辨。

因此本实验着重介绍如何通过分频计数器的方式将50MHz 的输入频率降低为人眼可分辨的频率(10Hz 以下),并在实验板的LED2~LED5上显示出来。

三、 主要仪器设备1. 电脑2. 实验板3. 实验电源及下载线四、 实验记录及分析主要程序:reg [22:0]cnt;always @(posedge clk )if (rst_n) cnt <=23'd0;else cnt <=cnt +1'b1; //带复位键的位宽为24位的分频计数器,以降低闪烁频率reg [7:0]led;always @(posedge clk )if (rst_n)led <=8'b00000001; //按键复位else if ((cnt==23'h7fffff) &&(led==8'b10000000))led <=8'b00000001; //循环一周后从D5开始下一周的循环else if (cnt==23'h7fffff)led <=led <<1; //左移一位,右端补零assign led_d2=~led[2];assign led_d4=~led[4];assign led_d3=~led[3];assign led_d5=~led[5];assign led_d0=~led[0];assign led_d1=~led[1];专业:电子信息工程姓名:学号:日期:地点:assign led_d6=~led[6];assign led_d7=~led[7];实验现象:初始状态时,led0亮,其余熄灭,一个clk信号后,led1亮,其余熄灭,依次不断循环,由于闪烁时间很短,所以观察的时候看到的led灯跑得很快。

哈工大FPGA设计与应用分频器设计实验报告

FPGA设计与应用分频器设计实验报告班级:1105103班姓名:郭诚学号:1110510304日期:2014年10月11日实验性质:验证性实验类型:必做开课单位:电信院学时:2学时一、实验目的1、了解Quartus II软件的功能;2、掌握Quartus II的HDL输入方法;3、掌握Quartus II编译、综合、适配和时序仿真;4、掌握Quartus II管脚分配、数据流下载方法;5、了解设计的资源消耗情况;6、掌握分频器和计数器的实现原理;7、掌握数码管的静态和动态显示原理二、实验准备(1分)2.1 EP2C8的系统资源概述逻辑单元8,256M4K RAM 块(4k比特+512校验比特) 36总的RAM比特数165,888嵌入式乘法器18锁相环PLLs 22.2 工程所用到的FPGA引脚及功能说明工程所用到的FPGA引脚及功能说明:PIN_23是时钟引脚;PIN_114 PIN_117 PIN_127 PIN_134是数码管的位选引脚;PIN_133 PIN_116 PIN_110 PIN_112 PIN_128 PIN_118 PIN_115是数码管段选信号引脚;实验所用的LED是共阴级连接2.3 数码管的动态显示原理动态显示是将所有数码管的8个显示笔划"a,b,c,d,e,f,g,dp"的同名端连在一起,另外为每个数码管的公共极COM增加位选通控制电路,位选通由各自独立的I/O 线控制,当输出字形码时,所有数码管都接收到相同的字形码,但究竟是那个数码管会显示出字形,取决于FPGA对位选通COM端电路的控制,所以只要将需要显示的数码管的选通控制打开,该位就显示出字形,没有选通的数码管就不会亮。

通过分时轮流控制各个数码管的的COM端,就使各个数码管轮流受控显示,这就是动态驱动。

在轮流显示过程中,每位数码管的点亮时间为1~2ms,由于人的视觉暂留现象及发光二极管的余辉效应,尽管实际上各位数码管并非同时点亮,但只要扫描的速度足够快,给人的印象就是一组稳定的显示数据,不会有闪烁感。

数字电子电路 数电 实验报告 基于FPGA的分频器设计

装……订……线基于FPGA的分频器设计一、实验目的1、了解EDA软件在电子设计当中的重要作用EDA:EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪60年代中期从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

EDA技术:就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性。

2、熟悉并掌握MAXPLUS II 或QUARTUS II等开发软件的基本使用方法。

3、运用图解法设计分频器电路,并进行电路仿真。

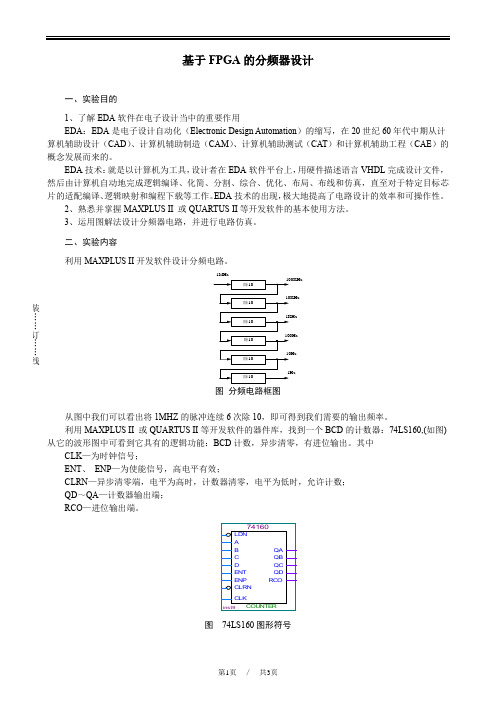

二、实验内容利用MAXPLUS II开发软件设计分频电路。

1MHz图分频电路框图从图中我们可以看出将1MHZ的脉冲连续6次除10,即可得到我们需要的输出频率。

利用MAXPLUS II 或QUARTUS II等开发软件的器件库,找到一个BCD的计数器:74LS160,(如图)从它的波形图中可看到它具有的逻辑功能:BCD计数,异步清零,有进位输出。

其中CLK—为时钟信号;ENT、ENP—为使能信号,高电平有效;CLRN—异步清零端,电平为高时,计数器清零,电平为低时,允许计数;QD~QA—计数器输出端;RCO—进位输出端。

图74LS160图形符号装……订……线图74LS160波形图74LS160是一个对输入时钟进行十分频的器件。

当计数器从0计数到9时,RCO从低电平跳到高电平,在下一个脉冲到来时,RCO再回到低电平。

每十个计数脉冲RCO翻转一次,利用RCO特性,将前一级的TC输出端接到下一级的时钟输入端,就完成了连续分频的目的。

调用6次74LS160,即可完成设计电路要求。

FPGA设计与应用实验指导书-v2

FPGA设计与应用实验指导书实验一Quartus II开发软件入门一、实验目的1. 熟悉Quartus II 开发软件的基本使用方法2. 掌握用VHDL语言设计组合逻辑电路的方法二、实验内容1. 运用Quartus II 开发软件,完成工程创建、代码编写、程序调试、编译仿真等基本操作。

2. 用VHDL语言设计实现一个3-8译码器,并进行功能仿真验证。

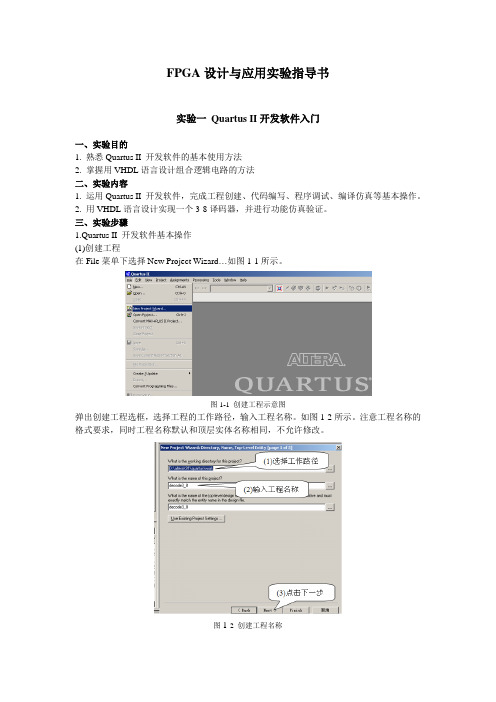

三、实验步骤1.Quartus II 开发软件基本操作(1)创建工程在File菜单下选择New Project Wizard…如图1-1所示。

图1-1 创建工程示意图弹出创建工程选框,选择工程的工作路径,输入工程名称。

如图1-2所示。

注意工程名称的格式要求,同时工程名称默认和顶层实体名称相同,不允许修改。

图1-2 创建工程名称可选择添加已有的程序文件,如图1-3所示。

这里不添加,直接下一步。

图1-3 添加文件选框选择芯片系列和芯片型号,如图1-4所示。

实验中使用的是Altera公司的Cyclone II系列FPGA 芯片,型号为EP2C35F672C6。

如果不进行硬件下载,可直接下一步。

图1-4 芯片参数选框EDA外部工具选框如图1-5所示。

一般选择默认值,直接下一步。

图1-5 EDA外部工具选框完成工程设置后的工程信息如图1-6所示。

图1-6 工程信息选框至此完成工程的创建。

(2)新建VHDL文件在File菜单下选择New选项,如图7所示。

图1-7新建文件示意图点击新建菜单后给出新建文件选框如图1-8所示。

选择VHDL File项创建VHDL文件。

图1-8 新建VHDL文件选框确定后弹出新建VHDL文件编辑窗口如图1-9所示。

可在窗口中编写程序内容并保存,注意文件名称与工程实体名称必须一致。

图1-9 VHDL文件编辑窗口至此完成VHDL文件的创建和VHDL程序的编写。

(3) 程序编译程序编写完成后,选择Processing菜单下的编译工具(Compiler Tool)菜单,如图1-10所示,调出编译工具。

FPGA实验一简单分频器的设计-图文

FPGA实验一简单分频器的设计-图文专业:__电子信息工程__姓名:_____陈华杰_____实验报告学号:______日期:___星期五上午___地点:应电楼303桌号2组课程名称:_____FPGA实验______指导老师:__竺红卫/陈宏__成绩:__________________实验名称:___实验一:简单分频器的设计____实验类型:_FPGA实验_同组学生姓名:__一、实验目的和要求(必填)二、实验内容和原理(必填)实验内容:根据实验板上晶振的输入频率50MHz,如果直接用这么高的时钟频率来驱动LED的闪烁,人眼将无法分辨。

因此本实验着重介绍如何通过分频计数器的方式将50MHz的输入频率降低为人眼可分辨的频率(10Hz以下),并在实验板的LED0~LED7上显示出来。

LED照片如下图:实验原理:实验板在滑动开关的上面有8个独立的贴片LED。

LED一端接地,另一端通过390欧的限流电阻接到Spartan-3E上。

要点亮一个LED,向相应的控制位置输出高电位。

三、主要仪器设备(必填)1.电脑一台;2.实验板一块,某ilin某Spartan-3E;3.实验板电源一只;四、实验步骤和现象1.新建Project和VerilogModule打开电脑桌面上的某ilin某ISE14.1软件,选择project→newproject建立新项目,输入projectname。

第1页,共17页核对选择Spartan3E和某C3S500E和FG320的封装形式。

跳出下面的选择框。

第2页,共17页选择NewSource,并在下面的选择框中选VerilogModule,填写刚才的newprojectname。

跳出下面的选择框。

点击NE某T。

第3页,共17页输入文件名,跳出下面的选择框。

点击NE某T。

跳出下面的选择框。

点击FINISH。

第4页,共17页2.建立约束文件选中SourceforProject窗口中的tet1.v文件,在Procee进程窗口中双击CreateNewSource。

FPGA分频器设计

《CPLD/FPGA原理及应用》上机实验报告姓名:学号:20091185015班级:2009级0901班院系:计算机及电子系专业:电子科学与技术算机及电子系2012年5月《CPLD/FPGA原理及应用》课程上机实验报告(三)实验名称实验时间2012年5月16日实验地点计算机实验室101实验人姓名合作者学号20091185015 实验小组第 2 组实验性质□验证性□设计性□综合性□应用性实验成绩:评阅教师签名:一.实验目的:(1)掌握常用的EDA设计工具的使用方法;(2)熟悉软件编程环境,熟练使用QuartusⅡ软件的各项功能;(3)在软件上调用各项已编译好的Verilog语言程序,参考熟悉Verilog语言编程的格式;(4)提高学生使用开发工具进行实际电路或系统设计的能力。

二.实验内容:(1)用HDL完成10分频,占空比为50%(2)用HDL完成9分频,占空比为50%(3) 分别对上述仿真进行验证,并综合处电路图。

三.用HDL完成10分频,占空比为50%源代码如下:module odd_division(clk,rst,count,clk_odd);input clk,rst;output clk_odd;output[3:0] count;reg clk_odd;reg[3:0] count;parameter N = 10;always @ (posedge clk)if(! rst)begincount <= 1'b0;clk_odd <= 1'b0;endelseif ( count < N/2-1)begincount <= count + 1'b1;endelsebegincount <= 1'b0;clk_odd <= ~clk_odd;endendmodule激励波形:仿真后的结果:仿真成功后得到的电路图:四.用HDL完成9分频,占空比为50% 源代码为:module count_num(reset,clk,count); parameter num=9;input clk,reset;output wire count;reg[4:0] m,n;reg count1,count2;assign count=count1|count2;always @(posedge clk)begin if(!reset)begin count1<=0;m<=0;endelsebegin if(m==num-1) m<=0; else m<=m+1; if (m<(num-1)/2) count1<=1;else count1<=0;endendalways @(negedge clk)begin if(!reset) begin count2<=0;n<=0;end elsebegin if(n==num-1) n<=0; else n<=n+1;if (n<(num-1)/2) count2<=1;else count2<=0;endendendmodule/仿真成功后的电路图:实验总结:(1).学习运用HDL语言描述简单的分频电路,9分频和10分频看似一样其实中间有些许区别,9分频为奇分频,9分频时将两个分频叠加;十分频为偶分频,使用一模N计数器模块即可实现,即每当模N计数器上升沿从0开始计数至N-1时,输出时钟进行翻转,同时给计数器一复位信号使之从0开始重新计数,以此循环即可。

基于FPGA的多种形式分频的设计与实现

基于FPGA的多种形式分频的设计与实现摘要:本文通过在QuartursⅡ开发平台下,一种能够实现等占空比、非等占空比整数分频及半整数分频的通用分频器的FPGA设计与实现,介绍了利用VHDL硬件描述语言输入方式,设计数字电路的过程。

关键词:FPGA;VHDL硬件描述语言;数字电路设计;分频器引言分频器是数字系统设计中的基本电路,根据不同设计的需要,我们会遇到偶数分频、奇数分频、半整数分频等,有时要求等占空比,有时要求非等占空比。

在同一个设计中有时要求多种形式的分频。

通常由计数器或计数器的级联构成各种形式的偶数分频及非等占空比的奇数分频,实现较为简单。

但对半整数分频及等占空比的奇数分频实现较为困难。

本文利用VHDL硬件描述语言,通过QuartusⅡ3.0开发平台,使用Altera公司的FPGA,设计了一种能够满足上述各种要求的较为通用的分频器。

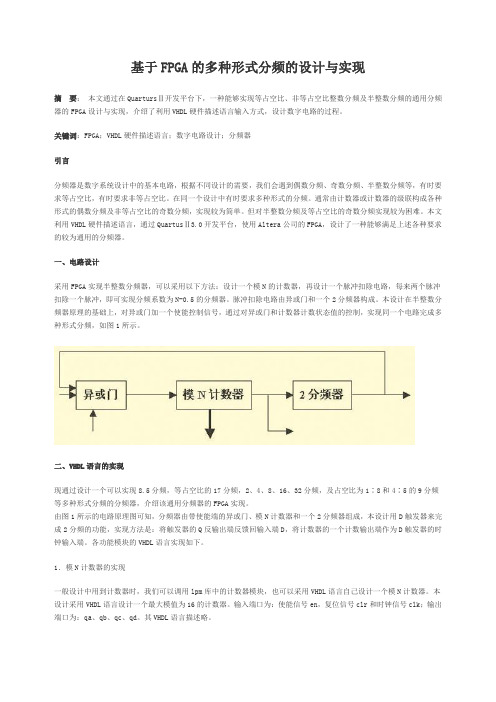

一、电路设计采用FPGA实现半整数分频器,可以采用以下方法:设计一个模N的计数器,再设计一个脉冲扣除电路,每来两个脉冲扣除一个脉冲,即可实现分频系数为N-0.5的分频器。

脉冲扣除电路由异或门和一个2分频器构成。

本设计在半整数分频器原理的基础上,对异或门加一个使能控制信号,通过对异或门和计数器计数状态值的控制,实现同一个电路完成多种形式分频,如图1所示。

二、VHDL语言的实现现通过设计一个可以实现8.5分频,等占空比的17分频,2、4、8、16、32分频,及占空比为1∶8和4∶5的9分频等多种形式分频的分频器,介绍该通用分频器的FPGA实现。

由图1所示的电路原理图可知,分频器由带使能端的异或门、模N计数器和一个2分频器组成,本设计用D触发器来完成2分频的功能,实现方法是:将触发器的Q反输出端反馈回输入端D,将计数器的一个计数输出端作为D触发器的时钟输入端。

各功能模块的VHDL语言实现如下。

1.模N计数器的实现一般设计中用到计数器时,我们可以调用lpm库中的计数器模块,也可以采用VHDL语言自己设计一个模N计数器。

基于FPGA的分频器的设计与实现

基于FPGA的分频器的设计与实现摘要:在数字逻辑电路设计中,分频器通常用来对某个给定频率进行分频,以得到所需的频率。

整数分频器的实现采用标准的计数器,也可采用可编程逻辑器件实现。

有时,时钟源与所需的频率不成整数倍关系可采用小数分频器进行分频。

本文在模拟设计频率计脉冲信号时,使用半整数分频器设计电路,且利用VHDL硬件描述语言和原理图输入方式,通过Quartus II以及EPM240T100C5型FPGA方便地完成了半整数分频器电路的设计。

关键词:FPGA;QUARTUSⅡ;VHDL语言;分频器中图分类号:G64 文献标识码:A 文章编号:1673-9132(2016)25-0023-02DOI:10.16657/ki.issn1673-9132.2016.25.013一、分频器的基本原理(一)整数分频的基本原理整数分频包含偶数分频和奇数分频,对于偶数N分频通常使用N/2计数器实现占空比为1:1的N分频器,分频输出信号模为N\2自动取反;对于奇数分频必须分频输出信号为模N计数中的一位[1]。

整数分频器的实现,采用可编程逻辑器件设计实现,当时钟源与所需的频率不成整数倍关系,此时可采用小数分频器进行分频。

(二)小数分频的基本原理小数分频的基本原理是采用脉冲吞吐计数器和锁相环技术先设计两个不同分频比的整数分频器,然后通过控制单位时间内两种分频比出现的不同次数来获得所需要的小数分频值,分频系数为N-0.5(N为整数)时,可控制扣除脉冲的时间,以使输出成为一个稳定的脉冲频率,而不是一次N分频,一次N-1分频[2]。

二、实验目的使用Quartus II仿真软件,使用半整数分频的方式,通过VHDL语言将整个分频器各个模块的编写使用FPGA实现分频器的整个设计和实现,通过分频器的设计实现掌握基本的整数分频和小数分频的原理,加强对硬件语言的理解,以及对使用组合电路设计复杂器件的能力[3]。

三、设计过程1.运行Quartus II,新建立一个工程,器件选择EPM240T100C5新片,完成新工程的建立[4]。

基于FPGA的奇偶分频器的设计与实现

内蒙古科技大学本科生毕业设计说明书(毕业论文)题目:基于FPGA的奇偶分频器的设计与实现学生姓名:学号:专业:电子信息工程班级:电信10-1班指导教师:基于FPGA的奇偶分频器的设计与实现摘要分频器作为一种最基本的数字电路,广泛的应用在各种复杂的逻辑电路设计中,对于FPGA芯片来说,虽然能用自带的锁相环来产生一部分我们所需的频率,但是,用VHDL 语言实现分频能从同一时钟较为方便、快捷的生成多个所需要的频率,同时能够实现信号的同步,因此,分频器的应用非常广泛。

本设计应用软件为开发平台,运用VHDL语言编程实现整数的奇偶分频的设计,在本设计中实现了0、2、4、6、8、10、12、14偶数的整数分频器设计和1、3、5、7、9、11、13、15奇数的整数分频器设计。

通过仿真结果,验证了设计的正确性.关键词:FPGA;分频器;VHDL语言;Quartus ⅡDesign and implementation of FPGA-based parity dividerAbstractDivider as a basic digital circuits,widely used in a variety of complex logic circuit design, the FPGA chip,although able to own a part of our phase—locked loop to produce the desired frequency, but using VHDL language divide from the same clock frequency is more convenient and efficient to generate multiple needs,while able to achieve synchronization signal,and therefore, the divider is widely used。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

H a r b i n I n s t i t u t e o f T e c h n o l o g y实验报告课程名称: FPGA设计与应用实验题目:分频器设计实验院系:电子与信息工程学院班级: 1005104 姓名:原亚欣学号: 1100500235 实验时间: 2013年11月哈尔滨工业大学分频器设计实验一、实验目的1、了解Quartus II软件的功能;2、掌握Quartus II的HDL输入方法;3、掌握Quartus II编译、综合、适配和时序仿真;4、掌握Quartus II管脚分配、数据流下载方法;5、了解设计的资源消耗情况;6、掌握分频器和计数器的实现原理;7、掌握数码管的静态和动态显示原理二、实验准备2.1 EP2C8的系统资源逻辑单元8,256M4K RAM 块(4k比特+512校验比特) 36总的RAM比特数165,888嵌入式乘法器18锁相环PLLs 22.2 工程所用到的FPGA引脚及功能说明node name direction location i/o bank VREF groupclk clkout seg7[0] seg7[1] seg7[2] seg7[3] seg7[4] InputOutputOutputOutputOutputOutputOutputPIN_23PIN_107PIN_115PIN_118PIN_128PIN_112PIN_1101333333B1_N0B3_N1B3_N1B3_N1B3_N1B3_N1B3_N1seg7[5]seg7[6]seg7_select[0] seg7_select[1] seg7_select[2] seg7_select[3] OutputOutputOutputOutputOutputOutputPIN_116PIN_133PIN_134PIN_127PIN_117PIN_114333333B3_N1B3_N0B3_N0B3_N1B3_N1B3_N1工程所用到的FPGA引脚及功能说明PIN_23 是时钟引脚。

PIN_114 PIN_117 PIN_127 PIN_134是数码管的位选引脚。

PIN_133 PIN_116 PIN_110 PIN_112 PIN_128 PIN_118 PIN_115是数码管的段选信号引脚。

2.3 数码管的动态显示原理动态显示是将所有数码管的8个显示笔划"a,b,c,d,e,f,g,dp"的同名端连在一起,另外为每个数码管的公共极COM增加位选通控制电路,位选通由各自独立的I/O线控制,当输出字形码时,所有数码管都接收到相同的字形码,但究竟是那个数码管会显示出字形,取决于fpga对位选通COM端电路的控制,所以我们只要将需要显示的数码管的选通控制打开,该位就显示出字形,没有选通的数码管就不会亮。

通过分时轮流控制各个数码管的的COM端,就使各个数码管轮流受控显示,这就是动态驱动。

在轮流显示过程中,每位数码管的点亮时间为1~2ms,由于人的视觉暂留现象及发光二极管的余辉效应,尽管实际上各位数码管并非同时点亮,但只要扫描的速度足够快,给人的印象就是一组稳定的显示数据,不会有闪烁感。

三、源代码及测试结果3.1 分频器4连体数码管显示源代码及分析Library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_unsigned.all;Entity yyx_shiyan1 isport ( yyx_clk : in std_logic;yyx_clkout : out std_logic;yyx_s7: out std_logic_vector( 6 downto 0 ); --7断码输出yyx_s3: out std_logic_vector( 3 downto 0)); --4个数码管选通end;architecture one of yyx_shiyan1 issignal yyx_L1,yyx_L2,yyx_L3,yyx_L4,yyx_L:integer; --L1,L2是前两个数码管表示分钟的高两位L3,L4是分钟的低两位signal yyx_a:std_logic_vector(26 downto 0); --用作计数signal yyx_q1:std_logic; --LED灯信号signal yyx_b:std_logic_vector(12 downto 0); --用作计数signal yyx_q2:std_logic; --数码管扫描信号signal yyx_clkout1:std_logic; --数码管扫描信号的输出signal yyx_c:std_logic_vector(1 downto 0):="00"; --用于数码管选通--将时钟信号83333333分频得到频率为0.6Hz的输出信号要求占空比为75%beginprocess(yyx_clk)beginif yyx_clk'event and yyx_clk='1' thenif yyx_a<62500000 thenyyx_a<=yyx_a+1;yyx_q1<='1';elsif yyx_a<83333333 thenyyx_a<=yyx_a+1;yyx_q1<='0';elseyyx_a <= (others=>'0');end if;end if;yyx_clkout<=yyx_q1;end process;--将时钟信号分频得到周期为1ms的信号作为数码管扫描信号process(yyx_clk)beginif yyx_clk'event and yyx_clk='1' thenif yyx_b<250000 thenyyx_b<=yyx_b+1;yyx_q2<=yyx_q2;elseyyx_b <= (others=>'0');yyx_q2<=not yyx_q2;end if;end if;yyx_clkout1<=yyx_q2;end process;--进行计数,第一、三位模10计数,第二、四位模6计数process(yyx_q1)variable min_10:integer:=0;variable min:integer:=0;variable sec_10:integer:=0;variable sec:integer:=0;beginif yyx_q1'event and yyx_q1='1' thenif sec =9 thensec:=0;if sec_10=5 thensec_10:=0;if min=9 thenmin:=0;if min_10=5 thenmin_10:=0;elsemin_10:=min_10+1;end if;elsemin:=min+1;end if;elsesec_10:=sec_10+1;end if;elsesec:=sec+1;end if;end if;yyx_L1 <= min_10;yyx_L2 <= min;yyx_L3 <= sec_10;yyx_L4 <= sec;end process;--用1ms时钟进行模4 计数,用于数码管选通。

计00选通第一位,01选通第二位,10选通第三位,11选通第四位。

分别把改为的数值送给led进行七段码译码。

process(yyx_q2)beginif yyx_q2'event and yyx_q2 = '1' thenif yyx_c ="11"thenyyx_c<="00";elseyyx_c <= yyx_c +1;end if;end if;case yyx_c iswhen "00" => yyx_s3 <="0001";yyx_L <= yyx_L4;when "01" => yyx_s3 <="0010";yyx_L <= yyx_L3;when "10" => yyx_s3 <="0100";yyx_L <= yyx_L2;when "11" => yyx_s3 <="1000";yyx_L <= yyx_L1;when others => null;end case;end process;--七段码译码process(yyx_L)begincase yyx_L iswhen 0 => yyx_s7 <= "0111111";when 1 => yyx_s7 <= "0000110";when 2 => yyx_s7 <= "1011011";when 3 => yyx_s7 <= "1001111";when 4 => yyx_s7 <= "1100110";when 5 => yyx_s7 <= "1101101";when 6 => yyx_s7 <= "1111101";when 7 => yyx_s7 <= "0000111";when 8 => yyx_s7 <= "1111111";when 9 => yyx_s7 <= "1101111";when others => null;end case;end process;end one;3.2 分频器4连体数码管显示SignalTap II波形图四、论述Quartus II开发流程1、创建工程(1) 新建文件夹;(2) 输入源程序;(3) 保存文件;(4) 创建工程并添加源程序;(5) 选择目标芯片;(6) 设置EDA工具;(7) 结束设置。

2、编译工程通过New Project Wizard建立了目标系统的工程之后,可以对所建工程进行全程编译。