MIPI CSI 协议介绍

MIPI DSI 协议介绍

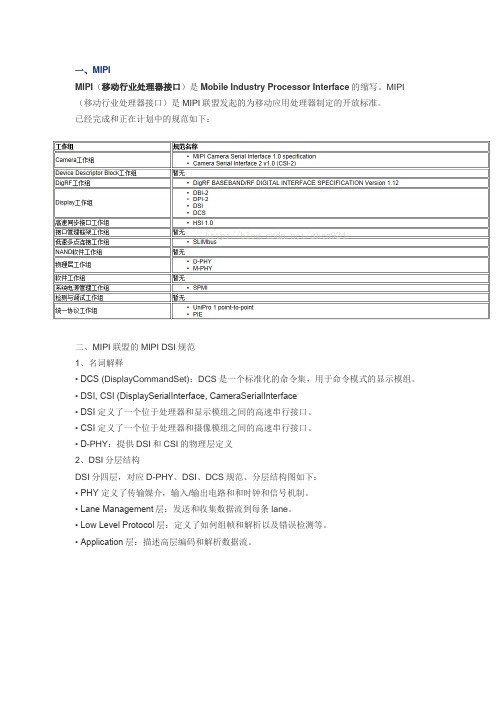

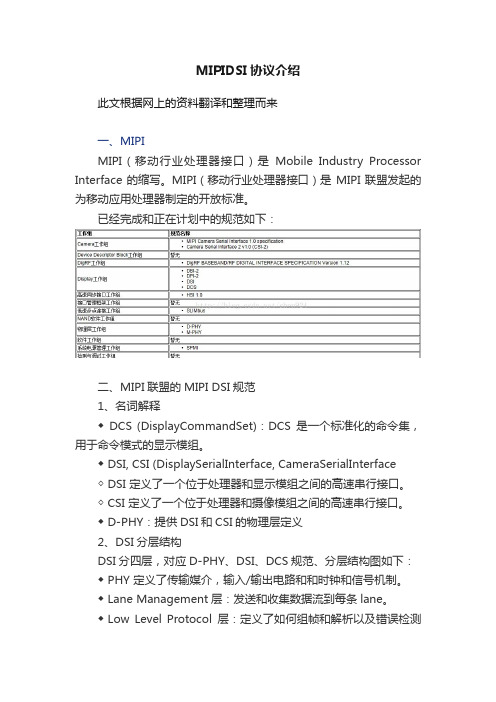

一、MIPIMIPI(移动行业处理器接口)是Mobile Industry Processor Interface的缩写。

MIPI (移动行业处理器接口)是MIPI联盟发起的为移动应用处理器制定的开放标准。

已经完成和正在计划中的规范如下:二、MIPI联盟的MIPI DSI规范1、名词解释• DCS (DisplayCommandSet):DCS是一个标准化的命令集,用于命令模式的显示模组。

• DSI, CSI (DisplaySerialInterface, CameraSerialInterface• DSI 定义了一个位于处理器和显示模组之间的高速串行接口。

• CSI 定义了一个位于处理器和摄像模组之间的高速串行接口。

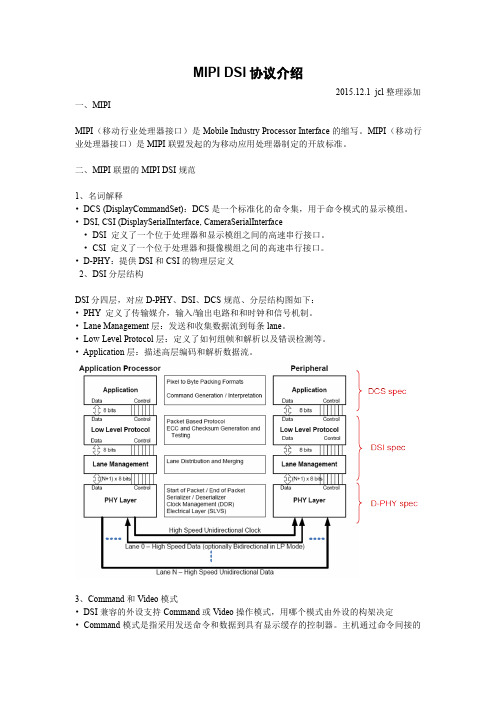

• D-PHY:提供DSI和CSI的物理层定义2、DSI分层结构DSI分四层,对应D-PHY、DSI、DCS规范、分层结构图如下:• PHY 定义了传输媒介,输入/输出电路和和时钟和信号机制。

• Lane Management层:发送和收集数据流到每条lane。

• Low Level Protocol层:定义了如何组帧和解析以及错误检测等。

• Application层:描述高层编码和解析数据流。

3、Command和Video模式• DSI兼容的外设支持Command或Video操作模式,用哪个模式由外设的构架决定• Command模式是指采用发送命令和数据到具有显示缓存的控制器。

主机通过命令间接的控制外设。

Command模式采用双向接口• Video模式是指从主机传输到外设采用时实象素流。

这种模式只能以高速传输。

为减少复杂性和节约成本,只采用Video模式的系统可能只有一个单向数据路径三、D-PHY介绍1、 D-PHY 描述了一同步、高速、低功耗、低代价的PHY。

• 一个 PHY配置包括• 一个时钟lane• 一个或多个数据lane• 两个Lane的 PHY配置如下图• 三个主要的lane的类型• 单向时钟Lane• 单向数据Lane• 双向数据Lane• D-PHY的传输模式•低功耗(Low-Power)信号模式(用于控制):10MHz (max)• 高速(High-Speed)信号模式(用于高速数据传输):80Mbps ~ 1Gbps/Lane • D-PHY低层协议规定最小数据单位是一个字节• 发送数据时必须低位在前,高位在后.• D-PHY适用于移动应用• DSI:显示串行接口• 一个时钟lane,一个或多个数据lane• CSI:摄像串行接口2、Lane模块• PHY由D-PHY(Lane模块)组成• D-PHY可能包含:• 低功耗发送器(LP-TX)• 低功耗接收器(LP-RX)• 高速发送器(HS-TX)• 高速接收器(HS-RX)• 低功耗竞争检测器(LP-CD)• 三个主要lane类型• 单向时钟Lane• Master:HS-TX, LP-TX• Slave:HS-RX, LP-RX• 单向数据Lane• Master:HS-TX, LP-TX• Slave:HS-RX, LP-RX• 双向数据Lane• Master, Slave:HS-TX, LP-TX, HS-RX, LP-RX, LP-CD3、Lane状态和电压• Lane状态• LP-00, LP-01, LP-10, LP-11 (单端)• HS-0, HS-1 (差分)• Lane电压(典型)• LP:0-1.2V• HS:100-300mV (200mV)4、操作模式• 数据Lane的三种操作模式• Escape mode, High-Speed(Burst) mode, Control mode•从控制模式的停止状态开始的可能事件有:• Escape mode request (LP-11→LP-10→LP-00→LP-01→LP-00)• High-Speed mode request (LP-11→LP-01→LP-00)• Turnaround request (LP-11→LP-10→LP-00→LP-10→LP-00)• Escape mode是数据Lane在LP状态下的一种特殊操作•在这种模式下,可以进入一些额外的功能:LPDT, ULPS, Trigger•数据Lane进入Escape mode模式通过LP-11→LP-10→LP-00→LP-01→LP-00•一旦进入Escape mode模式,发送端必须发送1个8-bit的命令来响应请求的动作• Escape mode 使用Spaced-One-Hot Encoding•超低功耗状态(Ultra-Low Power State)•这个状态下,lines处于空状态 (LP-00)•时钟Lane的超低功耗状态•时钟Lane通过LP-11→LP-10→LP-00进入ULPS状态•通过LP-10 → TWAKEUP →LP-11退出这种状态,最小TWAKEUP时间为1ms•高速数据传输•发送高速串行数据的行为称为高速数据传输或触发(burst)•全部Lanes门同步开始,结束的时间可能不同。

MIPI CSI-2 协议介绍解读

四、协议层

4.2、 LLP(Low Level Protocol) 层: *LLP层是一个面向字节的,基于包的协议;它支持任意大小的数据通过短包和长包 格式传输。各个包之间由EOT-LPS-SOT序列隔开。

*同步短包、数据长包: .帧同步短包:每帧图象必须开始于帧开始包(FRAME START PACKET),结束于 帧结束包(FRAME END PACKET); .行同步短包是可选的,对于RGB、YUV、RAW数据格式,每个数据长包里面必 须包含一整行图象数据,接收端利用WC解出行同步信号。

7)低速多点连接工作组: * SLIMbus ; 8)NAND软件工作组:暂无规范; 9)物理层工作组: * D-PHY: MIPI D-PHY Specification v1.00, MIPI D-PHY Specification v0.90.00, MIPI D-PHY Specification v0.65, * M-PHY; 10)软件工作组:暂无规范; 11)系统电源管理工作组 *SPMI ; 12)检测与调试工作组:暂无规范; 13)统一协议工作组: *UniPro 1 point-to-point *PIE

2、该组织下设了:高速多端链接工作小组(High-Speed Multipoint Link Working Group,包含基带、应用处理器、相机模组、蓝牙、和Wi-Fi之间的高 速连接)、软件工作小组、显示接口工作小组、存储界面以及负责市场的工作小组。 工作组名称和相应规范名称如下: 1)Camera工作组: * MIPI Camera Serial Interface 1.0 specification, * Camera Serial Interface 2 v1.0 (CSI-2) ; 2)Device Descriptor Block工作组:暂无规范; 3)DigRF工作组: * DigRF BASEBAND/RF DIGITAL INTERFACE SPECIFICATION Version 1.12 ; 4)Display工作组: * DBI-2 , * DPI-2, * DSI , * DCS ; 5)高速同步接口工作组: * HSI 1.0 ; 6)接口管理框架工作组:暂无规范;

如何分析mipi协议

如何分析mipi协议MIPI协议是一种用于移动设备的通信协议,它在实现高速数据传输和接口标准化方面发挥着重要作用。

MIPI(Mobile Industry Processor Interface)是一个由移动设备行业联盟(MIPI Alliance)推出的标准化协议,旨在促进移动通信和嵌入式系统的技术发展。

本文将介绍如何分析MIPI协议以及其在移动通信领域的重要性。

首先,MIPI协议涵盖了多个不同的子协议,如MIPI D-PHY、MIPI CSI-2和MIPI DSI等。

其中,MIPI D-PHY是一种物理层协议,用于在芯片之间进行高速数据传输。

它提供了具有低功耗、高带宽和低干扰的特性,适用于移动设备的显示、摄像头和传感器等部件间的通信。

MIPI CSI-2(Camera Serial Interface 2)则是一种用于摄像头模块和图像处理器之间数据传输的协议,主要用于移动设备中的摄像头功能。

类似地,MIPI DSI(Display Serial Interface)是一种用于移动设备显示屏和图形处理器之间数据传输的协议。

在对MIPI协议进行分析时,可以从以下几个方面入手。

首先,了解协议的基本结构和通信原理是非常重要的。

可以查阅相关的技术文档和规范,掌握协议的各个层次以及数据帧的格式和传输方式。

其次,要深入了解协议的特性和特点。

MIPI协议在功耗管理、时序控制和数据处理方面都有一些独特的要求和特性,这些特性对于系统设计和开发至关重要。

此外,还需要了解协议的应用范围和实际场景。

MIPI协议主要应用于移动设备,如智能手机、平板电脑和可穿戴设备等,因此需要对这些设备的硬件和软件架构有一定的了解。

分析MIPI协议还可以从协议的优缺点以及应用案例等方面展开。

MIPI协议在提高数据传输速率、降低功耗、简化系统设计等方面有诸多优点。

首先,它提供了可靠的高速数据传输通道,使得移动设备可以实现更快速和稳定的数据传输。

MIPI协议学习总结(一)【转】

MIPI协议学习总结(⼀)【转】转⾃:⼀、MIPI 简介: MIPI(移动⾏业处理器接⼝)是Mobile Industry Processor Interface的缩写。

MIPI是MIPI联盟发起的为移动应⽤处理器制定的开放标准。

已经完成和正在计划中的规范如下:⼆、MIPI DSI规范:1、名词解释• DCS (Display Command Set):DCS是⼀个标准化的命令集,⽤于命令模式的显⽰模组。

• DSI, CSI (Display Serial Interface , Camera Serial Interface )• DSI 定义了⼀个位于处理器和显⽰模组之间的⾼速串⾏接⼝。

• CSI 定义了⼀个位于处理器和摄像模组之间的⾼速串⾏接⼝。

• D-PHY:提供DSI和CSI的物理层定义2、DSI分层结构DSI分四层,对应D-PHY、DSI、DCS规范;分层结构图如下:• PHY Layer层:定义了传输媒介,输⼊/输出电路和和时钟和信号机制。

• Lane Management层:发送和收集数据流到每条lane。

• Low Level Protocol层:定义了如何组帧和解析以及错误检测等。

• Application层:描述⾼层编码和解析数据流3、Command和Video模式• DSI兼容的外设⽀持Command或Video操作模式,⽤哪个模式由外设的构架决定;• Command模式是指采⽤发送命令和数据到具有显⽰缓存的控制器,主机通过命令间接的控制外设;Command模式采⽤双向接⼝;• Video模式是指从主机传输到外设采⽤实时象素流,这种模式只能以⾼速传输,为减少复杂性和节约成本,只采⽤Video模式的系统可能只有⼀个单向数据路径;三、D-PHY介绍1、 D-PHY 描述了⼀同步、⾼速、低功耗、低代价的PHY。

⼀个 PHY配置包括 :• ⼀个时钟lane• ⼀个或多个数据lane2、两个Lane的 PHY配置如下图:3、PHY由D-PHY(Lane模块)组成D-PHY可能包含:• 低功耗发送器(LP-TX)• 低功耗接收器(LP-RX)• ⾼速发送器(HS-TX)• ⾼速接收器(HS-RX)• 低功耗竞争检测器(LP-CD)4、三个主要的lane的类型 :• 单向时钟Lane• Master:HS-TX, LP-TX• Slave:HS-RX, LP-RX• 单向数据Lane• Master:HS-TX, LP-TX• Slave:HS-RX, LP-RX• 双向数据Lane• Master, Slave:HS-TX, LP-TX, HS-RX, LP-RX, LP-CD5、D-PHY的传输模式• 低功耗(Low-Power)信号模式(⽤于控制):10MHz (max)• ⾼速(High-Speed)信号模式(⽤于⾼速数据传输):80Mbps ~ 1Gbps/Lane• D-PHY低层协议规定最⼩数据单位是⼀个字节• 发送数据时必须低位在前,⾼位在后6、Lane状态和电压Lane状态 :• LP-00, LP-01, LP-10, LP-11 (单端)• HS-0, HS-1 (差分)Lane电压(典型) :• LP:0-1.2V• HS:100-300mV (200mV)7、操作模式数据Lane的三种操作模式:Escape mode, High-Speed(Burst) mode, Control mode ;从控制模式的停⽌状态开始的可能事件有:• Escape mode request (LP-11→LP-10→LP-00→LP-01→LP-00)• High-Speed mode request (LP-11→LP-01→LP-00)• Turn around request (LP-11→LP-10→LP-00→LP-10→LP-00)Escape mode是数据Lane在LP状态下的⼀种特殊操作,在这种模式下,可以进⼊⼀些额外的功能:LPDT、ULPS、Trigger ,数据Lane进⼊Escape mode模式通过LP-11→LP-10→LP-00→LP-01→LP-00 ;⼀旦进⼊Escape mode模式,发送端必须发送1个8-bit的命令来响应请求的动作,Escape mode 使⽤Spaced-One-Hot Encoding•超低功耗状态(Ultra-Low Power State)这个状态下,lines处于空状态 (LP-00)•时钟Lane的超低功耗状态:•时钟Lane通过LP-11→LP-10→LP-00进⼊ULPS状态•通过LP-10 → TWAKEUP →LP-11退出这种状态,最⼩TWAKEUP时间为1ms• ⾼速数据传输•发送⾼速串⾏数据的⾏为称为⾼速数据传输或触发(burst)•全部Lanes门同步开始,结束的时间可能不同。

MIPIDSI协议介绍

MIPIDSI协议介绍此文根据网上的资料翻译和整理而来一、MIPIMIPI(移动行业处理器接口)是Mobile Industry Processor Interface的缩写。

MIPI(移动行业处理器接口)是MIPI联盟发起的为移动应用处理器制定的开放标准。

已经完成和正在计划中的规范如下:二、MIPI联盟的MIPI DSI规范1、名词解释◆DCS (DisplayCommandSet):DCS是一个标准化的命令集,用于命令模式的显示模组。

◆ DSI, CSI (DisplaySerialInterface, CameraSerialInterface◇ DSI 定义了一个位于处理器和显示模组之间的高速串行接口。

◇ CSI 定义了一个位于处理器和摄像模组之间的高速串行接口。

◆ D-PHY:提供DSI和CSI的物理层定义2、DSI分层结构DSI分四层,对应D-PHY、DSI、DCS规范、分层结构图如下:◆ PHY 定义了传输媒介,输入/输出电路和和时钟和信号机制。

◆ Lane Management层:发送和收集数据流到每条lane。

◆ Low Level Protocol层:定义了如何组帧和解析以及错误检测等。

◆ Application层:描述高层编码和解析数据流。

3、Command和Video模式◆ DSI兼容的外设支持Command或Video操作模式,用哪个模式由外设的构架决定◆ Command模式是指采用发送命令和数据到具有显示缓存的控制器。

主机通过命令间接的控制外设。

Command模式采用双向接口◆ Video模式是指从主机传输到外设采用时实象素流。

这种模式只能以高速传输。

为减少复杂性和节约成本,只采用Video模式的系统可能只有一个单向数据路径三、D-PHY介绍1、 D-PHY 描述了一同步、高速、低功耗、低代价的PHY。

◆一个 PHY配置包括◇一个时钟lane◇一个或多个数据lane◆两个Lane的 PHY配置如下图◆三个主要的lane的类型◇单向时钟Lane◇单向数据Lane◇双向数据Lane◆ D-PHY的传输模式◇低功耗(Low-Power)信号模式(用于控制):10MHz (max)◇高速(High-Speed)信号模式(用于高速数据传输):80Mbps ~ 1Gbps/Lane◆ D-PHY低层协议规定最小数据单位是一个字节◇发送数据时必须低位在前,高位在后.◆ D-PHY适用于移动应用◇ DSI:显示串行接口○ 一个时钟lane,一个或多个数据lane◇ CSI:摄像串行接口2、Lane模块◆ PHY由D-PHY(Lane模块)组成◆ D-PHY可能包含:◇低功耗发送器(LP-TX)◇低功耗接收器(LP-RX)◇高速发送器(HS-TX)◇高速接收器(HS-RX)◇低功耗竞争检测器(LP-CD)◆三个主要lane类型◇单向时钟Lane◆ Master:HS-TX, LP-TX◆ Slave:HS-RX, LP-RX◇单向数据Lane○ Master:HS-TX, LP-TX○ Slave:HS-RX, LP-RX◇双向数据Lane○ Master, Slave:HS-TX, LP-TX, HS-RX, LP-RX, LP-CD3、Lane状态和电压◆ Lane状态◇ LP-00, LP-01, LP-10, LP-11 (单端)◇ HS-0, HS-1 (差分)◆ Lane电压(典型)◇ LP:0-1.2V◇ HS:100-300mV (200mV)4、操作模式◆数据Lane的三种操作模式◇Escape mode, High-Speed(Burst) mode, Control mode◆从控制模式的停止状态开始的可能事件有:◇Escape mode request (LP-11→LP-10→LP-00→LP-01→LP-00)◇ High-Speed mode request (LP-11→LP-01→LP-00)◇ Turnaround request (LP-11→LP-10→LP-00→LP-10→LP-00)◆ Escape mode是数据Lane在LP状态下的一种特殊操作◇在这种模式下,可以进入一些额外的功能:LPDT, ULPS, Trigger◇数据Lane进入Escape mode模式通过LP-11→LP-10→LP-00→LP-01→LP-00◇一旦进入Escape mode模式,发送端必须发送1个8-bit的命令来响应请求的动作◇ Escape mode 使用Spaced-One-Hot Encoding◆超低功耗状态(Ultra-Low Power State)◇这个状态下,lines处于空状态 (LP-00)◆时钟Lane的超低功耗状态◇时钟Lane通过LP-11→LP-10→LP-00进入ULPS状态◇通过LP-10 → TWAKEUP →LP-11退出这种状态,最小TWAKEUP时间为1ms◆高速数据传输◇发送高速串行数据的行为称为高速数据传输或触发(burst)◇全部Lanes门同步开始,结束的时间可能不同。

mipi csi2标准

mipi csi2标准

MIPI CSI-2(MIPI Camera Serial Interface 2)是一种用于连

接图像传感器和图像处理器的串行接口标准。

它是由Mobile Industry Processor Interface(MIPI)联盟制定的,旨在提供高速、低功耗和

高带宽的图像传输解决方案。

MIPI CSI-2标准支持单个或多个图像传感器,并且可以在不同设备之间传输图像和控制数据。

它使用高速串行差分信号传输数据,支

持多种数据格式和解析度。

该标准定义了CSI-2主机和CSI-2设备之间的物理层和数据链路

层规范,包括信号传输速率、电气特性、协议和控制命令等。

它还定

义了一些特性,如图像流的错误检测和纠正、时钟同步和功耗管理等。

使用MIPI CSI-2接口可以实现高质量、低延迟和低功耗的图像

传输,广泛应用于移动设备、汽车电子、工业视觉和机器视觉等领域。

mipi csi协议结构

mipi csi协议结构

MIPI CSI(Mobile Industry Processor Interface Camera Serial Interface)是一种用于移动设备和嵌入式系统的摄像头串

行接口协议。

它定义了摄像头传感器和图像处理器之间的通信接口,允许高速传输图像和控制数据。

MIPI CSI协议结构主要包括以下几

个方面:

1. 物理层,MIPI CSI协议使用低压差分信号传输数据,通常

使用两对差分信号进行数据传输,这有助于减少电磁干扰和提高抗

噪声能力。

物理层还定义了时序和电气特性,以确保数据的可靠传输。

2. 数据链路层,MIPI CSI协议的数据链路层负责将图像数据

和控制数据进行打包和传输。

它定义了数据包的格式、同步机制、

差错校正和重传等功能,以确保数据的完整性和可靠性。

3. 控制器接口,MIPI CSI协议还定义了摄像头控制器和主机

处理器之间的控制接口,包括配置摄像头参数、启动/停止传输、中

断处理等功能。

这些接口使主机处理器能够有效地控制和管理摄像

头设备。

4. 协议栈,MIPI CSI协议还包括协议栈,定义了摄像头设备和主机处理器之间的通信协议,包括数据包格式、命令和响应的交互流程等。

协议栈的设计有助于确保不同厂商生产的摄像头和处理器能够互相兼容和互操作。

总的来说,MIPI CSI协议结构涵盖了物理层、数据链路层、控制器接口和协议栈,它为移动设备和嵌入式系统提供了一种高效、可靠的摄像头接口标准,促进了摄像头设备和处理器之间的互操作性和兼容性。

摄像头MIPI-CSI介绍

结构层介绍

CSI分三层,对应D-PHY(物理层)、CSI(协议层)、 DCS规范(应用层)、分层结构图如下:

D-PHY :物理层定义了传输媒介,输入/输出电路 和时钟和信号机制。 Lane Management层:通道管理层, 发送和接收数据流到每条lane(通道的分布和合并) Low Level Protocol层:定义了如何组帧和解析 以及错误检测等。 Application层:描述高层编码和解析数据流 (像素到字节格式命令/解释)

物理层介绍一

除电源及地线外,MIPI CSI2一般会有1对I2C通信引脚,1对MIPI差分时钟引脚 和1~4对MIPI差分数据信号引脚

物理层介绍二

定义了传输介质 (electrical conductors,导体),输入/输出电路信号的电气特性( electricalparameters)和时钟机制(时序)。即如何从串行位流(Bit Stream)中获取 “0”和“1”信号。规范中的这一部分记录了传输介质的特性,并依据时钟和数据通道

MIPI 概念介绍二

MIPI 接口包括:DCS(显示命令接口)、DBI(显示总线接口)、DPI(显示像素接口)、DSI (显示串行接口)、CSI(显示摄像接口)。 DCS (DisplayCommandSet):DCS是一个标准化的命令集,用于命令模式的显示模组。 DSI(DisplaySerialInterface):定义了一个位于处理器和显示模组之间的高速串行接口。 CSI( CameraSerialInterface ): 定义了一个位于处理器和摄像模组之间的高速串行接口 D-PHY:提供DSI和CSI的物理层定义

LLP(low Level Protocol)层

LLP层包括,为串行数据在传输开始(SoT) 到传输结束(EoT)之间传输事件,和传输 数据到下一层,建立位级和字节级同步的方 法。LLP最小数据粒度是一字节。(即面向 字节)LLP层也包括,每字节中各位数值分 布解释,即“端”(Endian)分布。

mipi参数

mipi参数MIPI是一种用于移动设备的串行接口标准,是Mobile Industry Processor Interface的缩写。

它旨在提高移动设备内部各组件之间的通信速度、效率和可靠性。

MIPI参数涵盖了多个方面,包括物理连接、传输协议和数据格式。

以下是关于MIPI参数的一些相关参考内容:1. 物理连接参数:- MIPI D-PHY:MIPI D-PHY是一种物理层接口,专为连接摄像头、显示器和其他外设设计。

它使用差分信号传输数据,并支持多通道和高带宽。

- MIPI C-PHY:MIPI C-PHY是另一种物理层接口,用于连接高分辨率显示器。

它采用多通道方式传输数据,并支持高达24 Gbps的数据速率。

2. 传输协议参数:- MIPI CSI-2:MIPI CSI-2(Camera Serial Interface 2)是一种用于连接摄像头和图像处理器的传输协议。

它支持多通道传输、像素编码和误码纠正,并提供了灵活的配置选项。

- MIPI DSI:MIPI DSI(Display Serial Interface)是一种用于连接显示器和图形处理器的传输协议。

它支持像素编码、多通道传输和灵活的显式命令。

3. 数据格式参数:- MIPI CSI-2数据格式:MIPI CSI-2支持多种数据格式,包括RAW、YUV和RGB等。

其中,RAW格式用于原始图像数据的传输,YUV格式用于彩色图像的传输,RGB格式用于显示器的传输。

- MIPI DSI数据格式:MIPI DSI支持多种像素编码格式,包括RGB565、RGB666、RGB888和YUV422等。

不同的编码格式可以满足不同显示设备的需求。

4. 其他参数:- MIPI Power Management:MIPI还提供了用于设备电源管理的标准接口,可以实现对移动设备各组件的电源控制和监测。

- MIPI RFFE:MIPI RFFE(RF Front-End)是一种用于无线通信前端的控制接口,可用于控制和监测射频前端模块的各项参数。

MIPI CSIDSI 简介及信号和协议测试方法

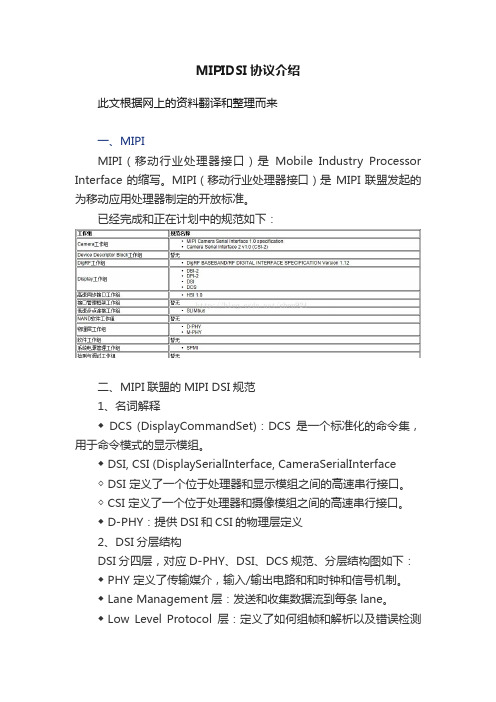

MIPI CSI/DSI简介及信号和协议测试方法--李凯一、MIPI CSI/DSI简介对于现代的智能手机来说,其内部要塞入太多各种不同接口的设备,给手机的设计和元器件选择带来很大的难度。

下图是一个智能手机的例子,我们可以看到其内部存储、显示、摄像、声音等内部接口都是各不相同的。

即使以摄像头接口来说,不同的摄像头模组厂商也可能会使用不同的接口形式,这给手机厂商设计手机和选择器件带来了很大的难度。

MIPI (Mobile Industry Processor Interface)是2003年由ARM, Nokia, ST ,TI等公司成立的一个联盟(),目的是把手机内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性。

MIPI联盟下面有不同的WorkGroup,分别定义了一系列的手机内部接口标准,比如摄像头接口CSI、显示接口DSI、射频接口DigRF、麦克风/喇叭接口SLIMbus等。

统一接口标准的好处是手机厂商根据需要可以从市面上灵活选择不同的芯片和模组,更改设计和功能时更加快捷方便。

MIPI组织主要致力于把移动通信设备内部的接口标准化从而减少兼容性问题并简化设计。

下图是按照MIPI组织的设想未来智能移动通信设备的内部架构。

目前已经比较成熟的MIPI应用有摄像头的CSI接口、显示屏的DSI接口以及基带和射频间的DigRF接口。

UFS、LLI等规范正在逐步制定和完善过程中。

CSI/DSI的物理层(Phy Layer)由专门的WorkGroup负责制定,其目前采用的物理层标准是D-PHY。

D-PHY采用1对源同步的差分时钟和1~4对差分数据线来进行数据传输。

数据传输采用DDR方式,即在时钟的上下边沿都有数据传输。

D-PHY的物理层支持HS(High Speed)和LP(Low Power)两种工作模式。

HS模式下采用低压差分信号,功耗较大,但是可以传输很高的数据速率(数据速率为80M~1Gbps);LP模式下采用单端信号,数据速率很低(<10Mbps),但是相应的功耗也很低。

MIPI协议详细介绍1.

D-PHY suited for mobile applications

DSI:Display Serial Interface

• A clock lane, One to four data lanes.

LP-10 → TWAKEUP →LP-11 The minimum value of TWAKEUP is 1ms

High-Speed Data Transmission

The action of sending high-speed serial data is called HS transmission or burst. Start-of-Transmission

• Four possible Low-Power Lane states (LP-00, LP-01, LP-10, LP-11)

A HS-TX drives the Lane differentially.

• Two possible High Speed Lane states (HS-0, HS-1)

D-PHY

• D-PHY provides the physical layer definition for DSI and CSI.

DSI Layers

DCS spec

DSI spec

D-PHY spec

Outline D-PHY

Introduction Lane Module, State and Line levels Operating Modes

• Master:HS-TX, LP-TX • Slave:HS-RX, LP-RX • Master:HS-TX, LP-TX • Slave:HS-RX, LP-RX

MIPI协议归纳整理

MIPI DSI协议介绍2015.12.1jcl整理添加一、MIPIMIPI(移动行业处理器接口)是Mobile Industry Processor Interface的缩写。

MIPI(移动行业处理器接口)是MIPI联盟发起的为移动应用处理器制定的开放标准。

二、MIPI联盟的MIPI DSI规范1、名词解释•DCS(DisplayCommandSet):DCS是一个标准化的命令集,用于命令模式的显示模组。

•DSI,CSI(DisplaySerialInterface,CameraSerialInterface•DSI定义了一个位于处理器和显示模组之间的高速串行接口。

•CSI定义了一个位于处理器和摄像模组之间的高速串行接口。

•D-PHY:提供DSI和CSI的物理层定义2、DSI分层结构DSI分四层,对应D-PHY、DSI、DCS规范、分层结构图如下:•PHY定义了传输媒介,输入/输出电路和和时钟和信号机制。

•Lane Management层:发送和收集数据流到每条lane。

•Low Level Protocol层:定义了如何组帧和解析以及错误检测等。

•Application层:描述高层编码和解析数据流。

3、Command和Video模式•DSI兼容的外设支持Command或Video操作模式,用哪个模式由外设的构架决定•Command模式是指采用发送命令和数据到具有显示缓存的控制器。

主机通过命令间接的控制外设。

Command模式采用双向接口•Video模式是指从主机传输到外设采用时实象素流。

这种模式只能以高速传输。

为减少复杂性和节约成本,只采用Video模式的系统可能只有一个单向数据路径三、D-PHY介绍1、D-PHY描述了一同步、高速、低功耗、低代价的PHY。

•一个PHY配置包括•一个时钟lane•一个或多个数据lane•两个Lane的PHY配置如下图•三个主要的lane的类型•单向时钟Lane•单向数据Lane•双向数据Lane•D-PHY的传输模式•低功耗(Low-Power)信号模式(用于控制):10MHz(max)•高速(High-Speed)信号模式(用于高速数据传输):80Mbps~1Gbps/Lane•D-PHY低层协议规定最小数据单位是一个字节•发送数据时必须低位在前,高位在后.•D-PHY适用于移动应用•DSI:显示串行接口•一个时钟lane,一个或多个数据lane•CSI:摄像串行接口2、Lane模块•PHY由D-PHY(Lane模块)组成•D-PHY可能包含:•低功耗发送器(LP-TX)•低功耗接收器(LP-RX)•高速发送器(HS-TX)•高速接收器(HS-RX)•低功耗竞争检测器(LP-CD)•三个主要lane类型•单向时钟Lane•Master:HS-TX,LP-TX•Slave:HS-RX,LP-RX•单向数据Lane•Master:HS-TX,LP-TX•Slave:HS-RX,LP-RX•双向数据Lane•Master,Slave:HS-TX,LP-TX,HS-RX,LP-RX,LP-CD3、Lane状态和电压•Lane状态•LP-00,LP-01,LP-10,LP-11(单端)•HS-0,HS-1(差分)•Lane电压(典型)•LP:0-1.2V•HS:100-300mV(200mV)4、操作模式•数据Lane的三种操作模式•Escape mode,High-Speed(Burst)mode,Control mode•从控制模式的停止状态开始的可能事件有:•Escape mode request(LP-11→LP-10→LP-00→LP-01→LP-00)•High-Speed mode request(LP-11→LP-01→LP-00)•Turnaround request(LP-11→LP-10→LP-00→LP-10→LP-00)•Escape mode是数据Lane在LP状态下的一种特殊操作•在这种模式下,可以进入一些额外的功能:LPDT,ULPS,Trigger•数据Lane进入Escape mode模式通过LP-11→LP-10→LP-00→LP-01→LP-00•一旦进入Escape mode模式,发送端必须发送1个8-bit的命令来响应请求的动作•Escape mode使用Spaced-One-Hot Encoding•超低功耗状态(Ultra-Low Power State)•这个状态下,lines处于空状态(LP-00)•时钟Lane的超低功耗状态•时钟Lane通过LP-11→LP-10→LP-00进入ULPS状态•通过LP-10→TWAKEUP→LP-11退出这种状态,最小TWAKEUP时间为1ms •高速数据传输•发送高速串行数据的行为称为高速数据传输或触发(burst)•全部Lanes门同步开始,结束的时间可能不同。

MIPIDSI协议介绍

MIPIDSI协议介绍此文根据网上的资料翻译和整理而来一、MIPIMIPI(移动行业处理器接口)是Mobile Industry Processor Interface的缩写。

MIPI(移动行业处理器接口)是MIPI联盟发起的为移动应用处理器制定的开放标准。

已经完成和正在计划中的规范如下:二、MIPI联盟的MIPI DSI规范1、名词解释◆DCS (DisplayCommandSet):DCS是一个标准化的命令集,用于命令模式的显示模组。

◆ DSI, CSI (DisplaySerialInterface, CameraSerialInterface◇ DSI 定义了一个位于处理器和显示模组之间的高速串行接口。

◇ CSI 定义了一个位于处理器和摄像模组之间的高速串行接口。

◆ D-PHY:提供DSI和CSI的物理层定义2、DSI分层结构DSI分四层,对应D-PHY、DSI、DCS规范、分层结构图如下:◆ PHY 定义了传输媒介,输入/输出电路和和时钟和信号机制。

◆ Lane Management层:发送和收集数据流到每条lane。

◆ Low Level Protocol层:定义了如何组帧和解析以及错误检测等。

◆ Application层:描述高层编码和解析数据流。

3、Command和Video模式◆ DSI兼容的外设支持Command或Video操作模式,用哪个模式由外设的构架决定◆ Command模式是指采用发送命令和数据到具有显示缓存的控制器。

主机通过命令间接的控制外设。

Command模式采用双向接口◆ Video模式是指从主机传输到外设采用时实象素流。

这种模式只能以高速传输。

为减少复杂性和节约成本,只采用Video模式的系统可能只有一个单向数据路径三、D-PHY介绍1、 D-PHY 描述了一同步、高速、低功耗、低代价的PHY。

◆一个 PHY配置包括◇一个时钟lane◇一个或多个数据lane◆两个Lane的 PHY配置如下图◆三个主要的lane的类型◇单向时钟Lane◇单向数据Lane◇双向数据Lane◆ D-PHY的传输模式◇低功耗(Low-Power)信号模式(用于控制):10MHz (max)◇高速(High-Speed)信号模式(用于高速数据传输):80Mbps ~ 1Gbps/Lane◆ D-PHY低层协议规定最小数据单位是一个字节◇发送数据时必须低位在前,高位在后.◆ D-PHY适用于移动应用◇ DSI:显示串行接口○ 一个时钟lane,一个或多个数据lane◇ CSI:摄像串行接口2、Lane模块◆ PHY由D-PHY(Lane模块)组成◆ D-PHY可能包含:◇低功耗发送器(LP-TX)◇低功耗接收器(LP-RX)◇高速发送器(HS-TX)◇高速接收器(HS-RX)◇低功耗竞争检测器(LP-CD)◆三个主要lane类型◇单向时钟Lane◆ Master:HS-TX, LP-TX◆ Slave:HS-RX, LP-RX◇单向数据Lane○ Master:HS-TX, LP-TX○ Slave:HS-RX, LP-RX◇双向数据Lane○ Master, Slave:HS-TX, LP-TX, HS-RX, LP-RX, LP-CD3、Lane状态和电压◆ Lane状态◇ LP-00, LP-01, LP-10, LP-11 (单端)◇ HS-0, HS-1 (差分)◆ Lane电压(典型)◇ LP:0-1.2V◇ HS:100-300mV (200mV)4、操作模式◆数据Lane的三种操作模式◇Escape mode, High-Speed(Burst) mode, Control mode◆从控制模式的停止状态开始的可能事件有:◇Escape mode request (LP-11→LP-10→LP-00→LP-01→LP-00)◇ High-Speed mode request (LP-11→LP-01→LP-00)◇ Turnaround request (LP-11→LP-10→LP-00→LP-10→LP-00)◆ Escape mode是数据Lane在LP状态下的一种特殊操作◇在这种模式下,可以进入一些额外的功能:LPDT, ULPS, Trigger◇数据Lane进入Escape mode模式通过LP-11→LP-10→LP-00→LP-01→LP-00◇一旦进入Escape mode模式,发送端必须发送1个8-bit的命令来响应请求的动作◇ Escape mode 使用Spaced-One-Hot Encoding◆超低功耗状态(Ultra-Low Power State)◇这个状态下,lines处于空状态 (LP-00)◆时钟Lane的超低功耗状态◇时钟Lane通过LP-11→LP-10→LP-00进入ULPS状态◇通过LP-10 → TWAKEUP →LP-11退出这种状态,最小TWAKEUP时间为1ms◆高速数据传输◇发送高速串行数据的行为称为高速数据传输或触发(burst)◇全部Lanes门同步开始,结束的时间可能不同。

MIPI-中文协议

对于现代的智能手机来说,其内部要塞入太多各种不同接口的设备,给手机的设计和元器件选择带来很大的难度。

下图是一个智能手机的例子,我们可以看到其内部存储、显示、摄像、声音等内部接口都是各不相同的。

即使以摄像头接口来说,不同的摄像头模组厂商也可能会使用不同的接口形式,这给手机厂商设计手机和选择器件带来了很大的难度。

MIPI (Mobile Industry Processor Interface) 是2003年由ARM,Nokia, ST ,TI等公司成立的一个联盟,目的是把手机内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性. MIPI联盟下面有不同的WorkGroup,分别定义了一系列的手机内部接口标准,比如摄像头接口CSI、显示接口DSI、射频接口DigRF、麦克风 /喇叭接口SLIMbus等。

统一接口标准的好处是手机厂商根据需要可以从市面上灵活选择不同的芯片和模组,更改设计和功能时更加快捷方便。

下图是按照 MIPI的规划下一代智能手机的内部架构.MIPI是一个比较新的标准,其规范也在不断修改和改进,目前比较成熟的接口应用有DSI(显示接口)和CSI(摄像头接口)。

CSI/DSI分别是指其承载的是针对Camera或Display应用,都有复杂的协议结构。

以DSI为例,其协议层结构如下:CSI/DSI的物理层(Phy Layer)由专门的WorkGroup负责制定,其目前的标准是D-PHY。

D-PHY采用1对源同步的差分时钟和1~4对差分数据线来进行数据传输。

数据传输采用DDR方式,即在时钟的上下边沿都有数据传输.D— PHY的物理层支持HS(High Speed)和LP(Low Power)两种工作模式。

HS模式下采用低压差分信号,功耗较大,但是可以传输很高的数据速率(数据速率为80M~1Gbps); LP模式下采用单端信号,数据速率很低(<10Mbps),但是相应的功耗也很低.两种模式的结合保证了MIPI 总线在需要传输大量数据(如图像)时可以高速传输,而在不需要大数据量传输时又能够减少功耗。

006.MIPI扫盲——CSI-2介绍(三)

006.MIPI扫盲——CSI-2介绍(三)目录篇地址:MIPI CSI-2的Low Level Protocol主要有一下特征:•Transport of arbitrary data (Payload independent)•8-bit word size•Support for up to four interleaved virtual channels on the same link•Special packets for frame start, frame end, line start and line end information•Descriptor for the type, pixel depth and format of the Application Specific Payload data•16-bit Checksum Code for error detection.CSI-2的Data Lane的Low Level Protocol数据包的一般形式为:如上图所示,也就是说,CSI-2的数据包有两种:长包和短包。

无论是长包还是短包,包的开头都是SoT(Start ofTransmission),包的结尾都是EoT(End of Transmission)。

此外,长包的SoT之后还有包头(PH,Packet Header),EoT之前还有包尾PF(Packet Footer)。

在两次HS传输过程之间,插入的是LP状态(一般是LP11等Control状态,当然也可以进入Escape状态进行LPDT或者进入UPLS)。

一个长包的基本结构如下图所示:•第一部分是PH,包头:分别由Data ID、16bit的WC和ECC 构成,对应功能如上图所示;•第二部分是包的有效数据;•第三部分是PF,即CHECKSUM;其中,ECC采用的是Hamming Code的方式,可以纠正PH(包头)中一位的错误或者发现两位的错误,具体可以看一下我之前转发的博文:而CHECKSUM采用的则是CCITT的16-bit的CRC校检,即x^16+x^12+x^5+x^0。

mipi csi2标准

mipi csi2标准MIPI CSI-2(Camera Serial Interface 2)是一种用于将摄像头传感器与处理器之间传输图像和控制数据的接口标准。

MIPICSI-2标准定义了一整套硬件和软件接口规范,以确保不同厂商的摄像头和处理器能够互通。

MIPI CSI-2标准包括以下方面的内容:1. 物理层:MIPI CSI-2使用低压差分信号传输(LVDS),通过串行传输方式将图像和控制数据传输到处理器。

支持多通道连接,可以同时传输多个摄像头的数据。

标准规定了传输时钟频率、电压电平和差分信号的编码、调整和解码方式。

2. 数据格式:MIPI CSI-2支持多种数据格式,包括RAW、YUV和RGB格式。

标准规定了各种数据格式的编码方式、位宽和数据排列方式。

3. 控制信号:MIPI CSI-2定义了控制信号的接口规范,包括传输控制信号、触发信号和配置信号。

标准规定了控制信号的编码方式、电平范围和传输协议。

4. 数据包格式:MIPI CSI-2将图像和控制数据分成多个数据包进行传输。

每个数据包包括一个包头和一个数据载荷。

标准规定了数据包的格式、长度和传输顺序。

5. 错误检测和纠正:MIPI CSI-2标准支持错误检测和纠正机制,可以检测和修复传输过程中的错误。

标准规定了错误检测和纠正的算法和流程。

6. 电源和时钟管理:MIPI CSI-2标准定义了电源和时钟管理接口规范,包括电源控制信号和时钟同步机制。

标准规定了电源和时钟管理的操作方式和控制协议。

7. 兼容性和互操作性测试:MIPI CSI-2标准要求设备生产厂商进行兼容性和互操作性测试,以确保不同厂商的摄像头和处理器能够正常工作。

测试内容包括物理层电气特性测试、数据格式和控制信号测试、数据包传输测试和性能测试等。

以上是关于MIPI CSI-2标准的相关参考内容,该标准涵盖了物理层、数据格式、控制信号、数据包格式、错误检测和纠正、电源和时钟管理以及兼容性和互操作性测试等方面的规范。

MIPI CSI 协议介绍

接收机收到包头后,也计算一次ECC,然后与收到的ECC相异或, *若异或结果为0,则说明收到的{WC[15:0], DI[7:0]}无错; *否则,用异或结果查表,若异或结果与表中的某一项相同,则指示相应的位出错,

相应的位取反就得到正确结果; *但若异或结果与表中的任一项都不同,则说明有两位以上出错;

4.3、LANE MANAGEMENT

* LANE MANAGEMENT根据通道的具体配置情况,对已经打包好的数据进行通道管理, 同时准备好相应的时序和同步信号,跟物理层接口对接起来;

双通道情况下数据的传输模式

Start-of-Transmission 传输开始标志位 10’hB8

End-of-Transmission 结束标志位,为 {8{!Byte N-1[7]}}

串行时钟与数据差分传输的过渡时间关系

LP 时的电平是0和1.2V 数据时钟通道 对电压的要求

HS时的共模电平200mV,差模电平时200mV

各个时间参数需要满足以下的要求

UI 的值

数据与时钟的相位关系

数据通道进入和退出SLM(即睡眠模式)的控制:

DATA_LANE TX:(注:进入ULPS之后,将一直保持LP-00状态,直到退出该模式,另 外,三个物理通道(一个时钟通道和两个数据通道)是否进入ULPS模式可由寄存 器分开控制)

Ultra-Low Power State entry command: 00011110

退出Escape模式:

(LP-00,LP-10,LP-11)

数据通道中各种模式转换的状态图

进入各种状态数据通道需要发送的命令

时钟通道中各种模式转换的状态图

五、物理层

CSI-2物理层时钟传输通道结构示意图

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

接收机收到包头后,也计算一次ECC,然后与收到的ECC相异或, *若异或结果为0,则说明收到的{WC[15:0], DI[7:0]}无错; *否则,用异或结果查表,若异或结果与表中的某一项相同,则指示相应的位出错,

相应的位取反就得到正确结果; *但若异或结果与表中的任一项都不同,则说明有两位以上出错;

号和数据类型来标志不同的数据流,比如JPEG数据流中穿插着YUV 缩略图数据流; *16位计数值WC:为长包里面数据域(图像数据)的字节数N;

在短包里面的WC可以默认是0,在有需要的情况下表示是第几帧或 是第几行。 *8位ECC:允许包头中前24位(8位数据标志符+16位计数值)在传输过程中两位出错 被发现、一位错误被纠正; *16位CRC:16bit的循环沉余校验码,可以指示收到的该包数据在传输过程中是否出 错; *每个字节都是低位先传,多字节元素(16位计数值、 16位CRC)也是低字节低位先传。

0x10 – 0x17 Generic Long Packet Data Types

0x18 – 0x1F YUV Data

0x20 – 0x27 RGB Data

0x28 – 0x2F RAW Data

0x30 – 0x37 User Defined Byte-based Data

0x38 – 0x3F Reserved

幁头幁尾、行头行尾的DT值

数据通道数

数据类型

用于数据包

*长包格式:一个长包由32位(4Byte)的包头,N字节的数据域,和16位的CRC构 *短包格式:短包只包含一个32位(4Byte)包头; *包头格式:包头由8位数据标志符+16位计数值+8位ECC构成; *数据标志符DI:由2位虚拟通道号+6位数据类型构成,CSI2可以通过不同的虚拟通道

*对应于同步信号完成并串转换; *HS 状态为高速低压差分信号,传输高速连续串行数据; *LP 状态为低速低功耗信号,传输控制信号和状态信号; *MIPI要求HS 工作在1GHz 的频率下,完成共模信号为0.2v 差模信号为0.2v 的差分 信号的传输; *LP 传递控制信号,要求高电平为1.2v 低电平为0的电平信号输出; *HS 及LP 状态下,输出信号的电学特性要求非常苛刻,具体电学性能的要求可见 附带文档表格。

*同步短包、数据长包: .帧同步短包:每帧图象必须开始于帧开始包(FRAME START PACKET),结束于 帧结束包(FRAME END PACKET); .行同步短包是可选的,对于RGB、YUV、RAW数据格式,每个数据长包里面必 须包含一整行图象数据,接收端利用WC解出行同步信号。

用于幁头幁尾、行头行尾、以及数据长包的包头

DLANE DP

DLANE Dn

LP_DATA

LP-10

_LANE LP-11 LP-10 LP-00 LP-01 LP-00 01 00 01 00 01 00 10 00 10 00 10 00 10 00 01 00 LP-00 LP-11

Escape 模式 Entry procedure:

(LP-11,LP-10,LP-00,LP-01,LP-00)

串行时钟与数据差分传输的过渡时间关系

LP 时的电平是0和1.2V 数据时钟通道 对电压的要求

HS时的共模电平200mV,差模电平时200mV

各个时间参数需要满足以下的要求

UI 的值

数据与时钟的相位关系

数据通道进入和退出SLM(即睡眠模式)的控制:

DATA_LANE TX:(注:进入ULPS之后,将一直保持LP-00状态,直到退出该模式,另 外,三个物理通道(一个时钟通道和两个数据通道)是否进入ULPS模式可由寄存 器分开控制)

*可以看出,对于Raw10,需要把10bit的数据转换成8bit的数据,需要进行时钟域转换, Raw10字节打包后的时钟频率=打包前的1.25倍; *其他格式的打包前后时钟频率相同;

4.2、 LLP(Low Level Protocol) 层:

*LLP层是一个面向字节的,基于包的协议;它支持任意大小的数据通过短包和长包 格式传输。各个包之间由EOT-LPS-SOT序列隔开。

4. 应用举例(2通道):

5. 发送端结构:

6. 接收端结构:

7. 总体结构:

应用层

CSI2 协议层

D-PHY 物理层

板级传 输,

连线延时 不能超过 2ns!!

应用层

CSI2 协议层

D-PHY 物理LP(Low Level Protocol) 层是一个面向字节的,基于包的协议;所以 在LLP之前必须进行字 节打包; *针对除了Raw8、JPEG8等几种数据本身是8bit的外, Raw10、YUV422、RGB565、RGB555、 RGB444等都需要特定的数据顺序: * YUV422 :CB0Y0CR0 Y1 CB2Y2CR2 Y3 CB4Y4CR4 ……… * RGB565:{G[4:2], B[7:3]}, {R[7:3], G[7:5]} ……… * RGB555:{G[4:3],1’B0, B[7:3]}, {R[7:3], G[7:5]} ……… * RGB444:{G[4],2’B10, B[7:4], 1’B1}, {R[7:4], 1’B1, G[7:5]} ……… * Raw10 : D0[9:2],D1[9:2],D2[9:2] D3[9:2], {D3[1:0],D2[1:0],D1[1:0] ,D0[1:0]}, D4[9:2],D5[9:2], D6[9:2],D7[9:2], {D7[1:0],D6[1:0],D5[1:0] ,D4[1:0]} ……….. ………

Ultra-Low Power State entry command: 00011110

退出Escape模式:

(LP-00,LP-10,LP-11)

数据通道中各种模式转换的状态图

进入各种状态数据通道需要发送的命令

时钟通道中各种模式转换的状态图

五、物理层

CSI-2物理层时钟传输通道结构示意图

物理层时钟传输通 道控制及输出接口

{DI[7:0],WC[15:0]}为24位,由2‘b00和6位监督位组成: 对24位的标准公式: P7=0, P6=0, P5=D10^D11^D12^D13^D14^D15^D16^D17^D18^D19^D21^D22^D23, P4=D4 ^D5 ^D6 ^D7^D8^D9^D16^D17^D18^D19^D20^D22^D23, P3=D1^D2^D3^D7^D8^D9^D13^D14^D15^D19^D20^D21^D23, P2=D0^D2^D3^D5^D6^D9^D11^D12^D15^D18^D20^D21^D22, P1=D0^D1^D3^D4^D6^D8^D10^D12^D14^D17^D20^D21^D22^D23, P0=D0^D1^D2^D4^D5^D7^D10^D11^D13^D16^D20^D21^D22^D23;

* 数据标志符由两位虚拟通道号和6位数据类型构成,

.虚拟通道允许最多四个数据流交叉传输,(比如JPEG数据流中穿插着YUV

缩略图数据流);

.6位数据类型允许8类64种数据类型:

0x00 – 0x07 Synchronization Short Packet Data Types

0x08 – 0x0F Generic Short Packet Data Types

CSI-2物理层数据传输通道结构示意图

物理层数据传输通道 控制及数据输出接口

MIPI 传输的物理层,实现MIPI 协议的数据串行传输。 此物理层的接口分为输入和输出两种接口,现只讨论接口电路模块,在我们芯片内 部只用到输出接口。协议中数据传输有不同的模式,接口电路也有不同的应用。 在我们的芯片状态(L中会用到两种状态机,LP ow Power)和HS 状态(High Speed)。

4.3、LANE MANAGEMENT

* LANE MANAGEMENT根据通道的具体配置情况,对已经打包好的数据进行通道管理, 同时准备好相应的时序和同步信号,跟物理层接口对接起来;

双通道情况下数据的传输模式

Start-of-Transmission 传输开始标志位 10’hB8

End-of-Transmission 结束标志位,为 {8{!Byte N-1[7]}}

•完成通道分配后,需要生成与物理层对接的时序、同步信号: MIPI规定,传输过程中,包内是200mV、包间以及包启动和包结束时是1.2V,两种不同的电 压摆幅,需要两组不同的LVDS驱动电路在轮流切换工作;为了传输过程中各数据包之间的 安全可靠过渡,从启动到数据开始传输,MIPI定义了比较长的可靠过渡时间,加起来最少也 有600多ns;而且规定各个时间参数是可调的,所以需要一定等待时间,需要缓存,我们用 寄存器代替FIFO,每通道128Byte。

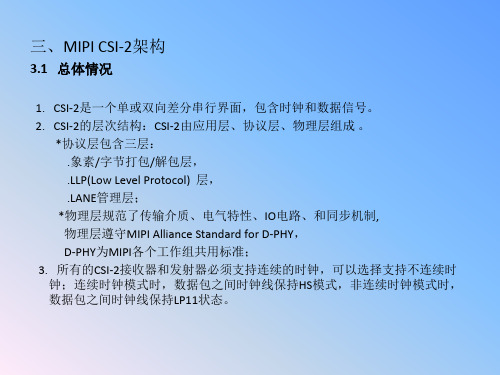

*物理层规范了传输介质、电气特性、IO电路、和同步机制, 物理层遵守MIPI Alliance Standard for D-PHY, D-PHY为MIPI各个工作组共用标准; 3. 所有的CSI-2接收器和发射器必须支持连续的时钟,可以选择支持不连续时 钟;连续时钟模式时,数据包之间时钟线保持HS模式,非连续时钟模式时, 数据包之间时钟线保持LP11状态。

* 16位CRC循环沉余校验码:可以指示收到的该包数据在传输过程中是否出错; CSI2里面采用CRC16 CCITT:生成多项式g(x)=x^16+x^12+x^5+1

CRC[0] = Data[0] ^ Data[4] ^ CRC[0] ^ CRC[4] ^ CRC[8] ; CRC[1] = Data[1] ^ Data[5] ^ CRC[1] ^ CRC[5] ^ CRC[9] ; CRC[2] = Data[2] ^ Data[6] ^ CRC[2] ^ CRC[6] ^ CRC[10] ; CRC[3] = Data[0] ^ Data[3] ^ Data[7] ^ CRC[0] ^ CRC[3] ^ CRC[7] ^ CRC[11] ; CRC[4] = Data[1] ^ CRC[1] ^ CRC[12] ; CRC[5] = Data[2] ^ CRC[2] ^ CRC[13] ; CRC[6] = Data[3] ^ CRC[3] ^ CRC[14] ; CRC[7] = Data[0] ^ Data[4] ^ CRC[0] ^ CRC[4] ^ CRC[15] ; CRC[8] = Data[0] ^ Data[1] ^ Data[5] ^ CRC[0] ^ CRC[1] ^ CRC[5] ; CRC[9] = Data[1] ^ Data[2] ^ Data[6] ^ CRC[1] ^ CRC[2] ^ CRC[6] ; CRC[10] = Data[2] ^ Data[3] ^ Data[7] ^ CRC[2] ^ CRC[3] ^ CRC[7] ; CRC[11] = Data[3] ^ CRC[3] ; CRC[12] = Data[0] ^ Data[4] ^ CRC[0] ^ CRC[4] ; CRC[13] = Data[1] ^ Data[5] ^ CRC[1] ^ CRC[5] ; CRC[14] = Data[2] ^ Data[6] ^ CRC[2] ^ CRC[6] ; CRC[15] = Data[3] ^ Data[7] ^ CRC[3] ^ CRC[7] ;