数电课设--带proteus仿真的电子秒表设计

基于数字电路的电子秒表课程设计报告

基于数字电路电子秒表课程设计摘要电子秒表是一种用数字电路技术实现时、分、秒计时的装置,无机械装置,具有较长的使用寿命,因此得到了广泛的使用。

它从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

本次实验所做电子式秒表由信号发生系统和计时系统构成,并具有清零,暂停功能。

由于需要比较稳定的信号,所以信号发生系统555定时器与电阻和电容组成的多谐振荡器构成,信号频率为100HZ。

计时系统由计数器、译码器、显示器组成。

计数器由74 LS160构成,由十进制计数器组成了一百进制和六十进制计数器,采用异步进位方式。

译码器由74LS48构成,显示器由数码管构成。

清零,暂停功能由RS触发器构成防抖动开关。

具体过程为:由晶体震荡器产生100HZ脉冲信号先进入计数器,然后传入译码器,将4位信号转化为数码管可显示的7位信号,结果以“分”、“秒”、“10毫秒”依次在数码管显示出来。

该秒表最大计时值为59分59.99秒,“10毫秒”为一百进制计数器组成,“分”和“秒”为六十进制计数器组成。

关键词:计时精度计数器显示器AbstractElectronic stopwatch is the realization of a digital circuit technology,.It can realize the hour, minute, second timer.It does not have mechanical means and has a longer life, so it has been widely used. The principle is a typical digital circuit, which includes a combination logic circuit and a timing circuit. The experiments can be done by electronic stopwatch constituted by the signal system and timing system, and has cleared pause function. Due to the need of a more stable signal, the signal generating system is constituted by the 555 Timer with the resistors and capacitors, and the signal frequency is 100Hz. Timing system contains the counter, decoder, display. Counter 74 LS160 constituted by the decimal counter the decimal and sexagesimal counter, which uses asynchronous binary. The decoder from 74LS48 constitute display digital tube constitute Cleared, the pause function by the RS flip-flop. Its specific process: the 100Hz pulse signal generated by the crystal oscillator and first into the counter, and then the incoming decoder, a 4-bit signal is converted to 7-bit signal of the digital control can be displayed, the result by "minute", "second", "10 milliseconds" turn on the digital display. The stopwatch timing is 59 minutes, 59.99 seconds, 10 milliseconds is the 150 binary counter, "minute" and "second" is the six decimal counter.Keyword:Timing accuracy counter display目录一、设计任务与要求 (2)二、方案设计与论证 (2)三、单元电路设计与参数计算 (4)1.信号发生器单元电路 (4)2.时钟分频计数单元电路 (6)3.显示及译码单元电路 (11)4.控制电路 (13)四、总原理图及元器件清单 (14)五、结论与心得 (17)六、参考文献 (18)一、设计任务与要求用74系列数字器件设计一个电子秒表,要求:1.以0.01秒为最小单位进行显示。

数电课设--带proteus仿真的电子秒表设计说明

工业大学课程设计课程:数电课程设计题目:电子秒表专业班级: 通信工程1003班学号: 100404308、309、315 学生: 路、智佳、吴开来指导教师: 柏山完成时间: 2013年6月25日目录第1章设计要求.................................. 第2章设计方案.................................. 第3章总电路设计思路..................... 第4章分解电路的设计及说明......... 第5章电路的仿真 ............................. 第6章设计总结及心得体会............. 参考文献: ............................................ 附录:.....................................................第1章设计要求结合数字逻辑电路知识,设计或分析下述功能电路,利用Proteus软件对电路进行功能仿真,并基于仿真结果对电路进行功能改进。

给出仿真机及分析过程及结果。

设计参数:1.设计可控的计数器(定时器)、分频器、键去抖电路和动态扫描显示电路;2.设计系统顶层电路;3.进行功能仿真和时序仿真;4.对仿真结果进行分析,确认仿真结果达到了设计要求:1.分析设计要求,明确性能指标。

必须仔细分析课题要求、性能、指标及应用环境等,广开思路,构思出各种总体方案,绘制结构框图。

2.确定合理的结构方案,对各种方案进行比较,以电路的先进性、结构的繁简、成本的高低及制作的难易等方面作综合比较并考虑器件的来源,敲定可行方案。

3.设计各单元电路。

总体方案化整为零,分解成若干子系统或单元电路,逐个设计。

4.组成系统。

在一定幅面的图纸上合理布局,通常是按信号的流向,采用左进右出的规律摆放各电路,并标出必要的说明。

第2章设计方案方案一:实现秒表的功能有很多种,该方案采用的是用555定时器产生一个1000HZ的秒脉冲,然后通过分频电路接到延时电路上,跟一个去抖电路连接在一起,输出给74160做触发信号,与另一个74160连接组成,然后把输出端分别连接到7448译码器上,通过共阴极七段数码管来显示结果,算选用的器件便宜,精度小于5%,可实现0-59秒的计时,另有启动、暂停、和清零三个功能。

数电课程设计:电子秒表

数电课程设计:电子秒表

电子秒表是一种常见的计时工具,它通过使用电子元件实现高精度的计时功能。

下面是一个基于数电的电子秒表的设计方案:

1. 运算部分设计:

- 使用一个1Hz的时钟源,可以通过计数器或者振荡器实现。

- 使用一个可重置的二进制计数器,位数根据需要的计时范

围确定。

例如,如果计时范围为1小时,可使用一个4位二进制计数器。

- 计时开始/停止控制逻辑:这可以通过一个开关电路实现,可以使用一个门电路或者触发器电路。

- 计数器重置逻辑:可以使用一个按钮或者开关来重置计数

器的值。

2. 显示部分设计:

- 使用数码管或者液晶显示器来显示计时结果。

数码管可以

使用共阳或者共阴的7段数码管。

- 使用译码器将计数器的二进制输出转换为译码信号,用于

控制数码管显示的数字。

3. 其他功能:

- 可以添加一个暂停功能,通过一个按钮或者开关来实现。

当计时中按下暂停按钮时,计时器会停止计数,再次按下暂停

按钮时,计时器继续计数。

- 可以添加一个拆表功能,通过一个按钮或者开关来实现。

按下拆表按钮时,计时器会记录当前的计时值,然后重置为0,再次按下拆表按钮时,计时器恢复原来的计时状态。

该设计方案中的电子秒表可根据实际需求进行调整和扩展,例如增加更多的功能按钮、调整计时范围和精度等。

同时,需要注意电路的稳定性和可靠性,以及对供电电源和信号的处理。

基于Proteus仿真实现秒表电路仿真实验

基于Proteus仿真实现秒表电路仿真实验基于Proteus仿真实现秒表电路仿真实验⼀、实验⽬的99秒表设计⼀个00~~99的2位秒表,⽤单⽚机控制2个LED静态显⽰。

⼆、实验要求1、绘图必须规范、严谨,可以不拘⼀格,但要求仿真成功。

2、不得相互拷贝和抄袭,每个仿真电路图下⾯写上电路名称及⾃⼰的班级、学号姓名。

3、Proteus仿真图、相应的源程序(⽤到单⽚机的项⽬)、Word⽂档实训报告均以电⼦版形式上交。

三、仿真电路分析单⽚机有4个并⾏I/O⼝ P0-P3,每个I/O⼝包括8条I/O⼝线。

采⽤P0⼝、P1⼝来控制2个共阳极LED的段码,我们⽤的是共阴数码管,所以公共端接地,P0⼝控制的LED显⽰⼗位数,P1⼝控制的LED显⽰个位数,从0开始显⽰。

显⽰到99后,从新从0开始显⽰。

四、实训结果五、实训⼼得99秒表调⽤了单⽚机中,⾃带的(定时器/计时器)系统,是学习单⽚机所必须了解的⼀个模块,这是⼀次基本的应⽤,也⽐较简单,但是在接下来的学习中还要针对系的学习,(定时器/计时器)应⽤的还是⽐较的⼴泛。

还要好好学习。

六、附页Keil程序#includevoid time59ms(unsigned char i) {unsigned char k;for(k=0;k{TH0=(65536-9000)/256;TL0=(65536-9000)%256;TR0=1;while(!TF0);TF0=0;}}void main(){ unsigned charled[]={ 0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0 x07,0x7f,0x6f};unsigned char i;TMOD=0x01;P0=0xff;P2=0xff;while(1){for(i=0;i<100;i++) { P0=led[i/10];P2=led[i%10]; time59ms(90);}}}。

数电课程设计--带proteus仿真的电子秒表设计(00.00····99.99)

沈阳工业大学课程设计课程:数电课程设计题目:电子秒表专业班级: 通信工程1003班学号: *********、309、315 学生姓名: 张路、刘智佳、吴开来****: ***完成时间: 2013年6月25日目录第1章设计要求 ................................ 第2章设计方案 ................................ 第3章总电路设计思路 .................... 第4章分解电路的设计及说明 ........ 第5章电路的仿真 ............................ 第6章设计总结及心得体会 ............ 参考文献: .......................................... 附录:...................................................第1章设计要求结合数字逻辑电路知识,设计或分析下述功能电路,利用Proteus软件对电路进行功能仿真,并基于仿真结果对电路进行功能改进。

给出仿真机及分析过程及结果。

设计参数:1.设计可控的计数器(定时器)、分频器、键去抖电路和动态扫描显示电路;2.设计系统顶层电路;3.进行功能仿真和时序仿真;4.对仿真结果进行分析,确认仿真结果达到了设计要求:1.分析设计要求,明确性能指标。

必须仔细分析课题要求、性能、指标及应用环境等,广开思路,构思出各种总体方案,绘制结构框图。

2.确定合理的结构方案,对各种方案进行比较,以电路的先进性、结构的繁简、成本的高低及制作的难易等方面作综合比较并考虑器件的来源,敲定可行方案。

3.设计各单元电路。

总体方案化整为零,分解成若干子系统或单元电路,逐个设计。

4.组成系统。

在一定幅面的图纸上合理布局,通常是按信号的流向,采用左进右出的规律摆放各电路,并标出必要的说明。

第2章设计方案方案一:实现秒表的功能有很多种,该方案采用的是用555定时器产生一个1000HZ的秒脉冲,然后通过分频电路接到延时电路上,跟一个去抖电路连接在一起,输出给74160做触发信号,与另一个74160连接组成,然后把输出端分别连接到7448译码器上,通过共阴极七段数码管来显示结果,算选用的器件便宜,精度小于5%,可实现0-59秒的计时,另有启动、暂停、和清零三个功能。

数电课程设计--数字秒表

数字电子技术课程设计题目:电子秒表的设计专业: 08自动化(1)班学号: ************ *名:***完成日期: 2010.12.30 指导教师:姚杰老师数字电子技术课程设计任务书班级:08自动化一班姓名:谢志平指导教师:姚杰 2010年12月28日教研室主任签字:年月日目录1 引言 (4)2 设计方案及系统框图2.1 设计方案 (5)2.2系统框图 (5)3 单元电路设计3.1 消抖电路 (6)3.2 上电复位电路 (6)3.3 微分电路 (7)3.4 0.1秒脉冲电路 (7)3.5 计数器电路 (8)3.6 译码电路 (9)3.7 七段译码管电路 (10)4总体电路设计4.1各单元电路工作原理 (11)4.2 电路工作原理 (11)5课程设计总结 (13)6参考文献 (14)7电子秒表原理图元器件明细表 (15)8总电路图 (16)1 引言随着电子技术的发展,电子技术在各个领域的运用也越来越广泛。

人们对他的认识也逐步加深,不断完善电子秒表的功能,人们也利用了电子技术以及相关的知识解决了一些实际问题。

电子秒表广泛应用于对运动物体的速度、加速度的测量实验,还可用来验证牛顿第二定律、机械能守恒等物理实验,同时也是用于对时间测量精度要求较高的场合。

数字测量仪表不仅比模拟测量仪表精度高、能强,而且容易实现测量的自动化和自能化。

随着集成计数的发展,数字电子技术的应用范围将会更广泛的渗透到国民经济的各个部门,并将产生越来越深刻的影响。

电子秒表用微型电池作能源,电子元件测量显示,可精确至千分之一秒,广泛应用于科学研究、体育运动以及国防等方面。

在当今非常注重工作效率的社会环境中,定时器能给我们的工作、生活娱乐带来很大的方便,充分利用定时器,能有效地加强我们的工作效率。

随着电子科技的迅速发展,要求我们要理论联系实际。

数字电路课题设计的进行,使我们我们的动手和实际操作能力得到了一定程度的提升,而不是单纯的学习理论。

数字电子技术课程设计-数字秒表

数字电子技术课程设计报告课程设计(大作业)报告课程名称:数字电子技术设计题目:数字秒表院系:信息技术学院班级:设计者:学号:指导教师:**设计时间:2015.12.14--2015.12. 18 信息技术学院昆明学院课程设计(大作业)任务书目录一、设计目的 (1)二、设计要求和设计指标 (1)三、设计内容 (1)3.1电子秒表工作原理 (1)3.1.1总体设计 (2)3.1.2 脉冲电路设计 (2)3.1.3总清零控制电路 (6)3.1.4时间计数单元 (6)3.1.5分频电路 (8)3.1.6码驱动及显示单元 (9)3.1.7多功能数字秒表电路的组合 (10)3.2仿真结果与分析 (12)3.2.1 时钟发生器的测试 (12)3.2.2 计数、译码、显示单元的测试 (13)3.2.3 整体测试 (13)3.2.4 电子秒表准确度的测试 (14)四、本设计改进建议 (14)五、总结 (15)六、主要参考文献 (16)一、设计目的1、学习数字电路中基本RS触发器、单稳态触发器、时钟发生器及计数、译码显示器等单元电路的综合应用。

2、学习电子秒表的调试方法。

3、秒表由五位七段LED显示器显示,其中一位显示“min”,四位显示“s”,其中显示分辨率为0.01s,计时范围为0~9分59秒99毫秒;具有清零、启动计时、暂停计时及继续计时等功能;控制开关为两个;启动(继续)/暂停计时开关和复位开关。

二、设计要求和设计指标制作一个数字秒表,将单个数字秒表组合设计成可以同时对多人进行计时的多人数字秒表。

电子秒表的工作原理就是不断输出连续脉冲给加法计数器,而加法计数器通过译码器来显示它所记忆的脉冲周期个数。

1.时钟发生器:利用石英震荡555定时器构成的多谐振荡器做时钟源,产生脉冲。

2.记数器:对时钟信号进行记数并进位,百分之一秒和十分之一秒以及个位秒之间10进制,十位秒为六进制; 本设计采用可预置的十进制同步加法计数器74LS90构成电子秒表的计数单元。

单片机基于PROTEUS仿真的秒表的课程设计

1 引言1.1 课程设计的目的1) 通过本次课程设计加深对单片机课程的全面认识和掌握,对单片机课程的应用进一步的了解。

2) 通过本次课程设计将单片机软硬件结合起来,对程序进行编辑,校验,锻炼理论联系实际的能力。

3) 综合运用《单片机原理及应用》课程的理论知识、与设计课题相关的参考资料、基本开发仪器及工具和实验室所具有的其它软硬件环境,设计一个典型的单片机应用系统并通过仿真调试出结果。

4) 通过本次课程设计提高学生的综合能力、动手能力、文献资料查阅能力,为毕业设计和以后工作打下一个良好的基础。

1.2 课程设计的任务用Proteus仿真MCS51系列单片机及其外围电路,用它与Keil开发工具结合,搭建单片机开发平台。

设计一个单片机控制的秒表系统。

利用单片机的定时器/计数器定时和记数的原理,结合显示电路、LED数码管以及按键来设计秒表计时器。

基本功能要求:用AT89C51设计一个2位LED数码显示“秒表”,开始时,显示“00”:第一次按下SP1后就开始从0~9.9计时,显示精度为0.1s;第二次按SP1后,计时停止,显示当前计时值;第三次按SP1后,及时停止归零。

1.3 课程设计的要求1)硬件设计:根据任务要求,完成单片机最小系统及其扩展设计,组成功能完整的系统;2)软件设计:根据秒表的设计要求,完成控制软件的编写与调试;3)用PROTEUS ARES绘制电路原理图并生成PCB图;4)PROTEUS仿真。

2 硬件设计2.1 设计方案介绍及工作原理说明该实验要求进行计时并在数码管上显示时间,则可利用proteus仿真软件设计电路并仿真AT89C51。

使用AT89C51单片机作为核心控制部件,采用12M晶体振荡器及微小电容构成振荡电路;用两个共阴极数码显示管作为显示部分,构成数字式秒表的主体结构,配合独立式键盘和复位电路完成此秒表的计时、清零、停止各项功能。

对于时钟,它有两方面的含义:一是指为保障系统正常工作的基准振荡定时信号,主要由晶振和外围电路组成,晶振频率的大小决定了单片机系统工作的快慢;二是指系统的标准定时时钟,即定时时间,是用软件实现,即用单片机内部的可编程定时/计数器来实现,但误差很大。

数电课程设计-数字电子秒表设计

数电课程设计-数字电⼦秒表设计理学院School of Sciences创新课程设计报告学⽣姓名:学⽣学号:所在班级:电⼦092所在专业:电⼦信息科学与技术指导教师:数字电⼦秒表设计1. 引⾔电⼦秒表在⽣活中的应⽤,它可⼴泛应⽤于对运动物体的速度、加速度的测量实验,还可⽤来验证⽜顿第⼆定律、机械能守恒等物理实验,同时也适⽤于对时间测量精度要求较⾼的场合.测定短时间间隔的仪表。

有机械秒表和电⼦秒表两类。

机械秒表与机械⼿表相仿,但具有制动装置,可精确⾄百分之⼀秒;电⼦秒表⽤微型电池作能源,电⼦元件测量显⽰,可精确⾄千分之⼀秒。

⼴泛应⽤于科学研究、体育运动及国防等⽅⾯在当今⾮常注重⼯作效率的社会环境中,定时器能给我们的⼯作、⽣活以及娱乐带来很⼤的⽅便,充分利⽤定时器,能有效的加强我们的⼯作效率。

数字电⼦秒表是利⽤数字电⼦技术把模拟信号转换成数字信号来完成的,具有直观、准确性⾼的特点。

1.1 设计⽬的1.建⽴数字电⼦电路系统的基本概念;2.运⽤CD4060分频器的应⽤,计数器的级联及其计数、译码、显⽰电路的整体配合;3.建⽴分频的基本概念。

1.2 设计要求设计⼀个数字电⼦秒表,该秒表具有显⽰功能和清零、开始计时、停⽌计时等功能。

设计的要求如下:1.以1秒为最⼩单位进⾏显⽰;2.秒表可显⽰0~9秒的量程;3.该秒表具有清零、开始计时、停⽌计时功能;4.除了以上功能,个⼈可根据具体情况进⾏电路功能扩展。

1.3 设计内容1.搭接电⼦秒表的整体设计电路;2.校准0.1秒信号源;3.测试电⼦秒表清零、开始计时、停⽌计时功能。

2. 电路分析图2.1.1 电⼦秒表电路图图2.1.1是电⼦秒表完全的电路图,按功能可以分成四个单元电路进⾏分析,由时钟脉冲发⽣器、计算器、译码器和数码管组成。

其原理⽅框图如图2.2.1所⽰。

2.2.1 时钟脉冲发⽣器555 定时器是模拟 — 数字混合式集成电路,利⽤它可以⽅便地构成脉冲产⽣、整形电路和定时、延时电路。

数电课程设计报告(数字电子时钟秒倒计时)

课程设计任务书2011 —2012学年第1学期电气与信息工程学院学院(系、部)自动化专业班级课程名称:电子技术设计题目:数字电子时钟及篮球24秒计时器完成期限:自2012年1月2日至2012年1月9日共1周指导教师(签字):年月日系(教研室)主任(签字):年月日电子技术课程设计课题一数字电子时钟一、设计目的:1、熟悉集成电路的引脚安排和各芯片的逻辑功能及使用方法2、了解数字电子钟的组成及工作原理3、熟悉数字电子钟的设计与制作二、设计内容和要求:设计一个数字电子钟,具体要求:1、以24小时为一个计数周期;2、具有“时”、“分”、“秒”数字显示;3、数码管显示电路;4、具有校时功能;5、整点前10秒,数字钟会自动报时,以示提醒;6、用PROTEUS画出电路原理图并仿真验证;三、设计思路:1、首先设计一个秒脉冲产生电路,可采用555定时器构成多谐振荡器,通过设计多谐振荡器电阻、电容的参数大小,使555定时器输出一个固定频率为1HZ的方波;2、设计计时电路,计时电路即是计数电路,通过计数器集成芯片如:74LS161、74LS 163、74LS 192等完成对秒脉冲的计数,其中要重点考虑所选择的计数器芯片的进制问题。

秒钟个位计到9进10时,秒钟个位回0,秒钟十位进1,秒钟计到59,进60时,秒钟回00,分钟进1…,以此类推,完成全部计时设计;(可通过添加相应的与非门电路,使计数器按照要求回0)3、显示电路,根据EWB或PROTEUS元器件库中数码管的不同,有四个引脚的(显示二进制)、有8个引脚的(显示8段位码,需要添加译码芯片),完成计数结果的输出显示。

4、校准电路通过RS触发器及与非门对“时”和“分”进行校准的电路如图1所示。

下面以校“分”电路来说明校准电路的原理:①正常计数时,G1门开,秒脉冲进行单位产生的分脉冲可通过G1,G3(开门状态)送入分计数器,此时G2封锁,校准脉冲(即秒脉冲)进不去。

②按下S1则G1封锁,“分”脉冲受阻,而G2打开,秒脉冲进入分计数器进行快速计数(即较分),校时电路与此完全相同。

数字电子技术课程设计--电子秒表的设计

数字电子技术课程设计--电子秒表的设计数字电子技术课程设计课程设计题目:电子秒表的设计目录摘要 (2)1引言 (3)1.1设计目的 (3)1.2技术要求 (3)1.2.1基本要求 (3)1.2.2提高要求 (3)1.3设计内容 (3)1.4工作原理 (3)2设计框图 (4)3各个部分功能简介 (5)3.1按键去抖电路 (5)3.2控制器电路 (6)3.3时钟产生电路 (8)3.4计时电路 (9)3.5显示译码电路 (10)3.6 50000分频电路 (11)4硬件仿真 (13)4.1顶层逻辑图 (13)4.2LB0介绍 (14)4.3硬件仿真 (14)5课程设计的心得体会 (15)参考文献 (16)附录 (17)摘要本文以数字电子技术作为理论基础、以quartusⅡ软件为开发平台、以相关电路知识作为辅助,实现电子秒表电路的设计和制作。

该电子秒表可以准确显示时间,范围为00.00—99.99。

并且可以手动调节时间,随时启动、清零、暂停记录时间等。

操作起来简易、方便。

首先,本文针对电子秒表进行初步框架设计,并在对多种方案进行了认真比较和验证的基础上,又进一步详细介绍了时间脉冲发生器、秒计数器、译码及驱动显示电路。

其次,在总体电路图组装完成以后,用quartusⅡ软件对设计好的电路进行了仿真与调试,并逐一解决设计过程中出现的一系列问题。

最后,对照着电子秒表设计方案,对制作好的电子秒表功能进行总体验证。

并利用学院的LB0开发板进行硬件仿真。

关键词:电子秒表计数器分频quartusⅡ、1引言1.1设计目的1)掌握同步计数器74160,74161的使用方法,并理解其工作原理。

2)掌握用74160,74161进行计数器、分频器的设计方法。

3)掌握用三态缓冲器74244和74160,74138,7448进行动态显示扫描电路设计的方法。

4)掌握电子秒表的设计方法。

5)掌握在EDA系统软件MAX + plus Ⅱ环境下用FPGA/CPLD进行数字系统设计的方法,掌握该环境下功能仿真、时序仿真、管脚锁定和芯片下载的方法。

数电课程设计电子秒表

电子电路课程设计题目名称:电子秒表课程设计姓名:学号:专业班级:一.设计任务及功能简介(1)显示分辨率为1s/100,外接系统时钟频率为100KHz。

(2)计时最长时间为1h,六位显示器,显示时间最长为59m59.99s。

系统设置启/停键和复位键。

复位键用来消零,做好计时准备、启/停键是控制秒表起停的功能键二.设计框原理三.各单元电路的设计及使用说明1.启动和停止单元电路由一个开关控制CP脉冲,从而控制秒表的启动与停止2.秒脉冲电路LM555CN定时器构成的多谐振荡器,是一种性能较好的时钟源。

该脉冲电路产生100KHz的脉冲(MULTISIM仿真太慢,调快了频率)3. 100进制计数器由两片74ls160级联组成,采用了串行的方式,低位片的进位端RCO接低位片的CLK端。

4. 60进制计数器60进制计数器采用串行整体置数的方式级联,将电路的59状态译码产生的低电平信号接到两片计数器的同步置数端,当下一个脉冲到来的时候同时把0000置入两片74ls160计数器中,从而得到六十进制计数器。

5.计数与译码显示十进制加法计数器74LS160构成电子秒表的计数单6.电子秒表总设计图四.主要芯片介绍1.74LS00Inputs输入Ouput输出74LS00功能为四2 输入与非门A B Y其真值表及管脚图为:L L HL H HH L HH H L2.74LS16074LS160 十进制同步计数器(异步清零)其真值表如下( H:高电平,L:低电平,↑:上升沿,X:任意,D0 ~D3 :A~D稳态输入电平)输入输出Cr LD S1 S2 CP A B C D QA QB QC QDL X X X X X X X X L L L LH L X X↑D0 D1 D2 D3 D0 D1 D2 D3H H H H↑X X X X 计数H H L X X X X X X 保持H H X L X X X X X 保持五.总电路的仿真在仿真的过程中遇到过很多的问题,比如六十进制计数器计数到五十的时候高位片出现进位等,这些问题的出现是由于对任意进制计数器的组成、上升沿触发还是下降沿触发没理解透彻而导致的细节性问题。

数字电子技术课程设计(电子秒表)

数字电子技术课程设计报告题目:电子秒表的设计专业:班级:姓名:指导教师:课程设计任务书学生班级:学生姓名:学号:设计名称:电子秒表的设计起止日期:指导教师:周珍艮目录绪论- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 4 第一章、设计要求1.1设计任务及目的- - - - - - - - - - - - - - - - - - - - - - -- - - - - - - - -51.2 系统总体框图- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 51.3、设计方案分析- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -6第二章、电路工作原理及相关调试2.1 电路工作原理- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 72.1相关调试- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -- 11第三章、实验总结附录A 电子秒表原理图附录B 相关波形元件清单参考文献绪论随着电子技术的发展,电子技术在各个领域的运用也越来越广泛,渗透到人们日常生活的方方面面,掌握必要的电工电子知识已经成为当代大学生特别是理工类大学生必备的素质之一。

电子秒表是日常生活中比较常见的电子产品,秒表的逻辑结构主要由时基电路、分频器、二一五一十进制异步加法记数器、数据选择器和显示译码器等组成。

整个秒表需有一个清零/ 启动信号和一个停止/保持信号装置,以便秒表能随意停止及启动,计数器的输出全都为BCD码输出,方便显示译码器连接。

基于Proteus软件仿真的秒表时钟设计

基于 Proteus软件仿真的秒表时钟设计摘要:Proteus软件是一款强大的EDA软件,可以用来仿真单片机及外围器件,通过搭建电路即可进行仿真,测试控制系统的功能。

利用Proteus软件仿真秒表时钟系统,可以十分方便的优化硬件结构以及修改程序,以便能够制造出性能更加强大的设备。

【1】关键词:Proteus,仿真,单片机一个完整的系统需要包括硬件、软件等方面的设计,在本文中分别进行了讨论,并根据相关功能列出对应的程序。

一、硬件电路图及工作原理描述1)单片机最小系统:由AT89C52单片机芯片及其外部电路组成。

芯片有成品可直接购买,外围电路(复位电路和晶振电路)需要搭建。

复位电路可实现单片机复位,回到初始状态,主要由充电电容和复位按钮组成;晶振电路可为单片机提供动力,驱动单片机工作,主要由晶振和电容组成。

2)数码管显示电路:由4个2位共阴极数码管组成,其段选端连接单片机的位置相同,共用I/O口,而位选端连接到单片机不同的I/O。

给位选端高电平选中所需数码管,再给段选端不同口发光二极管高低电平,显示不同数字。

3)蜂鸣器和按键电路:在蜂鸣器控制电路中,控制NPN的开关即可控制蜂鸣器的导通。

在按键电路中,只要开关按下就可以将单片机I/O接地,输入低电平。

图1 秒表系统总电路二、软件功能对应实现程序1)秒表以0.1S精度开始计时,用定时器0实现,首先要给定时器装初值,计数满溢出进入中断。

计时精度程序:2)秒表启动停止是由key0按键控制,如果按下导通接地,则TR0=1,启动定时器,开始计时。

秒表清0则由key1控制,如果按下导通接地,times等计数显示值均为0.启停程序:清0程序:3)计时一分钟提醒,主要是判断计时变量timemin是否加1,如果加1蜂鸣器响一段时间。

一分钟提醒程序:4)秒表的最长计时长度为1:59:59,超过此长度,报警,主要是判断计时变量timeh是否将要达到2,如果达到最大值,蜂鸣器响,数码管闪烁。

电子跑秒表计时器设计——基于PROTEUS

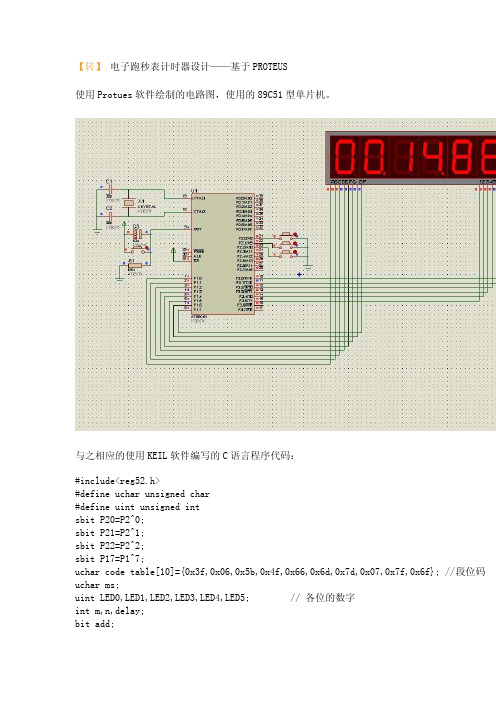

【转】电子跑秒表计时器设计——基于PROTEUS使用Protues软件绘制的电路图,使用的89C51型单片机。

与之相应的使用KEIL软件编写的C语言程序代码:#include<reg52.h>#define uchar unsigned char#define uint unsigned intsbit P20=P2^0;sbit P21=P2^1;sbit P22=P2^2;sbit P17=P1^7;uchar code table[10]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f}; //段位码uchar ms;uint LED0,LED1,LED2,LED3,LED4,LED5; // 各位的数字int m,n,delay;bit add;bit sub;bit scankey;bit start;bit stop;bit ready;bit start0;void begin1() //初始化子程序{m=0;n=0;ms=0;LED0=0;LED1=0;LED2=0;LED3=0;LED4=0;LED5=0;add=0;sub=0;start=0;ready=0;start0=0;scankey=0;}void display(){ switch (ms%6){ //显示子程序 case 0:P3=0xfe;P1=table[LED3];P17=0;break;case 1:P3=0xfd;P1=table[LED2];P17=0;break;case 2:P3=0xfb;P1=table[LED1];P17=1;break;case 3:P3=0xf7;P1=table[LED0];P17=0;break;case 4:P3=0xef;P1=table[LED4];P17=1;break;case 5:P3=0xdf;P1=table[LED5];P17=0;break;default: return;}}void time0(void) interrupt 1 using 1 //中断程序{TL0=0x18 ;TH0=0xfc;ms++;if(ms==10){ ms=0;scankey=1; //扫描键盘标志位有效 }display(); //显示程序调用}void add1(time)uint time;{ uint n,a;a=time/1000;LED0=a; //计算十秒位数值n=time%1000;LED1=(n/100); //计算秒位数值n=n%100;LED2=(n/10); //计算十分一秒位数值LED3=n%10; //计算百分一秒位数值}void add2(t){ LED5=(t/10); //计算分钟十位数值LED4=t%10; //计算分钟个位数值}void scan() //扫描开关输入子程序{ P2=0xff;if(P20==0&&ready==0&&start0==0) //K1计时与暂停{ for(delay=0;delay<=200;delay++);P2=0xff;if(P20==0)start=!start;}if(P21==0&&ready==0&&start0==0) //K2计时 { for(delay=0;delay<=200;delay++);P2=0xff;if(P21==0)stop=1;}if(P22==0&&ready==0&&start0==0) //K3进入倒计时状态{ for(delay=0;delay<=200;delay++);P2=0xff;if(P22==0)ready=1;}if(P20==0&&ready==1&&start0==0) //K1调整倒计值加标志位有效{ for(delay=0;delay<=200;delay++);P2=0xff;if(P20==0&&ready==1)add=1;}if(P21==0&&ready==1&&start0==0) //K2调整倒计值减标志位有效{ for(delay=0;delay<=200;delay++);P2=0xff;if(P21==0&&ready==1)sub=1;}if(P22==0&&start0==1) //K3倒计时暂停{ for(delay=0;delay<=200;delay++);P2=0xff;if(P22==0&&start0==1)start0=0;}if(P22==0&&ready==1&&start0==0) //K3倒计时开始{ for(delay=0;delay<=200;delay++);P2=0xff;if(P22==0&&ready==1)start0=1;}if(P21==0&&start0==1) //K2倒计时清零,只能在倒进行时使用{ for(delay=0;delay<=200;delay++);P2=0xff;if(P21==0&&start0==1)start=0;ready=0;start0=0;stop=1;}}void main(){begin1();TMOD=0x01;TL0=0x18;TH0=0xfc;EA=1;ET0=1;TR0=1;for(;;){if(scankey==1) //进行键盘扫描{ scankey=0;scan();if(start==1&ready==0) //计时开始{ m++;if(m==6000){m=0; n++;if(n==60){n=0;start=0;}}add1(m);add2(n);}if(stop==1&ready==0) //计时清零{m=0;n=0;start=0;stop=0;add1(m);add2(n);}if(add==1) //倒计时初值加10 { m=m+10;add=0;if(m==6000){m=0; n++;if(n==60)n=0;}add1(m);add2(n);}if(sub==1) //倒计时初值减10 { m=m-10;sub=0;if(m==-1&&n!=0){n--;m=5999;}if(m==-1&&n==0){m=0;}add1(m);add2(n);}if(start0==1) //倒计时{ m--;if(m==-1&&n!=0){n--;m=5999;}if(m==-1&&n==0){m=0;ready=0;start0=0;start=0;}add1(m);add2(n);}}}。

数电电子秒表课程设计

数电电子秒表课程设计一、课程目标知识目标:1. 理解数字电路基本原理,掌握电子秒表的基本组成及工作原理;2. 掌握计数器、定时器等数字电路的应用,能正确运用相关元器件搭建电子秒表;3. 学会分析电子秒表的电路图,并能进行简单的故障排查。

技能目标:1. 培养学生动手操作能力,能够独立完成电子秒表的搭建和调试;2. 培养学生运用所学知识解决实际问题的能力,提高创新意识和团队合作精神;3. 提高学生运用相关软件(如Multisim、Protel等)进行电路设计和仿真测试的能力。

情感态度价值观目标:1. 培养学生对电子技术的兴趣和热情,激发学生学习主动性和积极性;2. 培养学生严谨的科学态度,注重实验数据,遵循实验操作规程;3. 培养学生团结协作、互相帮助的精神,增强集体荣誉感和责任感。

课程性质分析:本课程为电子信息类学科,旨在让学生通过实际操作,掌握数字电路基础知识,培养实际动手能力。

学生特点分析:学生年级为高中二年级,具备一定的物理和数学基础,具有较强的逻辑思维能力和动手操作欲望。

教学要求:结合课程内容和学生的特点,注重理论与实践相结合,充分调动学生的主观能动性,培养实际操作能力和团队协作精神。

通过本课程的学习,使学生在知识、技能和情感态度价值观方面取得具体的学习成果,为后续相关课程的学习打下坚实基础。

二、教学内容1. 数字电路基础知识回顾:逻辑门电路、触发器、计数器原理;2. 电子秒表的原理与设计:秒表的计时原理、秒表电路的组成、各部分功能;3. 常用元器件介绍:集成电路、晶体振荡器、显示屏等;4. 电路图分析:学会分析电子秒表的电路图,理解各部分之间的连接关系;5. 搭建与调试:根据电路图,使用面包板或实验箱搭建电子秒表,并进行调试;6. 故障排查:学会分析搭建过程中可能出现的问题,进行故障排查;7. 仿真测试:运用Multisim、Protel等软件进行电路设计和仿真测试;8. 教学案例分享:分析优秀电子秒表设计方案,学习借鉴经验。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

工业大学课程设计课程:数电课程设计题目:电子秒表专业班级: 通信工程1003班学号: *********、309、315学生: 路、智佳、吴开来指导教师: 柏山完成时间: 2013年6月25日目录第1章设计要求.................................. 第2章设计方案.................................. 第3章总电路设计思路..................... 第4章分解电路的设计及说明......... 第5章电路的仿真 ............................. 第6章设计总结及心得体会............. 参考文献: ............................................附录:.....................................................第1章设计要求结合数字逻辑电路知识,设计或分析下述功能电路,利用Proteus软件对电路进行功能仿真,并基于仿真结果对电路进行功能改进。

给出仿真机及分析过程及结果。

设计参数:1.设计可控的计数器(定时器)、分频器、键去抖电路和动态扫描显示电路;2.设计系统顶层电路;3.进行功能仿真和时序仿真;4.对仿真结果进行分析,确认仿真结果达到了设计要求:1.分析设计要求,明确性能指标。

必须仔细分析课题要求、性能、指标及应用环境等,广开思路,构思出各种总体方案,绘制结构框图。

2.确定合理的结构方案,对各种方案进行比较,以电路的先进性、结构的繁简、成本的高低及制作的难易等方面作综合比较并考虑器件的来源,敲定可行方案。

3.设计各单元电路。

总体方案化整为零,分解成若干子系统或单元电路,逐个设计。

4.组成系统。

在一定幅面的图纸上合理布局,通常是按信号的流向,采用左进右出的规律摆放各电路,并标出必要的说明。

第2章设计方案方案一:实现秒表的功能有很多种,该方案采用的是用555定时器产生一个1000HZ的秒脉冲,然后通过分频电路接到延时电路上,跟一个去抖电路连接在一起,输出给74160做触发信号,与另一个74160连接组成,然后把输出端分别连接到7448译码器上,通过共阴极七段数码管来显示结果,算选用的器件便宜,精度小于5%,可实现0-59秒的计时,另有启动、暂停、和清零三个功能。

但在电路仿真过程中不是很顺利,仿真结果与自己的设想有所出入,故方案一仅在设计总结及评估中提及。

方案二:利用555定时器产生一个100HZ脉冲;设计秒逻辑电路实现时间的正确显示功能;设计秒校时电路对电子秒表显示时间进行基本校正,经7448译码后通过共阴极七段数码管来显示结果。

该电子秒表可以准确的显示00.00-99.99s,可手动启动、暂停、清零等。

第3章总电路设计思路该数字式秒表电路的工作原理:由555定时器产生100Hz脉冲信号,作为10毫秒的计时脉冲;10毫秒计数器计满10后,向100毫秒计数器产生进位脉冲;100毫秒计数器计满10后,向1秒计数器产生进位脉冲;1秒计数器计满10后,向10秒计数器产生进位脉冲。

计数器的输出经显示译码器译码后送显示器显示。

该电路设置两个控制键“SW1”,“SW2”。

键“SW1”控制电路的清零功能,键“SW2”控制电路的暂停功能。

图3-1 数字式秒表电路的结构框图第4章 分解电路的设计与说明○1100HZ 脉冲发生器的设计 时钟发生器是模拟 — 数字混合式集成电路。

用555定时器构成的自激式多谐振荡器,是一种性能较好的时钟源。

T2=R2Cln2=0.7R2C;T=T1+T2;输出脉冲的占空比q为,q=T1/T2=(R1+R2)/(R1+2R2)我选用的参数为:R1=2.05K+2K=4.05KR2=5.1K, C=1u,f=1/0.7(R1+2R2)C=100HZ○2计数器的设计计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,还常用作数字系统的定时,分频和执行数字运算以及其它特定的逻辑功能. 计数器种类很多.按构成计数器中的各触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器.根据计数制的不同,分为二进制计数器,十进制计数器和任意进制计数器.根据计数的增减趋势,又分为加法,减法和可逆计数器.还有可预置数和可编程序功能计数器等等。

40192是十进制计数器,40192上的Rd控制端是异步清零端,高电平有效;Ld输入端是异步预置数控制端,低电平有效;预置数数据输入端包括D3、D2、D1和D0,D3为最高位,D0为最低位;C0端是进位输出端,低电平有效;B0端是借位输出端,低电平有效;计数结果从Q3、Q2、Q1和Q0端输出,Q3为最高位,Q0为最低位。

当计数时钟脉冲从CPU输入时,集成芯片实现加法计数过程,计数过程为0000-1001-0000。

40192集成计数器的逻辑功能如表3-2所示。

表中“↑”表示时钟脉冲的上升沿。

表3-2 40192逻辑功能表计数功能主要利用十进制加法计数器40192来实现。

因要求电子秒表显示时间为00:00—99:99秒,因此需四片40192芯片,其与译码显示单元的相应输入端连接,可显示00:00—99:99秒。

通过不同的连接方式,40192可以实现四种不同的逻辑功能;而且还可借助RD对计数器清零。

由四片40192芯片构成的计数器电路如下图所示○3译码及驱动显示电路的设计计数器实现了对时间的累计以8421BCD码形式输出,选用显示译码电路将计数器的输出数码转换为数码显示器件所需要的输出逻辑和一定的电流,选用74××48作为显示译码电路,选用LED数码管作为显示单元电路。

7448引脚图LED数码显示管448管脚功能介绍如下:LT:试灯输入端,当T=0时,不管其他各个输入端输入如何,输出显示为‘8’,正常显示时该端应输入高电平。

RBI端称为动态消零输入端。

BI/RBO动态清零输出端,该端主要作为多位显示中的多个译码器动态消零连接。

A、B、C、D、为8421BCD码输入端。

a、b、c、d、e、f、g:为译码输出端,输出为高电平1有效。

8421BCD码对应的显示图:8421BCD码对应的显示图译码显示器电路由于设计中要有分频器、按键去抖电路两个要求,我所设计的方案二没有应用到,但方案一中有这两个子电路,故下面将作介绍。

○4分频器设计74LS90为2-5-10进制计数器,作为十进制进行分频。

74LS90是异步二—五—十进制加法计数器,它既可以作二进制加法计数器,又可以作五进制和十进制加法计数器。

通过不同的连接方式,74LS90可以实现四种不同的逻辑功能;而且还右借助R0(1)、R0(2)对计数器清零,借助S9(1)、S9(2)将计数器置9。

其具体功详述如下:(1)计数脉冲从CP1输入,Q A作为输出端,为二进制计数器。

(2)计数脉冲从CP2输入,Q D Q L Q H作为输出端,为异步五进制加法计数器。

(3)若将CP2和Q A相连,计数脉冲由CP1输入,Q D、Q C、Q B、Q A作为输出端,则构成异步8421码十进制加法计数器。

(4)若将CP1与Q D相连,计数脉冲由CP2输入,Q A、Q D、Q C、Q B作为输出端,则构成异步5421码十进制加法计数器。

(5)清零、置9功能。

a)异步清零当R0(1)、R0(2)均为“1”;S9(1)、S9(2)中有“0”时,实现异步清零功能,即Q D Q C Q B Q A=0000。

b)置9功能当S9(1)、S9(2)均为“1”;R0(1)、R0(2)中有“0”时,实现置9功能,即Q D Q C Q B Q A =1001.下图为方案一分频器截图,由555定时器产生的1000HZ信号输入到第一片74LS90的CKA端,从第三片74LS90的Q3端输出,经过分频后便产生了1HZ 的时钟信号。

系统的控制开关我选择的是单刀双掷开关,然后接一个抖动消除电路,控制秒表的计数和停止。

它的一路输出Q作为延迟电路的输入,按动按钮开关J1时(接地),则门U2B输出Q=0;门U1B输出Q’=1,状态保持不变。

再按动按钮开关时;则Q 由0变为1,输出U4A开启,为计数器启动作为准备。

Q由0变1,启动单稳态触发器工作。

基本RS触发器第5章电路的仿真方案二仿真全图:方案一仿真全图:第6章设计总结及心得体会设计总结:本次课程设计我设计了两个方案,其中方案一我尽量使用分频器、按键去抖电路等设计所要求的来设计电路图。

但很遗憾,方案一并没有达到我的预期,经过反复调试也没能好使,不得已,我又设计了方案二,虽然电路里没有使用分频器、按键去抖电路,但在方案一的设计过程中我已经对上述两个子模块电路有了一定的了解,并在报告里面均作了一一叙述。

心得体会:课程设计进一步加深了对数字电子技术的认识,熟悉了对proteus软件的学习和使用,在仿真过程中出现较多的问题,通过自己的努力和组员的帮助都一一解决了。

通过这次对电子秒表的设计与仿真及制作,为以后的电路设计打下良好的基础,得到了一些宝贵经验和教训,加强了自己的动手能力和协同合作能力,为以后的学习和工作提供了良好的例,我会把这种认真和实在带到以后的生活当中去。

参考文献:○1康华光. 《电子技术基础》. 5.版.:高等教育○2阎石.数字电子技术基础.5版.:高等教育○3童诗白,华成英.模拟电子技术基础.4版.:高等教育附录参考元器件清单:方案一:七段LED数码管(共阴)2片555芯片1片74LS90 4片74160 2片7448 2片74LS04 3片74S00 2片74HC08 1片NAND 1片单刀双掷开关2个电阻、电容、地、电源若干方案二:七段LED数码管(共阴)4片7448 4片40192 4片555芯片1片74LS08 1片单刀双掷开关2个电阻、电容、地、电源若干。