EP4CE6E22开发板完整原理图

学号_姓名_3-8译码器实验报告

电子科技大学实验报告学生姓名:学号:指导教师:黄*实验地点:主楼C2-514实验时间:(1班)一、实验室名称:虚拟仪器实验室二、实验项目名称:3-8 译码器实验三、实验学时:4学时四、实验原理开发板上共四个按键:SW3~SW6,其中SW3 为总开关;SW4、SW5、SW6 作为三个译码输入。

本实验3-8 译码器所有的接口如下。

input ext_clk_25m, //外部输入25MHz 时钟信号input ext_rst_n, //外部输入复位信号,低电平有效input[3:0] switch, //4个拨码开关接口,ON -- 低电平;OFF -- 高电平。

SW3 为总开关;SW4、SW5、SW6 的三个译码输入output reg[7:0] led //8 个LED 指示灯接口注:X 表示ON 或OFF,即任意状态。

五、实验目的熟悉利用HDL代码输入方式进行电路的设计和仿真的流程,掌握Verilog语言的基本语法。

并通过一个3-8译码器的设计把握利用EDA软件(Quartus II 13.1)进行HDL代码输入方式的电子线路设计与仿真的详细流程。

六、实验内容利用HDL代码输入方式在Quartus II 13.1平台上实现一个3-8译码器设计,并进行仿真,然后生成配置文件下载到开发板上进行验证。

七、实验器材(设备、元器件)1. 计算机(安装Quartus II 13.1& ModelSim13.1软件平台);2. Cyclone IV FPGA开发板一套(带Altera USB-Blaster下载器)。

八、实验步骤(1)新建工程,设置器件属性:在Quartus II 13.1平台中,新建一个工程(注意命名规范),在“Family”中选择“Cyclone IV E”系列,“Availabledevice”中选择具体型号“EP4CE6E22C8”,设置好器件属性。

在EDATool Settings 页面中,可以设置工程各个开发环节中需要用到的第三方(Altera 公司以外)EDA 工具,我们只需要设置“Simulation”工具为“ModelSim-Altera”,Format 为“Verilog HDL”即可,其他工具不涉及,因此都默认为<None>。

EP4CE6 引脚功能说明

Bank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF256/U256E144(4)DQS for X8/X9 in F256/U256DQS for X16/X18 in F256/U256DQS for X8/X9 in E144B1 VREFB1N0 IO D41B1 VREFB1N0 IO E52B1 VREFB1N0 IO F53B1 VREFB1N0 IO B1 DQS2L/CQ3L DQS2L/CQ3L DQS2L/CQ3LB1 VREFB1N0 IO DIFFIO_L1p C2B1 VREFB1N0 IO DIFFIO_L1n DATA1,ASDO C16B1 VREFB1N0 IO VREFB1N0 F37B1 VREFB1N0 IO DIFFIO_L2p FLASH_nCE,nCSO D28B1 VREFB1N0 IO DIFFIO_L2n D1B1 VREFB1N0 nSTATUS nSTATUS F49B1 VREFB1N0 IO G5B1 VREFB1N0 IO DIFFIO_L3p F2B1 VREFB1N0 IO DIFFIO_L3n F1B1 VREFB1N0 IO DIFFIO_L4p G210 DQS0L/CQ1L,DPCLK0 DQS0L/CQ1L,DPCLK0 DQS0L/CQ1L,DPCLK0B1 VREFB1N0 IO DIFFIO_L4n G111B1 VREFB1N0 DCLK DCLK H112B1 VREFB1N0 IO DATA0 H213B1 VREFB1N0 nCONFIG nCONFIG H514B1 VREFB1N0 TDI TDI H415B1 VREFB1N0 TCK TCK H316B1 VREFB1N0 TMS TMS J518B1 VREFB1N0 TDO TDO J420B1 VREFB1N0 nCE nCE J321B1 VREFB1N0 CLK1 DIFFCLK_0n E123B2 VREFB2N0 CLK2 DIFFCLK_1p M224B2 VREFB2N0 CLK3 DIFFCLK_1n M125B2 VREFB2N0 IO DIFFIO_L5p J2 DQ1LB2 VREFB2N0 IO DIFFIO_L5n J1 DQ1LB2 VREFB2N0 IO J6B2 VREFB2N0 IO DIFFIO_L6p K6B2 VREFB2N0 IO DIFFIO_L6n L628B2 VREFB2N0 IO DIFFIO_L7p K2B2 VREFB2N0 IO DIFFIO_L7n K1 DQ1LB2 VREFB2N0 IO DIFFIO_L8p L230 DQS1L/CQ1L#,DPCLK1 DQS1L/CQ1L#,DPCLK1 DQS1L/CQ1L#,DPCLK1B2 VREFB2N0 IO DIFFIO_L8n L1 DQ1LB2 VREFB2N0 IO VREFB2N0 L331B2 VREFB2N0 IO DIFFIO_L9p N2 DQ1LB2 VREFB2N0 IO DIFFIO_L9n N1 DQ1LB2 VREFB2N0 IO RUP1 K532 DQ1LB2 VREFB2N0 IO RDN1 L433 DQ1LB2 VREFB2N0 IO34B2 VREFB2N0 IO R1 DQS3L/CQ3L# DQS3L/CQ3L# DQS3L/CQ3L#B2 VREFB2N0 IO DIFFIO_L10p P2 DQ1LB2 VREFB2N0 IO DIFFIO_L10n P1 DM1L/BWS#1LB3 VREFB3N0 IO DIFFIO_B1p N338B3 VREFB3N0 IO DIFFIO_B1n P339 DM3B/BWS#3B DM5B/BWS#5BNotes (1), (2), (3)Bank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF256/U256E144(4)DQS for X8/X9 in F256/U256DQS for X16/X18 in F256/U256DQS for X8/X9 in E144Notes (1), (2), (3)Bank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF256/U256E144(4)DQS for X8/X9 in F256/U256DQS for X16/X18 in F256/U256DQS for X8/X9 in E144Notes (1), (2), (3)Bank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF256/U256E144(4)DQS for X8/X9 in F256/U256DQS for X16/X18 in F256/U256DQS for X8/X9 in E144Notes (1), (2), (3)Bank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF256/U256E144(4)DQS for X8/X9 in F256/U256DQS for X16/X18 in F256/U256DQS for X8/X9 in E144Notes (1), (2), (3)Bank Number VREFB Group Pin Name /Function Optional Function(s)Configuration Function F256/U256E144(4)DQS for X8/X9 in F256/U256DQS for X16/X18 in F256/U256DQS for X8/X9 in E144Notes (1), (2), (3)Notes:Cyclone IV Device Family Pin Connection Guidelines.(4) The E144 package has an exposed pad at the bottom of the package. This exposed pad is a ground pad that must be connected to the ground plane on your PCB. This exposed pad is used for electrical connectivity, and not for thermal purposes.(1) If the p pin or n pin is not available for the package, the particular differential pair is not supported.(2) For DQS pins that do not have the associated DQ pins, the particular DQS is not supported. (3) For more information about pin definition and pin connection guidelines, refer to the。

单片机开发板电路图(原理图)

6 4 5

G1 G2A G2B 74LS138

J12 8 7 6 5 4 3 2 1 2 3 4 5 6 7 8 9 GND 1 LE 11 P10 VCC

U13 D0 D1 D2 D3 D4 D5 D6 D7 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 19 18 17 16 15 14 13 12 R20 R21 100R R22 R23 R24 R25 R26 R27 D11 D12 D13 D14 D15 D16 D17 D18

M2 B2 D2 C2 VCC A2 1 2 3 4 5 M1

RP4B

ISP XT1 C1 XT2 C2 33P P15 RST P17 P16 1 3 5 7 9 2 4 6 8 10 VCC GND GND GND GND

U15 IM1 4 3 2 1 1 2 3 4 5 6 7 8 GND IN1 IN2 IN3 IN4 IN5 IN6 IN7 GND ULN2003D VCC OUT1 OUT2 OUT3 OUT4 OUT5 OUT6 OUT7 COM 16 15 14 13 12 11 10 9 C2 D2 A1 B1 C1 D1

双色点阵

D Pa-D Pd : 为74HC573 输出 端 R E1-R E2: 为点 阵红 色端 GR1-GR2: 为 点阵 绿 色端

VCC

138译码器

74HC573 动静LED 共 阴极数 码管

J16

74HC595锁 存器与共阳 极数码 管

Jp3 为 单位 数码 管的 接口 Jp2 595(传 入并 出)锁存 器输 出接 口, 这两 个接 口需 要用 排线 连接

B1 D1 C1 VCC A1

1 2 3 4 5

P15

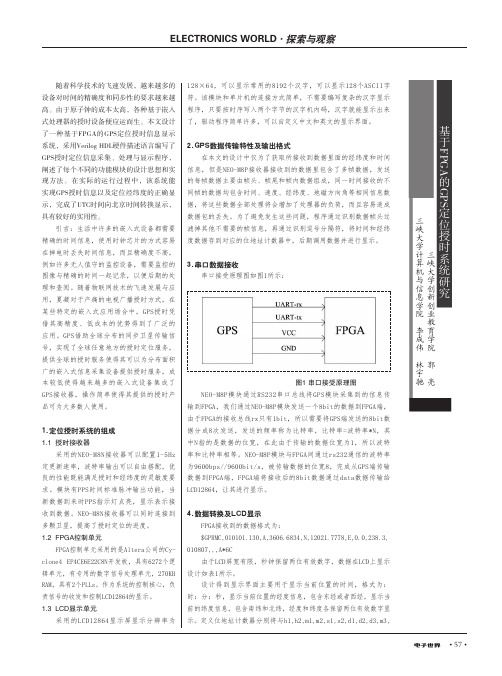

基于FPGA的GPS定位授时系统研究

• 57•随着科学技术的飞速发展,越来越多的设备对时间的精确度和同步性的要求越来越高。

由于原子钟的成本太高,各种基于嵌入式处理器的授时设备便应运而生。

本文设计了一种基于FPGA的GPS定位授时信息显示系统,采用Verilog HDL硬件描述语言编写了GPS授时定位信息采集、处理与显示程序,阐述了每个不同的功能模块的设计思想和实现方法。

在实际的运行过程中,该系统能实现GPS授时信息以及定位经纬度的正确显示,完成了UTC时间向北京时间转换显示,具有较好的实用性。

引言:生活中许多的嵌入式设备都需要精确的时间信息,使用时钟芯片的方式容易在掉电时丢失时间信息,而且精确度不高,例如许多无人值守的监控设备,需要监控的图像与精确的时间一起记录,以便后期的处理和查阅。

随着物联网技术的飞速发展与应用,夏凝对于产痛的电视广播授时方式,在某些特定的嵌入式应用场合中,GPS授时凭借其高精度、低成本的优势得到了广泛的应用。

GPS借助全球分布的同步卫星传输信号,实现了全球任意地方的授时定位服务,提供全球的授时服务使得其可以为分布面积广的嵌入式信息采集设备提供授时服务,成本较低使得越来越多的嵌入式设备集成了GPS接收器,操作简单使得其提供的授时产品可为大多数人使用。

1.定位授时系统的组成1.1 授时接收器采用的NEO-M8N接收器可以配置1-5Hz 定更新速率,波特率输出可以自由搭配,优良的性能既能满足授时和经纬度的灵敏度要求。

模块有PPS时间标准脉冲输出功能,当新数据到来时PPS指示灯点亮,显示表示接收到数据。

NEO-M8N接收器可以同时连接到多颗卫星,提高了授时定位的进度。

1.2 FPGA控制单元FPGA控制单元采用的是Altera公司的Cy-clone4 EP4CE6E22C8N开发板,具有6272个逻辑单元,有专用的数字信号处理单元,270KB RAM,具有2个PLLs。

作为系统的控制核心,负责信号的收发和控制LCD12864的显示。

开发板电路原理图

HE ADE R 1 2X 2

U8 VCC ADC_ CS ADC_ RD ADC_ W R CL KIN ADC_ INT R 1 2 3 4 5 6 7 8 9 10 CS RD WR CL KIN INT R Vi n (+) Vi n (-) AGND Vre f/ 2 DGND

ADC0 80 4 VCC CL KR DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 20 19 18 17 16 15 14 13 12 11 VCC CL KR ADC_ D0 ADC_ D1 ADC_ D2 ADC_ D3 ADC_ D4 ADC_ D5 ADC_ D6 ADC_ D7

VCC

GND U2 SN74 HC57 3N VCC 20 VCC J7 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 19 18 17 16 15 14 13 12 A0 A1 A2 A3 A4 A5 A6 A7 1 2 3 4 5 6 7 8 CON8 1 11 D0 D1 D2 D3 D4 D5 D6 D7 2 3 4 5 6 7 8 9 10 OE LE D1 D2 D3 D4 D5 D6 D7 D8 GND

LCM_ D 0 LCM_ D 1 LCM_ D 2 LCM_ D 3 LCM_ D 4 LCM_ D 5 LCM_ D 6 LCM_ D 7

L IGHT

R1 7

8 K2 GND

JP6 HE ADE R 8 X2 D0 D1 D2 D3 D4 D5 D6 D7 1 3 5 7 9 11 13 15 2 4 6 8 10 12 14 16 L CM _D0 L CM _D1 L CM _D2 L CM _D3 L CM _D4 L CM _D5 L CM _D6 L CM _D7

MHz等精度频率计设计基于VerilogHDL

姓名:郑中权班级:电子1班 数电课设报告江苏科技大学2017/10/12100MHz等精度频率计设计(基于Verilog HDL)一、设计要求:提供一个幅值为10mV ~ 1 V,频率为 1 ~ 100MHz的正弦信号,需测试以下指标:1.频率:测频范围 1Hz ~ 100MHz,测频精度为测频全域内相对误差恒为百万分之一。

2.占空比:测试精度 1% ~ 99%3.相位差:测试两个同频率的信号之间的相位差,测试范围 0 ~ 360二、设计分析使用FPGA数字信号处理方法,首先需要将正弦信号转换成可读取的数字方波信号,再经过FPGA设计计算得出所需测量值。

三、模电部分首先选择比较器,对于 100 MHz 信号,比较器灵敏度需要达到5ns内,TI公司的LTV3501灵敏度为4.5ns,符合要求由TLV3501数据手册得知:当频率低于 50MHz 的时候,正弦波的峰峰值需大于20mV,频率高于50MHz时,峰峰值需大于 1V。

然后需要选择放大器,当正弦波幅值为 10mV时,放大倍数需大于35。

方法通过二级放大,一级用OPA847放大20倍,二级用OPA675放大8倍,得到总放大倍数160的正弦波。

经转换后的输出电压符合TTL电平要求,可以被识别出0和1。

四、数电部分开发板:Cyclone IV E: EP4CE6E22C8板载时钟为 50MHz,带4个按键和一个复位键(按键按下为0,抬起为1),四个七段数码管(共阳),FPGA的引脚可由杜邦线引出。

设计思路:测量频率:输入一个100MHz的基准频率,由计数器CNT1来计算基准频率的上升沿个数,即周期数。

输入一个被测信号,它由计数器CNT2来测量周期数。

两个信号在同一个使能信号EN(使能信号时间为1~2s)下开始计数,计数完后,存储计数结果,由(CNT1 * 10)可以算出具体的计数时间(单位ns),再由((CNT1 * 10ns)/CNT2 )*10^9可算得被测信号频率,单位Hz。

100MHz等精度频率计设计(基于某VerilogHDL)

某某:X中权学号:152210303127班级:电子1班数电课设报告100MHz等精度频率计设计〔基于Verilog HDL〕一、设计要求:提供一个幅值为10mV ~ 1 V,频率为 1 ~ 100MHz的正弦信号,需测试以下指标:1.频率:测频X围 1Hz ~ 100MHz,测频精度为测频全域内相对误差恒为百万分之一。

2.占空比:测试精度 1% ~ 99%3.相位差:测试两个同频率的信号之间的相位差,测试X围 0 ~ 360 某某科技大学2017/10/12二、设计分析使用FPGA数字信号处理方法,首先需要将正弦信号转换成可读取的数字方波信号,再经过FPGA 设计计算得出所需测量值。

三、模电局部首先选择比拟器,对于 100 MHz 信号,比拟器灵敏度需要达到5ns内,TI公司的LTV3501灵敏度为4.5ns,符合要求由TLV3501数据手册得知:当频率低于 50MHz 的时候,正弦波的峰峰值需大于 20mV,频率高于50MHz时,峰峰值需大于 1V。

然后需要选择放大器,当正弦波幅值为 10mV时,放大倍数需大于35。

方法通过二级放大,一级用OPA847放大20倍,二级用OPA675放大8倍,得到总放大倍数160的正弦波。

经转换后的输出电压符合TTL电平要求,可以被识别出0和1。

四、数电局部开发板:Cyclone IV E: EP4CE6E22C8板载时钟为 50MHz,带4个按键和一个复位键〔按键按下为0,抬起为1〕,四个七段数码管〔共阳〕,FPGA的引脚可由杜邦线引出。

设计思路:测量频率:输入一个100MHz的基准频率,由计数器T1来计算基准频率的上升沿个数,即周期数。

输入一个被测信号,它由计数器T2来测量周期数。

两个信号在同一个使能信号EN〔使能信号时间为1~2s〕下开始计数,计数完后,存储计数结果,由〔T1 * 10〕可以算出具体的计数时间〔单位ns〕,再由(〔T1 * 10ns〕/T2 )*10^9可算得被测信号频率,单位Hz。

学号姓名译码器实验报告

电子科技大学实验报告学生姓名:学号:指导教师:黄敏实验地点:主楼C2-514实验时间:(1班)一、实验室名称:虚拟仪器实验室二、实验项目名称:3-8 译码器实验三、实验学时:4学时四、实验原理开发板上共四个按键:SW3~SW6,其中SW3 为总开关;SW4、SW5、SW6 作为三个译码输入。

本实验 3-8 译码器所有的接口如下。

计算机(安装Quartus II & 软件平台);2. Cyclone IV FPGA开发板一套(带Altera USB-Blaster下载器)。

八、实验步骤(1)新建工程,设置器件属性:在Quartus II 平台中,新建一个工程(注意命名规范),在“Family”中选择“Cyclone IV E”系列,“Available device”中选择具体型号“EP4CE6E22C8”,设置好器件属性。

在 EDA Tool Settings 页面中,可以设置工程各个开发环节中需要用到的第三方(Altera 公司以外)EDA 工具,我们只需要设置“Simulation”工具为“ModelSim-Altera”,Format为“Verilog HDL”即可,其他工具不涉及,因此都默认为<None>。

(详见实验指导书)(2)Verilog源码文件创建与编辑:点击菜单栏的“File→New…”,然后弹出如图所示的新建文件窗口,在这里我们可以选择各种需要的设计文件格式。

可以作为工程顶层设计文件的格式主要在Design Files 类别下,我们选择 Verilog HDL File(或者 VHDLFile)并单击 OK完成文件创建。

将新建的文件保存后通过菜单栏“Project→Add/Remove Files in Project”将刚刚创建的文件加入新建的工程中,点击“Add”加入后选择OK按钮。

(详见实验指导书)(3)Modelsim仿真验证:将工程编译,无误后,采用第三方EDA仿真工具Modelsim进行仿真。

开发板原理理图

单⽚片机外围⽤用户接⼝口标准IO开发板引出⼏几路路通⽤用IO,有Reset复位按键;⽤用户LED两路路蓝⾊色;⽤用户按键两路路,作为输⼊入使⽤用;蜂鸣器器作为提醒⽤用户使⽤用;1套Arduino标准接⼝口;1套通讯模组扩展⼝口,8P*6P;4路路电源开关:单⽚片机⼀一路路,WiFi模组⼀一路路,SUB1G 模组⼀一路路,通讯模组⼀一路路。

单独可以控制开关,单独可以关闭电源指示灯;USB 转串串⼝口多路路调试,UART4,UART5,USART3,USART1;USART1,⽤用于NB通讯模组;USART3,⽤用于WiFi模组;USART2,⽤用于Arduino扩展;通讯模组NB-IoT模组由锂电池直接供电;BC95 NB-IoT模组使⽤用USART2与单⽚片机通讯;有⼀一个总电源插座B C95 PWR;Sub-1GnRF24L01是直插式,天线朝向开发板外部插⼊入;PCB 布局整体布局本开发板整体布局较为紧凑,按理理说开发板应该做的宽松和相对密度⼩小⼀一些,⽽而本开发板在布局上参考了了实际项⽬目中的产品设计布局⽽而特意做成⾼高密度型,这样便便于读者参考,应⽤用在实际项⽬目中以减少PCB⾯面积。

本开发板是双层PCB板,元器器件⼤大部分是在表⾯面布局,读者在实际产品应⽤用过程中可以做成双⾯面焊接以节省PCB⼤大⼩小。

模组和其他外设可以摆放背⾯面,既美观⼜又节约空间;观⼜又节约空间;开发板采⽤用了了0805封装的电阻电容焊盘,⼀一⽅方⾯面是⽅方便便查看元器器件的型号,另⼀一⽅方⾯面是便便于维修和看清整体布局。

读者在实际应⽤用过程中,可以替换成0603或0402更更⼩小⼀一些的封装;为了了⽅方便便安装和替换锂电池,本开发板使⽤用了了XH2.54焊盘,采⽤用扁平的锂电池节省PCB空间,减少产品的物理理⾼高度;本开发板NB模组射频采⽤用板载PCB式天线,读者可以参考此天线设计做在实际产品中,⼀一⽅方⾯面是减少安装外置天线的步骤,另⼀一⽅方⾯面是没有外置天线占⽤用物理理空间。

EP4CE6E22C8中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

December 2013 CYIV-53001-1.8

CYIV-53001-1.8

1. Cyclone IV器件手册

本章介绍了电气和开关特性旋风

IV

设备.电气特性包括操作条件和功耗.开关特性包括收发信机的规格,核心,和外围性

能.本章还介绍了I / O定时,包括可编程I / O单元(IOE)延迟和可编程输出缓冲延迟.

f

有关支持的速度牌号为各自的Cyclone IV更多信息

设备,指的是

Cyclone IV FPGA器件系列简介

一章.

1

Cyclone IV E器件均提供了1.0和1.2与1.0伏的核心电压V. Cyclone IV E器件的核

心电压已经连接到速度等级为“L”字头.

在这一章中,与工作温度范围相关联的前缀所连接到 速度等级;商业用“C”字头,工业用“I”前缀, 汽车有一个“A”字头.因此,商用设备被表示为C6,C7, C8,C8L,或C9L每各自的速率等级.工业设备被表示为I7,I8,或I8L.汽车设备被表示为A7.

对于Cyclone IV器件最大额定值.

表1-1 列出的绝对

c

超出所列条件

表1-1 对器件造成永久性损坏.

此外,在延长的时间周期的绝对最大额定值设备操作具有设备上的不良影响.

表 1-1.对 Cyclone IV器件绝对最大额定值

符

参数

VCCINT

内核电压,PCI Express的 (PCIe )硬IP 块,和收发器物理编码子层 (PCS)电源

V

2.375 2.5 2.625 V

1.71 1.8 1.89 V

1.425 1.5 1.575 V

1.14 1.2 1.26 V

FPGA助学板教材-睿智FPGA开发板硬件详解

睿智FPGA助学板硬件详解开发板套件硬件是保证实验学习的基础,这部分内容主要针对硬件部分做简单描述,可适当阅读或翻查,特别是涉及到硬件接口定义等信息时,了解这部分内容很有必要。

同时,可与光盘附带的硬件原理图一并参考使用。

1.睿智FPGA助学板硬件1.1 总体介绍图1 助学板硬件实拍图主硬件资源1 .主芯片采用ALTERA公司最新四代FPGA CycloneIV系列EP4CE6E22C8N;2 .板载EPCS4N/EPCS16大容量串行配置芯片,支持JTAG/AS模式;3. 板载64MbitSDRAM,支持SOPC,NIOSII开发(很多价低的板不带SDRAM,无法支持NIOS SOPC开发) ;4 .板载50MHz有源晶振,提供系统工作主时钟 ;5 .采用1117-3.3V稳压芯片,提供3.3V电压输出 ;6 .采用1117-1.2V稳压芯片,提供FPGA内核电压 ;7 .采用1117-2.5V稳压芯片,提供PLL电压 ;8 .精心的去耦设计,采用大量去耦电容;9. 提供5V直流电源插座;10. 提供方口USB接口电源插座;11. 一个系统复位按键Reset,也可做为用户输入按键 ;12. 自锁按键电源开关 ;13. LED电源指示灯 ;14. 精心设计分配的IO资源,所有IO引出,3个扩展接口,通用2.54mm间距,任由您自己扩展;15.JTAG下载接口对应下载的文件是.SOF,速度快,平常学习推荐使用此接口 ;16. AS下载接口对应下载的文件是.POF,速度较慢,需要固化程序时使用 。

丰富外设资源1 .板载4个独立按键,可做按键控制,数字逻辑基础实验等 ;2 .板载4位LED发光二极管,可做LED控制,数字逻辑基础实验等 ;3. 板载4位数码管,频率计,秒表 ;4. 板载4位拨码开关,可做开关控制等实验 ;5 .设有1X20液晶屏排座,支持LCD1602,LCD12864,TFT液晶屏(不包括LCD,需另购) ;6 .精密可调电阻,调节液晶背光;7 .板载1路蜂鸣器,可做发声及音乐实验 ;8 .PS2接口,可做PS/2键盘实验 ;9 .板载全新原装进口温度传感器芯片LM75A,可以做温度计实验 ;10 .RS232串口,可做串口通讯实验 ;11 .VGA接口,可做显示器实验等 ;12. I2C串行EEPROM AT24C08,做IIC总线实验 ;13 .红外线接收模块;1.2 FPGA的IO分配FPGA的硬件设计与单片机,ARM或DSP还是有所不同,MCU的IO通常功能都是固定好的,Datasheet要求某个引脚什么功能,就必须是什么功能。

100MHz等精度频率计设计(基于某VerilogHDL]

![100MHz等精度频率计设计(基于某VerilogHDL]](https://img.taocdn.com/s3/m/777beadf81c758f5f61f67e1.png)

数电课设报告姓名:郑中权学号:152210303127班级:电子1班江苏科技大学2017/10/12100MHz等精度频率计设计(基于Verilog HDL)一、设计要求:提供一个幅值为10mV ~ 1 V,频率为 1 ~ 100MHz的正弦信号,需测试以下指标:1.频率:测频范围 1Hz ~ 100MHz,测频精度为测频全域内相对误差恒为百万分之一。

2.占空比:测试精度 1% ~ 99%3.相位差:测试两个同频率的信号之间的相位差,测试范围 0 ~ 360二、设计分析使用FPGA数字信号处理方法,首先需要将正弦信号转换成可读取的数字方波信号,再经过FPGA设计计算得出所需测量值。

三、模电部分首先选择比较器,对于 100 MHz 信号,比较器灵敏度需要达到5ns内,TI公司的LTV3501灵敏度为4.5ns,符合要求由TLV3501数据手册得知:当频率低于 50MHz 的时候,正弦波的峰峰值需大于 20mV,频率高于50MHz 时,峰峰值需大于 1V。

然后需要选择放大器,当正弦波幅值为 10mV时,放大倍数需大于35。

方法通过二级放大,一级用OPA847放大20倍,二级用OPA675放大8倍,得到总放大倍数160的正弦波。

经转换后的输出电压符合TTL电平要求,可以被识别出0和1。

四、数电部分开发板:Cyclone IV E: EP4CE6E22C8板载时钟为 50MHz,带4个按键和一个复位键(按键按下为0,抬起为1),四个七段数码管(共阳),FPGA的引脚可由杜邦线引出。

设计思路:测量频率:输入一个100MHz的基准频率,由计数器CNT1来计算基准频率的上升沿个数,即周期数。

输入一个被测信号,它由计数器CNT2来测量周期数。

两个信号在同一个使能信号EN(使能信号时间为1~2s)下开始计数,计数完后,存储计数结果,由(CNT1 * 10)可以算出具体的计数时间(单位ns),再由((CNT1 * 10ns)/CNT2 )*10^9可算得被测信号频率,单位Hz。

比亚迪e 先行者汽车电路识图

接仪表板线束(左) 接仪表板线束(左)

接油门踏板 接水温传感器 接右前碰撞传感器 接前驱电机-A 接前驱电机-B

接搭铁3 接搭铁2 接右前轮轮速传感器 接ABS ECU 接右地板线束 接右地板线束 接制动灯开关

接前舱配电盒Ⅱ

B17 接左前轮轮速传感器

B1C

接前舱配电盒C

B1I

接前舱配电盒I

B1J

C08

接左蜗牛喇叭

C25

C22

接搭铁

接左前雾灯 接洗涤液电机 接左散热风扇 接左前远大灯 左侧大灯调节 接左前位置灯 接左前近光灯 接左前转向灯 接继电器插座 接前舱配电盒F 接前舱配电盒H 接前舱线束 接水泵电机

技术·品质·责任

仪表板线束 接短接器

G58

接6#搭铁

G53

接3#搭铁

G49

接3#搭铁 G20 接1#搭铁 G75

内部资料 禁止外传

★一般★

e6先行者汽车电路识图

技术·品质·责任

1 比亚迪汽车线路原理图上元素编码规则 2 e6先行者整车线束介绍

3 配电盒、继电器、熔断器位置介绍

4 配电盒插脚定义

5 全车搭铁位置 6 e6先行者 CAN网络

技术·品质·责任

1 e6先行者整车工作原理及总体介绍

技术·品质·责任

产品型号名称

接阳光传感器

接烟灰缸照明灯

G45

接鼓风机电机

接螺旋线圈Ⅰ

G46 接鼓风机调速模块

接螺旋线圈Ⅱ

G48 接仪表板右侧扬声器

接组合开关

G49

接搭铁2

技术·品质·责任

G50 接安全气囊副爆模块 G64

284223-3 (TYCO)

G51