芯片介绍_上海贝岭BL7442

BL8023D 产品说明书

BL8023D SOT23-6 双向驱动继电器芯片说明书上海贝岭股份有限公司1. 概述BL8023D 是双向继电器驱动集成电路,用于控制磁保持继电器的工作,具有输出电流大,静态功耗小的特点,可广泛用于智能电表的生产行业及其他用于该类继电器的行业。

2. 主要指标1) 工作电压在5-40V ,静态功耗电流<1uA2) 输入高低转换电平在2V 左右,与各种单片机兼容3) 典型驱动电流150mA ,并根据继电器本身线圈内阻不同(驱动电流等于电源电压除以芯片本身驱动内阻和继电器线圈内阻之合芯片本身驱动内阻:电源电压12V 时为15Ω,电源电压20V 时为10Ω)。

4) 最大驱动电流500mA (是指芯片能承受的继电器线圈电感反冲电流的值。

该值与电源电压有关,500mA 是指一般工作电压24V 的情况。

在极限工作电压40V 时,则因封装功率限制,驱动电流应小于150mA )。

5) 工作温度适用范围:-40o C - 80oC 。

3. 功能框图4. 逻辑功能表输入输入输出OA输出OB5. 封装形式,管脚排列及功能封装形式:SOT23-6封装6. 应用电路1) 脉冲触发输入端A,B用脉冲触发,只要直接把输入端与相应器件的输出端连接就可以工作。

只要触发脉冲按功能表状态触发,继电器就会相应地动作(VDD应小于BL8023D供电电压,Rs为限流电阻,在电压低于20V时,可以忽略,即Rs=0)。

推荐脉冲宽度100毫秒。

正向驱动和反向驱动脉冲;正向驱动和下一个正向驱动脉冲;反向驱动和正向驱动脉冲;以及反向驱动和下一个反向驱动脉冲之间最小间隔100毫秒。

脉冲示意图如下:输入A输入B输入A 输入B2) 电平触发输入端A ,B 使用电平触发应在输入端加电阻R1,R2到地,保持低电平的静态状态。

在输入端按真值表加相应的高电平,继电器就可以相应的动作。

(R1,R2=30K-100K ,R3,R4=100k,C1,C2=10n 用于滤除输入毛刺; VDD 应小于BL8023D 供电电压;Rs 为限流电阻,在电压低于20V 时,可以忽略,即Rs=0)。

感应锁酒店锁常用智能卡有哪些类型?

感应锁酒店锁常用智能卡有哪些类型?信息来源: 浏览:1512次时间:2015-08-05智能卡技术经过多年的发展,历经磁卡、接触式IC卡、射频卡三个阶段,并广泛应用于我们的生活中。

智能卡的演变发展,也丰富了酒店感应锁相关技术,促进酒店锁领域技术的更新。

那么现在酒店锁市面上常见的感应卡类群有哪些呢?一、磁卡磁卡的原理是通过记录磁头磁化磁卡上的磁性微粒,磁卡被磁化之后,卡片上就留下和电流变化规律相同的磁性,此时的磁卡也就纪录下了电流送来的信息。

磁卡成本低、读写方便,但也容易磨损和失磁。

我们日常接触的银行卡就是磁卡,磁卡也是酒店锁最早使用的智能卡,即使到了现在仍有一些小旅馆在使用,但已经濒临淘汰。

二、IC卡IC卡就是在“基片”(塑料卡)固定位置上嵌装封装的集成电路芯片,可读写电子信息。

IC卡的历史比较悠久,大家也很熟悉。

支持IC卡的系统有西门子的SLE4442、飞利浦PHILIPS2042、上海贝岭的BL7442等系列加密IC卡。

数据卡使用ATMEL 的存储卡。

IC卡的特点是怕水、怕尘,但是比较便宜。

IC卡可分为接触式与非接触是两种。

接触式IC卡是将卡插入卡座后,卡片通过留在在塑料卡外面的一块含有电路腿的接触片与外界交换信息。

在现今感应锁行业常用的IC卡也可细分不同类型。

TM卡TM卡是Touch Memory的缩写,也叫IB卡(iButton)。

TM卡是美国著名半导体公司Dallas Semiconductor 的独家专利产品,有非接触式IC卡的易操作性,又具有接触式IC 卡的廉价性,是当前性价比最优秀的IC卡之一。

每个TM卡具有全球唯一序列号,不可复制。

TM卡外表用不锈钢封装,可以存放加密的信息。

TM卡本身是一个微型电脑芯片,由于外表用不锈钢封装,外表类似于纽扣电池,不怕水,不怕磁场,也不怕灰尘。

适用于学校、出租屋、桑拿柜锁、宾馆酒店等场合。

非接触式IC卡是通过电磁波与外界交换信息,它工作的基本原理是:外界设备向IC 卡发一组电磁波,卡片内有一个LC协振电路,其频率与发射的频率相同,这样在电磁波激励下,LC协振电路产生共振,从而使电容内有了电荷,当所积累的电荷达到2V时,此电容就可作为电源为其它电路提供工作电压,将卡内数据发射出去或接受读写器的数据。

详解智能电网的主流计量芯方案

详解智能电网的主流计量芯方案中心议题:•BL6523A的性能介绍和结构分析•实现电气测量的原理电气测量原理•从硬件设计分析智能电网的计量芯片BL6523A•从软件设计分析智能电网的计量芯片BL6523A解决方案:智能电表计量芯片系统方案在智能电网的诸多应用中。

智能电表应用已率先落地。

根据国家电网公司电网智能化建设规划,在国家电网公司“计量、抄表和收费标准化建设研究”项目成果的基础上,全国的大多数电表企业均设计研发了符合新一代智能电网要求的电度表。

在单相电度表的设计过程中,由于设计周期短,任务重,各个厂家对于设计芯片选型、硬件布局等还有待改进的地方。

本文针对新一代智能、电网的计量芯片BL6523A,从硬件设计和软件设计上进行分析。

智能电表原理框图由上面方框图可以看出,智能电表所需IC包括多功能计量、MCU、通讯、带温补的高精度实时时钟、液晶驱动、数据存储及电源等。

在设计中,由于计量部分要与MCU等其他部分隔离,因此目前的方案计量部分均采用单独的芯片。

目前的主流方案计量芯片通常采用上海贝岭的BL6523、深圳锐能微RN8209及CS5464等,MCU则大多采用NEC、瑞萨、飞思卡尔等国外品牌的产品。

BL6523A计量芯片是结合国内外计量要求,集合防窃电技术、多项专利技术而设计的能实现包括电压电流等多种电气测量的计量芯片产品。

BL6523A的性能介绍和结构分析及电气测量原理1.BL6523A的性能介绍BL6523A是一款高精度、高稳定性的计量芯片,其精度在输入动态工作范围(1500:1)内,非线性测量误差小于0.1%;稳定性高,输出频率波动小于0.1%。

BL6523A可精确测量正负两个方向的有功功率,输出快速输出脉冲(CF);具有两个电流采样端,采样火线和零线电流;给出电压和双电流的有效值,以及可测量范围(1500:1)。

BL6523A还具有电压失压和断相检测功能;芯片上有电源电压监测电路,检测掉电状;具有防潜动功能,可编程防潜阀值设置;同时具有可编程调整脉冲输出的频率;此外,BL6523A还具有可编程增益调整和相位补偿;给出功率因子(PF),计算功率因数;可按需要给出中断请求信号(/IRQ);提供SPI通信接口,用于数据传输。

上海贝岭 BL8307 Ballast control IC 说明书

BL8307 Ballast control IC主要特点n可驱动由双极型晶体管或MOSFET组成的半桥电路n驱动双极型晶体管时,基极回路注入电流强度可自动调节n低功耗启动(启动电流小于100uA)n启动电路具有2V的迟滞(电源电压高于13.7V芯片启动,低于11.7V关闭输出)n预热时间、预热频率与工作频率均可调整n有预热结束输出信号,可用做CUTOFF n有窗口比较器,可做EOL检测和保护n在点火时,有升频功能,可做过流或过压控制n有过扫频功能,可改善低温点火性能n内置一误差放大器,可做简单调光功能典型应用n电子镇流器及节能灯或其他功能简介BL8307是荧光灯电子镇流器专用驱动控制电路,可为荧光灯提供正常工作所需要的预热、点火以及故障保护等功能,且预热时间可以通过外置预热电容CPRE进行设置,同样的,荧光灯的预热频率及工作频率也可以分别通过外接电阻RPRE 和RT进行调节。

BL8307的另外一个特点就是可以驱动13XXX系列的双极型晶体管半桥和MOS晶体管半桥。

比较早期的BL8305A,BL8307的驱动输出电压范围和灯异常保护作了适当的改进,外围电路也作了适当的简化,所以电路更具实用。

在对荧光灯提供完善保护机制的同时,又加入了一个内置误差放大器可用作调光。

电路可具有固定死区(驱动MOS型半桥:1.5us;驱动双极型半桥:3us),以防止半桥上、下管同时导通,以实现零电压开(ZVS),降低损耗,对半桥电路起到保护作用。

_________________________________________________________________________ _________________________________________________________________________Contentspage 1系统框图 (3)2引脚定义 (3)2.1 管脚图 (3)2.2 管脚描述 (4)3 功能描述 (4)3.1 上电启动及芯片供电 (4)3.2 预热、点火及运行 (5)3.3 MOSFET型和Bipolar型半桥驱动 (6)3.3.1 Bipolar型半桥驱动 (6)3.3.2 MOSFET型半桥驱动 (7)3.4调光 (8)3.5 故障保护 (8)3.5.1 点火模式下的过流保护 (8)3.5.2 进入正常工作模式后的过流保护 (9)3.5.3 荧光灯寿命结束检测保护 (9)3.6 PEND输出信号 (10)4 技术参数 (10)4.1 极限参数 (10)4.2 温度参数 (10)4.3 电特性参数 (11)5 电参数特性图....................................................................................................... 错误!未定义书签。

IC卡封装的芯片型号有哪些

IC卡封装的芯片型号有哪些?

今天有个客户问我“你们制作IC卡时里面封装的是什么型号的芯片,你们能提供那些型号的IC卡芯片”。

相信也有很多客户有同样的疑问,下面就让我来为大家说明一下IC卡芯片的型号到底有哪些.

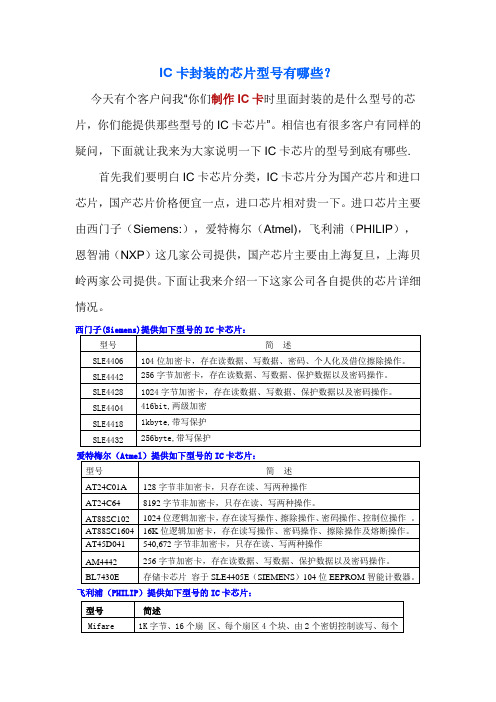

首先我们要明白IC卡芯片分类,IC卡芯片分为国产芯片和进口芯片,国产芯片价格便宜一点,进口芯片相对贵一下。

进口芯片主要由西门子(Siemens:),爱特梅尔(Atmel),飞利浦(PHILIP),恩智浦(NXP)这几家公司提供,国产芯片主要由上海复旦,上海贝岭两家公司提供。

下面让我来介绍一下这家公司各自提供的芯片详细情况。

飞利浦(PHILIP)提供如下型号的IC卡芯片:。

BL6522B 高精度三相多功能电能计量芯片 产品说明书

高精度三相多功 能明书

(版本:1.0)

如需得到最新的产品信息,请与上海贝岭有限公司联系,本公司保留不需要通知本数据 手册读者而修改本数据手册的权利。

Edit by Richard Han, Shi Fei, Fei yu hang

1)电参数性能指标................................................................................................................. 12 2)极限范围 ........................................................................................................................... 15 二 工作原理 ............................................................................................................................................ 17 (一)系统框图及原理.................................................................................................................... 17 1)三相原理结构描述图 ......................................................................................................... 17 2)单相原理结构描述图(以 A 相为例)................................................................................ 19 (二)电流电压瞬态波形测量前端(以 A 相为例) ........................................................................ 20 1)前端增益调整 .................................................................................................................... 20 2)相位补偿 ........................................................................................................................... 20 3)输入偏差校正 .................................................................................................................... 21 4)通道增益校正 .................................................................................................................... 21 5)电流电压波形输出 ............................................................................................................. 22 6)电压通道增益粗调 ............................................................................................................. 22 (三)有功功率计量原理(以 A 相为例)....................................................................................... 23 1)有功功率偏差校正 ............................................................................................................. 24 2)有功功率增益调整 ............................................................................................................. 24 3)有功功率的防潜动 ............................................................................................................. 24 4)有功功率的小信号补偿...................................................................................................... 25 5)有功功率反向指示阈值 ...................................................................................................... 25 6)正向有功能量计算 ............................................................................................................. 25

贴片稳压芯片bl9342参数

贴片稳压芯片bl9342参数贴片稳压芯片BL9342是一种高效率、低压差、稳定性好的线性电源芯片,广泛应用于手机、平板电脑、数码相机等电子产品中。

下面将详细介绍该芯片的参数。

1. 输入电压范围:4.5V~18V输入电压范围是指该芯片能够正常工作的最小和最大输入电压值。

BL9342的输入电压范围为4.5V~18V,适用于多种不同的输入电源。

2. 输出电压范围:0.8V~6V输出电压范围是指该芯片能够输出的最小和最大输出电压值。

BL9342的输出电压范围为0.8V~6V,可满足各种不同应用场合对输出电压的需求。

3. 输出电流:1A输出电流是指该芯片能够提供给负载的最大稳定输出电流值。

BL9342的输出电流为1A,可满足多种不同负载需求。

4. 超低静态功耗:≤0.1μA超低静态功耗是指该芯片在待机状态下消耗的极少量功率。

BL9342具有超低静态功耗,仅为≤0.1μA,可大大延长电池寿命。

5. 超低压差:≤70mV超低压差是指该芯片在工作时输出电压与输入电压之间的差值。

BL9342具有超低压差,仅为≤70mV,可保证输出电压的稳定性。

6. 过温保护和短路保护过温保护和短路保护是指该芯片具有在异常情况下自动切断输出电流以保护芯片和负载的功能。

BL9342具有过温保护和短路保护功能,可有效防止因异常情况导致的损坏。

7. 封装形式:SOT-23-5封装形式是指该芯片的外观尺寸和引脚排列方式。

BL9342采用SOT-23-5封装形式,具有小巧、轻便等特点。

总之,贴片稳压芯片BL9342是一款高效率、低静态功耗、超低压差、稳定性好的线性电源芯片。

它适用于多种不同输入电源和负载需求,并具有过温保护和短路保护等功能,可大大提高电子产品的可靠性和稳定性。

7442中文资料

SYMULATED L+R

- L-R +

MUSIC

TREBLE-L 20

OFF

MUSIC/ SYMULATED

SURR

OFF

MIXING AMP

TREBLE

LPF 9KHz

EFFECT CONTROL

MIXING AMP

TREBLE SURR

30K

OFF

Vref SUPPLY

BIN(L) BOUT(L)

8

9

30K

100nF

PS1 17

RPS1

PS1 90Hz

-

+

+

SYMULATED L+R

- L-R +

MUSIC

5.6nF

TREBLE-L 18

5.BOUT(L)

14

15

RB

FIX

OFF

MUSIC/ SYMULATED

SURR

OFF

MIXING AMP

TREBLE

16

17

RB

FIX

BASS

VAR

-

+

FIX

I2C BUS DECODER + LATCHES

BASS

FIX

VAR

+

-

RB

4

11 13

MONITOR(R) MUXOUT(R)

18 27

28 26

LP

VS

CREF

22 TREBLE-R

14 BIN(R)

13 BOUT(R)

IN(R) AGND

2.2µF

1.2nF

元器件交易网

BL0942 应用指南说明书

BL0942应用指南目录版本信息 (1)芯片功能特点: (1)芯片管脚说明: (2)关于电参数转换 (3)关于有功功率防潜动阈值设置 (4)PCB设计注意事项 (5)BL0942是上海贝岭股份有限公司开发的一款用于物联网领域进行电能测量的专用芯片。

具有体积小(SSOP10L/TSSOP14封装),外围电路简单,成本低廉的优点。

芯片功能特点:●两路独立的Sigma-Delta ADC,一路电流和一路电压。

●电流有效值范围(10mA~35A)@1mohm●有功电能(1w~7700w)@1mohm●可测量电流电压有效值,快速电流有效值,有功功率,电流电压波形●批次出厂增益误差小于1%,外围元件满足一定条件下可以免校准●电流通道具备过流监控功能,监控阈值及响应时间可设置●电压/电流过零信号输出●内置波形寄存器,可输出波形数据用于负载类型分析●集成SPI(最快速率支持900KHz)/UART(4800-38400bps)通信方式●电源掉电监测,低于2.7V时,芯片进入复位状态●内置1.218V参考电压源●内置振荡电路,时钟约4MHz●芯片单工作电源3.3V,低功耗10mW(典型值)以SOP10L封装进行举例说明电流采样信号35mV rms 电压采样信号70mV rms电能脉冲输出或配置输出TX/SDO VDDIP INVP GNDSCLK_BPS SEL SSOP10LUART/SPI 通信接口应用电路图:以电阻采样为例进行说明,也可采用互感器方式进行采样;NL注意:1)CF1、CF2管脚可配置为过流报警输出;ZX 用于输出电压过零信号;如果仅需要电参数检测功能,这两个管脚可以不接入MCU ;2)SPI 、UART 接口的速率,通信协议的描述见“BL0942 datasheet v1.0.pdf ”;3)BL0920在出厂时已做增益修正,如果要免校准,外围器件的精度保证在1%以内; 4)TX 管脚需要外接上拉电阻; 考虑智能家居类产品一般最大电流不超过16A ,电流采用使用合金电阻1毫欧,电压采样通道使用电阻分压方式将220V 电压降低到57.52mV rms 由芯片的VP 管脚进行采样。

贴片稳压芯片bl9342参数

贴片稳压芯片BL9342参数一、BL9342芯片简介BL9342是一款贴片稳压芯片,具有高效、稳定、可靠的特点。

它适用于各种电子设备中的电源管理系统,能够提供稳定的电压输出,保障设备的正常运行。

二、BL9342芯片的主要参数BL9342芯片具有以下主要参数:1.输入电压范围:2.5V-5.5V2.输出电压范围:0.8V-3.6V3.输出电流:最大200mA4.输出电压精度:±2%5.软启动时间:约10ms6.过压保护:4.4V-4.6V7.短路保护:有8.超温保护:有9.工作温度范围:-40℃至+85℃10.封装形式:SOT-23-5三、BL9342芯片的功能特点1. 高效稳定BL9342芯片采用先进的稳压技术,能够在输入电压波动较大的情况下,保持输出电压的稳定性。

它能够有效地抑制电源噪声和纹波,提供高质量的电源输出。

2. 低功耗BL9342芯片在工作状态下具有较低的功耗,能够有效节省电池能量。

在待机或关机状态下,芯片能够进入低功耗模式,进一步降低功耗,延长电池寿命。

3. 多重保护BL9342芯片内置多重保护机制,能够有效保护电子设备和芯片本身的安全。

它具有过压保护、短路保护和超温保护功能,能够防止电路故障引起的损坏和安全问题。

4. 快速启动BL9342芯片具有快速启动功能,软启动时间约为10ms,能够快速响应设备的开机指令,提供稳定的电源输出。

四、BL9342芯片的应用领域BL9342芯片广泛应用于各种电子设备中的电源管理系统,包括但不限于以下领域:1.移动通信设备:智能手机、平板电脑、便携式音乐播放器等;2.消费电子产品:数码相机、便携式游戏机、蓝牙耳机等;3.工控设备:工业控制器、仪器仪表等;4.汽车电子:车载导航仪、车载音响等;5.家用电器:电视机、空调、冰箱等。

五、BL9342芯片的优势与劣势优势:•高效稳定的电源输出•低功耗,节省电池能量•多重保护机制,保障设备安全•快速启动,提供稳定的电源输出劣势:•输出电流较小,适用于低功耗设备,不适合高功耗设备六、BL9342芯片的未来发展趋势随着电子设备的不断发展,对电源管理系统的要求也越来越高。

hpc-7442参数

hpc-7442参数HPC-7442参数详解HPC-7442是一款高性能计算机,具有出色的处理能力和稳定性,适用于各种大规模计算任务。

本文将对HPC-7442的参数进行详细解析,以帮助读者更好地了解该产品。

一、处理器HPC-7442采用了先进的多核处理器,具有强大的计算能力。

该处理器拥有多个独立的计算核心,能够同时执行多个线程,实现高效的并行计算。

这使得HPC-7442在处理复杂的科学计算和大数据分析时表现出色。

二、内存HPC-7442配备了大容量的内存,能够存储大量的数据和程序。

高速的内存访问速度保证了计算任务的顺利进行,提高了系统的响应速度。

同时,HPC-7442还支持内存扩展,用户可以根据需要进行升级,满足不同计算需求。

三、存储HPC-7442具备高速的存储系统,能够快速读写大量数据。

它采用了先进的固态硬盘技术,具有更高的数据传输速度和更低的能耗。

这使得HPC-7442在处理大规模数据集时能够快速获取和存储数据,提高计算效率。

四、显卡HPC-7442配备了强大的图形处理单元(GPU),具有出色的图形处理能力。

GPU能够加速复杂的图形计算,如三维建模、渲染和科学可视化等。

这使得HPC-7442在科学研究、医学影像处理和虚拟现实等领域具有广泛的应用价值。

五、网络HPC-7442支持高速网络连接,能够实现大规模计算集群的互联。

它采用了先进的网络传输协议,具有低延迟和高带宽的特点。

这使得HPC-7442在分布式计算和并行计算任务中能够实现高效的数据交换和通信。

六、操作系统HPC-7442支持多种操作系统,包括Windows和Linux等。

用户可以根据实际需求选择合适的操作系统,以满足不同的计算环境和软件要求。

同时,HPC-7442还提供了丰富的开发工具和编程接口,方便用户进行软件开发和优化。

七、能耗管理HPC-7442采用了先进的能耗管理技术,能够根据实际负载情况进行动态调整,实现能源的有效利用。

BL6552三相电能监测及分析专用芯片数据手册说明书

BL6552三相电能监测及分析专用芯片数据手册V1.12目录1、产品简述 (6)2、基本特征 (7)2.1主要特点 (7)2.2系统框图 (8)2.3管脚排列 (9)2.4性能指标 (10)2.4.1 电参数性能指标 (10)2.4.2 极限范围 (11)3、工作原理 (12)3.1电流电压波形产生原理 (12)3.1.1 有功相位补偿 (13)3.1.2 通道偏置校正 (14)3.1.3 通道增益校正 (14)3.1.4 电流电压波形输出 (15)3.2有功功率计算原理 (16)3.2.1 有功功率输出 (17)3.2.2 有功功率校准 (17)3.2.3 有功功率的防潜动 (18)3.2.4 有功功率小信号补偿 (19)3.2.5 有功功率选择 (19)3.3有功能量计量原理 (20)3.3.1 有功能量输出 (20)3.3.2 有功能量脉冲输出选择 (21)3.3.3 有功电能脉冲输出比例 (22)3.4电流电压有效值计算原理 (23)3.4.1 有效值输出 (23)3.4.2 有效值输入信号的设置 (24)3.4.3 有效值刷新率的设置 (24)3.4.4 电流电压有效值校准 (24)3.4.5 有效值的防潜动 (25)3.5快速有效值检测原理 (26)3.5.1快速有效值输出 (26)3.5.2 快速有效值输入选择 (26)3.5.3 快速有效值累计时间 (27)3.5.4 电网频率选择 (27)3.6无功计算 (27)3.6.2 无功功率输出 (29)3.6.3 无功功率校准 (29)3.6.4 无功功率的防潜动 (30)3.6.5 无功功率小信号补偿 (31)3.6.6 无功能量输出 (31)3.7视在和功率因子计算 (32)3.7.1 视在功率和能量输出 (32)3.7.2 视在功率校准 (33)3.7.3 功率因子 (33)3.8三相电流和的计算 (34)3.8.1 电流和的输出 (34)3.8.2 电流和的调整 (34)3.8.3 电流和的比较 (34)3.9小信号补偿 (35)3.10电参数测量 (36)3.11.1 线周期计量 (36)3.11.2 线频率计量 (36)3.11.3 相角计算 (36)3.11.4 功率符号位 (37)3.11故障检测 (38)3.12.1 过零检测 (38)3.12.2 峰值超限 (38)3.12.3 线电压跌落 (39)3.12.4 过零超时 (41)3.12.5 过零指示 (42)3.12.6 电源供电指示 (42)4、内部寄存器 (44)4.1电参量寄存器(外部读) (44)4.2校表寄存器1 (46)4.3校表寄存器2 (48)4.4校表寄存器详细说明 (50)4.4.1 通道PGA增益调整寄存器 (50)4.4.2 相位校正相关寄存器 (50)4.4.3 有效值增益调整寄存器 (52)4.4.3 有效值偏置校正寄存器 (52)4.4.4 功率小信号补偿寄存器 (53)4.4.6 快速有效值相关设置寄存器 (55)4.4.7 故障检测相关寄存器 (55)4.4.8 ADC使能控制 (55)4.4.9 模式寄存器1 (55)4.4.10 模式寄存器2 (56)4.4.11 模式寄存器3 (56)4.4.12 中断状态寄存器 (57)4.4.13 中断屏蔽寄存器 (58)4.4.14 能量读后清零设置寄存器 (59)4.4.15 用户写保护设置寄存器 (59)4.4.16 软复位指令 (59)4.4.17 通道增益调整寄存器 (59)4.4.18 通道偏置调整寄存器 (60)4.4.19 功率增益调整寄存器 (61)4.4.20 功率偏置调整寄存器 (61)4.4.21 CF缩放比例寄存器 (62)4.4.22 AT1~3逻辑输出管脚配置寄存器 (63)4.5电参数寄存器详细说明 (64)4.5.1 波形寄存器 (64)4.5.2 有效值寄存器 (65)4.5.3 快速有效值寄存器 (65)4.5.4 有功功率寄存器 (66)4.5.5 无功功率寄存器 (67)4.5.6 视在功率寄存器 (67)4.5.7 电能脉冲计数寄存器 (68)4.5.8 波形夹角寄存器 (70)4.5.9 功率因数寄存器 (70)4.5.10 线电压频率寄存器 (71)5、通讯接口 (72)5.1SPI (72)5.1.1 概述 (72)5.1.2 工作模式 (72)5.1.3 帧结构 (72)5.1.4 读出操作时序 (74)5.1.5 写入操作时序 (74)5.1.6 SPI接口的容错机制 (75)5.2 UART (76)5.2.1 概述 (76)5.2.2 每个字节格式 (76)5.2.3 读取时序 (76)5.2.4 写入时序 (77)5.2.5 UART接口的保护机制 (77)6、封装信息 (78)6.1订单信息 (78)6.2封装 (78)6.3封装外观 (78)1、产品简述BL6552是一颗7通道三相电能监测及分析芯片,适用于三相智能断路器、三相导轨表、电测仪表、大功率设备电源监控等应用,具有较高的性价比。

BL5372用户手册

2.5.2 万年历功能BL5372可以与CPU交换年份(低两位)到秒的时钟数据。

当年份的低两位能被4整除时,该年为闰年。

它能够自动识别2000~2099年的年份。

这些数据分别存放在0H~6H 的寄存器中。

2.5.3 高精度的时间调整功能BL5372振荡电路可以通过CGND、CVDD电容微调晶体振荡器的精度;最重要的精度调整还是通过BL5372内部集成的数字化的时间精度调整电路(内部地址7H),它根据CPU检测出的晶振本身的频率,再写入调整电路寄存器中,可以有效的调整时钟走时的精度(±1.5ppm)。

调整范围:±189ppm(±194ppm当使用32.000KHz晶振时),最小的调整步长为3ppm。

▲ 使用精度偏差较大的晶体也可以使时钟走时保持高精度▲ 能够调整由于晶振季节性偏差导致时钟走不准情况▲ 对于配有温度检测的系统,能有效的调整晶振精度随温度波动带来的走时偏差情况2.5.4 报时功能与周期性中断报时功能:定时寄存器内部地址为(8H~DH),当星期、时、分与定时寄存器预设的时间吻合时,两套定时中断信号就可以从INTRA、INTRB输出。

其两套报时系统(ALARM-A,ALARM-B),根据所设定的时间,分别产生独立的中断信号。

报时功能的开启与关闭可以通过控制寄存器1(内部地址EH)中的D7,D6位选择,也可以通过星期来选择,这样就能选择每天或者一个星期中的几天产生特定的中断。

ALARM-A只能从INTRA输出,而ALARM-B可以从INTRA或者INTRB引脚输出,到底从哪个引脚输入通过控制寄存器(内部地址EH的D4、D5)可以选择的。

周期性中断:BL5372除了从INTRA、INTRB引脚能够输出闹钟信号,还能输出周期性中断脉冲。

该周期性中断频率可以从2Hz、1Hz、1/60Hz、1/3600Hz和一个月通过控制寄存器1(内部地址EH的低三位)选择性输出。

周期性中断输出波形包括:标准的脉冲波形(2Hz和1Hz)和电平波形(每秒、每分、每时、每月)2.5.5 停振检测功能BL5372配有专门的寄存器(内部地址FH的XSTP位)来保存晶振停振信息。

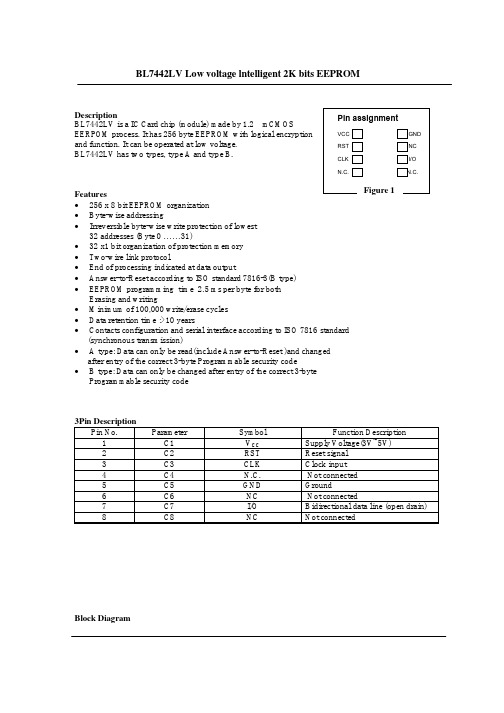

BL7442LV Low voltage lntelligent 2K bits EEPROM

Description BL7442LV is a IC Card chip (module) made by 1.2mCMOSEERPOM process. It has 256 byte EEPROM with logical encryptionand function. It can be operated at low voltage. BL7442LV has two types, type A and type B.Features• 256 x 8 bit EEPROM organization • Byte-wise addressing• Irreversible byte-wise write protection of lowest32 addresses (Byte 0 ……31)• 32 x1 bit organization of protection memory • Two-wire link protocol• End of processing indicated at data output• Answer-to-Reset according to ISO standard 7816-3(B type) • EEPROM programming time 2.5 ms per byte for bothErasing and writing• Minimum of 100,000 write/erase cycles • Data retention time :>10 years• Contacts configuration and serial interface according to ISO 7816 standard (synchronous transmission)• A type: Data can only be read(include Answer-to-Reset )and changed after entry of the correct 3-byte Programmable security code• B type: Data can only be changed after entry of the correct 3-byteProgrammable security code3Pin DescriptionPin No. Parameter Symbol Function Description 1 C1 V CC Supply Voltage(3V~5V) 2 C2 RSTReset signal 3 C3 CLK Clock input 4 C4 N.C. Not connected 5 C5 GND Ground 6 C6 NC Not connected 7 C7 I/O Bidirectional data line (open drain) 8 C8 NC Not connectedBlock DiagramTechnical Data•Absolute Maximum RatingsParameter SymbolLimitValues Unit Test Condition min. typ. MaxSupply voltage V CC-0.3 6.0 V Input voltage (any pin) V I-0.3 6.0 V Storage temperature T S-40 125 O C Power comsumption PT - 70 mw Operation temperature -35 70 O C•DC CharacteristicsParameter Symbol LimitValuesUnit Test ConditionSupply voltage V CC 2.7 5.0 5.5 V Supply current I CC 3 10 mA High-level inputvoltage(I/O,CLK,RST)V IH V CC -1 - V CC +0.3 VLow-level input voltage (I/O,CLK,RST) V IL V GND-0.2- V GND+0.8VHigh-level input current(I/O,CLK,RST)I H- - 50 uALow-level output current(I/O) I OL 1 - - mA V OL=0.4V,opendrainHigh-level leakage current(I/O) I OH- - 50 A V OH =V CC,open drainInput capacitance C I- - 10pF •AC CharacteristicsParameter SymbolLimitValuesUnit TestCondition min. typ. MaxClock frequency CLK 7 50Clock high period t H9 s Clock low period t L9 s Rise time t R 1 s Fall time t F 1 s Hold time start condition t d1 4 us Delay time t d2 2.5 us Setup time for stop condition t d3 4 s Setup time t d4 4 s Hold time data t d5 1 s Answer to reset t d620 s Setup time data t d7 1 s Setup time for start condition t d78 4 s Reset t RES 5 s Delay time t dg 2.5 s Eraser time T ER 2.5* ms Write time t WR 2.5* ms Time before new startconditionT BUF10 s *f =50 kHzFunction DescriptionmemoryWith PROM functionality .The main memory is erased and written byte by byte. When erased, all 8 bits of a data byte are set to logical one. When written, the information in the individual EEPROM cells is to the input data, altered bit by bit to logical zeros (logical AND between the old and the new data in the EEPROM).Normally a data change consists of an erase and write procedure. It depends on the contents of the data byte in the main memory and the new data byte whether the EEPROM is really erased and/or written. If none of the 8 bits in the addressed byte requires a zero-to-one transition the erase access will be suppressed. Vice versa the write access will be suppressed if no one-to-zero transition is necessary. The write and the erase operation takes at least 2.5 ms each. The first 32 bytes can be irreversibly protected against data change by writing the corresponding bit in the protection memory. Each data byte in this address range is assigned to one bit of the protection memory and has the same address as the data byte in the main memory which it is assigned to. Once written the protection bit cannot be erased.Additionally to the above functions the BL7442LV provides a security code logic which controls the write/erase access to the memory. For this purpose ,the BL7442LV contains a4-byte security memory with an error counter EC (bit 0 to bit 2) and 3 bytes reference data(figure 2).These 3 bytes as a whole are called programmable security code (PSC). After poweron the whole memory, except for the reference data, BL7442LV type B can only be read. Writing and erasing is only possible after a successful comparison of verification data with the internal reference data. After power on the whole memory,BL7442LV type A is neither written, erased nor read. Reading, writing and erasing is only possible after a successful comparison of verification data with the internal reference data. After three successive unsuccessful comparisons the error counter blocks any subsequent attempt, and hence any possibility to write and erase.Transmission ProtocolThe transmission protocol is a two wire link protocol between the interface device IFD and the integrated circuit IC. It is identical to the protocol type “S=10”. All data changes on I/O are initiated by the falling edge on CLK.The transmission protocol consists of the 4 modes:(1)Reset and Answer-to-Reset(2)Command Mode(3)Outgoing Data Mode(4)Processing Mode(1)Reset and Answer-to-Reset (BL7442LV type B only)Answer-to-Reset takes place according to ISO standard 7816-3.The reset can be given at any time during operation. In the beginning, the address counter id set to zero together with a clock pulse and the first data bit (LSB) is output to I/O when RST is set from state H to state L. Under a continuous input of additional 31 clock pulses the contents of the first 4 EEPROM addresses can be read out. The 33rd clock pulse switches I/O to state H (figure 3). During Answer-to-Reset any start and stop condition is ignored.V CC RST CLK I/O1233132RSTCLK I/Ot d4t d4t d2t H t Lt d5Figure 3 Reset and Answer-to-Reset(2)Command ModeAfter the Answer-to-Reset the chip waits for a command. Every command begins with a start condition, includes a 3 bytes long command entry followed by an additional clock pulse and ends with a stop condition (figure 4).--Start condition: Falling edge on I/O during CLK in state H --Stop condition: Rising edge on I/O during CLK in state Ht f I H t R t Ht d7t d5t d3t d1t d8I BufCLKI/OCLK I/OComma nd231231Figure 4 Command ModeAfter the reception of a command there are two possible modes: --Outgoing data mode for reading--Processing mode for writing and erasing(3)Outgoing Data ModeIn this mode the IC sends data to the IFD. Figure 5 shows the timing diagram. The first bit becomes valid on I/O after the first falling edge on CLK. After the last data bit an additional clock pulse is necessary in order to set I/O to state H and to prepare the IC for a new command entry. During this mode any start and stop condition is discarded.I/O123n-1nCLKI/Ot d2Figure 5 Outgoing Data Mode(4)Processing ModeIn this mode the IC processes internally. Figure 6 shows the timing diagram. The IC has to be clocked continuously until I/O which was switched to state L after the first falling edge of CLK is set to state H. Any start and stop condition id discarded during this mode.CLKt d2t d2Figure 6 Processing ModeCommands(1)Command FormatEach command consists of three byte: MSB Control LSB MSB Address LSBMSB Data LSBBeginning with the control byte LSB is transmitted first.Byte 1 ControlByte 2AddressByte 3DataOperation ModeB7 B6 B5 B4 B3 B2 B1B0A7~A0 D7~D00 0 1 1 0 0 0 0 Address No effect ReadMain Memory Outgoing data0 0 1 1 1 0 0 0 Address Input data UpdateMain MemoryProcessing0 0 1 1 0 1 0 0 No effect No effect Read ProtectionMemory Outgoing Data0 0 1 1 1 1 0 0 Address Input data WriteProcectionMemoryProcessing0 0 1 1 0 0 0 1 No effect No effect Read SecurityMemory Outgoing Data0 0 1 1 1 0 0 1 Address Input data Update SecurityMemoryProcessing0 0 1 1 0 0 1 1 Address Input data CompareVerificationDataProcessing(2)Description of CommandRead Main MemoryThe command reads out the contents of the main memory(with LSB first)starting at the given byte address(N) UP TO THE END MEMORY. After the command entry the IFD has to supply sufficient clock pulses. The number of clocks is m=(256-N)*8+1.The read access to the main memory is always possible.Read Protection MemoryThe command transfers the protection bits under a continuous input of 32 clock pulses to the output. I/O is switched to state H by an additional pulse. The protection memory can always be read.Read Security MemorySimilar to the read command for the protection memory this command reads out the 4 bytes of the security memory. The number of clock pulses during the outgoing data mode is 32.I/O is switched to state H by an additional pulse. Without a preceeding successful verification of the PSC the output of the reference bytes is suppressed, that means I/O remains in state L.Update Main MemoryThe command programs the address EEPROM byte with the data byte transmitted. Depending on the old and new data, one of the following sequences will take place during the processing mode:-- erase and write (5ms) corresponding to m = 255 clock pulses-- write without erase (2.5ms) corresponding to m = 124 clock pulses-- erase without write (2.5ms) corresponding to m =124 clock pulses(all values at 50 kHZ clock rate)12324123m-2m-1m1224Command EntryProcessingCLK I/O RSTFigure 7 Update Main MemoryUpdate Security MemoryRegarding the reference data bytes this command will only be executed if a PSC has been successfully verified before. Otherwise only each bit of the error counter (Address 0)can bewritten from “1” to “0”.The execution times and the required clock pulses are the same as described under Update Main Memory. Write Protection MemoryThe execution of this command contains a comparison of the entered data byte with theassigned byte in the EEPROM .In case of identity the protection bit is written thus making the data information unchangeable. If the data comparison results in data differences writing of the protection bit will be suppressed. Execution times and required clock pulses see Update Main Memory. Compare Verification DataThis command can only be executed in combination with an update procedure of the error counter(see Usage of Compare Command).The command compares one byte of the entered verification data byte with the corresponding reference data byte. For this procedure clock pulses are necessary during the processing mode.A type: Before data comparison , I/O pin is high impedance. Because the data of error counter (EC) can not be read, the identification of EC is different from BL7442. After power on, whatever EC is in which state, it is considered to 111(07H), Then the EC is written one bit and compared one time, After comparison is correct(can be read out the content of PSC),it will be written back to 07H.If original data of EC is 07H, it is same as type B. If original data of EC is not 07H,the security code verification is unsuccessful. Although security code is correct, EC operation is of no effect when EC is equal to 01H or 03H. Both A andB type the internal operation is same. The difference between type A and type B is only type A can not be read out the content of EC.B type: It is same as BL7442.Usage of the Compare CommandThe following procedure has to be carried out exactly as described. Any variation leads to a failure so that a write/erase access will not be achieved. As long as the procedure has not been successfully concluded the error counter bits can only be changed from “1” to “0” but not erased.All first an error counter bit has to be written to “0” by an UPDATE command (see figure 8)followed by three COMPARE VERIFICATION DATA commands beginning with byte 1 of the reference data. A successful conclusion of the whole procedure can be recognized by being able to erase the error counter which is not automatically erased. Now write/erase access to all memory areas is possible as long as the operating voltage is applied. In case of error the whole procedure can be repeated as long as erased counter bits are available. Having been enabled, the reference data are allowed to be altered like any other information in the EEPROM.As shipped, the RSC is programmed with a code according to individual agreement with the customer. Thus, knowledge of this code is indispensable to alter data.Figure 8 Verification ProcedureReset Modes(1)Power-on-ResetAfter connecting the operating voltage to VCC ,I/O is state H. By all means, a read access to an address or an Answer-to-Reset must be carried out before data can be altered.(2)BreakIf RST is set to high during CLK in state L any operation is aborted and I/O is switched to state H. Minimum duration of Tres=5us is necessary to trigger a defined valid reset(figure 9).After Break the chip is ready for further operations.t RCSt d9RSTCLK I/OFigure 9 BreakFailuresBehavior in case of failures:In case of one of the following failures, the chip sets the I/O to state H after 8 clock pulses at the latest.ºóEC=Error counter SM=Security memory VD=Verification dataCommands Verification Procedure Comparison blockComparison Unseccessful number of "1"=number of possible retriesByte 1Byte 2Byte 3Address 1Address 2Address 3Compare VD Compare VD Compare VDPossible failures:--Comparison unsuccessful --Wrong command--Wrong number of command clock pulses --Write/erase access to already protected bytes--Rewriting and erasing of a bit in the protection memoryCoding of the ChipDue to security purposes every chip is irreversibly coded by a scheme. By this way fraud and misuse is excluded. As an example, figures 10 and 11 show ATR and Directory Data of structure 1.When delivered, ATR header, ICM and ICT are programmed. Depending on the agreement between the customer and Shanghai Belling CO. LTD. ICCF, the chip type and other content can be also programmed before delivery.Figure 10 Synchronous Transmission ATR and Directory Data of Structure1ICT LA LDLM LT AID Application identifierApplicationpersonalizer identifier AP ATR DirectoryDIR H1,H2ATR protocol bytes H3,H4ATR historical bttes TA ICCF ·ûTD ICCSN TM ICM IC manufacturer identifier IC typeTTAnswer-to-Reset Length of application templateLength of AIDIC card serial number IC card fabricator identifierTag of application dataTag of manufacturer data Tag of discretionary data Tag of AIDLength of application template Length of manufacturer dataFigure 11 Answer-to-Reset for Synchronous Transmission Coding of Structureb8b7b6b5b4b3b2b1b8b7b6b5b4b3b2b1b8b7b6b5b4b3b2b1b8b7b6b5b4b3b2b110100010000100110001000010010001RFU(2 )xx b8=1b7-b1=b8=0b7-b1=00=000=001=128010=256011=512100=1024101=2048110=4096111=RFU 0:1:1:0:Protocol bytes according to ISO 7816-3Historical bytes acoording to ISO 7816-4Protocol type H1Protocol parameter H2Category indicator H3DIR data reference H4Protocol type RFUStructure indentifierno indication Number of data units Length of data units in bits Categoryindicator according to ISO7816-4reference ofDIR dataOutside the scopeof 7816-40-7 =defined by ISO 8-E = notdel. by ISO 8= serial data accessprotocol9=3 wire bus protocol A=2 wire bus protocolF=RFUDIR data referencespecifiedDIR data reference not specifiedRead to end Read with defined lengthdefined by ISOnot defined by ISO10=structure 101=structure 211=structure 3I 0.16?.03Figure 12 Chip and Package Outlines Wire-Bonded Module M2.2。

2K存储卡/加密存储卡集成电路——BI7432/BL7442

2K存储卡/加密存储卡集成电路——BI7432/BL7442马犁

【期刊名称】《计算机与信息处理标准化》

【年(卷),期】1997(000)001

【总页数】2页(P12-13)

【作者】马犁

【作者单位】上海贝岭

【正文语种】中文

【中图分类】TN430.2

【相关文献】

1.基于SLE4442加密存储卡的汽车行驶记录仪中驾驶员身份识别系统设计 [J], 栗方;陆二庆

2.AT88SC1604加密存储卡的应用设计 [J],

3.逻辑加密存储卡的操作控制程序设计 [J], 黄智伟;李富英

4.BL7432/BL7442—2K位IC存储卡/加密存储卡集成电路 [J], 马犁

5.用"明码"记忆逻辑加密存储卡SLE4442的"密码" [J], 杨瑞生

因版权原因,仅展示原文概要,查看原文内容请购买。

7442逻辑功能和真值表

7442逻辑功能和真值表

7442是一种二-十进制译码器,具有4个输入端和10个输出端。

其逻辑功能是将每

个输入的二进制代码译成对应的输出高、低电平信号或另外一个代码。

其真值表具体如下:

1.当输入A、B、C为000时,输出Y0为低电平;

2.当输入A、B、C为001时,输出Y1为低电平;

3.当输入A、B、C为010时,输出Y2为低电平;

4.当输入A、B、C为011时,输出Y3为低电平;

5.当输入A、B、C为100时,输出Y4为低电平;

6.当输入A、B、C为101时,输出Y5为低电平;

7.当输入A、B、C为110时,输出Y6为低电平;

8.当输入A、B、C为111时,输出Y7为低电平;

9.当输入A、B、C为0时(灭零),输出RBO’为高电平;

10.当输入A、B、C为1时(灭零),输出RBI’为高电平。

综上所述,7442二-十进制译码器具有真值表功能,可以实现将二进制代码转换为相应的输出信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

BL7442LV 还提供一个控制对存储区进行写入/擦除操作的密码逻辑。为此包含了一个

具有出错计数器 EC(位 0 至位 2)和 3 字节参考数据的 4 字节保密存储区(见框图)。这 3

数据

更新主存储器

处理

0 0 1 1 0 1 0 0 无效

无效

读保护存储器

数据输出

0 0 1 1 1 1 0 0 地址

数据

写保护存储器

处理

0 0 1 1 0 0 0 1 无效

无效

读保密存储器

数据输出

0 0 1 1 1 0 0 1 地址

数据

更新保密存储器

处理

0 0 1 1 0 0 1 1 地址

数据

比较密码*

此命令只能与出错计数器的一次更新步骤组合使用(见比较命令用法),该命令将输 入的一个认证数据字节和对应的参考数据字节进行比较,对此过程来说,处理模式期间 的时钟脉冲是必需的(至少 2 个脉冲)。

A 型:在比较认证数据前,IO 口呈高阻态。由于出错计数器 EC 的数据无法读出,因此 对 EC 的判别不同于 B 型。在芯片上电后,无论 EC 处于何种状态,都将其作为 111 (07H)状态,然后对 EC 记数器写一位,比较一次,比较正确(能读出 PSC 内容) 后,再把它写回 07H。如原先 EC 的数据为(07H)的话,则和 B 型(或 BL7442) 相同,也有三次密码验证的机会。如原先 EC 的数据不为 07H,那么,会出现第一 次或前二次(EC 分别为 01H 或 03H)验证时,虽然密码正确但因对 EC 的操作没 起作用而比较不通过的情况。不管是 A 型还是 B 型,芯片内部的操作相同,仍然 按照实际 EC 数据进行,三次操作失败芯片自锁。

Command

-1Total 11 Pages

C6 C5 C4

8/16/2006

BL7442LV 2K 位 EEPROM 逻辑加密存 储卡

四、功能描述

1、原理框图 BL7442LV 电路原理如图 1 所示。

主存贮区 255

EEPROM 256X8 32 31 可 由 保 护 位 封锁的字节 0 范围 地址 数据

期间将执行下述操作序列中一种。

-擦除和写入

(5ms)对应于 m=255 个时钟脉冲

-不进行擦除而直接写入 (2.5ms) 对应于 m=124 个时钟脉冲

-只进行擦除而无写入

(2.5ms) )对应于 m=124 个时钟脉冲

(所有数值是按 50kHz 时钟速率计算所得)

命命命命

处处

CLK

123

24

123

二、产品特点

• 字节寻址:每字节 8 位,共 256 字节 • 32 X 1bit 保护存储器结构 • 最低 32 地址(0…31 字节)不可逆字节写保护 • 双线通讯协议、触点定义和串行接口符合 ISO7816 标准(同步传输) • 复位应答符合 ISO7816-3 标准 • 读写次数大于 10 万次 • 单字节的擦、写编程时间各为 2.5ms • 数据输出时指示处理结束 • BL7442LV 有 Type A 和 Type B 两中类型 • A 型:只有在输入正确的 3 字节可编程密码(PSC)后,数据才可读出和改变 • B 型:只有在输入正确的 3 字节可编程密码(PSC)后,数据才可改变

-5Total 11 Pages

8/16/2006

BL7442LV 2K 位 EEPROM 逻辑加密存 储卡

复位应答时序如图 4 所示。

VCC

RST

1

2

3

4

...

CLK

1

2

3

...

I/O

RST CLK I/O

td4

td4

tH

tL

td2

td5

图 4 复位应答时序

图 3:PSC 认证过程

3.3 传输协议和命令时序

传输协议为接口设备 IFD 和 IC 之间的两线连接协议。协议类型标识为"S=10"。I/O 上

的所有数据交换由 CLK 的下降沿触发。

传输协议由 4 个模式组成:

(1)复位和响应复位

(2)命令模式

(3)数据输出模式

(4)处理模式

【复位应答】 响应复位按 ISO78163 标准产生。在操作期间,任何时候都可以给出复位信号。复位时,

假使出错,只要错误计数器还有 1 位,上述整个过程就可以重新进行。在密码比较 通过后,参考数据可以象 E2PROM 中的任何其它信息一样被改变。在电路(模块)发运时, PSC 根据与用户之间独立协议进行编码,这样,要改变数据就必须知道此代码。

比较 被封锁

认证过程

读 EC

Y (EC)=000? N

将 EC的一位 写为 ”0”

3、命令和基本时序 3.1 命令格式 BL7442LV 的命令包括三个字节:命令码,地址码,数据码。命令格式如表 1 所示。 表1

命令码

地址码

数据码

B7 B6 B5 B4 B3 B2 B1 B0 A7 A6 A5 A4 A3 A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0

MSB

LSB MSB

地址计数器由一时钟脉冲置到零;当 RST 从 H 态置成 L 态时,第一个数据位(LSB)输出到 I/O。通过此后连续的 31 个时钟脉冲,可读出前 4 个 E2PROM 地址单元中的内容。第 33 个时钟脉冲将 I/O 置成 H 态。在响应复位期间,忽略所有启动和停止条件。复位应答时序如 图 4 所示。

同后才可进行读出、写入和擦除操作。密码比较有三次机会,在三次比较失败后,出错

计数器就封锁所有后续的任何尝试,即禁止对电路的任何擦、写、读(仅对 A 型)操作。

-2Total 11 Pages

8/16/2006

BL7442LV 2K 位 EEPROM 逻辑加密存 储卡

BL7442LV 为一款 2K 位存储卡电路,具有一个 256 字节的 E2PROM 主存储区(见框图) 和一个 32 位 PROM 保护存储区。主存储区按字节进行擦除和写入。擦除时,数据字节的 8 位都置为逻辑 1;写入时,E2PROM 各单元的信息,可根据输入数据按位改写成逻辑 "0"(EEPROM 中数据与输入的新数据进行逻辑与)。通常,一次数据的改写过程由一次擦除 和一次写入过程组成。E2PROM 单元是否真的被擦除和(或)写入取决于主存储区中数据字节 和新的数据字节的内容。如果指定位字节的 8 位没有一位需要 0 至 1 的翻转, 就跳过擦除操 作。反之,如果不需要 1 至 0 的翻转, 就省却写入操作。写和擦除的工作至少需要 2.5ms。

比较认证数 据参考数据

擦除 EC

比较失败 后 1 个数 =可以再试的次数

N

读EC

(EC)=111? Y

命令 读 SM

更新 SM 地址

数据

比较 VD 比较 VD 比较 VD

地址 地址 地址

1 2 3

字节数据1 字节数据2 字节数据3

更新 SM 地址 0 111111111

读SM

EC=出错计数器 SM=保密存贮器 VD=认证数据

类似于保护存储区的读命令,此命令读出保密存储区的 4 个字节。数据输出模式期 间的时钟脉冲数为 32。通过一个附加脉冲,I/O 被置成 H 态。如无预先成功的 PSC 认证, 参考数据字节的输出就被禁止的,这意味着 I/O 仍然处在"L"态。 (6)更新保密存储区

关于参考数据字节,只有在成功地认证了 PSC 后,此命令才能执行,否则,只有 出错计数器(地址 0)的各位可以有从"1"写成"0"的更新。执行时间和所需的时钟脉冲与 上述"更新主存储区"的相同。 (7)比较认证数据

三、管脚描述

C1

C2

C3

M3 模块管脚描述

M2 模块管脚描述

M2 模块触点 M3 卡模块触点

C1

C1

C2

C2

C3

C3

C4

C5

C4

C6

C5

ቤተ መጻሕፍቲ ባይዱC7

C6

C8

符号 功能描述 VCC 工作电压 3V~5V RST 复位 CLK 时钟 NC 不用 GND 接地 NC 不用 I/O 输入/输出 NC 不用

BL7442LV 2K 位 EEPROM 逻辑加密存 储卡

一、概述

BL7442LV 是上海贝岭自行开发、采用 1..2 um CMOS E2PROM 工艺制造的 2Kbit 加密 IC 卡芯片。256 字节,带写保护功能,具有可编程密码(PSC),可在 3V~5V 电压下工作。 BL7442LV 有 A 型和 B 型两种,可用于电子消费卡、公司卡、健康卡、会员卡和 ID 卡等等。 上海贝岭对此产品拥有集成电路版图设计版权(登记号:BS.02500046.2)和相关专利授权。

"H"状态。保护存储区是可读的。 (4)写保护存储区

此命令的执行包括一个输入数据字节与 E2PROM 中指定字节的比较过程,如果指定字 节的数据与指令输入数据一致,就执行写保护位操作,使此数据信息成为不可改变的。如果 两者数据不同,写保护位的操作就将被禁止。执行时间和所需脉冲同"更新主存储区"。 (5)读保密存储区

31

32

30

31

32

【命令输入】 响应复位后,IC 等待命令的输入。每条命令从一启动条件开始,包括 3 个字节长的命

令体及其后的一个附加时钟脉冲,最后由停止条件结束(参见图 5)。 -启动条件:CLK 处于 H 态期间,I/O 线上的下降沿 -停止条件:CLK 处于 H 态期间,I/O 线上的上升沿 命令输入时序如图 5 所示。