Vivado中debug用法

debug指令详解

debug指令详解debug指令详解一、DEBUG概述DEBUG是在DOS状态下面供程序员使用的程序调试工具。

它可以用来检查内存中任何地址中的内容以及修改特定地址中的内容。

DEBUG还可以用于逐指令执行某个程序,追踪程序的执行过程,比较一条指令执行前后数值变化情况,读写文件与磁盘扇区。

此外,DEBUG还可以用于读写端口中的数值。

在DEBUG状态下,所有数据都作为字节序列,可以用DEBUG把任何类型的文件读入内存中。

DEBUG能够处理的数据为两种: 十六进制数和ASCⅡ码,使用两位数表示十六进制数据(0~9,A~F)。

在DEBUG中涉及内存中的数据时,要指定数据所在的内存单元的地址,地址的输入格式是: [段地址]: [位移]。

如果没有输入地址,DEBUG将假定为当前内存段,从位于地址100H的字节开始。

前100H字节保留给程序段前缀使用(称PSP结构,包含程序执行的各种信息),该区域用于建立DOS与程序之间的联系。

在DEBUG中,使用四位十六进制数表示地址(0~9,A~F)。

DEBUG输入数据时有两种方法: 提示方法和非提示方法。

在提示方法下,输入要求输入数据的命令,后跟保存数据的地址。

执行后可以看到该地址中已有的内容及一个冒号提示符。

此时可以在提示符下输入一个新的值或者按下回车键或CTRL+C回到“—”提示符。

在非提示方法下,输入保持数据的内存地址以及要输入的数据。

DEBUG 的启动:进入DOS状态下,键入DEBUG ,按ENTER键,如:C:\>DEBUG ,则屏幕显示:-符号“-”是进入DEBUG的提示符,在该提示符下可键入任意DEBUG命令。

DEBUG的退出:在DEBUG的提示符后输入Q命令,按ENTER键,则退出DEBUG 返回DOS。

DEBUG的使用:在DEBUG的提示符后输入DEBUG命令,按ENTER键。

二、DEBUG 命令详解★ A命令格式:A[地址]功能:将指令直接汇编成机器码输入到内存中。

VIVADO中debug用法

VIVADO中debug用法VIVADO和ISE相比ChipScope已经大幅改变,很多人都不习惯。

在ISE中称为ChipScope而VIVADO中就称为in system debug。

下面就介绍VIVADO中如何使用debug工具。

Debug分为3个阶段1.探测信号:在设计中标志想要查看的信号2.布局布线:给包含了debug IP的设计布局布线3.分析:上板看信号一探测信号探测信号有2种方法一种是直接在HDL源代码中用(*mark_debug = “true”*)标识出要探测的信号另一种是在综合过后的网表文件中添加标志。

1 .在HDL源代码中添加标志然后点击 open Synthesized Design然后点击Tools-> Set Up Debug点击 Next点击 Add/Remove Nets点击find会出来所有信号。

如果需要添加debug的信号,从左边框中选择所需信号,点击按钮加到右边来。

如果需要去除不需要的debug信号,从右边框中选择所需信号,点击按钮就去除了。

选好信号之后,在右下角点击Ok按钮。

在此框中为所有debug信号选择时钟域,选择debug信号,右键选择Select Clock Domain。

注意每一个时钟域对应一个单独的ILA 2.0core。

在此框中选择所需时钟,点击ok点击next然后继续下面的Implement 流程点击Save保存修改后的工程后面像以前一样等工程跑结束。

2.在网表文件中添加标志网表文件添加标志,第一步也是打开综合后设计。

如下图所示第二步是打开debug窗口Open synthesized Design之后,有2种方法来标志debug信号(1)第一种方法是在Netlist窗口中选择信号,右键点击Mark Debug(2)第二种方法是在Tools中选择Setup Debug 推荐使用此方法然后和前面一样继续跑工程。

二上板调试上板的时候选择Open hardware session ,然后Open a new hardware target选择next选择next选择Next选择FPGA来配置文件注意移到另一台电脑看debug信号时,必须将debug_nets.ltx 文件和bit文件一起移过去。

VIVADO设计工具使用方法

Vivado使用方法

一、软件安装 二、建立工程 三、建立仿真环境 四、为工程添加约束 五、综合、布局布线和生成bit文件 六、debug

一、软件安装

一、软件安装

一、软件安装

一、软件安装

一、软件安装

二、建立工程

二、建立工程

二、建立工程

二、建立工程

二、建立工程

二、建立工程

添加一个模块设计

六、debug

在对程序进行debug时,vivado为我们提供了ILA工具,他和 ISE下的chipscope同样可以用JTAG的方式让我们看到芯片内部的 信号。他的启动方式和使用方法和chipscope略有不同。 ILA工具允许我们在代码中标注debug时观测的信号,在代码 中声明为”DEBUG”,即使没有连接到其他模块,也不会被优化掉。 这样方便我们添加和找到需要观察的信号。 ILA也可以和chipscope一样在完成综合后,查找信号并添加 到ILA中。 除此之外ILA可以允许添加多个采样时钟,对不同组观测信号 一起在vivado下编译。这样可以提高debug时的工作效率。

二、建立工程

添加模块设计后,在设计区域提示添加IP,点击“add IP”添加 IP或者点击工具栏图标添加

添加IP

二、建立工程

在IP搜索栏输入Ipcore的名称可以帮助我们快速找到需要添加的IPcore

二、建立工程

添加IP core后工具自动提示添加外设连线,可以根据工具提示自动完成模块之间 的连接。

三、建立仿真环境

在tcl命令窗口,我们 敲入help可以获得关于 vivado软件操作的帮助说 明。 此时我们先输入help, 然后在给出的帮助主题中 选择simulation主题继续查 找帮助。在simulation主题 下给出的帮助包括添加文 件,编译仿真库和配置编 译仿真文件等等多个帮助 主题,我们选择编译仿真 库主题。

Vivado 设计流程指导手册 (含安装流程与仿真)

Vivado设计流程指导手册——2013.4Vivado设计分为Project Mode和Non-project Mode两种模式,一般简单设计中,我们常用的是Project Mode。

在本手册中,我们将以一个简单的实验案例,一步一步的完成Vivado 的整个设计流程。

一、新建工程1、打开Vivado 2013.4开发工具,可通过桌面快捷方式或开始菜单中Xilinx Design Tools->Vivado 2013.4下的Vivado 2013.4打开软件,开启后,软件如下所示:2、单击上述界面中Create New Project图标,弹出新建工程向导,点击Next。

3、输入工程名称、选择工程存储路径,并勾选Create project subdirectory选项,为工程在指定存储路径下建立独立的文件夹。

设置完成后,点击Next。

注意:工程名称和存储路径中不能出现中文和空格,建议工程名称以字母、数字、下划线来组成。

4、选择RTL Project一项,并勾选Do not specify sources at this time,勾选该选项是为了跳过在新建工程的过程中添加设计源文件。

点击Next。

5、根据使用的FPGA开发平台,选择对应的FPGA目标器件。

(在本手册中,以Xilinx官方开发板KC705为例,Nexys4开发板请选择Artix-7 XC7A100TCSG324-2的器件,即Family和Subfamily均为Artix-7,封装形式(Package)为CSG324,速度等级(Speed grade)为-1,温度等级(Temp Grade)为C)。

点击Next。

6、确认相关信息与设计所用的的FPGA器件信息是否一致,一致请点击Finish,不一致,请返回上一步修改。

7、得到如下的空白Vivado工程界面,完成空白工程新建。

二、设计文件输入1、如下图所示,点击Flow Navigator下的Project Manager->Add Sources或中间Sources中的对话框打开设计文件导入添加对话框。

VIVDAO DEBUG信号

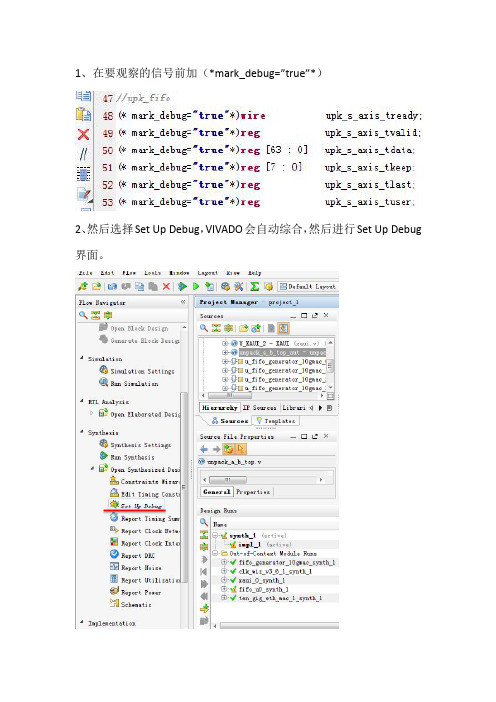

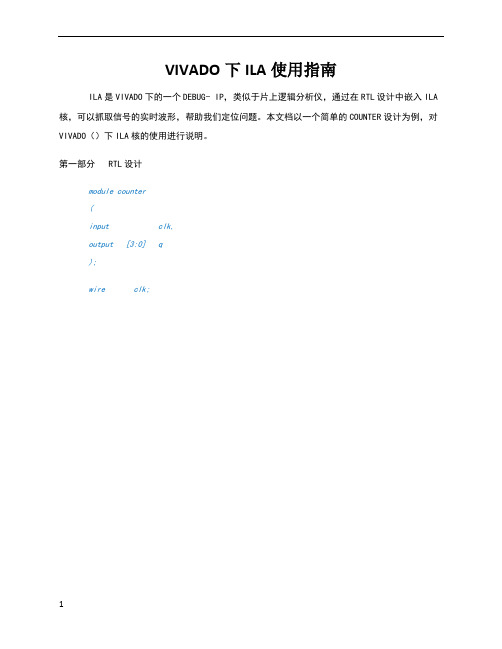

1、在要观察的信号前加(*mark_debug=”true”*)

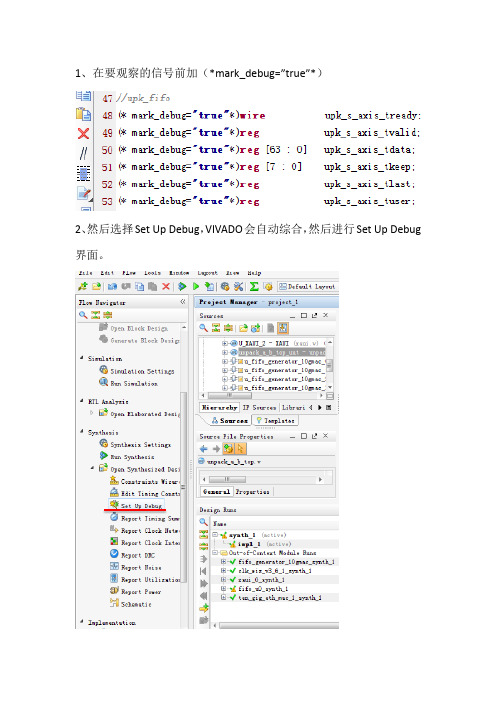

2、然后选择Set Up Debug,VIVADO会自动综合,然后进行Set Up Debug 界面。

3、单击next

4、里边是加了(*mark_debug=”true”*)的所有信号,可以再添加或减少信号

5、最好统一所有时钟域,多个时钟域,有时会在上板测试时报错。

6、单击next,选择采样深度。

7、最后单击finish,完成。

过一会儿,会自动进入如下界面,此时所有观察的信号就都添加完了。

8、如果有些信号没有添加(*mark_debug=”true”*),但想要观察它。

如图所示,已添加的数据信号旁有个小爬虫。

没有添加信号的可以选择Mark_Debug。

9、然后,选择的信号会出现在下边的窗口中。

在Unassigned Debug Net 分组下。

10、然后,鼠标右键,选择Set Up Debug,即可。

此时,会重新进入Set Up Debug界面让你选择。

11、信号添加完后,单击关闭。

12、OK

13、Yes

14、至此,所有要观察的信号都会添加到xdc文件中。

如果下次观察的debug信号有变,请先清理xdc中原有的debug信号,VIVADO不会自动清除。

否则会产生冲突。

15、最后产生bit文件和debug_nets.ltx文件,下载到板子上,会弹出类似仿真的界面。

由于没有板子,所以无法截图。

VIVO下ILA使用指南

V I V O下I L A使用指南 Company Document number:WTUT-WT88Y-W8BBGB-BWYTT-19998VIVADO下ILA使用指南ILA是VIVADO下的一个DEBUG- IP,类似于片上逻辑分析仪,通过在RTL设计中嵌入ILA核,可以抓取信号的实时波形,帮助我们定位问题。

本文档以一个简单的COUNTER设计为例,对VIVADO()下ILA核的使用进行说明。

第一部分 RTL设计module counter(input clk,output [3:0] q);wire clk;lk (clk),.probe0 (cnt));endmoduleps:ILA的clk需要连接到需要观察信号的相应时钟域,在一个RTL中可以嵌入多个ILA,方便观察不同时钟域的信号第四部分使用vivado在线抓取信号波形1)修改完RTL后,点击Generate Bitstream生成bit文件2)开发板上电,接上JTAG下载器,然后打开open Target打开Open New Target..点击Next点击Next点击Next点击Finish点击ok,该错误是软件误报发现vivado界面的左下角的Program Device选项变亮,点击该选项,下载bit文件点击Pro...开始下载下载完成,vivado界面发生变化打开window菜单栏,选择Debug Probes选项,界面会多出一个Debug Probes窗口将需要观察的信号cnt 信号“拖入”右侧的Basic Trigger Setup窗口在这个界面中可以修改触发条件(cnt=2),触发深度(1024),触发位置(500)等参数(类似于chipscope)点击左侧的触发开关,vivado会自动打开一个wave窗口通过放大波形,可以观察波形细节。

VIVADO中debug用法

VIVADO中debug用法VIVADO和ISE相比ChipScope已经大幅改变,很多人都不习惯。

在ISE中称为ChipScope而VIVADO中就称为in system debug。

下面就介绍VIVADO中如何使用debug工具。

Debug分为3个阶段1.探测信号:在设计中标志想要查看的信号2.布局布线:给包含了debug IP的设计布局布线3.分析:上板看信号一探测信号探测信号有2种方法一种是直接在HDL源代码中用(*mark_debug = “true”*)标识出要探测的信号另一种是在综合过后的网表文件中添加标志。

1 .在HDL源代码中添加标志然后点击 open Synthesized Design然后点击Tools-> Set Up Debug点击 Next点击 Add/Remove Nets点击find会出来所有信号。

如果需要添加debug的信号,从左边框中选择所需信号,点击按钮加到右边来。

如果需要去除不需要的debug信号,从右边框中选择所需信号,点击按钮就去除了。

选好信号之后,在右下角点击Ok按钮。

在此框中为所有debug信号选择时钟域,选择debug信号,右键选择Select Clock Domain。

注意每一个时钟域对应一个单独的ILA 2.0core。

在此框中选择所需时钟,点击ok点击next然后继续下面的Implement 流程点击Save保存修改后的工程后面像以前一样等工程跑结束。

2.在网表文件中添加标志网表文件添加标志,第一步也是打开综合后设计。

如下图所示第二步是打开debug窗口Open synthesized Design之后,有2种方法来标志debug信号(1)第一种方法是在Netlist窗口中选择信号,右键点击Mark Debug(2)第二种方法是在Tools中选择Setup Debug 推荐使用此方法然后和前面一样继续跑工程。

二上板调试上板的时候选择Open hardware session ,然后Open a new hardware target选择next选择next选择Next选择FPGA来配置文件注意移到另一台电脑看debug信号时,必须将debug_nets.ltx 文件和bit文件一起移过去。

Vivado进行Debug测试

1.通过在代码中加入相应的标记代码可将相应的变量添加到Debug中,如下代码(*mark_debug = "true"*)reg [9 : 0] writeCounter;(*mark_debug = "true"*)reg [7 : 0] testInputData;该代码定义了两个寄存器变量,通过在代码中加入 (*mark_debug = "true"*)可将变量加入Debug进行观察。

2.在添加完变量之后进行综合,综合完之后在左侧的Synthesis中选择SynthesizedDesign,然后选择其中的Set Up Debug,如图1所示图1 打开Set Up Debug向导3.在出现的Set Up Debug的向导中会出现所标记的待调试变量。

图2位点击Set UpDebug之后出现窗口,此为向导的第一个窗口,直接点击Next即可图2 Set Up Debug向导第一个窗口4.图3为Set Up Debug向导的第二个窗口,点击Next即可图3 Set Up Debug向导第二个窗口5.然后就会出现之前标记的信号,此时变量前面会出现绿色的小虫子,中间的ClockDomain表示的是进行调试的时候信号采集的采样时钟,这里是一个锁相环的第一个时钟输出作为采样时钟图4 Set Up Debug向导第三个窗口6.点击Next之后会出现对采样深度和触发以及存储方式的设置,根据需要进行相应设置,此处采样深度为4096,表示前面的两个变量在Debug调试的时候进行采样会采集4096个样本图5 Set Up Debug向导第三个窗口7.将窗体布局切换到Debug模式下(图6)之后可在中间靠左边看到一个Netlist的小窗体(图7),从中可以找到被标记的带有绿色小虫的变量图6 切换窗体布局图7 Netlist窗口8.最后生成bit文件之后进行下载,下载的时候可以发现下载对话框中自动输入了两个文件的完整路径,在不进行Debug的时候只有一个下载文件,下载之后就会切换到调试窗口。

vivado 使用手册

vivado 使用手册Vivado 是一款由 Xilinx 公司开发的集成电路设计工具,广泛应用于 FPGA(现场可编程门阵列)的开发和设计过程中。

该使用手册将帮助您了解 Vivado 工具的基本功能和使用方法,使您能够更加高效地进行电路设计和验证。

首先,了解 Vivado 的基本概念是非常重要的。

Vivado 工具主要由两个部分组成:Vivado 设计套件和 Vivado 高级综合(HLS)。

Vivado 设计套件是一个全面的集成电路设计解决方案,包括设计、调试和验证等多个环节。

而 Vivado HLS 则是一种高级综合工具,可将 C/C++ 代码转换为可在 FPGA 上实现的硬件描述语言。

在开始使用 Vivado 进行设计时,您需要创建一个项目。

项目由设计文件、约束文件和其他相关文件组成。

设计文件可以使用 Verilog、VHDL 或其他硬件描述语言编写,约束文件用于指定电路的时序约束和板级约束等信息。

通过 Vivado 的GUI(图形用户界面)或 TCL(工具命令语言)进行项目管理和配置。

Vivado 提供了丰富的功能和工具,可帮助您进行电路设计、仿真和验证。

您可以使用自动布局布线(Auto Place and Route)工具自动生成电路的物理布局和连线。

借助 Vivado 的时序分析工具,您可以分析电路的时序约束和时钟域,以确保电路的性能和稳定性。

此外,还可以使用仿真工具验证电路的功能和正确性,并进行系统级调试和验证。

Vivado 还支持 IP(知识产权)核的使用。

IP 核是预先设计好的可重用电路模块,可以直接用于您的设计中,加快设计时间和减少工作量。

Vivado 拥有丰富的IP 核库,包含各种不同的功能模块,如存储器、接口、调制解调器等。

您可以使用 Vivado 的 IP 目录来浏览和添加 IP 核,也可以自定义开发您自己的 IP 核。

最后,在完成设计后,您可以使用 Vivado 工具将设计文件进行编译,并将生成的 Bitstream 文件下载到 FPGA 板卡上进行硬件实现和验证。

Vivado使用教程

Vivado将约束分为时序约束和物理约束。

物理约束主要是指管脚的使用。包括管脚的映射关系和电

平标准,以及诸如上拉、下拉等的属性参数。

可以使用自动分配管脚工具,在“Tools→I/O Planning”里面可以找到。

41

Vivado约束设计基本流程

对照板卡的具体情况,手动分配管脚。选择 “Layout-> I/O Planning”。

7

Vivado软件概述

以SPI模块为例,比较一下两个软件的综合布线后 的资源使用情况。

该SPI模块用于1431、1451项目中,同时输出两路SPI信号。工程选择的

比较芯片为xc7vx485tffg1157-1,时钟设为50MHz。 Vivado2014.2的利用率报告:

ISE14.7的利用率报告: 两者比较:

4

Vivado软件概述

Vivado与ISE相比,发生的改进:

1.数据格式更统一; 2.contraint文件采用了SDC格式,兼容业界标准; 3.Vivado的ECO和TCL脚本功能更强大; 4.推出了针对C开发的High Level Synthesis和针

对DSP的System Generator;

3

Vivado软件概述

Vivado的发展:

Vivado从2008年5月开始研发; 2011年4月开始进行超过100个试用用户的β测试; 目前版本号为2014.2。

Vivado将关注点集中在C2H、高层次综合等技术方 面,仿真内核的性能得到优化,宣称其仿真速度是 ISE的3倍。如果使用硬件联合仿真,可以将速度提 高100倍。官方宣称Vivado比竞争对手速度快4倍, 而消耗的资源是对手的50%。

xilinx vivado zynq pldma PL部分ILA调试

xilinx vivado zynq pldma PL部分ILA调试

通过前面的PL DMA设计,在SDK中运行,很正常的没有运行起来(block design与source desing都是自己手敲,明显的错误已经改正,能够生成bit文件启动SDK调试)。

首先在PL部分调试,作为PL DMA的控制APB总线,将其设置为Mark Debug,如下图所示。

然后重新综合,综合完成,不进行implemenTIon,在综合菜单下面找到Set Up Debug,进行ILA配置,出现下图的设置窗口。

在上图中点击more info,出现提示,部分网表没有设定时钟。

全部选择,然后右键选择时钟,如下图所示

选择FCLK_CLK1时钟,因为此时钟为150Mhz,而APB总线时钟为FCLK_CLK0为50Mhz,用150Mhz时钟采样便于观测,然后一路默认完成。

然后再生成bit文件。

VIVADO下ILA使用指南

VIVADO下ILA使用指南ILA是VIVADO 下的一个DEBUG- IP,类似于片上逻辑分析仪,通过在RTL设计中嵌入ILA核,可以抓取信号的实时波形,帮助我们定位问题。

本文档以一个简单的COUNTER设计为例,对VIVADO (2014.1 )下ILA核的使用进行说明。

第一部分RTL设计module cou nter(in put clk, output [3:0] q );wire clk;//想抓取cnt信号进行观察(* keep = "TRUE" *)reg [3:0] cnt = 4'd0;assig n q = cnt;always@(posedge clk) begincnt <= cnt + 4'd1; enden dmodule第二部分加入LIA核在vivado 工程中,打开IP Catalog 选项,找到ILA核N ame十A Lit runoti 舟Induslfi al3 产AKI Infrastruc+i-Lre由i- BaselF- r Fl尸m尸戸十qP L Cowiiiunication & Netwciking申「Debug & VeElXlcaTlcnW tL? Dubuj?ft IBERT 7 Series GTHp JTAG to AXI Wasterfl1VTO ^Virtual Tnpxit/Giitriit P Digital Signal Froccssing 由Embedded ProcesEing 也l^PGA tiir^s arid Design 申屋Hath Functions 丙” Memories & Storage Elenems 申i. St andard Bus Znteriac^s P Video 发Imas^ Processing进入ILA 核的配置界面(2页) 第一页Mjl £3c E-Ldaa a-T : 1: * *t £c-n b r I !P L.oc:> -t 4. on !uw£-t cJ-i, ~fca*ul -t ■C - rigpori ■.n^t 科 *n.™ Ill ■_ 1| ~T G 亡<>打昨■yhsr 甘 cfajji 忌』prE>e par<£ UB * *Vf"Bja<o Ht 】 匸心“《1<«Gcnn«--r «.l OpT l->niD …3 |H-nnl 1 cr T WTF<•»11V* r 1 AV TDTLMbe<r " FtrC&essfl "i H. - 10^4]SaiFipl# Data D wttijlpm,. *r Tirl M.eir CXat Fc^it I — T K ~1 :BJtcxr J ra P 口丁七 I np-u t R£qp ■■ is -ax| O ~J s-£ CiE*1®-Arisi £ t ora ■ « S*# * 4. ng EIT" c ap t LET >?r^i.I JL d.vna.n.-c. i=-J T~u 1F? r? J .I jrim r ol 「GnT ?* C >T 「tzr 7 ]?■厂*■•T"I™』ITi_-iTi 15*17 o C C"c-ii p-air a t ->T -s ] E ■«■UM£~|可以修改例化名,在“ Number of Prober"可以修改想抓取信号的分第二页1 I_J L ClrLtiecx- nt.ed ]_«>-£l>c JLnc. l^tzer >(4. O>D 叮匸LA 电Ji ;* nT L OJI h 」IF 1 Lccct L«n i iwi t chDef aul t B在“ Probe Width "选择各分组信号的位宽,我们需要观察的 点击0K ,到此为止,ILA 的配置完成第三部分 在RTL 中嵌入ILA 核 在vivado 工程的sources 窗口找到刚生成的ILA 核的例化代码I L A (Ini nt IL DIB IL O 1 A n« 1 IF z ex J 4.4L 0>组个数,在本例中仅观察 1 组信号 ent ,在“ sample Data Depth可以修改抓取信号的深度,本例选择默认值 1024。

vivado中debug用法

vivado中debug用法一、概述V i va do是一种流行的可编程逻辑设备(P L D)和复杂可编程逻辑设备(C PL D)设计工具,广泛应用于数字电路设计和硬件描述语言(HD L)建模。

在V iv ad o中,d e bu g是其中一个重要的功能,它可以帮助工程师在设计过程中定位和修复问题,提高设计效率和可靠性。

二、d e b u g的基本原理在V iv ad o中,d eb ug的基本原理是通过观察和分析信号波形来定位和分析问题。

当设计运行时,Vi va do可以捕获和显示信号的波形,以帮助工程师了解信号的变化和高低电平情况。

通过分析这些波形,工程师可以定位和排除设计中的问题,提高设计的可靠性。

三、d e b u g的使用方法3.1创建d e b u g模式在V iv ad o中,创建d e bu g模式的方法非常简单。

首先,打开V i va do工程,在“工程导航”窗格中选择需要调试的设计文件,右键单击并选择“创建d ebu g模式”。

接下来,根据提示完成创建d eb ug模式的步骤。

在创建过程中,可以选择需要观察和分析的信号,也可以设置触发条件和触发事件。

3.2启动d e b u g模式创建完成de bu g模式后,可以通过点击V iv ad o界面上的“启动d e bu g”按钮来启动d e bu g模式。

在d ebu g模式下,Vi va do会捕获和显示选择的信号波形,并提供波形分析和触发功能。

3.3波形分析在d eb ug模式下,可以通过波形窗口对信号波形进行分析。

V i va do提供了丰富的波形显示和分析功能,包括放大、缩小、平移、测量等。

通过这些功能,工程师可以更清晰地观察信号的变化情况,并确定问题所在。

3.4触发功能在d eb ug模式下,可以设置触发条件和触发事件来捕获感兴趣的信号波形。

例如,可以设置当某个寄存器的值达到某个特定的阈值时,触发波形捕获并显示。

这对于定位问题非常有帮助,可以快速找到问题所在。

【Vivado那些事儿】ILA使用总结

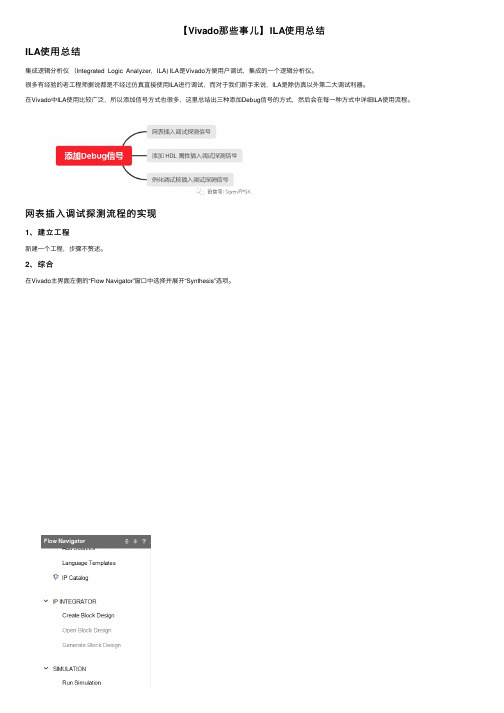

【Vivado那些事⼉】ILA使⽤总结ILA使⽤总结集成逻辑分析仪(Integrated Logic Analyzer,ILA) ILA是Vivado⽅便⽤户调试,集成的⼀个逻辑分析仪。

很多有经验的⽼⼯程师据说都是不经过仿真直接使⽤ILA进⾏调试,⽽对于我们新⼿来说,ILA是除仿真以外第⼆⼤调试利器。

在Vivado中ILA使⽤⽐较⼴泛,所以添加信号⽅式也很多,这⾥总结出三种添加Debug信号的⽅式,然后会在每⼀种⽅式中详细ILA使⽤流程。

⽹表插⼊调试探测流程的实现1、建⽴⼯程新建⼀个⼯程,步骤不赘述。

2、综合在Vivado主界⾯左侧的“Flow Navigator”窗⼝中选择并展开“Synthesis”选项。

点击“Run Synthesis”,进⾏综合。

3、等待综合完成后,弹出“Synthesis Completed”对话框。

在该对话框中,选择“Open Synthesized Design”选项。

4、查看“Netlist”.上图在点击【OK】后可能会出现“Critical Messages”对话框,单击【OK】即可,在下图中点击【Netlist】即可查看当前设计中的所有⽹络节点。

5、从上图中所有的⽹络节点选择需要进⾏调试/监测的端⼝,并进⾏标记针对本设计,我们选择【din(8)】作为监测端⼝,在“Netlist”⾥找到这个端⼝,右击出菜单,选择【Make Debug】,如下:6、根据需要选择其他端⼝按照上⼀步操作,选择其他端⼝,本⼯程还需要监测【dout(8)】、【rd_en】等。

上诉步骤完毕后,【Ctrl+S】保存修改的⽹表。

7、打开“Set up Debug”对话框在Vivado主界⾯的主菜单下,执⾏菜单命令【Tools】-->【Setup Debug...】,弹出“Set up Debug”对话框。

8、设置参数点击【Next】【Next】后弹出以下对话框:可以看到“Inst_fifo 1/din(8)”所对应的“Clock Domain”列显⽰红⾊的“partially defined”。

VIVADO下ILA使用指南

VIVADO下ILA使用指南ILA是VIVADO下的一个DEBUG- IP,类似于片上逻辑分析仪,通过在RTL设计中嵌入ILA 核,可以抓取信号的实时波形,帮助我们定位问题。

本文档以一个简单的COUNTER设计为例,对VIVADO()下ILA核的使用进行说明。

第一部分 RTL设计module counter(input clk,output [3:0] q);wire clk;lk (clk),.probe0 (cnt));endmoduleps:ILA的clk需要连接到需要观察信号的相应时钟域,在一个RTL中可以嵌入多个ILA,方便观察不同时钟域的信号第四部分使用vivado在线抓取信号波形1)修改完RTL后,点击Generate Bitstream生成bit文件2)开发板上电,接上JTAG下载器,然后打开open Target打开Open New Target..点击Next点击Next 点击Next点击Finish点击ok,该错误是软件误报发现vivado界面的左下角的Program Device选项变亮,点击该选项,下载bit文件点击Pro...开始下载下载完成,vivado界面发生变化打开window菜单栏,选择Debug Probes选项,界面会多出一个Debug Probes窗口将需要观察的信号cnt 信号“拖入”右侧的Basic Trigger Setup窗口在这个界面中可以修改触发条件(cnt=2),触发深度(1024),触发位置(500)等参数(类似于chipscope)点击左侧的触发开关,vivado会自动打开一个wave窗口通过放大波形,可以观察波形细节v1.0 可编辑可修改11。

VIVADO下ILA使用指南

VIVADO下ILA使用指南ILA是VIVADO下的一个DEBUG- IP,类似于片上逻辑分析仪,通过在RTL设计中嵌入ILA 核,可以抓取信号的实时波形,帮助我们定位问题。

本文档以一个简单的COUNTER设计为例,对VIVADO(2014.1)下ILA核的使用进行说明。

第一部分 RTL设计module counter(input clk,output [3:0] q);wire clk;//想抓取cnt信号进行观察(* keep = "TRUE" *)reg [3:0] cnt = 4'd0;assign q = cnt;always@(posedge clk)begincnt <= cnt + 4'd1;endendmodule第二部分加入LIA核在vivado工程中,打开IP Catalog选项,找到ILA核进入ILA核的配置界面(2页)第一页在“component Name”可以修改例化名, 在“Number of Prober”可以修改想抓取信号的分组个数,在本例中仅观察1组信号cnt,在“sample Data Depth”可以修改抓取信号的深度,本例选择默认值1024。

其他选项保持默认值。

第二页在“Probe Width”选择各分组信号的位宽,我们需要观察的cnt信号为4bit,这里选择4。

点击OK,到此为止,ILA的配置完成第三部分在RTL中嵌入ILA核在vivado工程的sources窗口找到刚生成的ILA核的例化代码将其复制到RTL设计中,并连接好信号module counter(input clk,output [3:0] q);wire clk;//想抓取cnt信号进行观察(* keep = "TRUE" *)reg [3:0] cnt = 4'd0;assign q = cnt;always@(posedge clk)begincnt <= cnt + 4'd1;endila_0 u_ila(.clk (clk),.probe0 (cnt));endmoduleps:ILA的clk需要连接到需要观察信号的相应时钟域,在一个RTL中可以嵌入多个ILA,方便观察不同时钟域的信号第四部分使用vivado在线抓取信号波形1)修改完RTL后,点击Generate Bitstream生成bit文件2)开发板上电,接上JTAG下载器,然后打开open Target打开Open New Target..点击Next点击Next点击Next点击Finish点击ok,该错误是软件误报发现vivado界面的左下角的Program Device选项变亮,点击该选项,下载bit文件点击Pro...开始下载下载完成,vivado界面发生变化打开window菜单栏,选择Debug Probes选项,界面会多出一个Debug Probes窗口将需要观察的信号cnt 信号“拖入”右侧的Basic Trigger Setup窗口在这个界面中可以修改触发条件(cnt=2),触发深度(1024),触发位置(500)等参数(类似于chipscope)点击左侧的触发开关,vivado会自动打开一个wave窗口通过放大波形,可以观察波形细节。

DEBUG使用方法

DEBUG使用方法为了解决问题和改进程序,我们经常需要在代码中进行调试。

调试是指通过检查代码的执行过程,找出可能的错误和问题,并修复它们。

在本文中,我们将介绍一些常见的调试技术和工具,帮助您进行有效的调试。

1.打印输出:打印输出是调试的最基本方法之一、通过在代码中插入打印语句,我们可以跟踪代码的执行流程和变量的值。

例如,在关键位置添加`print`语句来输出变量的值,以便了解其当前状态。

这种方法对于追踪代码执行路径和确定错误发生的地点非常有用。

但是,它不适用于大型程序或复杂的问题,因为太多的输出可能会让您迷失在信息中。

2.断点调试:断点调试是一种先进的调试技术,可以暂停程序的执行,以便我们可以检查和修改程序的状态。

通过在代码中设置断点,我们可以在程序执行到该点时暂停执行,并查看变量的值、执行的路径等信息。

在现代集成开发环境(IDE)中,我们可以通过单击代码行号或调试菜单来设置断点。

一旦程序执行到断点位置,调试器将暂停执行,我们可以检查变量的值并逐行执行代码,以便找出问题。

3.单步调试:与断点调试相似,单步调试也允许我们逐行执行代码并检查变量的值。

单步调试是一种逐行执行代码的方法,让我们可以了解代码执行的顺序和路径。

在单步调试中,我们可以逐行执行代码,并在每一步之后检查变量的值和程序状态。

这对于发现代码执行的异常路径、循环错误和边界条件非常有用。

4.调试器:调试器是一种针对软件调试的工具,它可以帮助我们通过提供图形界面和功能来检查程序的状态、执行流程和变量的值。

调试器通常集成在IDE中,提供了单步执行、设置断点、查看变量和堆栈跟踪等功能。

使用调试器,我们可以直观地了解程序的状态,并快速找到问题所在。

5.注释和重构:注释是一种记录代码用途和解释的方法,可以帮助我们理解程序的目的和逻辑。

通过添加注释,我们可以提高代码的可读性,并减少问题的发生。

在调试过程中,我们可以使用注释来解释代码块的用途、关键数据结构和预期输出,以便更好地理解问题。

[转]vivado硬件调试——mark_debug

![[转]vivado硬件调试——mark_debug](https://img.taocdn.com/s3/m/0597490ba9114431b90d6c85ec3a87c240288afc.png)

[转]vivado硬件调试——mark_debug最近两个⽉开始⽤Vivado做项⽬,之前⼀直⽤ISE开发,个⼈觉得ISE⽅便好⽤,⽽Vivado编译⼜慢,还占内存,打开⼀个⼯程就需要好半天,可视化界⾯感觉也没什么⽤处,不如模块化的代码来的简单,⽽且还有⼀些bug。

⽆奈xilinx公司不再开发ISE,到14.7就结束了,以后的芯⽚只能⽤Vivado做设计了,只能⽤它了,现在已经更新到了2014.4版本,我现在⽤的是2013.4版本,开发板是zedboard。

⽤Vivado进⾏硬件调试,就是要插⼊ila核,即“集成逻辑分析仪”,然后将想要引出来观察的信号连到这个核的probe上。

⾸先第⼀步,需要把想要观测的信号标记出来,即mark_debug,有两种mark_debug的⽅法,我⽤verilog写了⼀个简单的流⽔灯程序,只有⼏⾏代码,如下:1. module main(2. input clk,3. input rst,4. output reg [7:0] led5. );6.7. (*mark_debug = "true"*)reg [23:0] counter;8. always @(posedge clk) begin9. if(rst) begin10. counter <= 0;11. led <= 8'b00000001;12. end13. else counter <= counter + 1;14. if (counter == 24'hffffff)15. led <= {led[6:0],led[7]};16. end17.18. endmodule例如,要观察counter信号的波形,那么在第7⾏定义reg型信号counter时,前⾯加上(*mark_debug=“true”*),这样就把counter信号标记了出来。

VIVDAO_DEBUG信号

1、在要观察的信号前加(*mark_debug=”true”*)

2、然后选择Set Up Debug,VIVADO会自动综合,然后进行Set Up Debug 界面。

3、单击next

4、里边是加了(*mark_debug=”true”*)的所有信号,可以再添加或减少信号

5、最好统一所有时钟域,多个时钟域,有时会在上板测试时报错。

6、单击next,选择采样深度。

7、最后单击finish,完成。

过一会儿,会自动进入如下界面,此时所有观察的信号就都添加完了。

8、如果有些信号没有添加(*mark_debug=”true”*),但想要观察它。

如图所示,已添加的数据信号旁有个小爬虫。

没有添加信号的可以选择Mark_Debug。

9、然后,选择的信号会出现在下边的窗口中。

在Unassigned Debug Net 分组下。

10、然后,鼠标右键,选择Set Up Debug,即可。

此时,会重新进入Set Up Debug界面让你选择。

11、信号添加完后,单击关闭。

12、OK

13、Yes

14、至此,所有要观察的信号都会添加到xdc文件中。

如果下次观察的debug信号有变,请先清理xdc中原有的debug信号,VIVADO不会自动清除。

否则会产生冲突。

15、最后产生bit文件和debug_nets.ltx文件,下载到板子上,会弹出类似仿真的界面。

由于没有板子,所以无法截图。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Vivado中debug用法

由技术编辑archive1于星期四, 07/16/2015 - 16:03 发表

Vivado和ISE相比ChipScope已经大幅改变,很多人都不习惯。

在ISE中称为ChipScope而Vivado中就称为in system debug。

下面就介绍Vivado中如何使用debug工具。

Debug分为3个阶段:

1. 探测信号:在设计中标志想要查看的信号

2. 布局布线:给包含了debug IP的设计布局布线

3. 分析:上板看信号

一探测信号

探测信号有2种方法一种是直接在HDL源代码中用(*mark_debug = “true”*)标识出要探测的信号另一种是在综合过后的网表文件中添加标志。

1 .在HDL源代码中添加标志

然后点击open Synthesized Design

然后点击Tools-> Set Up Debug

点击Next

点击Add/Remove Nets

点击find会出来所有信号。

如果需要添加debug的信号,从左边框中选择所需信号,点击按钮加到右边来。

如果需要去除不需要的debug信号,从右边框中选择所需信号,点击按钮就去除了。

选好信号之后,在右下角点击Ok按钮。

在此框中为所有debug信号选择时钟域,选择debug信号,右键选择Select Clock Domain。

注意每一个时钟域对应一个单独的ILA 2.0core。

在此框中选择所需时钟,点击ok

点击next

然后继续下面的Implement 流程

点击Save保存修改后的工程

后面像以前一样等工程跑结束。

2.在网表文件中添加标志

网表文件添加标志,第一步也是打开综合后设计。

如下图所示

第二步是打开debug窗口

Open synthesized Design之后,有2种方法来标志debug信号(1) 第一种方法是在Netlist窗口中选择信号,右键点击Mark Debug

(2) 第二种方法是在Tools中选择Setup Debug 推荐使用此方法

然后和前面一样继续跑工程。

二上板调试

上板的时候选择Open hardware session ,然后Open a new hardware target

选择next

选择next

选择Next

选择FPGA来配置文件

注意移到另一台电脑看debug信号时,必须将debug_nets.ltx 文件和bit文件一起移过去。

如下图红框所示

如果需要设置触发条件,选择Windows –> Debug Probes

在Debug Probe窗口中选择需要设置的信号,然后设置触发条件。

在Trigger Pos中可以设置抓取到触发信号跳变前N个时钟周期可以被抓到。