第六章DSP外围设备接口介绍数字信号处理系统设计与实践理论

高速数字信号处理器外部电路设计

高速数字信号处理器外部电路设计在现代技术大量应用数字信号处理器(DSP)的时代,高速数字信号处理器外部电路设计成为了一个非常重要的课题。

如何设计一个高效、稳定、准确的数字信号处理系统,是影响数字信号处理器性能的关键因素之一。

因此本文将探讨高速数字信号处理器外部电路设计的技巧和注意事项。

一、高速数字信号处理器概述高速数字信号处理器是一种专门用于数字信号处理任务的微处理器,通过高效的数字信号处理算法对数据进行处理,可以极大地提高处理速度和精度。

常见的高速数字信号处理器有TI的TMS320系列、ADI的ADSP系列、ARM的CORETEX-M系列等。

二、高速数字信号处理器外部电路设计的要素1.时钟设计在高速数字信号处理器的使用中,时钟电路的设计非常重要。

时钟信号的稳定性、精度和频率对于数字信号处理器的运行速度和稳定性都有着直接的影响。

因此,时钟电路的设计应该尽可能的简单、稳定、可靠。

2.电源设计数字信号处理器的电源设计也非常关键。

由于高速设备对电源质量的要求比较高,因此电源的设计应该尽可能的保证稳定性和精度,减小电源波动和噪声对系统的影响。

3.信号输入输出接口数字信号处理器的输入输出接口是数据传输的核心,信号输入输出的速度和精度对于系统的性能影响非常大。

因此,设计过程中应该尽可能的减小信号传输中的失真和噪声,保证数据的准确和可靠。

4.可编程逻辑接口可编程逻辑电路是数字信号处理器的重要组成部分,它能够实现复杂的数字处理算法和运算功能,提高DSP的运算速度和效率。

因此,可编程逻辑电路的设计也是非常重要的。

三、高速数字信号处理器外部电路设计的技巧和注意事项1.时钟电路尽量使用独立时钟源在高速数字信号处理器的设计中,可靠的时钟源能够保证系统的稳定性和精度。

因此,时钟电路应该尽可能的使用独立时钟源,避免将时钟信号引入其他模块。

2.电源电路的设计建议采用隔离式电源隔离式电源是数字信号处理器的稳定性和精度保证的关键。

数字信号处理器(DSP)原理及应用

2020年4月12日

DSP原理及应用

12

第7章 数字信号处理器(DSP)原理及应用

⑤ 利用特殊用途的DSP 芯片实现

最高可达50MIPS ,内置A/D 及PWM型D/A转换器 ,内置MAC指令

2020年4月12日

DSP原理及应用

13

第7章 数字信号处理器(DSP)原理及应用

2020年4月12日

DSP原理及应用

16

第7章 数字信号处理器(DSP)原理及应用

1.2.1 DSP芯片的发展概况

第二阶段,DSP的成熟阶段(1990年前后)。

这个时期的DSP器件在硬件结构上更适合数字信号处理的 要求,能进行硬件乘法、硬件FFT变换和单指令滤波处理,其 单指令周期为80~100ns。

数字信号处理的实现是用硬件、软件或软硬结

合的方法来实现各种算法。数字信号处理的实现一般

有以下几种方法:

①③⑤⑥ 在用通单专基用片用于计机的通算实用DS机现DPS芯(,P片核用PC实的于机现A不)S,太I上C可复芯用用杂片软在的实件要数现(求字。如信信随F号o号着rt处处r专a理理n用、速。集C度不成语极适电

① 在通用的计算机上用软件实现

x(n) u(n) u(n 10)

x(n)

1.5 1 0.5

h(n) (0.9)n u(n)

0

h(n0)

1.5

1

0.5

10

20

30

40

n

50

0

0

10

20

30

40

50 n

y(n) x(n) h(n)

y(n)

8

9

7

DSP(数字信号处理器)原理及应用绪论

4.生活

…

2

主要内容

第01章 绪论 第02章 CCS软件应用基础 第03章 C/C++程序编写基础 第04章 TMS320X28xx系列DSP综述 第05章 双供电DSP电源设计 第06章 TMS320F2812的时钟及看门狗 第07章 可编程数字量通用I/0 第08章 中断系统及其应用 第09章 事件管理器及其应用 第10章 SPI接口及其应用 第11章 eCAN总线及其应用 第12章 SCI接口应用 第13章 A/D转换单元 第14章 存储器应用及Boot引导模式 第15章 交、直流电机的DSP控制 第16章 电力电子系统的DSP控制 第17章 DSP与Matlab联合应用 第18章 DSP2812指令系统

架构方式: 单片机+逻辑电路 单片机+CPLD DSP+CPLD 单片机+DSP+CPLD FPGA+DSP ASIC SOIC

15

基础知识:µ C--总线结构 P/µ

2种基本的总线结构: Von Neumann- 冯.诺依曼 Harvard – 哈弗 Von Neumann: 数据、代码共享内存空间 数据、代码共享内存总线 Example: Intel‘s x86 Pentium Processor family Harvard: 数据、代码独立存储空间 数据、代码独立存储总线 Example: TMS320F系列DSP

22

流水线

流水线深度从2~6级不等

多个指令重叠进行,理想情况下,K 段流水能

在 K+N-1个周期内,处理 N 条指令

23

多级流水线

24

专用的硬件乘法器

在通用的微处理器中,乘法指令是由一

dsp基本系统设计

04

同时,随着人工智能、物联网等技术的快速发展, DSP技术将与这些技术进行更紧密的结合,以实现更 高效、智能的数据处理和分析。

THANKS FOR WATCHING

感谢您的观看

算法实现与优化

总结词

DSP系统的核心是实现各种数字信号处理算法,因此算法实现与优化是DSP系统软件设计的关键环节 。

详细描述

在算法实现与优化方面,需要考虑算法的复杂度、运算量、存储需求等因素,并采用适当的优化技术 ,如循环展开、流水线设计、并行计算等,以提高DSP系统的性能。

程序结构与流程控制

总结词

存储器与I/O接口设计

存储器设计

根据DSP系统的需求,设 计适当的存储器容量和类 型,如SRAM、DRAM、 Flash等。

I/O接口设计

根据应用需求,设计适当 的I/O接口,如GPIO、SPI、 I2C、UART等。

考虑因素

在存储器和I/O接口设计时, 需要考虑容量、速度、功 耗以及与处理器的兼容性 等因素。

信号的频域分析

频域分析是将信号从 时域转换到频域进行 分析的方法。

频谱分析可以揭示信 号的频率成分、频率 范围和频率变化等特 性。

傅里叶变换是频域分 析的基础,可以将信 号表示为不同频率分 量的叠加。

04 DSP系统硬件设计

硬件平台选择

通用硬件平台

选择通用的DSP硬件平台,如TI 的TMS320系列或ADI的Blackfin 系列,这些平台具有成熟的开发 工具和丰富的应用案例。

05 DSP系统软件设计

软件开发环境选择

总结词

选择合适的软件开发环境是DSP系统设计的重要步骤,它影响着软件开发的效 率、可维护性和可扩展性。

dsp数字信号处理课程设计报告(精)

淮阴工学院《DSP技术与应用》课程设计报告选题名称:基于TMS320C54DSP的数字电话系统设计系(院):计算机工程学院专业:计算机工程系(嵌入式系统软件设计方向)班级:计算机1073姓名:王翔学号: 1071306121指导教师:马岱,常波学年学期: 2009 ~ 2010 学年第 2 学期2010 年 6 月 12 日设计任务书课题名称基于TMS320C54xDSP的数字电话系统设计设计 1. 理解DSP TMS320C54x和目的TLV1571的工作原理;2. 理解DSP应用系统开发的基本思路及方法;3. 练习使用汇编语言中循环、分支等知识编写应用程序的基本步骤;4. 学习软件开发过程及资料收集与整理,学会撰写课程设计报告;5. 学会对所学知识进行总结与提高;实验环境1.Windows 2000以上操作系统;2.CSS集成开发环境;任务要求1. 利用课余时间去图书馆或上网查阅课题相关资料,深入理解课题含义及设计要求,注意材料收集与整理;2. 在第14周末之前完成预设计,并请指导教师审查。

通过后方可进行下一步工作;3. 按指导书要求设计软件,实现设计的功能,并显示正确的结果;4. 要求形成稳定的程序软件,可以运行,方可申请参加答辩;工作进度计划序号起止日期工作内容12010.6.6~2010.6.7在预设计的基础上,进一步查阅资料,完成硬件电路设计。

22010.6.8~2010.6.8编写软件代码,调试与完善。

32010.6.8~2010.6.9测试程序,优化代码,增强功能,撰写课程设计报告。

42010.6.10~2010.6.10提交软件代码、硬件电路成果和设计报告,参加答辩。

指导教师(签章):年月日摘要:电话已成为现代生活不可缺少的交流工具之一,它方便了人们的交流使交流不再受物理距离的限制!基本上每个人都要用到电话,我们的身边的电话基本都是模拟电话。

虽然它基本可以买足我们的日常生活,语音效果也很好!但在有雷电等恶劣自然条件的情况下它的通话效果就很不近人意了。

dsp课件

在代码实现完成后,进行代码调试,确保程序的正确性和稳定性。

调试与测试结果分析总结

调试过程

在代码调试完成后,进行系统调试,确保各个模块之间的协调和正 常运行。

测试结果分析

对测试结果进行分析,包括性能测试、功能测试等,找出可能存在 的问题和不足。

总结

根据调试和测试结果,对项目进行总结,包括经验教训、改进方向等 ,为后续的项目提供参考和借鉴。

DSP课件

目录

• DSP概述 • DSP硬件结构与工作原理 • DSP软件编程与开发环境 • 典型应用案例分析 • DSP发展趋势与挑战 • 实践项目设计与实现

01 DSP概述

定义与发展

定义

数字信号处理(Digital Signal Processing,简称DSP)是一门涉及多个学科 的交叉学科,主要研究将模拟信号转换为数字信号,并对数字信号进行各种处 理。

通信信号处理应用

总结词

通信信号处理是数字信号处理的另一个重要应用领域,涉及信号的调制、传输和解调等环节。

详细描述

在通信信号处理中,数字信号处理技术可以用于信号的调制、编码、解调和解码等环节,同时还可以 进行信号特征提取、分类和识别等任务。具体的应用包括移动通信、卫星通信、数字电视和雷达信号 处理等。

未来DSP将进一步提高处理速度和效率,满足更 多复杂应用的需求。

更低的功耗

通过不断优化技术,降低DSP的功耗,延长设备 的使用寿命。

更广泛的应用领域

DSP将在更多领域得到应用,如智能家居、自动 驾驶、医疗保健等。

06 实践项目设计与 实现

项目需求分析与设计思路

明确项目目标

01

在开始实践项目之前,需要明确项目的目标,包括要实现的功

数字信号处理的理论与实践

数字信号处理的理论与实践数字信号处理(DSP)是一种数字化的信号处理技术,与传统的模拟信号处理相似,但使用数字信号代替模拟信号。

由于数字信号处理器的强大计算能力和广泛适用性,DSP技术已被广泛应用于通信,娱乐,生物医学和音频处理等领域。

一、理论基础在DSP技术中,数字信号通常通过模数转换器(ADC)转换为数字形式,然后由数字信号处理器(DSP器)进行采样,量化和处理。

DSP技术的理论基础主要包括时域信号处理,频域信号处理和滤波技术。

时域信号处理是指将数字信号看作随时间变化的信号,并利用时间域的方法进行信号分析的过程。

典型的时域分析方法包括卷积,相关和自相关分析,以及快速傅里叶变换(FFT)等。

频域信号处理是指将数字信号转换为频率域信号,并使用频域分析技术解决问题。

典型的频域分析方法包括傅里叶变换,数字滤波器的设计和数字化滤波器的设计。

滤波技术是数字信号处理中的核心问题,用于去除通信中的噪声,改善音频信号,以及调制和解调数字信号。

滤波分为两种类型:数字滤波和数字化滤波。

数字滤波是指直接对数字信号进行处理,而数字化滤波是指使用数字滤波器对模拟信号进行处理。

二、实践应用DSP技术在许多领域都有广泛的应用。

在通信领域中,DSP技术用于调制和解调数字信号,对信号进行滤波和二进制解码,以在数字通信中提高通信质量和信号传输速率。

在娱乐领域中,DSP技术用于处理音频和视频信号,以改善音频和视频质量,并提供环绕声和多媒体体验。

在生物医学领域中,DSP技术用于声波成像和信号处理,以辅助医疗诊断和治疗。

在自动控制领域中,DSP技术用于实时控制系统,包括机器人控制,自动驾驶汽车和航空器自动导航等。

此外,DSP技术还被广泛应用于音频和视频编解码,图像和视觉处理,雷达,信号处理以及旅游导航等领域。

三、未来发展趋势随着人工智能和机器学习技术的不断发展,DSP技术将面临更大的挑战和机遇。

DSP技术将有助于构建更高效的人工智能算法,并推动物联网,智能城市和自动驾驶等领域的发展。

什么是数字信号处理器(DSP)如何设计一个简单的DSP电路

什么是数字信号处理器(DSP)如何设计一个简单的DSP电路数字信号处理器(DSP)是一种专门用于处理数字信号的集成电路。

DSP可以对数字信号进行滤波、采样、压缩、降噪等处理,广泛应用于通信、音频、视频、雷达、医学影像等领域。

本文将介绍数字信号处理器的基本原理和设计一个简单的DSP电路的步骤。

一、数字信号处理器(DSP)的基本原理数字信号处理器(DSP)是一种专门设计用于执行数字信号处理任务的微处理器。

与通用微处理器相比,DSP的设计更加专注于数字信号处理和算法运算能力。

其主要特点包括:1. 高性能和低功耗:DSP采用了高性能的算法执行引擎和专用的数据通路结构,以实现高效的信号处理和低功耗运行。

2. 并行性和高密度:DSP通常拥有多个算术逻辑单元(ALU)和多路访问存储器(RAM),能够并行处理多个数据流,提高处理速度和效率。

3. 特定接口和指令集:DSP通常具有专门的接口和指令集,以适应数字信号处理算法的需要,如乘积累加、快速傅里叶变换等。

4. 可编程性和灵活性:DSP具备一定的可编程性,可以通过修改指令序列或参数配置,适应不同的应用需求,并能够方便地进行算法的更新和升级。

5. 软件开发支持:DSP通常有配套的开发环境和软件库,支持算法开发、调试和优化,简化开发流程。

二、设计一个简单的DSP电路的步骤设计一个简单的DSP电路涉及到以下几个主要步骤:1. 需求分析:确定所需信号处理任务的具体要求和性能指标,如采样率、频带宽度、处理算法等。

2. 系统建模:基于需求分析结果,对系统进行建模,包括信号源、传感器、前端采集电路、信号处理电路等组成部分。

3. 算法设计:选择适合的数字信号处理算法,如滤波、变换、解调等,根据系统建模结果进行算法设计和优化。

4. DSP芯片选择:根据系统要求和算法设计结果,选择合适的DSP 芯片,考虑性能、功耗、接口等因素,以及DSP芯片的开发和调试支持。

5. 电路设计:设计DSP电路的硬件部分,包括时钟、存储器、接口电路等,使用原理图和PCB布局工具进行设计。

数字信号处理系统DSP

数字信号处理DSP教材 2006.4.18§1.前言§2.数字信号预处理§3.东华信号测试分析系统中数字信号预处理§4.经典数字信号处理§5.近代数字信号处理技术:§6.DSP软件性能示例: DH-5920/22动态信号测试分析系统§7.专题附录一:参考文献附录二:图例(六张)(下文中各注为较深内容,初学时可跳过不看;本次讲座也不讲)在对传感器传来的即原始的信号进行处理前应了解其基本情况1.机械的测试工况(起动,惰转或盘车,正常运行 ,带故障运行 ,短时超速试验,停车),2.传感器种类型号性能:加速度,速度,位移,力,应变片;非接触式(如涡流计,LVDT差动变压器,霍尔传感器),接触式(LVDT差动变压器,ICP压电计(要恆流源),非ICP压电计(要电荷放大器,需要其参数)传感器灵敏度,频率范围,动态范围,安装方式(磁铁座,螺接,粘接,胶带(双面胶带,金属胶带+502)3. 数采仪器种类型号性能 ,通道数,AC耦合还是DC耦合,4.传感器与数采仪器何时校准,校准后的灵敏度等参数变动情况5.响应点测量位置,方向与编号 , 激励点位置,方向与编号,采样时间间隔Δt(采样频率Fs=1/Δt) 与采样点数 N,6.测试过程中工况和仪器增益或量程或滤波器截止频率变化情况 ( 如有 ),7. 是在现场测原型还是在实验室测模型(模型可用测力法,原型常常只能用不测力法)等等应在分析前由测试人员提供给信号处理人员.* 3M带: 鲍山 010-********,139******** 德国带: 赵小亮(长城所) 010-********* 带ICP(集成电路压电计)插座的东华数采仪器可直接与ICP传声器(麦克风)连接测量声音或噪声国内最好的声望公司ICP传声器+放大器约4000元, 测量声音可以求共振频率以至振型* 智能传感器TEDS(Transducer Electronic Data Sheet, 符合IEEE-P1451标准)是智能型模拟和数字混合模式传感器. 模拟模式用于输出测量信息,数字模式用于储存传感器信息如传感器型号,序列号,灵敏度校准值, 安装位置方向等.并可用专用仪器或通用PDA等读出* 无线传感器有兰牙和IEEE802.11,大容量存储传感器东华也正在研制中§1.前言1.1信号是载有信息的载体或物理表达式,.它携带信息从源到目的地.信号(SIGNAL)一词有时指纯信息(INFORMATION,如信噪比SNR),有时指混有噪声的信息(如信号降噪).噪声也可称为对我们'无用的信息',它干扰我们研究'有用的信息'.注1: 信号与信息有时概念不同,如信号理论(如本文),信息理论(如编码学,密码学等,本文不涉及).1.2 信号分类很多,如1.以物理特性分1.1 电信号1.2 振动信号一般机械或结构固有频率范围 0~10 kHz(MIL-STD-819F)试验频率范围飞行环境 20~2000 Hz地面运输 0.3~200 Hz1.3 冲击信号,爆炸信号1.4 声信号可听声 20~20 kHz1.5 力信号力传感器有的以最高频率计,有的(如PCB)以时间常数计1.6 压力信号压力传感器最高频率难以测量,用前沿上升时间(可用激波管测量)推算Fh=0.35/τFh--最高频率, τ--压力由0.1幅值上升到0.9幅值的时间1.7 应变信号应变无互易原理, 动应变的频响矩阵非对称阵.2.以连续或离散分2.1 模拟信号传感器输出的信号,也叫连续信号2.2 采样信号时间域用时间间隔Δt离散后的信号2.3 量化信号幅值域用量化单位q量化后的信号2.4 数字信号时间域和幅值域双离散后的信号从模拟信号到数字信号转换除双离散外,有时还有‖有限化‖(截断),把无限信号变成有限信号,或把过长信号变成足够长的信号.截断也称加矩形窗.说明1:模拟信号变成数字信号用模数转换器ADC实现N位ADC的动态范围(也叫信噪比) DR=6.02N+1.76≈6N (dB)例 N=16,DR≈96(dB) 说明2: 离散化产生泄漏Leakage,有限化产生混迭Aliasing, 详见后述.量化产生量化误差(高频) 说明3: 现在ADC位数最多已达24位,量化误差可忽略不计3.输入(激励)信号:一般为力 f(t)输出(响应)信号:一般为加速度 a(t)系统(特性)信号:常用脉冲响应函数 h(t),详见后述说明4:用于系统识别,或环境试验,或共振试验…的输入信号正弦定频(Dwell), 正弦步进, 正弦(慢)扫描,多频正弦脉冲, 正弦快扫(Chirp),阶跃纯随机(Pure Random),猝发随机(Burst Random),伪随机(Pseudo Random),周期随机4. 静态信号(直流信号)准静态(Quasi-Static) 信号,也称缓变信号. 频率大约小于1~2赫兹动态信号最低频率Fl > 0 (一般在0.1~0.3Hz左右)静动态信号最低频率Fl = 0,要用有直流响应的电容式加速度计,压阻式加速度计, 应变式加速度计测量5.( 时域 )实信号( 时域 )复信号 Xc(t)=Xr(t)+j Xi(t) Xr(t)-- 复信号的实部, Xi(t)-- 复信号的虚部, j=√-1物理信号全是实信号,但在研究相量(PHASOR),微分方程求解,迟滞阻尼,细化(ZOOM),包络(ENVELOP), 实信号的傅里叶变换(频域复信号)等等问题必须采用复信号注1: ADC常用有逐次逼近型和Sigma-Delta(Σ-Δ) 型,后者可用过采样,整形,调制等措施大大抑制噪声.注2:如果一系统,输入实信号Xr时, 输出为实信号Yr; 则可证明当假设输入为复信号X=Xr+jXi而原信号作其实部时, 计算得到的输出复信号的实部一定是Yr!注3:实信号也可表示为两共轭复信号之和,如cosωt=0.5(e jωt+ e-jωt)(欧拉公式).它简化了计算, 如微积分变成乘除,微分方程变成代数方程等,但也带来了物理上无意义的‖负频率‖和‖双边谱‖,‖单边谱‖之争.6. 时限(|t|>T0,x(t)=0),非时限频限(|f|>T0,X(f)=0), 非频限由傅里叶变换的尺度性质如 y(t)←→Y(f) 则y(kt)←→(1/|k|)Y(f/k),可知时域愈宽(窄),频域愈窄(宽)还可由傅里叶变换公式可得时限信号频域一定频无限,反之亦然7.平稳信号(Stationary,统计特性与时间起点无关),非平稳信号;6.时域单边(因果Causal)信号t < 0 x(t)=0时域双边(非因果)信号频域单边(解析)信号, f < 0 X(f)=0频域双边(非解析)信号注 4:海森堡测不准(不确定)原理:原定理为量子力学中位置和动量不能同时测准,量子力学与信号处理比拟时,变成信号时域宽度乘频域宽度ΔtΔf≥1/2,等式只对高斯信号成立.注5:单个信号本无所谓因果不因果,此名词来自因果系统的脉响函数h(t)必须是单边函数.注6:解析信号名词来自数学中满足Cauchy-Riemann可微条件的复函数称为解析函数解析信号是复信号,其频谱是单边谱,与实测结果相同(实测不会有负频率!).7.最小相位,非最小相位(最大相位,混合相位)信号;幅值谱相同的信号可能有无限多个,其相位谱有最小相位, 最大相位和中间相位(混合相位)注7:MATLAB命令RCEPS可将非最小相位信号转变成幅值谱相同的最小相位信号.8.确定性信号( 周期,非周期,似ALMOST周期,瞬态;... ),可以预测某时刻的瞬时值随机信号 :不能预测某时刻的瞬时值,只能了解其统计特性值如概率密度或各阶矩(均值,方差,…) 随机信号又可分为平稳随机信号:统计特性不随时间而变非平稳随机信号;遍历(Ergodic)信号集时间平均等于集合平均非遍历信号集以下讨论与范数(Norm),信号空间理论有关的一种分类.它对了解小波理论,了解近代分析仪为什么有多种单位 (U,U2,U/Hz,U2/Hz,U2s/Hz,U/√Hz )很有用.注7:MATLAB命令RCEPS可将非最小相位信号转变成幅值谱相同的最小相位信号注8:范数最通俗解释是比大小,标量可比大小,矢量,矩阵,函数也要用范数来比大小. 标量大小只有一个标准,范数有多个标准,常用欧几里德范数.1.2.1 .模拟信号(设x(t)单位为U)的分类1.绝对可积信号x(t): ∫|x(t)|dt < ∞t = -∞~+∞绝对可积信号傅里叶变换存在,有傅里叶谱密度X(f), X(f)单位为U/Hz2.平方可积信号x(t): ∫|x(t)|2dt < ∞t = -∞~+∞平方可积信号有能量谱密度(ESD)Gxx(f),Gxx(f)单位为(U2s)/Hz3.均方可积信号x(t): TLim (1/T) ∫|x(t)|2dt < ∞T→∞ 0均方可积信号有功率谱密度(PSD)Pxx(f),Pxx(f)单位为U2/Hz信号理论中的‖功率‖指‖平方量‖,如电压平方,电流平方,加速度平方,...; 平方量乘秒为‖能量‖.1.2.2.离散信号(设x(nΔt)单位为U)1.绝对可和信号x(nΔt):绝对可和信号有傅里叶谱X(mΔf), X(mΔf)单位为U2.平方可和信号x(nΔt):平方可和信号有能量谱Gxx(mΔf), Gxx(mΔf)单位为U2s3.均方可和信号x(Δt):均方可和信号有功率谱Pxx(mΔf), Pxx(mΔf)单位为U2x(nΔt)以后简写为x(n)或x n X(mΔf) 以后简写为X(m)或X m注 9:大多数模拟信号如果绝对可积,则也平方可积,但两者仍有本质区别,如有绝对可积但非平方可积信号,如狄拉克函数δ(t), 时域绝对可积(=1)但平方不可积.时域绝对可积,频域可能非绝对可积( 如δ(t),时域面积为一,频域面积为无穷大)但是由巴氏(Parseval)定理,时域如果平方可积, 频域一定平方可积.又平方可积函数的和,积与卷积仍为平方可积函数巴氏定理:∫|y(t)|2dt=∫|Y(f)|2df注 10:周期信号如正,余弦波(简弦波)非绝对可积,现在可用广义函数作‖广义的‖傅里叶变换, 但早期不知道,研究输入为交流电的电系统特性时,有人将输入X,输出Y写为复指数如:X=Acos(ωt+α)-→X=A e jαe jωt,其中A exp(jα)称为相量(相位矢量PHASOR=PHASe vectOR),输入,输出相除后,exp(jωt)消掉,比值为频率函数,称为阻抗Z”(Z=X/Y ),导纳Y ( Y=Y/X )。

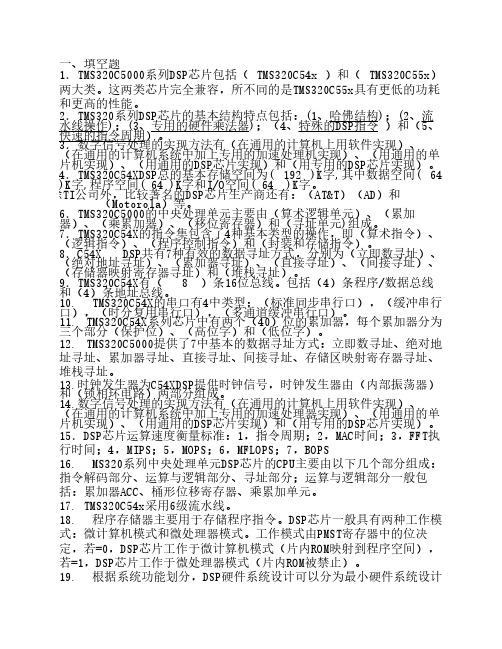

DSP芯片的原理与开发应用试题与答案【总结】

一、填空题1.TMS320C5000系列DSP芯片包括( TMS320C54x )和( TMS320C55x)两大类。

这两类芯片完全兼容,所不同的是TMS320C55x具有更低的功耗和更高的性能。

2.TMS320系列DSP芯片的基本结构特点包括:(1、哈佛结构);(2、流水线操作);(3、专用的硬件乘法器);(4、特殊的DSP指令 )和(5、快速的指令周期)。

3.数字信号处理的实现方法有(在通用的计算机上用软件实现)、(在通用的计算机系统中加上专用的加速处理机实现)、(用通用的单片机实现)、(用通用的DSP芯片实现)和(用专用的DSP芯片实现)。

4.TMS320C54XDSP总的基本存储空间为( 192 )K字,其中数据空间( 64 )K字,程序空间( 64 )K字和I/O空间( 64 )K字。

5.除TI公司外,比较著名的DSP芯片生产商还有:(AT&T)(AD)和(Motorola)等。

6.TMS320C5000的中央处理单元主要由(算术逻辑单元)、(累加器)、(乘累加器)、(移位寄存器)和(寻址单元)组成。

7.TMS320C54X的指令集包含了4种基本类型的操作,即(算术指令)、(逻辑指令)、(程序控制指令)和(封装和存储指令)。

8.C54X DSP共有7种有效的数据寻址方式,分别为(立即数寻址)、(绝对地址寻址)、(累加器寻址)、(直接寻址)、(间接寻址)、(存储器映射寄存器寻址)和(堆栈寻址)。

9.TMS320C54X有( 8 )条16位总线。

包括(4)条程序/数据总线和(4)条地址总线。

10. TMS320C54X的串口有4中类型:(标准同步串行口),(缓冲串行口),(时分复用串行口),(多通道缓冲串行口)。

11. TMS320C54X系列芯片中有两个(40)位的累加器,每个累加器分为三个部分(保护位)、(高位字)和(低位字)。

12. TMS320C5000提供了7中基本的数据寻址方式:立即数寻址、绝对地址寻址、累加器寻址、直接寻址、间接寻址、存储区映射寄存器寻址、堆栈寻址。

基于DSP的音频信号处理系统设计

基于DSP的音频信号处理系统设计一、导言随着数字信号处理(DSP)技术的不断发展和成熟,其在音频信号处理领域的应用也越来越广泛。

基于DSP的音频信号处理系统不仅可以实现高质量的音频处理和增强,也可以满足不同应用场景下的需求,如音频通信、娱乐、音频分析等。

本文将针对基于DSP的音频信号处理系统进行设计,从系统结构、信号处理算法、硬件平台等方面进行介绍和分析。

二、系统结构设计基于DSP的音频信号处理系统的设计首先需要确定系统的结构框架。

一般来说,这个结构包括了输入模块、DSP处理模块、输出模块和控制模块。

输入模块用于接收音频信号,可以是来自麦克风、音乐播放器、电视等各种音频设备。

DSP处理模块是音频信号处理的核心部分,其中包括了各种信号处理算法和算法的实现。

输出模块用于将处理后的音频信号输出到扬声器、耳机等输出设备中,以供用户听取。

控制模块可以用来控制和调节系统参数、算法选择、音频效果等。

三、信号处理算法音频信号处理系统的设计离不开各种信号处理算法的选择和实现。

常见的音频信号处理算法包括了滤波、均衡器、混响、压缩、编码解码等。

滤波算法用于去除音频信号中的杂音和干扰,使音频信号更加清晰;均衡器算法可以调节音频信号的频谱特性,使音频输出更加平衡;混响算法用于模拟不同的音频环境和效果;压缩算法可以调节音频信号的动态范围,使音频输出更加均衡;编码解码算法用于音频信号的数字化和解码处理。

在实际应用中,根据不同场景和需求,可以选择不同的信号处理算法,并通过DSP处理模块进行实现和调节。

四、硬件平台设计在基于DSP的音频信号处理系统的设计中,硬件平台的选择和设计也是非常重要的一部分。

常见的DSP芯片有TI的TMS320系列、ADI的Blackfin系列、Freescale的i.MX系列等。

在选择DSP芯片的还需要考虑到外围设备的选择和接口设计,如ADC(模数转换器)、DAC(数模转换器)、存储器、通信接口等。

为了提高系统的性能和稳定性,还需要考虑到功耗、体积、散热等方面的问题。

dsp数字信号处理课程设计报告

摘要:基于DSP的系统设计过程中,最小系统的设计是整个系统设计的第一步,系统设计总是从最小系统开始,逐步向系统应用扩展,最终实现以DSP为核心的大系统的设计。

因此,最小系统设计是DSP系统设计的关键。

DSP最小系统设计包括DSP电源设计和地线的设计,JPTG仿真口的设计,复位和时钟电路的设计,上拉和下拉引脚的设计等。

DSP的典型应用于网络,无线通信家电,另外还有虚拟现实,噪声对消技术,电机控制,图像处理等等。

可以说DSP是现代信息产业的重要基石,它在网络时代的地位与CPU在PC时代的地位是一样的。

它是信息产业的重要基石。

具有高速,专门为运算密集型而设计,目前速度已达到24亿次每秒。

高可靠性,也就是高重复性,例如雷达滤波器。

性价比高等特点。

关键词:复位电路;时钟电路;JPTG仿真口;电源;TMS3205402目录1 设计目的 (1)2 我的设计模块 (1)2.1TM320C5402 (1)2.2JTAG仿真接口的连接 (2)2.3引脚和测试信号 (4)3 最小系统的测试 (4)4 C5402 DSP最小系统PROTEL图(部分) (5)总结 (7)参考文献 (8)1 设计目的理解DSP系统开发的基本思路及方法,学习软硬件开发过程及资料收集与整理,学会撰写课程设计报告,学会对所学知识进行总结与提高,复习C语言的使用理解,C54XX汇编语言指令集。

2 我的设计模块2.1 TM320C5402TMS320VC5402是C5000系列中性价比较高的一颗芯片。

独特的6总线哈佛结构,使其能够6条流水线同时工作,工作频率达到100MHz。

VC5402除了使用VC54x系列中常用的通用I/O口(GeneralPurposeI/O,简称GPIO)外,还为用户提供了多个可选的GPIO:HPI-8和McBSP。

TMS320VC5402(简称VC5402)是TI公司的C54X家族的成员之一,它是基于先进的改进哈佛结构的16位定点DSP,拥有一条程序总线和3条数据总线。

DSP及其应用实践课程设计

DSP及其应用实践课程设计一、前言数字信号处理(Digital Signal Processing,DSP)是将模拟信号转换成数字信号,进而利用计算机进行处理、传输和存储的技术,在信号分析、图像处理、语音识别等领域得到了广泛的应用。

本文将介绍DSP及其应用实践课程的设计和实践情况。

二、课程设计思路本课程旨在通过理论学习与实践操作相结合的方式,帮助学生掌握DSP的基本概念、信号处理算法和系统设计方法,并在具体应用方面得到实践经验。

课程设计主要包含以下内容:1. 理论学习通过讲授DSP的基础知识,包括离散时间信号和系统、频率分析、数字滤波器等内容,使学生了解DSP概念、信号处理算法和理论基础。

2. 实验操作课程中设置实验操作环节,利用Matlab软件进行DSP信号处理算法的仿真实验和DSP芯片开发板的实验操作,让学生从实践中深入了解DSP的具体应用场景和处理方法。

3. 课程设计项目在课程设计项目中,学生需要选择一个具体的DSP应用方向进行深入研究和开发,并完成DSP方案设计和应用实现,如音频处理、图像处理等。

通过以上课程设计方式,使学生深入理解DSP技术在现实中的应用场景,培养学生解决实际问题的能力和创新精神。

三、课程实践情况本课程的实践内容主要包括Matlab仿真实验和DSP芯片开发板实验操作。

学生需要在实验室中,完成具体的DSP信号处理算法仿真以及DSP芯片开发板的实验操作。

1. Matlab仿真实验Matlab仿真实验环节的主要内容是利用MATLAB软件对DSP信号处理算法进行仿真实验。

学生首先需要了解MATLAB软件的基本操作,接着学习DSP信号处理算法的相关知识,如离散傅里叶变换、数字信号滤波等。

最后实际操作MATLAB软件进行仿真实验,掌握DSP信号处理算法的实际应用。

2. DSP芯片开发板实验操作DSP芯片开发板实验操作环节是课程实践的重点,学生需要在DSP芯片开发板上操作,完成具体的DSP信号处理任务。

DSP重点知识点总结

DSP重点知识点总结DSP(数字信号处理)是一门涉及数字信号获取、处理和分析的学科。

DSP技术被广泛应用于通信、音频和视频处理、雷达和图像处理等领域。

下面是DSP的重点知识点总结。

1.信号与系统理论:信号可以理解为一种函数或者波形,可以用数学模型表示。

系统是根据输入信号产生输出信号的过程。

信号与系统理论研究信号和系统之间的关系,如卷积、频谱分析等。

2.时域和频域分析:时域分析是指对信号在时间上的特征进行分析,如幅度、相位、周期等。

频域分析则是将信号在频率上进行分析,如频谱、谐波成分等。

3.Z变换和离散时间系统:Z变换是一种离散信号处理的分析工具,它可以将离散时间信号转换成复变量的函数。

离散时间系统是一种对离散时间信号进行处理的系统,可以用系统函数来描述其输入输出关系。

4.数字滤波器设计:数字滤波器是一种对数字信号进行滤波处理的系统。

低通滤波器可以通过去除高频成分来平滑信号,高通滤波器则可以去除低频成分,带通滤波器可以只保留一些频段的信号。

5.快速傅里叶变换(FFT):FFT是一种将时域信号转换成频域信号的算法,它可以高效地计算信号的频谱。

FFT广泛应用于频谱分析、滤波器设计、信号压缩等领域。

6.语音信号处理:语音信号处理是DSP的一个重要应用领域。

它包括语音信号的获取、去噪、压缩、识别等技术。

常用的算法包括线性预测编码(LPC)、梅尔倒谱系数(MFCC)等。

7.图像处理:图像处理是DSP的另一个重要应用领域。

它包括图像的获取、增强、压缩、分割、识别等技术。

常用的算法包括离散余弦变换(DCT)、小波变换等。

8.数字信号处理芯片:数字信号处理芯片是一种集成了数字信号处理功能的专用芯片。

它可以高效地进行信号处理和计算,并广泛应用于通信设备、音频设备等领域。

9.数字信号处理应用:DSP技术在通信、音频、视频、雷达、图像等领域有广泛的应用。

例如,DSP可以用于音频信号的压缩、通信系统的调制解调、雷达信号的处理等。

dsp项目课程设计

dsp项目课程设计一、课程目标知识目标:1. 学生能理解数字信号处理(DSP)的基本概念,掌握其基本原理和应用领域。

2. 学生能运用数学知识,如傅里叶变换、Z变换等,分析并解决实际问题。

3. 学生能了解DSP技术在现实生活中的应用,如音频处理、图像处理等。

技能目标:1. 学生能够熟练使用DSP开发工具和软件,完成简单的项目设计。

2. 学生能够运用所学知识,设计并实现一个简单的DSP应用系统,如音频信号滤波、图像去噪等。

3. 学生能够通过小组合作,培养团队协作和沟通能力,提高问题解决能力。

情感态度价值观目标:1. 学生能够认识到数字信号处理在科技发展中的重要性,激发对相关领域的兴趣。

2. 学生在学习过程中,培养勇于探索、积极进取的精神,增强自信心。

3. 学生通过课程学习,认识到科技发展对社会的贡献,树立正确的价值观。

课程性质:本课程为实践性较强的课程,结合理论教学和实际操作,培养学生对数字信号处理技术的理解和应用能力。

学生特点:学生具备一定的数学基础和编程能力,对新技术充满好奇,喜欢动手实践。

教学要求:教师需结合课本内容,以实际项目为导向,引导学生掌握基本理论,提高实际操作能力。

在教学过程中,注重培养学生的团队协作和创新能力,提高学生的综合素质。

通过课程目标分解,确保学生能够达到预期学习成果,为后续教学设计和评估提供依据。

二、教学内容1. 数字信号处理基础理论:- 傅里叶变换理论及其应用- Z变换及其性质- 离散时间信号与系统2. DSP算法与应用:- 数字滤波器设计- 快速傅里叶变换(FFT)算法- 数字信号处理在音频、图像领域的应用3. DSP实践项目:- 项目一:音频信号处理(滤波、增强)- 项目二:图像处理(去噪、边缘检测)- 项目三:DSP综合应用(如语音识别、图像识别)4. 教学内容的安排与进度:- 基础理论部分:占总课时的1/3,以课本相关章节为基础,逐步引导学生掌握基本概念和原理。

DSP课设PWM

目录一引言与概述_________________________________________________________ 2 1.1 DSP介绍 _______________________________________________________________ 2 1.2DSP的应用:____________________________________________________________ 2 1.3问题描述_______________________________________________________________ 3 1.4 DSP2407简介 ___________________________________________________________ 3 1.5事件管理器的引脚说明___________________________________________________ 4 1.6比较单元_______________________________________________________________ 4 1.7 PWM基本原理__________________________________________________________ 4二系统总体设计与工作原理_____________________________________________ 6 2.1总体设计与分析_________________________________________________________ 6 2.2基本理论_______________________________________________________________ 7三各单元硬件设计及工作原理__________________________________________ 12四软件设计与说明____________________________________________________ 12 4.1程序文件说明__________________________________________________________ 12 4.2主程序(pwm.c) _________________________________________________________ 13 4.3向量表程序(vectors.asm) _________________________________________________ 14 4.4存储器配置(2407CMD.cmd) ______________________________________________ 14五调试结果及其操作说明______________________________________________ 15 5.1 CCS 集成开发环境_____________________________________________________ 15 5.2 CCS 的调试操作_______________________________________________________ 15六参考文献__________________________________________________________ 16一引言与概述1.1 DSP介绍数字信号处理(Digital Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

如何使用数字信号处理器进行电路设计和优化

如何使用数字信号处理器进行电路设计和优化数字信号处理器(Digital Signal Processor,简称DSP)是一种专用的数字信号处理芯片,广泛应用于电子电路的设计和优化。

本文将介绍如何使用DSP进行电路设计和优化,以提高电路的性能和效率。

一、DSP在电路设计中的应用1. 数字信号处理算法的开发:通过DSP可以实现各种数字信号处理算法,如滤波、快速傅里叶变换(FFT)、数字调制解调等。

这些算法可以在电路设计中应用于信号处理、通信、音频处理等方面。

2. 数字控制系统设计:DSP可以用于设计数字控制系统,实现对电路的精确控制。

例如,通过DSP可以设计电机驱动器、机器人控制系统等,提高电路的控制性能和稳定性。

3. 音频处理和音效设计:借助DSP的高性能计算能力和丰富的数字信号处理算法,可以实现音乐合成、音频编解码、音效设计等应用。

这些应用广泛用于音频设备、影视制作等领域。

二、DSP电路设计的步骤1. 电路分析和需求确定:首先对待设计的电路进行全面的分析,明确电路的输入输出特性、性能要求等。

根据需求确定DSP的选择和配置。

2. DSP编程环境配置:根据所选DSP的型号和开发平台,配置相应的DSP编程环境。

常见的DSP开发工具包括CCS(Code Composer Studio)等。

3. 算法实现和优化:根据电路的特点和需求,在DSP编程环境下实现相应的数字信号处理算法。

同时,需要根据硬件平台和性能要求对算法进行优化,以提高整体的计算效率和响应速度。

4. 系统集成和测试:将DSP实现的算法与电路的硬件平台进行集成,进行系统级测试和调试。

确保DSP与其他电路模块的正常协作和性能符合设计要求。

5. 性能评估和优化:通过实际测试和性能评估,对DSP设计进行优化。

可以采用性能分析工具对DSP的运行效率和功耗进行评估,进一步提高电路的性能和效率。

三、DSP电路设计的注意事项1. DSP硬件资源的合理分配:在设计中要充分考虑DSP的计算能力和存储资源的限制,合理分配和利用硬件资源,以满足电路的计算需求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

BRINT0_ISR:

✓ 串行ADC和DAC ✓ 并行ADC或DAC

▪ ADC/DAC主要性能指标

✓ 采样频率 ✓ 采样精度 ✓ 接口类型 ✓ 自带采样保持与否 ✓ 通道数目 ✓ 电源数量和特性 ✓ 封装尺寸

▪ TLC320AD50C结构

▪ TLC320AD50C操作

✓ 主、从工作方式 ❖ 当M/S为高电平时,工作在主设备方式,此时FS和 SCLK为输出信号。当M/S为低电平时,工作在从设 备方式,数据传输由输入FS的和SCLK同步 ❖ 在与DSP的McBSP连接时,一般将TLC320AD50C 配置为主方式,而McBSP为从方式

✓ 主通信和辅助通信模式

❖ 主通信用于正常的ADC或DAC的数据传输,辅助 通信用于控制寄存器的读写 ❖ 辅助通信模式可由硬件和软件两种方式触发

✓ 两种数据格式 16位数据格式和15+1数据格式

▪ TLC320AD50C时序

FS

DIN or D O UT

FS DIN or D O UT

Primary 16 SCLKs

数字信号处理系统 设计和实践理论

第六章 DSP外围设备接口介绍

主要内容

➢ DSP与ADC、DAC的接口 ➢ DSP与外部存储器的接口 ➢ DSP与串口通信的接口 ➢ DSP与PCI总线的接口 ➢ 小结

➢ DSP与ADC、DAC的接口

▪ ADC/DAC的分类 ✓ 集成的模数(A/D)和数模(D/A)转换器(CODEC) ✓ 独立ADC或DAC ✓ 可编程 ADC和DAC ✓ 固定ADC或DAC

✓ 控制寄存器2(默认值00000000b,地址00010b)

比特位 描述 7 FLAG管脚输出值 6 D6=1:电话模式使能,D6=0:电话模式禁止 5 抽取FIR滤波器溢出标志 4 D4=1:16比特ADC数据格式,D4=0:15+1比特ADC数据格式 3 D3=1:模拟环路使能,D3=0:模拟环路禁止 2-0 保留

16 or 15+1 Data Primary 16 SCLKs

Secondary 16 SCLKs

16 or 15+1 Data

Register related data

128 SCLKs 256 SCLKs

▪ TLC320AD50C内部控制寄存器 ✓ 控制寄存器1(默认值00000000b,地址00001b)

;************************ macro definition ***********************eg

stm

#SPSA0, aux_reg

st

#0, *aux_reg+

orm

#0x0001, *aux_reg-

st

#1, *aux_reg+

✓ 控制寄存器3(默认值00000000b,地址00011b)

比特位 描述 7-6 从设备个数 5-0 FSD延迟于FS的SCLK个数,最小为18

✓ 控制寄存器4(默认值00000000b,地址00100b)

比特位 描述 7 D7=1:旁通内部PLL,D7=0:使能内部PLL 6-4 采样频率选择(N):fs=MCLK/(128N)或MCLK/(512N), 001b:N=1,010b:N=2,000b:N=8 3-2 D3D2=11b:模拟输入增益关闭 D3D2=10b:模拟输入增益=12 dB D3D2=01b:模拟输入增益=6 dB D3D2=00b:模拟输入增益=0 dB 1-0 D1D0=11b:模拟输出增益关闭 D1D0=10b:模拟输出增益=12 dB D1D0=01b:模拟输出增益=6 dB D1D0=00b:模拟输出增益=0 dB

▪ 辅助通信模式下DIN和DOUT数据格式

▪ TLC320AD50C与DSP的连接

✓TLC320AD50C的初始化例程

;*************************** begin *****************************

.mmregs

.include "AD50C_cnst.h54" ;include the constants used by the aic

andm

#0xfffe, *aux_reg-

.endm

;************************ memory allocation ************************

.bss

serial_int_flag, 1

;************************ interrupt vectors table **********************

比特位 描述 7 D7=1:软件复位 6 D6=1:软件下电 5 D5=1:AUXP和AUXM为输入,D5=0:INP和INM作为输入 4 D4=1:监控AUXP和AUXM,D4=0:监控INP和INM 3-2 D3D2=11b:监控放大器增益=-18dB D3D2=10b:监控放大器增益=-8dB D3D2=01b:监控放大器增益=0dB D3D2=00b:监控放大器关闭 1 D1=1:数字环路使能,D1=0:数字环路禁止 0 D0=1:16比特DAC数据格式,D0=0:15+1比特DAC数据格式

.sect "vectors"

int_reset: b

Main ;Main program

nop

nop

.space 76*16

int_brint0:

;McBSP0 reveive interrupt

bd

BRINT0_ISR

pshm ST0

pshm ST1

.space 44*16

.text

;************************ Interrupt Service Routine *******************

orm

#0x0001, *aux_reg-

.endm

;reset RRST/XRST to disable McBSP

McBSP0_DISABLE

.macro aux_reg

stm

#SPSA0, aux_reg

st

#0, *aux_reg+

andm

#0xfffe, *aux_reg-

st

#1, *aux_reg+