基于DDS的无线数据传输系统设计与实现

基于dds的数字信号调制器的设计与实现

基于dds的数字信号调制器的设计与实现

本文设计并实现了一种基于DDS的数字信号调制器。

该调制器能

够产生多种常用数字信号调制方式,例如正弦波调制、脉冲调制等。

首先,我们介绍DDS的工作原理。

DDS全称为数字直接合成技术(Direct Digital Synthesis),其基本工作原理是通过数字信号处

理技术生成指定频率的信号。

它的硬件结构如下图所示:

(这里插入一张DDS的硬件结构图,不涉及网址、超链接和电话)

DDS通过内部寄存器中的相位累加器来控制输出的频率和相位。

相位累加器每隔一个时钟周期增加一个预先设定的相位步进量,输出

的正弦波频率正好等于相位累加器的输出频率。

基于DDS的数字信号调制器的工作原理如下:首先,我们将需要

调制的模拟信号进行模数转换,转化为数字信号;然后,通过DDS产

生指定频率的正弦波基带信号,对其进行调制,生成相应的调制信号;最后,将调制信号进行模数转换,转换为模拟信号输出。

我们采用FPGA作为DDS的控制器,使用Verilog语言实现控制

逻辑,并通过时钟模块、相位累加器模块、幅度控制模块、正弦波生

成模块、调制模块、D/A转换模块等多个功能模块来实现数字信号调制器的设计与实现。

实验结果表明,该数字信号调制器能够生成多种常用数字信号调

制方式,正弦波调制和脉冲调制的输出波形稳定、质量高,并且具有

很高的可靠性和空间适应性,能够满足实际应用需求。

基于DDS技术的信号源设计与实现_彭文标

表 3 AD9852 的控制寄存器

- 272 - 360元 / 年 邮局订阅号: 82-946

图 4 BPSK 子程序流程图 图 4 为 BPSK 输出是的子程序流程图, 首先根据需要设置 AD9852 的控制寄存器, 然后 设 置 载 波 信 号 的 频 率 控 制 字 、两 个 相位调节字, 将待调制数据送入 AD9852 的 29 脚, 最后, 待更新 时钟作用后, 电路就输出 BPSK 信号。

基金项目:谐波信号处理与谐波电能精确计量研究 湖 北 省 自 然 科 学 基 金 (2006ABA202)

中(并 行 地 址 为 1FH) 的 三 位 工 作 模 式 设 置 位 进 行 选 择 , 设 置 方 式如表 1 所列。

《P LC 技术应用 200 例》

邮局订阅号: 82-946 360 元 / 年 - 271 -

题。AD9852 采用 3.3V 供电, 和单片机之间应设置一电平转换电

路 ; 参 考 时 钟 可 以 单 端 输 入 , 也 可 以 差 分 输 入 , 当 DIFF/SINGLE

SELECT(pin64)为 高 电 平 时 , 应 该 采 用 差 分 输 入 , 当 DIFF/SIN-

技 GLE SELECT 为低 电平时, 应该采用单端输入; AD9852 采用高

N 时, 输出的信号频率为 fout=FTW*fsc/2N。

系 统 时 钟 下 输 出 频 率 的 精 度 可 达 0.07Hz; 可 进 行 sin(x)/x 校 正 ;

理论上, DDS 的最高 输 出 频 率 可 达 参 考 源 频 率 的 一 半 。 当 具有良好的动态性能, 在 100MHz 输出时, DAC 输出的抑制寄生

5 结束语

基于DDS技术的信号发生器的设计与实现

基于DDS技术的信号发生器的设计与实现DDS(Direct Digital Synthesis)技术是一种基于数字信号处理的频率合成技术,通过数字方式生成正弦波信号。

DDS信号发生器可以用于科学实验、通信系统中的频率合成、音频处理等应用领域。

通过DDS技术,可以实现高精度、稳定性好、频率范围广的信号发生器。

DDS信号发生器的基本原理是:通过一个相位累加器、一个频率累加器和一个波表,来生成一个时域上的正弦波信号,并将其转换为模拟电压信号输出。

相位累加器用来控制波表中的每个周期的采样点,频率累加器用来控制相位累加器的步进。

波表中存储了一个完整的正弦波周期的数值,波表的长度决定了信号发生器的频率分辨率。

DDS信号发生器的主要模块包括:时钟模块、相位累加器、频率累加器、波表和数模转换器。

时钟模块是DDS信号发生器的产生步进信号的时钟源,可以采用稳定的晶振或者时钟信号源。

时钟信号的频率决定了DDS信号发生器的输出信号的频率精度。

相位累加器是DDS信号发生器的核心模块,它接收时钟信号,并根据频率累加器的输入生成一个相位累加信号。

相位累加器可以采用简化的模数累加器,根据时钟信号的周期计算脉冲个数,每当相位累加信号增加一个固定的脉冲数时,波表就输出一个采样点。

频率累加器实时地改变相位累加器的步进,从而改变信号发生器的输出频率。

频率累加器可以通过输入一个控制信号来改变频率累加器的增加或减少的步进大小,从而实现更精细的频率调节。

波表是DDS信号发生器的存储波形数据的模块。

它包含了一个完整的正弦波周期的采样点的数值,波表的长度决定了信号发生器的输出信号的频率分辨率。

波表的数据可以事先存储在ROM中,也可以动态生成。

数模转换器将生成的波形数据转换为模拟电压信号输出。

数模转换器的位宽决定了输出信号的精度,位宽越大,精度越高。

除了上述基本模块,DDS信号发生器还可以添加比较器、滤波器等模块,以实现输出电平调节、滤波等功能。

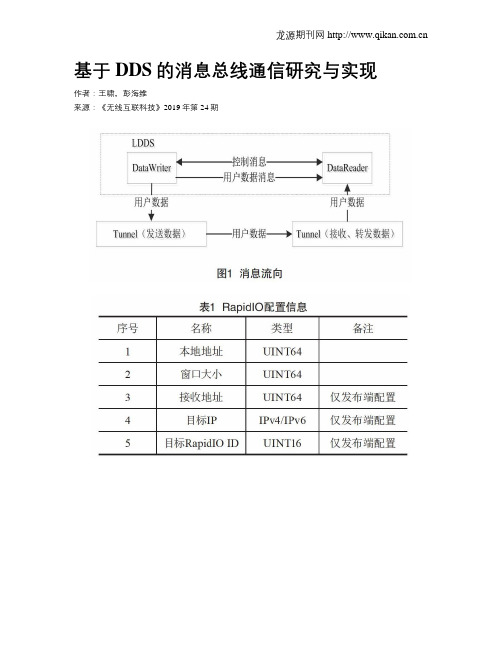

基于DDS的消息总线通信研究与实现

基于DDS的消息总线通信研究与实现作者:王啸,彭海维来源:《无线互联科技》2019年第24期摘要:文章对DDS进行了介绍,DDS实现了分布式环境中以数据为中心的数据实时传输,相比其他中间件,具有较好的灵活性、实时性和扩展性,所以DDS适用于对数据处理能力要求较高的场景。

通过对国产化LDDS产品进行分析、优化,给出了DDS适配通用消息总线的方案。

该技术具有通用性,适用于DDS适配多种消息总线。

结合RapidIO消息总线和国产化消息中间件LDDS,给出了具体的适配方案。

经优化适配后,LDDS可以广泛应用于消息量大的实时业务场景。

关键词:数据分发服务;发布/订阅;中间件;RapidIO在信息量爆炸的时代,如何实现各个节点快速通信以及如何对其进行高效的管理显得尤为重要。

尤其在军事领域,为实现军事装备武器系统快速适应新环境、动态重构新功能、及时应对新威胁,未来的军事电子装备势必从单平台向分布式多种异构平台统一协同处理发展;从相对封闭、单一功能向开放式、多任务、多功能一体化方向发展;从预先定义的固定信息流处理向智能化、软件化方向发展。

基于此,就必须解决异构分布式系统间的互联、互通和互操作问题。

消息中间件是当前一项实现异构系统之间快速访问的关键技术,可以屏蔽各个异构平台(包含软件和硬件)的差异,对应用者提供统一的标准通信接口,只需要关注业务本身的研究与开发,不需要感知具体平台的异构性。

目前这种开放式架构的消息中间件在我军相关设备系统和物联网中已经得到广泛的应用。

但现状是大多数消息中间件都是基于以太网实现的,而实际环境中,不仅需要支持以太网协议,还有高速串行通信总线(RapidIO)协议、增强型周边设备互连(PCIe)协议等[1]。

本文基于国产化数据分发服务(Data Distribution Service,DDS)的产品,在LDDS上对多种通信总线进行适配,并提出了通用的适配解决方案,可以快速适配多种消息总线,丰富了LDDS产品的功能,并使其通信性能得到了大幅的提高,满足了工业和军事设备上的通信要求。

dds方案

DDS方案概述DDS(Data Distribution Service)是一种实时数据分发中间件标准,旨在提供高性能、可靠的数据交换服务。

它广泛应用于工业自动化、网络通信、航空航天等领域,可满足高并发、低延迟、可扩展等需求。

本文将介绍DDS方案的基本原理、主要特点以及适用场景,并提供一些实际案例以供参考。

基本原理DDS方案的基本原理是发布-订阅模式,即数据的发布者(Publisher)将数据发布到特定的主题(Topic)上,而订阅者(Subscriber)则通过订阅相应的主题来接收数据。

DDS采用了一种分布式的架构,其中包含了各种组件,如发布者、订阅者、中间代理(Middleware)等。

发布者和订阅者通过中间代理来交换数据,中间代理负责数据的可靠分发、数据的过滤和转换等功能。

主要特点高性能DDS方案的核心目标之一是提供高性能的数据交换服务。

为此,DDS采用了一系列优化措施,如数据压缩、批处理、异步传输等。

这些措施可以显著提升数据传输的效率,降低系统的延迟。

此外,DDS还支持多种传输协议,如TCP/IP、UDP等,并可以根据实际需求选择最适合的协议进行数据传输。

可靠性DDS方案通过使用可靠的传输协议和机制来保证数据的可靠性。

它提供了丰富的错误处理机制,可以在数据传输过程中及时检测和处理错误,从而确保数据的完整性和可用性。

DDS还支持数据的持久化存储,可以将数据保存到本地磁盘或数据库中,以便在需要时进行回放和分析。

可扩展性DDS方案具有良好的可扩展性,可以根据实际需求灵活地扩展系统的规模和性能。

它支持集群部署,可以通过增加节点来提升系统的并发能力和容错性。

此外,DDS还提供了灵活的数据模型和接口,可以根据业务需求定制数据的格式和结构。

实时性DDS方案的设计目标之一是提供实时的数据交换服务。

它通过优化数据传输和处理的机制,可以在毫秒级别的延迟下实现数据的实时传输和响应。

DDS还支持数据的优先级处理,可以根据需求对数据进行优先级排序和处理,确保关键数据的实时性和可靠性。

基于DDS传输的较大数据包粘包的处理方法

基于DDS传输的较大数据包粘包的处理方法作者:蒋培培吴昊钱进来源:《无线互联科技》2023年第24期摘要:基于用户数据协议(UDP)的数据分发服务(DDS)传输是一种广泛应用在实时分布式系统的通信框架。

然而,DDS发送较大数据包时可能产生UDP粘包问题。

为解决这一问题,文章对比使用循环缓存和队列缓存方式存储DDS数据包的优缺点,给出了改进循环缓存存储方式,并提出了一种拆包粘包的数据处理方法。

结果可以得到完整正确的DDS数据包,说明了该方法的有效性。

关键词:DDS;较大数据包;UDP粘包;环形缓存;拆包粘包中图分类号:TP319.3 文献标志码:A0 引言数据分发服务[1](Data Distribution Service,DDS)是一种用于实时分布式系统的通信框架,它提供了高效、可靠的数据交换机制。

DDS在实时应用领域得到广泛应用,如现代化雷达、工业自动化、航空航天、医疗设备等。

在DDS中,选择适当的传输协议对数据传输的可靠性和性能具有重要影响。

尽管用户数据协议(User Datagram Protocol,UDP)[2]是一种无连接的、不可靠的传输协议,但它在某些情况下被广泛用于DDS的底层传输,以满足实时性和低延迟的需求。

然而,UDP在传输过程中存在一种常见的UDP粘包问题,UDP粘包指的是在网络传输过程中,多个数据包可能会被合并为一个较大的数据包,导致数据的丢失、重复和乱序。

这对DDS的可靠性和正确性产生了挑战,特别是对于那些对数据的时序性、完整性和顺序性要求较高的实时应用。

本文主要探讨在雷达数据处理中基于UDP的DDS通信传输时遇到的粘包问题,分析粘包对DDS通信的影响,对比2种缓存方式的数据包存储,同时,提出一种发送端拆包、接收端拆包粘包的数据处理方法,以确保传输的DDS数据在接收端的正确性和完整性。

1 DDS相关知识介绍1.1 DDS通信架构DDS是一种实时数据分发的协议和架构,用于构建分布式系统中的实时通信和数据分发应用。

DDS理论与实现

DDS理论与实现DDS(Data Distribution Service)是一种用于实时系统的通信协议标准,它提供了一种可编程的、分布式的消息传递机制。

DDS由OMG (Object Management Group)定义并得到广泛应用。

DDS理论和实现涉及很多方面,下面将从DDS的概念、特点和实现技术等方面进行详细探讨。

一、DDS概念DDS是一种基于发布/订阅模型的数据分发系统,提供了可靠、实时、分布式的消息传递。

在DDS中,数据的发布者(Publisher)将消息发布到DDS系统中,订阅者(Subscriber)根据自身的兴趣选择订阅消息,并接收到发布者所发送的信息。

DDS的核心概念包括数据样式、主题、QoS (Quality of Service)和通过数据访问接口进行交互等。

1.数据样式DDS中的数据通过数据样式定义其结构和类型。

数据样式包括IDL (Interface Definition Language)类型的定义,可用于描述数据的结构和字段等信息。

DDS提供了灵活的数据样式定义机制,可以根据具体应用的需求进行定制。

2.主题DDS中的主题(Topic)代表了发布者和订阅者之间共享的数据的抽象概念。

主题具有一个唯一的名称,发布者可以使用主题来发布消息,订阅者可以使用主题来选择订阅的消息。

DDS中的主题可以使用高级查询语言(SQL)进行搭配以便更好地描述订阅需求。

3.QoSDDS提供了一系列的QoS选项,可用于配置消息传递的质量和性能。

QoS选择包括消息可靠性、消息的传输速度、消息的持久性、数据的压缩等。

DDS的QoS机制可以根据需求进行灵活配置,以满足不同应用场景的需求。

4.数据访问接口DDS提供了一种数据访问接口,用于发布者和订阅者之间的交互。

通过数据访问接口,发布者可以将数据发布到DDS系统中,订阅者可以接收到发布者发布的消息。

DDS的数据访问接口提供了丰富的API,可以支持多种编程语言。

一种基于DDS技术的通信信号的调制方法与设计

万方数据万方数据模块的端口描述,其中clk由PLL将外部50MHz晶振倍频为212.5MHz后提供模块使用;clr为清零端;freq是用于设置基波输出频率,FM等调频载波是在该频率下进行基波频率增减调整;sele是不同调制类型的选择;sigal是输入被调制信号;out是输出调制完成的信号。

4系统测试及结果调制模块VerilogHDL语言端口描述moduleSigatWave(elk,clr,freq,sele,sigal,out);inputclk;//系统同步时钟inputclr;//清零复位信号input[19:0]freq;,/基波频率设置input[2:0]sele;//调制类型选择input[9:o]sigal;//通讯信号输入output[9:0]out;//调制信号输出图3调制模块端口描述将调制模块与外围接口模块相连接,实现系统功能。

本设计中,DA采用ADI公司的10位视频D/A转换器ADV7123,其速度最高可达240Msample/s;输出功率放大电路采用THS4211芯片,THS4211是TI公司推出的一款运放,该运放采用的是电压反馈,并图4实拍波形图且具有放大频率宽、功耗低等优点。

将程序下载到电路板后进行系统测试,图4为几种实拍的波形。

采用FPGA的设计方案可以直接面对用户,具有极大的灵活性和通用性,硬件测试和实现快捷.开发效率高,成本低,电路的体积小,稳定性好,而且可调制信号的步进精度有保证,产生的波形不失真,输出的波形稳定,有使用和推广的价值。

如对本文内容有任何观点或评论,请发E-mail至sjtx@21cn.com参考文献[1]付扬.基于FPGA直接数字频率合成两种控制电路设计.微计算机信息,2007,23(4~2)[2]孙超,林占江.基于DDS的雷达任意波形信号源的研究.电子测量与仪器学报,2008,(4):31~36f31尹继武.基于DDS技术提高频谱仪的频率分辨率.传感器与仪器仪表.2008,(5):153~154[4]王炜,赵可萍,郑易.基于FPGA的调制信号电路设计.微计算机信息,2007,(2)(收稿日期:2008年9月24日)DesignationandImplementationofCommunicationSignalModulatorBasedonDDSWuJinyin91,LinHuijun2,MaoHuazhanl,WuHa01(I.InstituteofPhysicsandInformationTechnologyphotoelectric,FujianNormalUniversity,Fuzhou350007,China)(2.SchoolofMathematicsandComputerScienceandTechnology,FujianNormalUniversity,Fuzhou350007,China)AbstractDirectDigitalSynthesis(DDS)technologyiswidelyusedinthefieldofwirelesscommunication.WithFPGA,thedesignandimplementationofsignalmodulatorbasedonDDSisintroducedinthispaper.ThismodulatorcouldimplementthesignalmodulationbothdigitalandanalogasFM,FSK,AM,ASK,PSK.Thefundamentalfrequencyofthissystemisadjustable,between100Hzand70Hz.KeywordsDI)S,FPGA,high—frequencyamplification,high-frequencymodulation中国新通信2008.1163万方数据。

基于dds技术的信号源设计

基于dds技术的信号源设计DDS技术是目前广泛应用于数字信号处理和通信的核心技术之一。

基于DDS技术的信号源设计可以实现高精度、高稳定性、高灵活性和低噪声等优异的性能,因此在无线通信系统、卫星通信、雷达系统、测量仪器等领域得到了广泛应用。

一、DDS技术简介DDS全称Direct Digital Synthesis,即直接数字合成技术。

它是一种基于数字信号处理技术和先进的ASIC、FPGA和DSP技术的数字频率合成器。

数字频率合成技术是一种通过数字计算实现频率合成的技术,它克服了传统的模拟频率合成器存在频率稳定度和相位噪声等问题。

二、基于DDS技术的信号源设计基于DDS技术的信号源设计主要包括两个方面,即DDC和DUC。

1.DDCDDC全称Digital Down-Converter,即数字下变频器。

它是一种基于DDS技术实现的数字信号处理器件,能够将高频率信号数字化并进行数字信号处理,提取出信号中的基带信号或低通信号。

通常采用FPGA或DSP为核心芯片,通过数字计算、滤波、放大等步骤实现信号处理功能。

2.DUCDUC全称Digital Up-Converter,即数字上变频器。

它是一种基于DDS技术实现的数字信号处理器件,能够将基带信号或低通信号进行数字信号处理,并将其变换到高频率,形成高频信号。

通常采用FPGA或DSP为核心芯片,通过数字计算、滤波、放大等步骤实现信号处理功能。

三、基于DDS技术的信号源设计的优势基于DDS技术的信号源设计比传统的信号源设计具有许多优势:1.高精度:DDS技术采用数字计算的方式实现信号合成,能够实现非常高的频率精度和相位精度,使得合成的信号具有非常高的精度。

2.高稳定性:DDS技术能够对合成信号的频率、相位和幅度等参数进行精确控制,使得信号具有非常高的稳定性,不会因为环境温度或供电电压等因素的变化而导致信号出现偏差。

3.高灵活性:DDS技术能够实现任意的信号合成,使得用户能够非常灵活地产生各种形式的信号。

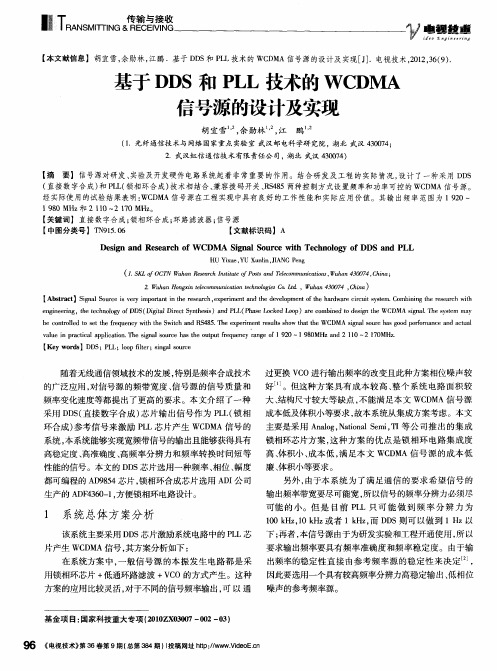

基于DDS和PLL技术的WCDMA信号源的设计及实现

嘞 翘 趱 缓

扩 i de o it i 口 fF ” r r

TA MT E IG■ I N IN&输 V T G C S I R与I F { E N

最后 , 因为本系统设计的输出信号要求具有频率转换 时间短 、 频率分 辨力高等 优点 。而 D S和 P L都具 有各 D L

z W h n ogi te m ui t n e nl i aL . W h n 304,h a u a nx l o m n a o c o g s t , ua 0 7 C i ) H n ec c i th o e C d 4 n

【 bt c】 i a Suc e pr n ite e a h epr etn e ee p etfh ad a iu sm C m ii e eer i A s at Sg l ore s r i ot tn h s r , em nad h vl m no t hr r ccis t . o bn gh s c wt r n iv y m a r e c x i t d o e w e r ty e nt r ah h

兼 容频率控 制

(

性 杖蛾

H M C27 4

): I } 1 I

转换 , 要采用较高的鉴相频率 , 从而保证 D S的频率转换速 D 度能够与 P L的频率锁定同步 , L 保证系统能够正常工作。 因此本信号源采用 1M z H 的鉴相频率 , 为了使锁相环

图 1 系统 功 能 结构 框 图

T N N8煞 s G 悲 M

嘲 魏 翰

i E nd Ⅲ o i dt r iI Tn

【 本文献信息 】胡 宜雪 , 余勋林 , 江鹏 . 于 D S P L技术 的 WC M 基 D 和 L D A信 号源的设计及 实现[] J.电视 技术 , 1 , ( ) 2 23 9 0 6

基于DDS技术的信号发生器的设计与实现

基于DDS技术的信号发生器的设计与实现DDS(Direct Digital Synthesis,直接数字合成)技术是一种通过数字方式产生任意波形信号的技术。

DDS信号发生器是一种能够产生可控频率、幅度和相位的信号的设备。

本文将介绍基于DDS技术的信号发生器的设计与实现。

首先,信号发生器的核心部件是DDS芯片。

DDS芯片是一种集成电路,能够通过数字方式产生任意波形信号。

它包含一个相位累加器和一个查找表。

相位累加器用于生成连续的相位值,而查找表则用于根据相位值输出相应的幅度值。

通过不断更新相位累加器的数值,就可以产生连续的信号。

然后,需要一个高性能的时钟源来提供DDS芯片所需的时钟信号。

一般使用晶振来提供稳定的时钟信号。

时钟信号的频率决定了DDS芯片所能产生的最高频率。

因此,选择合适的晶振对于信号发生器的性能和稳定性至关重要。

接下来,需要设计一个控制电路来控制DDS芯片的工作模式。

控制电路可以通过按键、旋钮或者电脑串口等方式与用户进行交互。

用户可以通过控制电路设定信号的频率、幅度和相位等参数。

控制电路接收用户输入的数据,并将数据传输给DDS芯片进行处理。

在实现过程中,还需要一块数模转换器(DAC)将DDS芯片输出的数字信号转换为模拟信号。

DAC负责将DDS芯片输出的数字信号转换为与之对应的模拟信号。

数模转换的精度直接影响信号发生器的性能,因此需要选择高性能的DAC。

最后,可以通过一个显示屏显示当前信号的频率、幅度和相位等参数。

显示屏可以直接与控制电路相连,通过控制电路获取当前信号的参数,并将参数显示在屏幕上。

这样用户可以直观地了解当前信号的状态。

总结起来,基于DDS技术的信号发生器的设计与实现包括选择合适的DDS芯片、时钟源和DAC,设计控制电路和显示屏,并将各部件进行连接。

通过这些步骤可以实现一个功能完善的信号发生器,能够产生任意波形信号,并提供简单的用户界面进行参数设置和显示。

基于DDS技术的通信信号源设计与实现

A 95 D 82等, 内部集成了高度 D A, / 应用更方便。

该 信号 源要产 生 的信 号形 式有 单频连 续

供电, 电平接 口芯片实现 电平转换。 采用

.

D — 7 O D A ^7

:A O A 7 D  ̄ D

A 8- D ^ ADl 2

参考 时钟 E CK RFI

的结构框架 , 能输出高信噪比的点频信号 , 支持

线性调频波形的输出和多种工作模式 ,支持并 行和 串行接 口操作 , 数据寄存器和控制寄存 器

统一编址 , 控制方便。因此 , 这里采用 A 9 5 。 D 82 以 A 95 为核心配 以外 围控制 电路和功 D 82

散 的幅度编码 , 该幅度码经过 D C变换后得到模拟的 A

笔者采用 了数字频率合成技术设计并实现 了能产

生多种信号形式的信号源 , 出信号的参数通过软件 输

灵活控制 , 具有很强的可控性 。笔者利用该信号源 , 根

据不 同通信模式特点对信号源 的输 出进行控制 ,实现

了M S F K和时延差编码通信方式 的信号输出。

1 D S的基 本 原理 D

直接数字频率合成( D ) D S是一种新的频率合成技 术. 它将先进 的数字处理理论 与方法引入频率合成领 域, 全数字化结构便于实现程控 。 采用全数字 的频率合

阶梯电压 , 再经过低通滤波器平滑后 , 即得到所需 的正

弦信号 。 相位累加器实现相位的线性变化 , 而线性调频 信号的相位不是线性变化的 ,因此需要在相位累加器

基于dds技术的信号发生器设计与实现

《基于S技术的信号发生器设计与实现》一、引言S技术(Direct Digital Synthesis)作为现代通信和信号处理领域的核心技术之一,其在信号发生器设计与实现中起着至关重要的作用。

本文将深入探讨基于S技术的信号发生器的设计和实现,通过对S技术的原理和应用进行介绍,以及具体的设计步骤和实现方法,帮助读者全面了解和掌握这一领域的知识。

二、S技术原理及应用S技术是一种通过数字方式直接合成周期性信号的技术,它可以实现频率和相位的精确控制,广泛应用于通信系统、雷达、医疗成像等领域。

基于S技术的信号发生器具有频率稳定度高、相位噪声低、频率调制灵活等特点,因此在工程和科研实践中得到了广泛的应用。

三、基于S技术的信号发生器设计步骤1. 确定需求和规格:首先需要明确设计信号发生器的需求和规格,包括输出频率范围、精度要求、调制方式等。

2. S芯片选型:根据需求和规格选择合适的S芯片,常用的芯片有AD9850、AD9851等。

3. 系统框图设计:设计信号发生器的系统框图,包括S芯片、时钟模块、滤波器、输出放大器等基本模块的连接和配置。

4. 编程控制:通过微处理器或FPGA对S芯片进行编程控制,实现频率和相位的精确调控。

5. 输出滤波和放大:设计合适的输出滤波电路和放大电路,使得输出信号符合要求并具有足够的驱动能力。

6. 调试和验证:对设计好的信号发生器进行调试和验证,检验其输出频率、相位、波形等是否符合设计要求。

四、基于S技术的信号发生器实现方法以AD9850为例,其基本工作原理是通过外部的时钟信号和串行输入的控制数据来合成输出信号。

在具体实现中,需要注意时钟信号的稳定性和精度,控制数据的传输和编程方式,输出滤波和放大电路的设计等方面。

五、个人观点和总结基于S技术的信号发生器具有很高的灵活性和精确性,在现代通信和信号处理系统中发挥着重要作用。

通过对S技术的掌握和应用,可以设计出性能优良的信号发生器,满足不同领域的需求。

dds数字通信技术原理及其应用

dds数字通信技术原理及其应用

数字化在现今的通信中占据重要地位,Direct-Sequence Spread Spectrum(DSSS)就是其中重要的数字化技术。

DSSS是一种面向移动频谱的无线数据传输技术。

它在把信号、指令或数据从源地传输至其

他位置时,可以将信号调幅瞬时之间,进行相移编码,从而避免信号

在传输过程中受到窃听和干扰,提高信号传输效率及信道质量。

DSSS将一帧信号分割为多个短帧,并根据一定的序列,使用特定的帧结构进行编码,码字长度由调制时的数字符号确定,比如2-QPSK,4ary-PSK,4-QAM等。

这里的序列就是DSSS的基础。

一个DSSS带宽可由好几条子载波组成,每个子载波可容纳十几个信号。

谱范围很宽,存储空间大,因而可以抵御噪声干扰及其他无线干扰,同时保证信号的传输效率。

Ddsss实现了可靠的无线通信,并且还支持实时数据处理,具有容错性、可扩展性、低延时性等优点,在事

务处理、数据传输、视音频传输、实时监控、远程控制等领域有广泛

的应用。

DDS原理及实现

DDS原理及实现DDS(Data Distribution Service)是一种基于发布-订阅模式的消息传递中间件,用于构建分布式系统中的数据通信。

DDS提供高效、可靠的实时数据传输,并支持灵活的数据交换模式,同时具备自适应性和可扩展性,使得它在嵌入式系统、工业控制、航空航天和军事等领域得到广泛应用。

DDS的基本原理是通过定义数据的发布和订阅,实现数据的传输和交互。

DDS系统由三个主要组件组成:发布者(Publisher)、订阅者(Subscriber)和中间件(Middleware)。

发布者负责将数据发布到中间件,订阅者从中间件中获取订阅的数据。

中间件负责实现数据的传输和分发。

在DDS系统中,数据传输是基于主题(Topic)的。

主题定义了一组相关数据的类型和结构,发布者和订阅者通过订阅特定的主题来进行数据交换。

DDS支持多种数据交换模式,包括点对点模式、发布-订阅模式和请求-回应模式。

发布者可以通过发布主题将数据发送到中间件,订阅者可以通过订阅主题接收数据。

DDS中间件会根据订阅者的需求和负载情况,选择合适的数据传输方式和频率,以保证数据的实时性和可靠性。

DDS实现数据传输的方式主要有两种:直接通信和间接通信。

直接通信是指发布者和订阅者直接进行数据传输,中间件只提供基础的通信功能;间接通信是指发布者和订阅者通过中间件进行数据交互,中间件负责数据的传输和分发。

DDS支持两种方式的混合使用,可以根据系统需求选择合适的通信方式。

DDS还提供了一些高级特性,增强系统的灵活性和可靠性。

其中包括:1.数据过滤:通过定义过滤条件,发布者和订阅者可以选择接收特定的数据;2.可靠性保证:DDS提供了多种机制,确保数据的可靠传输,包括故障检测和恢复、数据重传和顺序保证等;3.优先级控制:DDS支持对数据进行优先级排序和传输控制,保证关键数据的及时处理;4.发布者和订阅者的自适应:DDS可以根据系统负载和性能情况,自动调整数据发布和订阅的速率,以适应实时需求和资源约束。

基于DDS技术的信号发生器的设计与实现

唐山学院毕业设计设计题目:基于DDS技术的信号发生器的设计与实现系别:信息工程系班级:姓名:指导教师:2012年6月10 日基于DDS技术的信号发生器的设计与实现摘要DDS是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。

与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。

本设计采用单片机为核心处理器,利用键盘输入信号的参数,控制DDS的AD9850模块产生信号,信号的参数在LCD1602上显示,完成正弦信号和方波信号的输出,用示波器输出验证。

DDS是一种全数字化的频率合成器,由相位累加器、波形ROM、D/A转换器和低通滤波器构成。

时钟频率给定后,输出信号的频率取决于频率控制字,频率分辨率取决于累加器位数,相位分辨率取决于ROM的地址线位数,幅度量化噪声取决于ROM的数据位字长和D/A转换器位数。

与传统的频率合成方法相比,DDS合成信号具有频率切换时间短、频率分辨率高、相位变化连续等诸多优点。

使用单片机灵活的控制能力与AD9850的高性能、高集成度相结合,可以克服传统DDS设计中的不足,从而设计开发出性能优良的信号发生器系统。

关键词:单片机直接数字频率合成AD9850 DDSDesign and Implementation of the SignalGenerator Based on DDS TechnologyAbstractDDS is Direct Digital frequency Synthesizer (Direct Digital Synthesizer) English abbreviations. Compared with the traditional frequency synthesizer, with low cost, DDS low power consumption, high resolution and fast converting speed time and so on, widely used in telecommunications and electronic instruments field, is to realize equipment full digital a key technology.This design uses the single chip processor as the core, using a keyboard input signal parameters, control of DDS AD9850 module produce signals, the signal parameters in LCD1602 show that the complete sine signal and square wave signal output, the output with an oscilloscope validation.DDS is A full digital frequency synthesizer, by phase accumulators, waveform ROM, D/A converter and low pass filter composition. The clock frequency after A given, the output depends on the frequency of the signal frequency control word, the frequency resolution depends on accumulators digits, phase resolution depends on the ROM address line digits, amplitude quantization noise depends on the ROM data A word length and D/A converter digits. And the frequency of the traditional method than the synthesis, DDS synthesis signal has a frequency switching frequency of short time, high resolution and continuous phase changes, and many other advantages. Using single chip microcomputer control of the flexible ability and high performance, high level of integration of the AD9850 combination, can overcome the disadvantage of the traditional DDS design, to design the developed good performance of signal generator system.Key word:MCU; direct digital frequency synthesis;AD9850;DDS目录1 引言 (1)2DDS概要 (2)2.1DDS介绍 (2)2.1.1 DDS结构 (2)2.1.2典型的DDS函数发生器 (3)2.2DDS数学原理 (5)3 总体设计方案 (8)3.1系统设计原理 (8)3.2总体设计框图 (8)4 系统硬件模块的组成 (9)4.1单片机控制模块 (9)4.1.1 STC89C52主要性能 (9)4.1.2 STC89C52功能特性描述 (9)4.1.3 时钟电路 (11)4.1.4复位电路 (11)4.2AD9850模块 (12)4.2.1 AD9850简介 (12)4.2.2 AD9850的控制字与控制时序 (14)4.2.3单片机与AD9850的接口 (15)4.3滤波电路设计 (15)4.4键盘控制模块 (16)4.5LCD显示模块 (16)4.5.1液晶显示器显示原理 (16)4.5.2 1602LCD引脚与时序 (17)4.6A/D转换模块 (20)5 软件设计与调试 (21)5.1程序流程图 (21)5.2软件调试 (22)5.2.1 keil编程工具介绍 (22)5.2.2 STC-ISP下载工具介绍 (23)6 硬件电路制作 (24)6.1原理图的绘制 (24)6.2电路实现的基本步骤 (24)6.3硬件测试波形图 (25)7 结论 (27)谢辞 .............................................................................................. 错误!未定义书签。

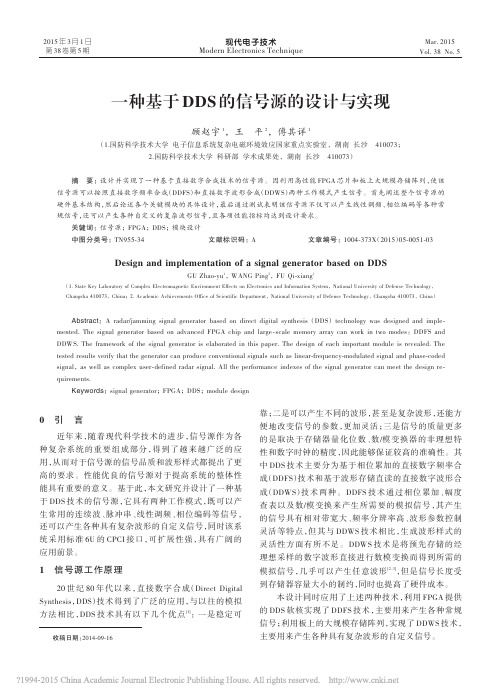

一种基于DDS的信号源的设计与实现_顾赵宇

本信号源基于标准 CPCI 接口,具有 DDFS 和 DDWS 两 种 工 作 模 式 ,由 上 位 机 软 件 进 行 选 择 ,系 统 结 构 图 如 图 1 所示。

图 1 信号源总体结构框图

在工作模式一时,利用计算机软件计算并通过串口 下 发 信 号 参 数 ,FPGA 对 串 口 下 发 的 参 数 进 行 解 析、存 储、运 算 后 得 到 波 形 控 制 字,然 后 调 用 DDS 软 核,通 过 相 位 累 加 、幅 度 查 表 得 到 需 要 的 数 字 波 形 ,最 后 通 过 DAC 转换成模拟波形经过放大滤波输出 。在工作模 式 二 时 ,利 用 计 算 机 软 件 直 接 下 发 数 据,FPGA 将 数 据 存储到板上的 SDRAM 中,然后将 SDRAM 中的数据读取 出来直接送到 DAC 转换成模拟信号。

2015 年 3 月 1 日 第 38 卷第 5 期

现代电子技术 Modern Electronics Technique

Mar. 2015 Vol. 38 No. 5

51

一种基于 DDS 的信号源的设计与实现

顾赵宇 1,王 平ห้องสมุดไป่ตู้2,傅其详 1

(1.国防科学技术大学 电子信息系统复杂电磁环境效应国家重点实验室,湖南 长沙 2.国防科学技术大学 科研部 学术成果处,湖南 长沙 410073)

410073;

摘 要:设计并实现了一种基于直接数字合成技术的信号源。因利用高性能 FPGA 芯片和板上大规模存储阵列,使该

信号源可以按照直接数字频率合成(DDFS)和直接数字波形合成(DDWS)两种工作模式产生信号。首先阐述整个信号源的

硬件基本结构,然后论述各个关键模块的具体设计,最后通过测试表明该信号源不仅可以产生线性调频、相位编码等各种常

基于DDS中间件的数据分发平台的设计与实现

际需求,并为用户提供独立的服务对于不同的服务而言,这些服务 关注的业务功能通常是单一的,也就是不同服务之间可以实现松散 耦合。核心服务主要包括配变负载告警、电网负载监控等。

可以借助于 API 来实现服务的调用,并以统一的方式在配置中 心中对其进行管理。通过使用手机 APP 和 Web 前端页面,可以直 接调用这些服务,并在获取数据以后对数据进行分析计算,然后直 接显示最终的计算结果。

3 软件实现

数据分发平台基于国产中标麒麟系统、RTI DDS5.1.0,采用模 块化设计思想,将软件分为主控模块、串口通讯模块、UDP 通讯模块、 DDS 通讯模块、数据处理模块。各软件模块间接口关系如图 3 所示。

3.1 主控模块

主控模块是数据分发系统的控制中心,主要完成初始化并管理 系统内的软硬件资源、创建并启动各任务和信号量消息队列、执行 系统时钟任务等。当软件启动 / 关闭时自动加载 / 卸载主控模块。

摘 要:本文简要介绍了 DDS 中间件,详细分析数据分发平台的需求,确定了采用以 DDS 混合 udp 的通讯架构,在软件层面上对各个 模块进行详细的功能讲解和代码实例 , 最后对平台进行功能、性能的测试,测试表明,本设计能有效满足系统需求。

关键词:DDS 中间件;服务质量策略;数据分发平台

1 引言

3.5 数据处理模块

46

电子技术与软件工程 Electronic Technology & Software Engineering

软件开发与应用 Software Development And Application

图 4:性能测试

数据处理模块对发送到分发平台的数据报文进行检查校验,减 少错误数据包向外发送,对确认无误的数据包进行相应的处理。

一种基于DDS技术的动态数据通信方法及设备[发明专利]

![一种基于DDS技术的动态数据通信方法及设备[发明专利]](https://img.taocdn.com/s3/m/75cfcdd7f71fb7360b4c2e3f5727a5e9856a277a.png)

专利名称:一种基于DDS技术的动态数据通信方法及设备专利类型:发明专利

发明人:唐宏冰,刘泽石,王兴龙,闫传博,于津

申请号:CN201910999675.4

申请日:20191021

公开号:CN110740182B

公开日:

20220506

专利内容由知识产权出版社提供

摘要:本申请属于实时嵌入式网络通信领域,特别涉及一种基于DDS技术的动态数据通信方法及设备。

方法包括:步骤一:根据DDS通信过程中动态产生的主题ID,生成通信通道;步骤二:根据主题路由表判断通信数据是否需要路由,并通过所述通信通道进行所述通信数据的传输;步骤三:通信结束后,释放主题内存资源,更新所述主题路由表。

本申请的基于DDS技术的动态数据通信方法,用户无须配置通信过程中的主题,即可适应各节点的点对点通信要求;通信的各节点只收到控制信息,不会收到与自身节点无关的信息,避免了冗余信息,同时保证了数据的安全。

申请人:中国航空工业集团公司沈阳飞机设计研究所

地址:110035 辽宁省沈阳市皇姑区塔湾街40号

国籍:CN

更多信息请下载全文后查看。

基于DDS的无线数据传输系统设计与实现

基于DDS的无线数据传输系统设计与实现

DDS 技术是近几年来迅速发展的频率合成技术,它采用全数字化的技术,具有集成度高、体积小、相对带宽宽、频率分辨率高、跳频时间短、相位连

续性好、可以宽带正交输出、可以外加调制的优点,并方便与控制器接口构

成智能化的频率源。

由于基准时钟的频率一般固定,因此相位累加器的位数

决定了频率分辨率,位数越多,分辨率越高。

基于DDS 诸多优点,本系统采用DDS 技术来实现数字调制功能,充分发挥DDS 的优势,使系统结构简单、功能强大。

1 硬件实现及工作原理

本系统为一套无线数据传输系统,硬件电路分为发射机电路和接收机电路

两部分。

1.1 发射机电路

如图1 所示,发射机硬件电路主要由控制器、调制电路、高频功率放大器、天线、显示电路与电源部分组成。

图1 发射机组成图

控制器以TI 公司高性能混合信号处理器MSP430F169 为核心,完成对DDS 、键盘、LCD 显示器的控制和信息处理的功能。

MSP430F169 为16 bit 具有精简指令集的超低功耗混合信号处理器(Mixed Signal Processor),采用1.8 V~3.6 V 电源电压,在1 MHz 的时钟条件下运行时,芯片的电流在200 μA~400μA,时钟关断模式的最低功耗只有0.2 μA,在8 MHz 晶体驱动下指令周期为125 ns。

且MSP430F169 具有丰富的片上外围模块,如看门狗、模拟比较器、定时。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

本系统为一套无线数据传输系统, 硬件电路分为发射机电路和接收机电路两部分。

1.1 发射机电路

,发射机硬件电路主要由控制器、调制电路、高频功率放大器、天线、显示电路与电源部分组成。

图1 发射机组成图

控制器以TI 公司高性能混合信号处理器MSP430F169为核心, 完成对DDS 、键盘、LCD 显示器的控制和信息处理的功能。MSP430F169 为16 bit 具有精简指令集的超低功耗混合信号处理器(Mixed Signal Processor) , 采用1.8 V~3.6 V 电源电压, 在1 MHz 的时钟条件下运行时,芯片的电流在200 μA~400 μA, 时钟关断模式的最低功耗只有0.2 μA,在8 MHz 晶体驱动下指令周期为125 ns。

接收机数据处理器同样采用MSP430F169 , 显示器采用与发射机相同的LCM12864 。由于接收机部分与发射机相比功耗低, 故接收机电源部分采用两节5 号干电池串联供电。

2 系统软件的实现

2.1 发射机的软件设计

发射机上电后, 首先对系统进行初始化, 包括对控制器本身的端口配置、片内外设的配置, 以及外部的AD9854[ 6]、PS2 键盘和显示器等部件的初始化。初始化结束后系统进入休眠模式, 直到被外部键盘产生的中断唤醒。然后根据得到的按键键码进行相应处理。为了让AD9854 产生2FSK 信号, 需进行如下的初始化过程:S/PSELECT 置1 或置0 以决定输入数据是并行还是串行。1为并行,0 为串行; 本系统采用串行接口, 在SCLK 信号控制下从并行输入口D0~D1 写入48 bit 并行寄存器, 或在SCLK 控制下从串行输入口SDATA 写入48 b储有3 幅图片) 。

AD9854 支持10 MHz 串行通信方式和100 MHz 并行通信方式, 本系统采用串行数据输入方式。AD9854 内置4~20 倍频的PLL, 外部较低频率的参考时钟可通过倍频后得到300 MHz 的系统时钟, 这样就避免了设计高频参考时钟的难度, 降低了高频时钟干扰。AD9854 参考时钟的输入有单端输入和差分输入两种方式, 为了使电路简单, 本设计选用单端输入方式。外部20 MHz 有源晶振输出经PLL 电路15 倍频到300 MHz 后作为系统时钟。

且MSP430F169 具有丰富的片上外围模块, 如看门狗、模拟比较器、定时器、串口、硬件乘法器等。在本系统中,MSP430F169 工作在3.3 V 电压、8 MHz 主频下。

调制电路以ADI 公司单片DDS 芯片AD9854 为核心。该芯片最高系统时钟为300 MHz , 理论输出信号频率范围为直流到150 MHz,最高并行编程速率为100 MHz,采用3.3 V 单电源供电, 与上述控制器芯片匹配, 无需加电平转换电路,从而实现控制器与调制器的无缝接口。

(2) 频率稳定度: 在单片机复位的前提下, 用频率计每隔2 min 测一次AD9854 的输出频率,共测5 次,如表1所示。根据测试结果计算:

表1 AD9854 输出频率测量值

频率稳定度=最大频率偏差/中心频率=(30.000 068-29.999 981)÷30.000 024=0.000 087÷30.000 024=2.9×10-6(3) 发射功率: 在发射功率级末端接50 Ω 假负载,用100 MHz 数字示波器测得发射信号的输出电压峰峰值VP-P, 据公式P=V2P-P/8RL, 得到发射功率值, 实验测得VP-P=2.98 V,P=V2P-P/8RL=22.2 mW。

图3 发射机流程图

2.2 接收机的软件设计

接收机不需要区分接收到的是英文字符还是汉字,故软件设计相对发射机来说较容易。同样, 开始对信号处理器以及外设进行初始化, 使其工作在等待信息接收状态, 此时, 只有接收机射频部分电路工作, 其他部件处于休眠模式。当接收机检查到有信息到来时, 通过中断唤醒控制器, 控制器再唤醒其他外设进行数据接收和处理。接收到的信息经信号处理器判断, 如果为字符( 包括英文字符和汉字) , 则控制LCD 进入字符模式, 进行字符的显示; 如果为图片, 则控制LCD 进入图片模式, 进行图片显示。接收机的软件流程。

(4) 传输速率: 发射机、接收机在通信距离为10 m 的情况下, 分别以1.2 kb/s 、9.6 kb/s 、57.6 kb/s 、115.2 kb/s的波特率传送5 次20 个汉字, 汉字错误率均为零。

(5) 图形传送功能: 发射机、接收机。发射机调用机内自带的三幅图形( 分别为公鸡、小兔及西工大校徽) 以点阵的形式传送, 接收机能够不失真接收, 说明本系统具有图形的点阵传送功能。

本系统可以简单高效地进行无线数据传输, 是实现无线通信的一种简单可行的设计方案。经过系统测试,系统技术指标令人满意, 工作可靠。另外, 由于本系统采用DDS 来实现信号调制, 故可以比较容易地改变调制信号频率, 为实现跳频通信提供了方便。

基于DDS的无线数据传输系统设计与实现

DDS 技术是近几年来迅速发展的频率合成技术, 它采用全数字化的技术, 具有集成度高、体积小、相对带宽宽、频率分辨率高、跳频时间短、相位连续性好、可以宽带正交输出、可以外加调制的优点, 并方便与控制器接口构成智能化的频率源。由于基准时钟的频率一般固定, 因此相位累加器的位数决定了频率分辨率, 位数越多, 分辨率越高。基于DDS 诸多优点, 本系统采用DDS技术来实现数字调制功能, 充分发挥DDS 的优势, 使系统结构简单、功能强大。

1.2 接收机电路

接收机硬件电路由解调电路、数据处理器、显示电路及电源部分组成, 接收机框图。

图2 接收机组成图

解调器以飞利浦专用FSK 解调芯SA639DH 为核心部件。它具有灵敏度高、动态范围大、传输速率快、稳定性好等特点。天线接收到的信号经输入回路取出的2FSK信号与本振信号同时送入乘法器进行混频, 再经一级带通滤波器滤除高频分量取其下变频到中频, 然后进行中频放大后经二级带通滤波送入限幅放大器进行限幅放大。限幅放大后的信号被分成两路, 一路直接送入乘法器, 另一路经移相网络移相90° 产生调相调频波再送乘法器, 两路信号进行相位比较, 乘法器输出的信号经低通滤波器取出原调制信号, 然后再把该信号送入比较器进行整形后送信号处理器进行处理。

图4 接收机流程图

3 系统测试结果

(1) 载波中心频率:发射机在2FSK 模式时,1 和0 所对应的两个频率分别为fH=30.003 000 MHz 和fL=29.997 000 MHz,系统在空闲时发射频率为30.000 000 MHz , 故选取频率为30.000 000 MHz 为中心频率。

滤波器采用由3 个电感和7 个电容构成的七阶椭圆滤波器, 因为AD9854 的最高工作频率为300 MHz , 而DDS输出最高频率为系统工作频率的40%左右, 所以本方案中滤波器的截止频率设计为120 MHz, 有效滤除了高频干扰,使输出信号较为平滑。

高频功率放大器工作在丙类方式, 能够实现较高的效率。显示器采用LCM128 128×64 点字符点阵液晶显示器, 用来完成人机交互界面和信息的显示功能。电源部分采用LM2576-3.3 三端稳压片, 能够提供最高3 A 的电流输出, 完全满足本系统的要求。同时为了防止AD9854工作时对电源造成干扰, 电路设计采用了大量的滤波电容, 且对数字电源和模拟电源作了很好的隔离, 以防止数字电源对模拟电源的串扰。