新手学版图—理解版图的层

pcb各层解释

pcb各层解释第一篇:pcb各层解释Mechnical: 一般多指板型机械加工尺寸标注层Keepoutlayer: 定义不能走线、打穿孔(via)或摆零件的区域。

这几个限制可以独立分开定义。

Topoverlay: 无法从字面得知其意义。

多提供些讯息来进一步讨论。

Bottomoverlay: 无法从字面得知其意义。

可多提供些讯息来进一步讨论。

Toppaste: 顶层需要露出铜皮上锡膏的部分。

Bottompaste: 底层需要露出铜皮上锡膏的部分。

Topsolder: 应指顶层阻焊层,避免在制造过程中或将来维修时可能不小心的短路Bottomsolder: 应指底层阻焊层。

Drillguide: 可能是不同孔径大小,对应的符号,个数的一个表。

Drilldrawing: 指孔位图,各个不同的孔径会有一个对应的符号。

Multilayer: 应该没有单独这一层,能指多层板,针对单面板和双面板而言。

拓展能力!第二篇:PCB电路板线路板加工,单面电路板,双面电路板,PCB电路板,PCB电路板厂,PCB电路板厂家-梅州市创福达电子有限公司,是一家专业生产各种高精密单,双面及多层印刷PCB电路板,致力于快速高密度多层板、特种PCB电路板的研发生产制造,为用户提供PCB线路板技术支持与服务。

创福达电路板厂位于梅州市丰顺县工业区,占地面积4000平米,员工100人左右,月生产PCB线路板能力20000平米。

创福达线路板厂家由多名PCB电路板业内人士创建,培养了一批制造经验丰富的员工,高素质的管理团队,先进的设备仪器和完善的质保体系,使我们不断提升在PCB电路板行业中的地位及在客户心中的良好形象。

工厂自 2006 年创建以来,规模迅速发展,拥有 4000 余平方米的厂房,100多名员工。

产品于2006年取得ISO9001、SGS认证,2009年一次取得欧盟ROHS无铅产品认证和美国UL认证。

引进整套先进的生产设备,培养了一支从事印刷电路板加工的专业队伍,健全了从市场开发,工程设计,到加工生产的一条龙服务。

PCB的层的详细解释

PCB的层:a.信号层(Signal Layers): 信号层包括Top Layer、Bottom Layer、Mid Layer 1……30。

这些层都是具有电气连接的层,也就是实际的铜层。

中间层是指用于布线的中间板层,该层中布的是导线。

b.内层(Internal Plane): Internal Plane 1……16,这些层一般连接到地和电源上,成为电源层和地层,也具有电气连接作用,也是实际的铜层,但该层一般情况下不布线,是由整片铜膜构成。

c.丝印层(Silkscreen Overlay): 包括顶层丝印层(Top overlay)和底层丝印层Bottom overlay) 。

定义顶层和底层的丝印字符,就是一般在阻焊层之上印的一些文字符号,比如元件名称、元件符号、元件管脚和版权等,方便以后的电路焊接和查错等。

d.锡膏层(Paste Mask): 包括顶层锡膏层(Top paste) 和底层锡膏层(Bottom paste) ,指我们可以看到的露在外面的表面贴装焊盘,也就是在焊接前需要涂焊膏的部分。

所以,这一层在焊盘进行热风整平和制作焊接钢网时也有用。

e.阻焊层(Solder Mask): 包括顶层阻焊层(Top solder)和底层阻焊层(Bottom solder) ,其作用与锡膏层相反,指的是要盖绿油的层。

该层不粘焊锡,防止在焊接时相邻焊接点的多余焊锡短路。

阻焊层将铜膜导线覆盖住,防铜膜过快在空气中氧化,但是在焊点处留出位置,并不覆盖焊点。

f.机械层(Mechanical Layers): 最多可选择 16 层机械加工层。

设计双面板只需要使用默认选项 Mechanical Layer 1。

g.禁布层(Keep Out Layer) : 定义布线层的边界。

定义了禁止布线层后,在以后的布线过程中,具有电气特性的布线不可以超出禁止布线层的边界。

h.钻孔层(Drill Layer): 包括钻孔引导层(Drill guide) 和钻孔数据层(Drill drawing) ,是钻孔的数据。

altiumdesignerPCB各层含义教学内容

Protel 99se 及 DXP 中 PCB 各层的含义详解1 Signal layer(信号层)信号层主要用于布置电路板上的导线。

Protel 99 SE提供了 32个信号层,包括Top layer顶层),Bottom layer(底层)和 30个 MidLayer(中间层)。

2 Internal plane layer(内部电源/接地层)Protel 99 SE提供了 16个内部电源层/接地层.该类型的层仅用于多层板,主要用于布置电源线和接地线 .我们称双层板,四层板,六层板,一般指信号层和内部电源 /接地层的数目。

3 Mechanical layer(机械层)Protel 99 SE提供了 16个机械层,它一般用于设置电路板的外形尺寸,数据标记,对齐标记,装配说明以及其它的机械信息。

这些信息因设计公司或 PCB 制造厂家的要求而有所不同。

执行菜单命令Design|Mechanical Layer能为电路板设置更多的机械层。

另外,机械层可以附加在其它层上一起输出显示。

4 Solder mask layer(阻焊层)在焊盘以外的各部位涂覆一层涂料,如防焊漆,用于阻止这些部位上锡。

阻焊层用于在设计过程中匹配焊盘,是自动产生的。

Protel 99 SE 提供了 Top Solder顶层)和Bottom Solder(底层)两个阻焊层。

5 Paste mask layer(锡膏防护层,SMD贴片层)它和阻焊层的作用相似,不同的是在机器焊接时对应的表面粘贴式元件的焊盘。

Protel 99 SE提供了 Top Paste顶层)和Bottom Paste(底层)两个锡膏防护层。

主要针对PCB板上的SMD元件。

如果板全部放置的是Dip(通孔)元件,这一层就不用输出Gerber文件了。

在将SMD元件贴PCB板上以前,必须在每一个SMD焊盘上先涂上锡膏,在涂锡用的钢网就一定需要这个Paste Mask文件, 菲林胶片才可以加工出来。

理解版图的层

新手学版图—理解版图的层版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS反相器为例,基本原理很简单,当输入高电平时,NMOS导通,输出端连接到地;当输入端为低电平时,PMOS导通,输出端连接到VDD。

版图的目的就是要以图形的方式形成这两个MOS管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POLY自对准形成MOS管子,输入为POLY,输出为金属连线,连接点为CONTACT。

首先创建新的cell view背景代表P型衬底,材料为Si-100 电阻率约5-10Ωcm,清洗后生长约200Å氧化层,再以LPCVD(低压化学气相沉积)沉积氮化硅约800A。

Wafer厚度大约为750um,但最后打磨贴片后的厚度大约只有约250um。

(10000A=1um)氧化层的应用大致可分为:屏蔽、遮蔽、场区及局部绝缘、衬垫、缺陷去除、栅介电层、浅沟槽阻挡,厚度依次约为200A、5000A、3000-5000A、100-200A、<1000A、30-120A、100-200A。

氮化物一般较为致密,所以可以用来隔离、阻挡,以及CMP 的停止层。

涂布光阻、曝光、显影,以氮化物等离子体干法刻蚀去除氮化硅,剥离光阻(以下将省略一些层的去除过程)。

版图Active层将定位出有源区,非有源区将通过LOCOS(硅的局部氧化)生长场氧化层,厚度大约3000-10000A。

不过因该过程存在鸟嘴效应及表面平坦度问题,90年代后已经由STI(淺沟槽绝缘)所取代。

版图P-well层定位P-well区域,在这一区域离子植入B+/225KeV/3x10^13cm^-2。

用版图N-well层定位N-well区域,离子植入P+/600KeV/2x10^13cm^-2。

第3章工艺基础及版图的层

第三章 集成电路工艺基础及版图设计

为了是SPICE能够精确地预测电路的复杂工 作过程,我们不仅需要设计规范和初始原理图, 还必须建立相关电路元件的数学描述。

第三章 集成电路工艺基础及版图设计

CMOS反相器的设计

在一定的工艺条件下,反相器的设计,关键是对晶体管的 尺寸(W/L)的设计,并由确定的沟道长度,获得沟道宽度 的具体数值。

多晶硅(Uin)

金属(Uout )

金属(UDD)

(b)

P+

N-Si

N+

P阱

薄 氧 化 层 (栅 氧 化 层 )

图3 - 6 反向器版图及结构剖面图 (a) 版图; (b) 结构剖面图

第三章 集成电路工艺基础及版图设计

硅晶圆 确定晶体管的基底区域 形成并绘制多晶硅栅的图案

确定有源区 为接触孔开孔(对每个互连层都如此操作) 确定互连层(对每个互连层都如此操作)

第三章 集成电路工艺基础及版图设计

3.3.4器件尺寸设计

栅和有源区的重叠确定了器件的尺寸,重叠区之外的区 域对器件的尺寸没有影响。

如何根据电路性能要求设计器件的尺寸?要设计多大的 重叠区?

第三章 集成电路工艺基础及版图设计

两个重要的尺寸参数——晶体管的长度和宽度

就版图而言,晶体管的长度是源极和漏极之间的距 离;就晶体管性能而言,晶体管的长度是电子所必须 移动的距离;就制造而言,晶体管的长度是多晶硅 (多晶)能够可靠制造的最窄可能长度。

第三章 集成电路工艺基础及版图设计

图3 - 5 反向器

第三章 集成电路工艺基础及版图设计

掩膜版1: 用来规定P阱的形状、 大小及位置。 掩膜版2: 用于确定薄氧化层。 掩膜版3: 用来刻蚀多晶硅, 形成多晶硅栅极及 多晶硅互连线。 掩膜版4: 确定需要进行离子注入形成P+的区域。

PCB板各层含义

转载——PCB 各层含义PCB 各层含义一、1 Signal layer(信号层信号层主要用于布置电路板上的导线.Protel 99 SE 提供了32个信号层, 包括Top layer(顶层,Bottom layer(底层和30个MidLayer(中间层.2 Internal plane layer(内部电源/接地层Protel 99 SE提供了16个内部电源层/接地层. 该类型的层仅用于多层板, 主要用于布置电源线和接地线. 我们称双层板, 四层板, 六层板, 一般指信号层和内部电源/接地层的数目.3 Mechanical layer(机械层Protel 99 SE提供了16个机械层, 它一般用于设置电路板的外形尺寸, 数据标记, 对齐标记, 装配说明以及其它的机械信息. 这些信息因设计公司或PCB 制造厂家的要求而有所不同. 执行菜单命令Design|Mechanical Layer 能为电路板设置更多的机械层. 另外, 机械层可以附加在其它层上一起输出显示.4 Solder mask layer(阻焊层在焊盘以外的各部位涂覆一层涂料, 如防焊漆, 用于阻止这些部位上锡. 阻焊层用于在设计过程中匹配焊盘, 是自动产生的.Protel 99 SE提供了Top Solder(顶层和Bottom Solder(底层两个阻焊层.5 Paste mask layer(锡膏防护层它和阻焊层的作用相似, 不同的是在机器焊接时对应的表面粘贴式元件的焊盘.Protel 99 SE 提供了Top Paste(顶层和Bottom Paste(底层两个锡膏防护层.6 Keep out layer(禁止布线层用于定义在电路板上能够有效放置元件和布线的区域. 在该层绘制一个封闭区域作为布线有效区, 在该区域外是不能自动布局和布线的.7 Silkscreen layer(丝印层丝印层主要用于放置印制信息, 如元件的轮廓和标注, 各种注释字符等.Protel 99 SE提供了Top Overlay和Bottom Overlay两个丝印层. 一般, 各种标注字符都在顶层丝印层, 底层丝印层可关闭.8 Multi layer(多层电路板上焊盘和穿透式过孔要穿透整个电路板, 与不同的导电图形层建立电气连接关系, 因此系统专门设置了一个抽象的层, 多层. 一般, 焊盘与过孔都要设置在多层上, 如果关闭此层, 焊盘与过孔就无法显示出来.9 Drill layer(钻孔层钻孔层提供电路板制造过程中的钻孔信息(如焊盘, 过孔就需要钻孔.Protel 99 SE提供了Drill gride(钻孔指示图和Drill drawing(钻孔图两个钻孔层.多层板顶层Top Layer(信号层底层Bottom Layer(信号层中间层MidLayer 1(信号层中间层MidLayer 14(信号层Mechanical 1(机械层Mechanical 4(机械层顶层丝印层TopOverlay底层丝印层BottomOverlay二、PCB 的各层定义及描述:1、 TOP LAYER(顶层布线层):设计为顶层铜箔走线。

PCB各层含义

toplayer ——顶层布线层,bottomlayer ——底层布线层,具有电气特性的走线。

就是线路板上连接各个元器件引脚的连线。

mechanical ——机械层,是定义整个PCB板的外观的,其实我们在说机械层的时候就是指整个PCB板的外形结构。

keepoutlayer ——禁止布线层,禁止布线层是定义我们在布电气特性的铜时的边界,也就是说我们先定义了禁止布线层后,我们在以后的布线过程中,所布的具有电气特性的线是不可能超出禁止布线层的边界。

topoverlay ——顶层丝印层,bottomoverlay ——底层丝印层,定义顶层和底层的丝印字符,就是一般我们在PCB板上看到的元件编号和一些字符。

toppaste ——顶层焊盘层,bottompaste ——底层焊盘层,顶层和底层焊盘层,它就是指我们可以看到的贴片元件的焊盘。

topsolder ——顶层阻焊层,bottomsolder ——底层阻焊层,由于PCB板是要默认上绿油的,用这两个层画线的地方就会开个“天窗",不上绿油。

在一些需要大电流流通的地方可以使用,以便另外加焊锡。

TopLayer(顶层)画出来的线条是红色,就是一般双面板的上面一层,单面板就用不到这层。

BottomLayer(底层)画出来的线条是蓝色,就是单面板上面的线路这层。

MidLayer1(中间层1)这个是第一层中间层,好像有30层,一般设计人员用不到,你先不用管他,多面板时候用的。

默认在99SE中不显示,也用不到。

Mechanical Layers(机械层)(紫红色)用于标记尺寸,板子说明,在PCB抄板加工的时候是忽略的,也就是板子做出来是看不出来的,简单点式注释的意思。

Top Overlay(顶层丝印层)(黄色)就是板子正面的字符,对应TopLayer(顶层)单面板就用到这层字符就可以了,Bottom Overlay(底层丝印层)(褐色)对应BottomLayer(底层)就是板子背面的字符,双面板时候用到以上两层字符。

Altium Desinger 学习笔记-层的概念

Altium Desinger中有

1.信号层(最多包括32个)Signal Layers:顶层Top Layer,中间层MidLayer1 to Midlayer30,底层Bottom Layer

2.Internal Planes:电源层、可以提供电势参考平面,可以用过孔链接

3.丝印层Silkscreen Layers:顶部和底部丝印层,放置元器件的轮廓。

4.机械层Mechanical Layers (最多16个、名字可以由用户自定义):包括生产和组装的一些信息,如对齐,标注等。

5.阻焊层Solder Mask:阻止焊锡沾上。

除元器件和过孔以外的所有部分都有组焊层。

6.阻锡层Paste Masks:放置锡料。

主要在表贴元器件中使用。

7.钻孔绘制层Drill Drwing:

8.Drill Guide:

9.Keep out layer:定义元器件和导线放置的位置,只能放置在区域内。

对所有的信号层有效。

10.多层Multi-layer:在所有的层中都要出现的某些元件。

altiumdesignerPCB各层含义教学内容

Protel 99se 及 DXP 中 PCB 各层的含义详解1 Signal layer(信号层)信号层主要用于布置电路板上的导线。

Protel 99 SE提供了 32个信号层,包括Top layer顶层),Bottom layer(底层)和 30个 MidLayer(中间层)。

2 Internal plane layer(内部电源/接地层)Protel 99 SE提供了 16个内部电源层/接地层.该类型的层仅用于多层板,主要用于布置电源线和接地线 .我们称双层板,四层板,六层板,一般指信号层和内部电源 /接地层的数目。

3 Mechanical layer(机械层)Protel 99 SE提供了 16个机械层,它一般用于设置电路板的外形尺寸,数据标记,对齐标记,装配说明以及其它的机械信息。

这些信息因设计公司或 PCB 制造厂家的要求而有所不同。

执行菜单命令Design|Mechanical Layer能为电路板设置更多的机械层。

另外,机械层可以附加在其它层上一起输出显示。

4 Solder mask layer(阻焊层)在焊盘以外的各部位涂覆一层涂料,如防焊漆,用于阻止这些部位上锡。

阻焊层用于在设计过程中匹配焊盘,是自动产生的。

Protel 99 SE 提供了 Top Solder顶层)和Bottom Solder(底层)两个阻焊层。

5 Paste mask layer(锡膏防护层,SMD贴片层)它和阻焊层的作用相似,不同的是在机器焊接时对应的表面粘贴式元件的焊盘。

Protel 99 SE提供了 Top Paste顶层)和Bottom Paste(底层)两个锡膏防护层。

主要针对PCB板上的SMD元件。

如果板全部放置的是Dip(通孔)元件,这一层就不用输出Gerber文件了。

在将SMD元件贴PCB板上以前,必须在每一个SMD焊盘上先涂上锡膏,在涂锡用的钢网就一定需要这个Paste Mask文件, 菲林胶片才可以加工出来。

解析AutoCAD中层的概念

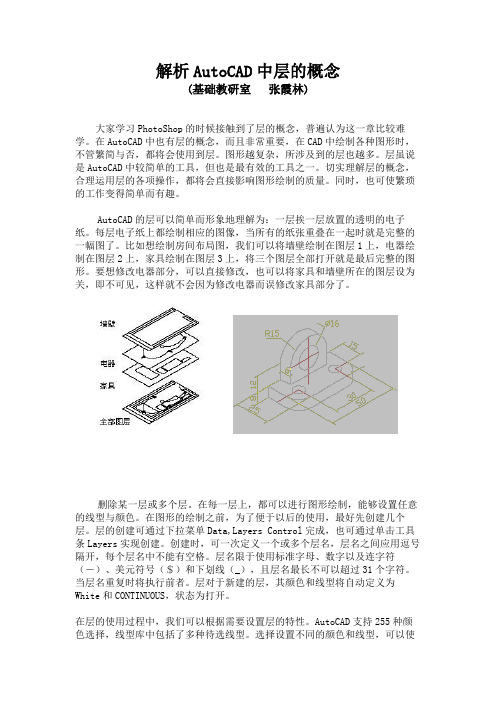

解析AutoCAD中层的概念(基础教研室张霞林)大家学习PhotoShop的时候接触到了层的概念,普遍认为这一章比较难学。

在AutoCAD中也有层的概念,而且非常重要,在CAD中绘制各种图形时,不管繁简与否,都将会使用到层。

图形越复杂,所涉及到的层也越多。

层虽说是AutoCAD中较简单的工具,但也是最有效的工具之一。

切实理解层的概念,合理运用层的各项操作,都将会直接影响图形绘制的质量。

同时,也可使繁琐的工作变得简单而有趣。

AutoCAD的层可以简单而形象地理解为:一层挨一层放置的透明的电子纸。

每层电子纸上都绘制相应的图像,当所有的纸张重叠在一起时就是完整的一幅图了。

比如想绘制房间布局图,我们可以将墙壁绘制在图层1上,电器绘制在图层2上,家具绘制在图层3上,将三个图层全部打开就是最后完整的图形。

要想修改电器部分,可以直接修改,也可以将家具和墙壁所在的图层设为关,即不可见,这样就不会因为修改电器而误修改家具部分了。

我们可以根据需要增加或删除某一层或多个层。

在每一层上,都可以进行图形绘制,能够设置任意的线型与颜色。

在图形的绘制之前,为了便于以后的使用,最好先创建几个层。

层的创建可通过下拉菜单Data,Layers Control完成,也可通过单击工具条Layers实现创建。

创建时,可一次定义一个或多个层名,层名之间应用逗号隔开,每个层名中不能有空格。

层名限于使用标准字母、数字以及连字符(-)、美元符号($)和下划线(_),且层名最长不可以超过31个字符。

当层名重复时将执行前者。

层对于新建的层,其颜色和线型将自动定义为White和CONTINUOUS,状态为打开。

在层的使用过程中,我们可以根据需要设置层的特性。

AutoCAD支持255种颜色选择,线型库中包括了多种待选线型。

选择设置不同的颜色和线型,可以使得屏幕上的图形美观且便于区分。

线型的设置比较简单,只要单击Set Linetype, 即可根据需要设置。

cxx版图学习初级(个人经验)

CXX版图设计学习目录1写在前面的话,一些感受、声明和注意事项2开始—画最简单的单元反相器3工艺层的相关知识1写在前面的话本人也是刚开始学习版图设计,但觉得版图的一些学习资料繁杂,难度深浅不一,对于一个新手来说很难通过这些学习资料自学成才,通过这一个多星期的学习,我将以自己独特的方式来组织这些学习资料,从而使得一个毫无基础的新手可以快速入门。

再次声明,这篇材料是各种版图资料的重新组合。

以后有什么想说的还会继续补充。

学习这种实践性很强的技术,只看书显然是不够的,必须要在软件上实际操作,通过不断的熟悉软件和设计规则来快速成为一名版图设计工程师。

本人的学习计划是实践+理论+实践+理论……2开始—画最简单的单元反相器Virtuoso Editing 的使用简介全文将用一个贯穿始终的例子来说明如何绘制版图。

这个例子绘制的是一个最简单的非门的版图。

§2-1 建立版图文件使用library manager。

首先,建立一个新的库myLib,关于建立库的步骤,在前文介绍cdsSpice 时已经说得很清楚了,就不再赘述。

与前面有些不同的地方是:由于我们要建立的是一个版图文件,因此我们在technology file 选项中必须选择compile a new tech file,或是attach to an exsiting tech file。

这里由于我们要新建一个tech file,因此选择前者。

这时会弹出load tech file的对话框,如图2-1-1 所示。

在ASCII Technology File 中填入csmc1o0.tf即可。

接着就可以建立名为inv的cell 了。

为了完备起见,读者可以先建立inv的schematic view和symbol view(具体步骤前面已经介绍,其中pmos 长6u,宽为0.6u。

nmos 长为3u,宽为0.6u。

model 仍然选择hj3p 和hj3n)。

新手学版图—理解版图的层(详细)

版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS反相器为例,基本原理很简单,当输入高电平时,NMOS导通,输出端连接到地;当输入端为低电平时,PMOS导通,输出端连接到VDD。

版图的目的就是要以图形的方式形成这两个MOS管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POL Y自对准形成MOS管子,输入为POL Y,输出为金属连线,连接点为CONTACT。

首先创建新的cell view背景代表P型衬底,材料为Si-100 电阻率约5-10Ωcm,清洗后生长约200Å氧化层,再以LPCVD(低压化学气相沉积)沉积氮化硅约800A。

Wafer厚度大约为750um,但最后打磨贴片后的厚度大约只有约250um。

(10000A=1um)氧化层的应用大致可分为:屏蔽、遮蔽、场区及局部绝缘、衬垫、缺陷去除、栅介电层、浅沟槽阻挡,厚度依次约为200A、5000A、3000-5000A、100-200A、<1000A、30-120A、100-200A。

氮化物一般较为致密,所以可以用来隔离、阻挡,以及CMP的停止层。

涂布光阻、曝光、显影,以氮化物等离子体干法刻蚀去除氮化硅,剥离光阻(以下将省略一些层的去除过程)。

版图Active层将定位出有源区,非有源区将通过LOCOS(硅的局部氧化)生长场氧化层,厚度大约3000-10000A。

不过因该过程存在鸟嘴效应及表面平坦度问题,90年代后已经由STI(淺沟槽绝缘)所取代。

版图P-well层定位P-well区域,在这一区域离子植入B+/225KeV/3x10^13cm^-2。

用版图N-well层定位N-well区域,离子植入P+/600KeV/2x10^13cm^-2。

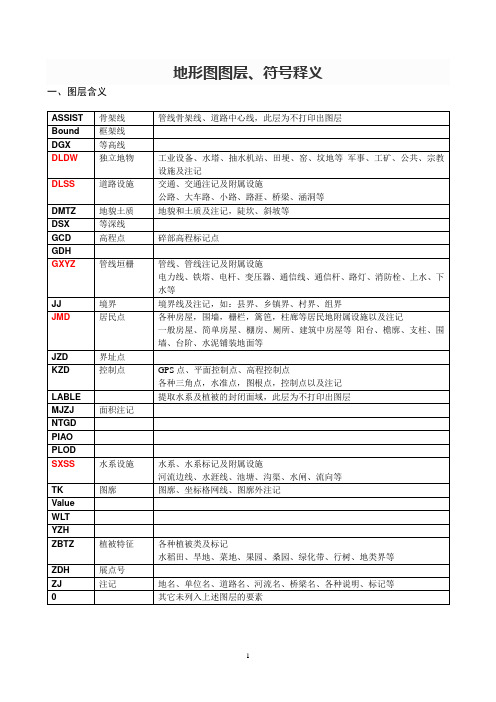

CAD地形图各图层表示含义

地形图图层、符号释义一、图层含义二、图层详解1.JMD图层(1)要求各要素均有代码且代码使用合理,合理的使用代码是地形数据的基本要求。

(2)在入库数据里,各种房屋以面状要素的身份入库,所以各种属性的房屋均要求闭合,到图廓边的房屋同样要求在图廓边闭合,目的是相同属性面状要素经过数据入库后可自动进行拼接。

(3)共线房屋要求数据上完全重合,达到“无缝连接”的目的。

(4)房屋的性质及楼层除了图面注记还要求将其输入扩展属性,且扩展属性表达的内容和图面注记要求完全一致。

(5)JMD注记包括单位名称,地名,楼层注记,单位名称和地名注记大小按照《地形图图式》要求,楼层注记大小则规定字高为2。

(6)单位名称和地名各有代码,且除了在合适的位置标注注记还要求在注记旁输入“地名标记点”,将名称输入该点的扩展属性里,由于该点的功能用于数据查询使用,要求录入的名称不能有空格或其他分隔符号。

(7)如果单位或地名比较长,用一排在所在面积表示不下,则分为两排或多排,这种排列为人工排列,不能使用MTEXT方式排列,在数据转换时MTEXT方式文字为非法文字方式。

2. DLDW层(1)要求各要素均有代码且代码使用合理。

(2)DLDW层除龙门吊、天吊等的框架线以面状的身份入库,其余除文字和符号外的工矿要素均以线要素身份入库,所以各种工矿线要素呈面状时不要求闭合,但禁止不合理的断线,到图廓边呈面状的地物不能在图廓边闭合。

(3)DLDW层注记包括工矿类的所有注记和其他注记如“水泥地”、“施工区”、“拆迁区”、“乱掘”、“堆土”等,注记大小规定字高为2.53. DLSS图层(1)要求各要素均有代码且代码使用合理。

(2)DLSS层除各种桥梁框架线以面状的身份入库,其余除文字和符号外的工矿要素均以线要素身份入库,所以各种道路线要素呈面状时不要求闭合,但禁止不合理的断线。

(3)同一条道路边线的代码要统一且合理。

(4)有名称的道路需绘道路中心线,道路中心线的图层为ASSIST层,此层为不打印输出层,绘制时目测即可,不需实地测绘,绘制道路中心线的目的也是用来在数据库里查询和数据分析使用,所以扩展属性里的道路名称不能有空格,道路宽度可直接在图上量取,数值单位使用实地距离。

版图初级-理解版图的层(彩图)

新手学版图—理解版图的层(详细)新手学版图—理解版图的层版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS反相器为例,基本原理很简单,当输入高电平时,NMOS导通,输出端连接到地;当输入端为低电平时,PMOS导通,输出端连接到VDD。

版图的目的就是要以图形的方式形成这两个MOS管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POLY自对准形成MOS管子,输入为POLY,输出为金属连线,连接点为CONTACT。

首先创建新的cell view背景代表P型衬底,材料为Si-100 电阻率约5-10Ωcm,清洗后生长约200Å氧化层,再以LPCVD(低压化学气相沉积)沉积氮化硅约800A。

Wafer厚度大约为750um,但最后打磨贴片后的厚度大约只有约250um。

(10000A=1um)氧化层的应用大致可分为:屏蔽、遮蔽、场区及局部绝缘、衬垫、缺陷去除、栅介电层、浅沟槽阻挡,厚度依次约为200A、5000A、3000-5000A、100-200A、<1000A、30-120A、100-200A。

氮化物一般较为致密,所以可以用来隔离、阻挡,以及CMP 的停止层。

涂布光阻、曝光、显影,以氮化物等离子体干法刻蚀去除氮化硅,剥离光阻(以下将省略一些层的去除过程)。

版图Active层将定位出有源区,非有源区将通过LOCOS(硅的局部氧化)生长场氧化层,厚度大约3000-10000A。

不过因该过程存在鸟嘴效应及表面平坦度问题,90年代后已经由STI(淺沟槽绝缘)所取代。

版图P-well层定位P-well区域,在这一区域离子植入B+/225KeV/3x10^13cm^-2。

PCB中各层的含义

PCB中各层的含义信号层(Signal Layers):信号层包括Top Layer、BottomLayer、Mid Layer 1…30。

这些层都是具有电气连接的层,也就是实际的铜层。

中间层是指用于布线的中间板层,该层中布的是导线。

顶层信号层(Top Layer)顶层信号层(Top Layer)也称元件层,主要用来放置元器件,对于双层板和多层板可以用来布置导线或覆铜。

底层信号层(BottomLayer)也称焊接层,主要用于布线及焊接,对于双层板和多层板可以用来放置元器件。

中间信号层(Mid-Layers)最多可有30层,在多层板中用于布置信号线,这里不包括电源线和地线。

内层(InternalPlane):Internal Plane 1…16,该类型的层仅用于多层板,这些层一般连接到地和电源上,成为电源层和地层,也具有电气连接作用,也是实际的铜层,但该层一般情况下不布线,是由整片铜膜构成。

通常简称为内电层,仅在多层板中出现,PCB板层数一般是指信号层和内电层相加的总和数。

与信号层相同,内电层与内电层之间、内电层与信号层之间可通过通孔、盲孔和埋孔实现互相连接。

丝印层(SilkscreenOverlay):包括顶层丝印层(Top overlay)和底层丝印层(Bottom overlay)。

定义顶层和底层的丝印字符,就是一般在阻焊层之上印的一些文字符号,比如元件名称、元件符号、元件管脚和版权等,方便以后的电路焊接和查错等。

一块PCB板最多可以有2个丝印层,分别是顶层丝印层(TopOverlay)和底层丝印层(Bottom Overlay),一般为白色,主要用于放置印制信息,如元器件的轮廓和标注,各种注释字符等,方便PCB的元器件焊接和电路检查。

顶层丝印层(TopOverlay)用于标注元器件的投影轮廓、元器件的标号、标称值或型号以及各种注释字符。

底层丝印层(BottomOverlay)与顶层丝印层相同,若所有标注在顶层丝印层都已经包含,底层丝印层可关闭。

IC版图设计1讲解学习

材料与能源学院微电子材料与工程系

Fundamentals of IC Analysis and Design (4)

(3)定义设计人员设计时所用的电参数的范围。 通常,这些电参数中包括晶体管增益、开启电压、

电容和电阻的数值,均反映在版图的电学设计规则文件 中。

一般来讲,设计规则反映了性能和成品率之间可能的最 好的折衷。

规则越保守,能工作的电路就越多(即成品率越高)。 规则越富有进取性,则电路性能改进的可能性也越大,

这种改进可能是以牺牲成品率为代价的。

材料与能源学院微电子材料与工程系

Fundamentals of IC Analysis and Design (4)

➢ contact设计规则示意图

材料与能源学院微电子材料与工程系

Fundamentals of IC Analysis and Design (4)

➢ Metal相关的设计规则列表

编号 描述

尺寸

5.1 金属宽度 2.5 5.2 金属间距 2.0

目的与作用 保证铝线的良好

电导

防止铝条联条

➢ Metal设计规则示意图

➢ 从设计的观点出发,设计规则可以分为三部分:

(1)决定几何特征和图形的几何尺寸的规定 作用:保证各个图形彼此之间具有正确的关系。 每层掩膜上的各个图形部件应该相切,或者应该保持互相分 开;不同掩膜上的各个图形部件应该套合,或者应该保持互相分 开。

(2)确定掩膜制备和芯片制造中都需要的一组基本图形部件的强制性 要求。 典型的图形部件可能包括制造中所用的各块掩膜精确套准所 需的对准标志,把各个电路从硅片切下来的划片间距以及供压焊 封装用的压焊点尺寸。

版图_基础篇

版图设计基础篇----invert1、虚拟机如下2、打开虚拟系统(预先将装好软件的虚拟系统拷贝到电脑中,拷贝的盘格式格式化为NTFS格式)3、Power on4、点击Power on this virtual machine,等待。

5、进入linux 用户名root 密码 mimamima6、显示桌面7、打开终端,右键选择open terminal8、Ls查看目录9、进入PDK文件夹 cd chrt1810、打开cadence icfb11、新建(打开(osc中有我做的例子))原理图12、File new library13、Name 选择attach to an existing techfile14、选择chrt18rf15、选择cellview16、选择刚新建的library,自命名cell name17、按i添加元件,或者选择add instance18、按browse选择选择library19、我们一般选择chrtbase和chrt18rf里的元器件,依次往右选,如上选择了chrtbase中MOS管,型号nmos-1p8,最后一栏选symbol,然后回到virtuoso schematic editing,点击左键即选中了该元件如下图20、选中器件按字母Q可以修改器件的属性,多MOS管而言一般是W,L,fingers,同样的方法选择其他器件修改属性。

21、save连线;左侧这几个功能经常用到22、 C 复制,p 添加pin(输入输出接口如下)23、输入四个pin name以空格隔开,direction 选择inputoutput,点击hide在virtuososchematic editing原理图中合适位置依次点击鼠标左键放置pin,然后连线如下图。

Save 至无错。

24、生成cellview供仿真调用,如下选择cellview,ok,ok,关闭生成的cellview和原理图invert25、可如下修改user preferences26、修改成10次,这个画错了,可以按u回到上一步,可回10步27、再新建一个原理图用来做前仿(原理图级仿真)28、这回可以在我们自己建的库里调出刚才画的反向器invert,方法同其他器件的添加,只是库选择mmlinvert,可按R再电击invert旋转器件。

教你识别四层板六层板和八层板

教你识别四层板六层板和八层板一、什么是PCB 很多人都听说过"PCB"这个英文缩写名称。

但是它到底代表什么含义呢?其实很简单,就是印刷电路板(Printed circuit board,PCB)。

它几乎会出现在每一种电子设备当中。

如果在某样设备中有电子零件,它们都是镶在大小各异的PCB 上的。

除了固定各种小零件外,PCB 的主要功能是提供上头各项零件的相互电气连接。

随着电子设备越来越复杂,需要的零件自然越来越多,PCB 上头的线路与零件也越来越密集了。

裸板(上没有零件)也常被称为"印刷线路板Printed Wiring Board(PWB)"。

板子本身的基板是由绝缘隔热、并不易弯曲的材质所制作成。

在表面可以看到的细小线路材料是铜箔,原本铜箔是覆盖在整个板子上的,而在制造过程中部份被蚀刻处理掉,留下来的部份就变成网状的细小线路了。

这些线路被称作导线(conductor pattern)或称布线,并用来提供PCB 上零件的电路连接。

通常PCB 的颜色都是绿色或是棕色,这是阻焊漆(solder mask)的颜色。

是绝缘的防护层,可以保护铜线,也可以防止零件被焊到不正确的地方。

在阻焊层上还会印刷上一层丝网印刷面(silk screen)。

通常在这上面会印上文字与符号(大多是白色的),以标示出各零件在板子上的位置。

丝网印刷面也被称作图标面(legend)。

二、PCB 板的分类在最基本的PCB 板子上,零件一般都集中在其中一面,导线则集中在另一面上。

因为导线只出现在其中一面,所以我们就称这种PCB 叫作单面板(Single-sided)。

因为单面板在设计线路上有许多严格的限制(因为只有一面,布线间不能交叉而必须绕独自的路径),所以只有早期的电路才使用这类的板子。

如何解决越来越复杂的电路设计方案呢?双面板(Double-Sided Boards)出现了。

这种电路板的两面都有布线。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

网站论坛| 旧讨论区stm_em(); //-->

最新公告:当前没有任何公告!

网站论坛| 加入收藏

您现在的位置:纯粹的版图IC Layout >> 文章专栏 >> 物理版图 >> [专题]新手学版图 >> 正文

新手学版图—理解版图的层(详细)热

新手学版图—理解版图的层(详细)

[ 作者:nfmao | 转贴自:本站原创 | 点击数:2143 | 更新时间:2006-8-17 | 文章录入:nfmao ]

新手学版图—理解版图的层

版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS反相器为例,基本原理很简单,当输入高电平时,NMOS导通,输出端连接到地;当输入端为低电平时,PMOS

导通,输出端连接到VDD。

版图的目的就是要以图形的方式形成这两个MOS管,并且有输入、出端,还有连接点连接到

地或电源。

有源区加POLY自对准形成MOS管子,输入为POLY,输出为金属连线,连接点为CONTACT。

首先创建新的cell view背景代表P型衬底,材料为Si-100 电阻率约5-10Ωcm,清洗后生长约200 Å氧化层,再以LPCVD(低压化学气相沉积)沉积氮化硅约800A。

Wafer厚度大约为750um,但最后打磨贴片后的厚度大约只有约250um。

(10000A=1um)

氧化层的应用大致可分为:屏蔽、遮蔽、场区及局部绝缘、衬垫、缺陷去除、栅介电层、浅沟槽阻挡,厚度依次约为

200A、5000A、3000-5000A、100-200A、<1000A、30-120A、100-200A。

氮化物一般较为致密,所以可以用来隔离、阻挡,以及CMP的停止层。

涂布光阻、曝光、显影,以氮化物等离子体干法刻蚀去除氮化硅,剥离光阻(以下将省略一些层的去除过程)。

版图Active 层将定位出有源区,非有源区将通过LOCOS(硅的局部氧化)生长场氧化层,厚度大约3000-10000A。

不过因该过程存在鸟嘴效应及表面平坦度问题,90年代后已经由STI(淺沟槽绝缘)所取代。

版图P-well层定位P-well区域,在这一区域离子植入B+/225KeV/3x10^13cm^-2。

用版图N-well层定位N-well区域,离子植入P+/600KeV/2x10^13cm^-2。

以P/250/2x10^12 + P/1200/3x10^13 + 950C,30min,为例最后深度大约2um,方块电阻

790ohms。

传统工艺制成的阱区深度约4um左右。

阱区形成后还可能进行阈值调整处理,这一步不需要版图层的参与。

版图Poly层定位poly及gate,不过在形成channel(沟道)之前,必须生长出一层优质的氧化层,这一层的厚度约30-120A,可能实际测量出来只有十几埃。

在这一层上以LPCVD沉积多晶硅约0.5um,并对poly掺杂P/30/5x10^15。

因为多晶硅各向异性所以采用RIE(反应离子刻蚀)方法进行刻蚀。

自对准形成源、漏极,被poly层挡住与active层重叠的下面将会是MOS的沟道,剩下的active 区域将形成源、漏极。

为了抑制热电子或热载流子效应要通过LDD(轻掺杂漏极)首先进行轻掺杂,然后在栅上形成侧墙后再以低能量、高电流来形成源漏区,这样会形成一个梯度。

版图P-imp层决定形成P+型,离子植入B/10/2x10^15,版图N-imp层决定形成N+型,离子植入As/30/3x10^15。

通常该区域的深度在2um左右。

此时器件已经基本形成,之后要为连接作好准备。

在表面濺射一层金属层(比如Ti),在与硅接触的表面反应形成金属硅化物(silicide),在外表面形成TiN。

如果栅、源、漏极都有silicide 俗称为salicide,如果只形成在多晶硅上称为polycide。

表面平坦化处理时,可以通过加热掺杂的BPSG(硼磷硅玻璃)软化流动,或以CMP(化学机械研磨)以达到表面平坦化。

版图contact层定位连接孔,contact光掩膜通常采用Dark形式,即图形区域透光,背景不透光,配合正光阻,光照射的区域可溶化,以此定位出开孔区域。

孔内金属是以MOCVD(金属有机化学气相沉积CVD)形式沉积金属W(钨),再以CMP方式打磨多余的金属。

濺射第一层金属,并以版图metal1层,刻画出金属连线。

覆盖CMP(介电层),以同样的方式开孔(版图via1层),刻画第二层金属(版图metal2层)。

如果是完整的项目还要使用版图pass层开出PAD的位置,并进行钝化处理以PECVD(介质等离子体增强化学气相沉积)沉积氮化硅,以达到保护芯片的目的。

现在各层的作用已经有了说明,接下来将利用实际的作用来举例说明,层与层之间的关系。

1,版图P-well层,N-wel l层在衬底形成各自的阱区,它们之间的关系应该不能相互重叠。

2,因为器件形成在阱中,所以

器件的图形必须被阱所覆盖,要么在P-well中,要么在N-well中。

3,P-well与P-well,N-well与N-well是否可以相连,取决于特性是否一致,比如相同的电位。

4,P-imp,N-imp层要比相对的active 大。

否则未覆盖的区域将没有离子植入。

5,因为自对准工艺,在形成channel的地方,poly要横跨过active层。

没有channel的地方避免接触。

6,contact层必须与metal层或poly层要有接触(在需要连接的地方)。

传统的“钉头”形式需要金属覆盖住contact。

(本文到此结束,不足之处还批评指正,谢谢!)

上一篇文章:新手学版图—理解版图的层

下一篇文章:新手学版图—认识保护环

发表评论 | 告诉好友 | 打印此文 | 关闭窗口热门文章推荐文章相关文章

. Virtuoso 库结构及object (522)

. 求职上海/江浙[898]. “IC版图设计师”培训班招 (762)

. 闩锁的物理分析[读书笔记] (1087)

· laker能够读取spice网表拉…[563]· 关于standard cell[4465]

. The art of analog layout (6955)

. 在RHEL下的Cadence IC5的安 (5611)

. 急聘兼职模拟版图设计工程 (208)

· 上海寻找LAYOUT兼职工作[369]

· 新手学版图—认识保护环[1881]

. 新手学版图—理解版图的层 (2194)

· 版图在新技术下的新变化[1298]

网友评论只显示最新10条。

评论内容只代表网友观点,与本站立场无关!

没有任何评论

查看关于此文章的所有评论关于本站 | 联系站长 | 友情链接 | 版权申明 | 网站论坛 | 访客留言

Copyright © 2000-2004 纯粹的版图站长:nfmao

Powered by:FreePower Ver 3.6 Sp2执行时间:156.25 毫秒 | 查询数据库:15 次当前模版:[蓝灰之意3]

非经营性沪ICP备05007351号。