新手学版图

初学cad画图步骤详解

初学CAD画图步骤详解简介CAD(计算机辅助设计)是一种广泛应用于工程设计、建筑设计、机械设计等领域的技术。

对于初学者来说,掌握CAD的基本画图步骤是非常重要的。

本文将为您详细介绍初学CAD画图的步骤。

步骤一:创建新文件打开CAD软件后,首先需要创建一个新的文件来进行画图。

在菜单栏中选择“文件”,然后选择“新建”或者使用快捷键“Ctrl + N”来创建新文件。

步骤二:设置图纸尺寸和比例在创建新文件后,您需要设置图纸的尺寸和比例。

在CAD中,可以选择常用的标准尺寸,也可以自定义尺寸。

在菜单栏中选择“格式”,然后选择“图纸设置”来进行尺寸和比例的设置。

根据您的需要,选择合适的尺寸和比例。

步骤三:绘制基本图形一般而言,CAD画图的基础是一些基本图形,如直线、矩形、圆形等。

在CAD 中,绘制基本图形的方式有多种。

下面以绘制直线为例进行说明。

1.在工具栏中选择“直线”工具,或者使用快捷键“L”。

2.在图纸上点击鼠标左键确定直线的起点。

3.移动鼠标并点击鼠标左键来确定直线的终点。

4.按下“Enter”键或者右键来结束绘制直线。

绘制其他基本图形的步骤类似,只需选择不同的工具即可。

步骤四:编辑图形在绘制完基本图形后,您可能需要调整、编辑或者修改图形的一些细节。

在CAD中,有许多编辑工具可以帮助您完成这些操作。

下面介绍一些常用的编辑操作:•移动图形:选择要移动的图形,然后使用“移动”工具来将图形移动到新的位置。

•缩放图形:选择要缩放的图形,然后使用“缩放”工具来调整图形的大小。

•旋转图形:选择要旋转的图形,然后使用“旋转”工具来将图形旋转到合适的角度。

•删除图形:选择要删除的图形,然后使用“删除”工具来删除选中的图形。

步骤五:添加文字和注释在CAD中,您可以添加文字和注释来解释图形的含义或者提供额外的信息。

下面介绍如何添加文字和注释:1.选择“文字”工具,或者使用快捷键“T”。

2.在图纸上点击鼠标左键确定文字的起点。

版图版画技巧

简易地理板图(板画)绘画技巧地理板图又叫地理黑板图。

是地理教师在教学过程中,凭借自己的记忆和熟练技巧,用简单的工具(如各色粉笔)和简练的笔法,把复杂的地理事物和现象迅速描绘在黑板上的简略地理图画。

主要包括地理略图、形态图、剖面图和过程图等主要类型。

其中,后三种又被称为地理板画。

一、学习简易地理板图(板画)绘画的意义地理板图只取神似,不计细节,旨在抓住特征,突出重点,说明地理问题。

在地理教学中具有十分重要的作用。

所有教学技术手段都有自身的价值和存在的意义。

我们发展现代教学技术,并不是要抛弃一切传统的教学技术,而是要把现代教学技术和传统教学手段结合起来,努力挖掘所有教学技术手段的使用价值,积极促进各种技术手段之间的协同互补,从而促进教学技术体系整体协调发展。

二、简易地理板图(板画)速绘的基本要求简易地理板图的绘画具有三要素,即略、像、快。

评价地理板图的优劣,主要应从以下几个方面入手:1.板图形式简略、美观要求线条流畅、简练、清晰;色彩鲜明、爽目;富于表现性,使人看之悦目。

切忌支离破碎,随手乱画,为此必须做好原图的简化工作。

(图1、2)2.内容准确,重点突出讲求地理科学性,明确图上各种地理要素之间的关系;突出所要表达的主要地理事物和现象。

3.作图迅速,与语言同步要具有熟练的作图技巧,迅速成图;应与教学语言配合协调,同步进行。

切忌为作图而作图。

图1 澳大利亚略图图 2 五带的划分三、简易地理板图(板画)绘画技巧及训练地理板图的速绘历来都被看成是少数人的天赋,对多数人来说,是可望而不可及的。

传统的板图描绘技法大都落笔只画一点、一线,费时多、效率低,且技法难以掌握。

许多教师往往因画跟不上讲,影响教学进程而放弃。

近年来,随着教学改革的不断深入,有关专家已大胆地改革了传统的绘图方法,在作图速度上有很大突破,形成了简单易学的作图技巧。

归纳起来大致可包括绘图工具的制作、笔法的运用和作图要领等。

1.工具的制作简易板图绘画技巧大大提高了作图的速度,落笔成片,一笔多点、多线,从而使作图速度提高了几倍,乃至几十倍之多。

新手学版图--几种电阻的画法

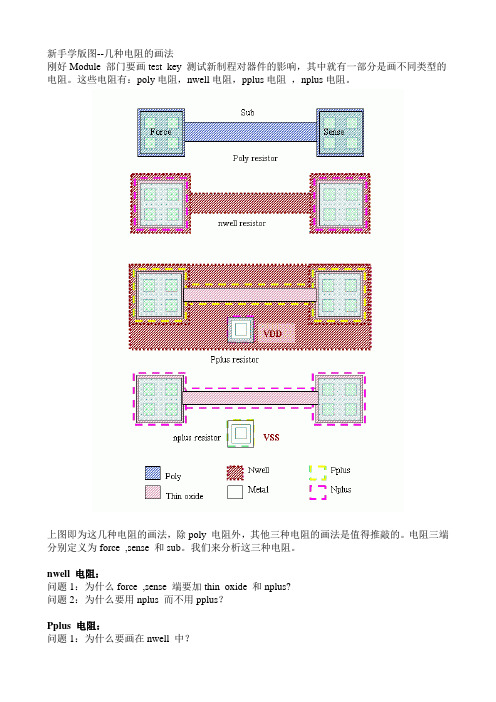

新手学版图--几种电阻的画法刚好Module 部门要画test key 测试新制程对器件的影响,其中就有一部分是画不同类型的电阻。

这些电阻有:poly电阻,nwell电阻,pplus电阻,nplus电阻。

上图即为这几种电阻的画法,除poly 电阻外,其他三种电阻的画法是值得推敲的。

电阻三端分别定义为force ,sense 和sub。

我们来分析这三种电阻。

nwell 电阻:问题1:为什么force ,sense 端要加thin oxide 和nplus?问题2:为什么要用nplus 而不用pplus?Pplus 电阻:问题1:为什么要画在nwell 中?问题2:为什么sub 要接高电位?问题3:为什么电阻中间要用thin oxide 连接?Nplus 电阻:问题1:可不可以画在nwell 中?其实以上问题的重点1是要理解thin oxide 的作用,以及nwell , p+/N+ plus 在制造过程中所处的步骤。

thin oxide 可以理解为去除FOX。

nwell 在制造的前端就形成了,FOX不会对此造成影响。

而P+/N+ plus 会受FOX的影响,如果FOX阻挡的话,wafer 上就不会形成相应的P型或N型。

重点2即是否会出现不正确的导通。

回答完这些问题之后,我们可以联想到加guard ring时的一些情况。

就p-sub /nwell CMOS 版图而言,少数载流子guard ring 为nwell + nplus + thin oxide +VDD, 多数载流子guard ring 为pplus + thin oxide + VSS。

讨论当两种guard ring thin oxide 不连续时的不同影响。

显然在thin oxide 断开的地方FOX 阻挡了n+/p+的形成,对于nwell guard ring在断开的地方形成nwell 电阻,但对于以p型为衬底的地方而言这里就完全断开了。

版图设计流程

版图设计流程版图设计是一项非常重要的工作,它直接关系到产品或者项目的整体形象和用户体验。

一个好的版图设计可以提升产品的吸引力和竞争力,因此,版图设计流程的规范性和有效性显得尤为重要。

在进行版图设计时,我们需要遵循一定的流程,以确保设计的高质量和高效率。

第一步,需求分析。

在进行版图设计之前,我们需要对产品或项目的需求进行充分的分析。

这包括对目标用户群体的需求分析,对产品功能和特性的分析,以及对市场和竞争对手的分析。

只有充分了解需求,我们才能进行有针对性的版图设计,满足用户的实际需求。

第二步,概念构思。

在完成需求分析后,我们需要进行概念构思。

这一阶段是版图设计的灵感迸发阶段,我们可以进行大胆的构思和创意的发挥。

在这个阶段,可以进行头脑风暴,绘制草图,或者进行一些简单的设计尝试,以寻找最合适的设计方向。

第三步,结构规划。

在完成概念构思后,我们需要进行版图设计的结构规划。

这包括对版图的整体结构进行规划,确定版面布局、内容分区、色彩搭配等。

在这一阶段,我们需要考虑版图的视觉引导和信息传达,确保用户在浏览版图时能够快速获取所需信息。

第四步,细节设计。

在完成结构规划后,我们需要进行版图设计的细节设计。

这包括对版面的各个细节进行精细化设计,包括文字排版、图标设计、配色搭配等。

在这一阶段,我们需要注重细节,确保版图的每一个元素都能够完美地融入整体设计中。

第五步,评审修改。

在完成版图设计后,我们需要进行评审和修改。

这一阶段需要邀请相关的人员对版图进行评审,包括设计师、产品经理、市场人员等。

根据评审意见,我们需要对版图进行适当的修改和调整,以确保设计符合实际需求和市场需求。

第六步,输出交付。

最后,我们需要将完成的版图设计进行输出和交付。

这包括将设计稿转化为可用的格式,如图片、PDF等,并交付给相关的部门或人员使用。

在交付时,我们需要确保设计的质量和准确性,以满足后续的使用需求。

总结。

版图设计流程是一个复杂而严谨的过程,需要设计师和相关人员的共同努力和配合。

【精】绘制世界地图板图的一般步骤

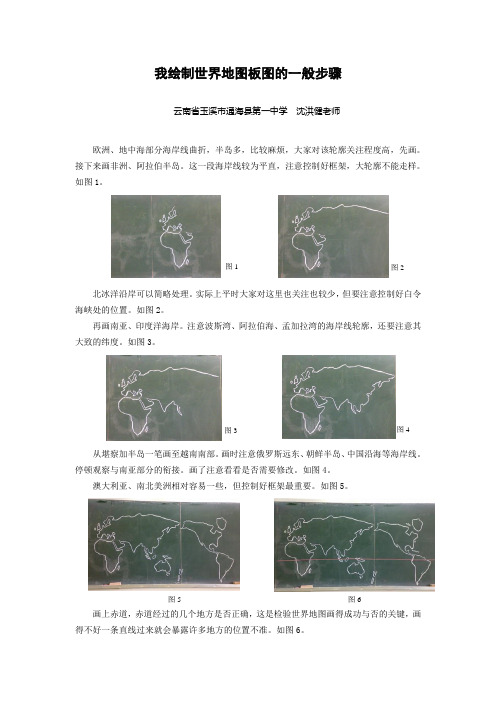

我绘制世界地图板图的一般步骤云南省玉溪市通海县第一中学 沈洪健老师欧洲、地中海部分海岸线曲折,半岛多,比较麻烦,大家对该轮廓关注程度高,先画。

接下来画非洲、阿拉伯半岛。

这一段海岸线较为平直,注意控制好框架,大轮廓不能走样。

如图1。

北冰洋沿岸可以简略处理。

实际上平时大家对这里也关注也较少,但要注意控制好白令海峡处的位置。

如图2。

再画南亚、印度洋海岸。

注意波斯湾、阿拉伯海、孟加拉湾的海岸线轮廓,还要注意其大致的纬度。

如图3。

从堪察加半岛一笔画至越南南部。

画时注意俄罗斯远东、朝鲜半岛、中国沿海等海岸线。

停顿观察与南亚部分的衔接。

画了注意看看是否需要修改。

如图4。

澳大利亚、南北美洲相对容易一些,但控制好框架最重要。

如图5。

画上赤道,赤道经过的几个地方是否正确,这是检验世界地图画得成功与否的关键,画得不好一条直线过来就会暴露许多地方的位置不准。

如图6。

图1 图2 图3 图4 图6图5有了轮廓图,就可以讲述海洋中的洋流、陆地上的山脉、河流、城市……。

在讲洋流时,画一下完整的大西洋海岸是很有必要的,这样才能完整的呈现大西洋里的洋流系统。

如图7。

叫学生上来画的0°、180°、20°W、160°E 经线。

也是为了鼓励学生参与,让他们体会说起来容易,做起来难。

很遗憾,虽然这几条线不难,但学生画得不太直,效果不好。

当然,再不好,也要鼓励,别打击学生的积极性。

敬请批评指正。

网友1跟贴提问:1、你花了多长时间完成这个作品。

2、你花完后学生是不是对你非常佩服?洪健老师答:不拍照的画,1—2分钟。

学生都习惯了,也没什么惊叹。

只是快速复习中,学生喜欢这种方式,学生上来填涂热闹、积极、不枯燥。

很多学生学着画、记得牢。

网友2跟贴提问:好奇的问。

你花了多长时间可以练就到这个程度。

洪健老师答:因为我很懒,而且以前学校困难没有地图,我从教书就没带过地图,喜欢空着手去上课。

也喜欢不批改作业,作业就叫学生上来做,有问题也好当堂课讲解。

Layout(集成电路版图)注意事项及技巧总结

Layout(集成电路版图)注意事项及技巧总结Layout主要⼯作注意事项●画之前的准备⼯作●与电路设计者的沟通●Layout 的⾦属线尤其是电源线、地线●保护环●衬底噪声●管⼦的匹配精度⼀、l ayout 之前的准备⼯作1、先估算芯⽚⾯积先分别计算各个电路模块的⾯积,然后再加上模块之间⾛线以及端⼝引出等的⾯积,即得到芯⽚总的⾯积。

2、Top-Down 设计流程先根据电路规模对版图进⾏整体布局,整体布局包括:主要单元的⼤⼩形状以及位置安排;电源和地线的布局;输⼊输出引脚的放置等;统计整个芯⽚的引脚个数,包括测试点也要确定好,严格确定每个模块的引脚属性,位置。

3、模块的⽅向应该与信号的流向⼀致每个模块⼀定按照确定好的引脚位置引出之间的连线4、保证主信号通道简单流畅,连线尽量短,少拐弯等。

5、不同模块的电源,地线分开,以防⼲扰,电源线的寄⽣电阻尽可能较⼩,避免各模块的电源电压不⼀致。

6、尽可能把电容电阻和⼤管⼦放在侧旁,利于提⾼电路的抗⼲扰能⼒。

⼆、与电路设计者的沟通搞清楚电路的结构和⼯作原理明确电路设计中对版图有特殊要求的地⽅包含内容:(1)确保⾦属线的宽度和引线孔的数⽬能够满⾜要求(各通路在典型情况和最坏情况的⼤⼩)尤其是电源线盒地线。

(2)差分对管,有源负载,电流镜,电容阵列等要求匹配良好的⼦模块。

(3)电路中MOS管,电阻电容对精度的要求。

(4)易受⼲扰的电压传输线,⾼频信号传输线。

三、layout 的⾦属线尤其是电源线,地线1、根据电路在最坏情况下的电流值来确定⾦属线的宽度以及接触孔的排列⽅式和数⽬,以避免电迁移。

电迁移效应:是指当传输电流过⼤时,电⼦碰撞⾦属原⼦,导致原⼦移位⽽使⾦属断线。

在接触孔周围,电流⽐较集中,电迁移更容易产⽣。

2、避免天线效应长⾦属(⾯积较⼤的⾦属)在刻蚀的时候,会吸引⼤量的电荷,这时如果该⾦属与管⼦栅相连,可能会在栅极形成⾼压,影响栅养化层质量,降低电路的可靠性和寿命。

新手学版图

新手学版图新手学版图—理解版图的层版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS反相器为例,基本原理很简单,当输入高电平时,NMOS导通,输出端连接到地;当输入端为低电平时,PMOS导通,输出端连接到VDD。

版图的目的就是要以图形的方式形成这两个MOS管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POLY自对准形成MOS管子,输入为POLY,输出为金属连线,连接点为CONTACT。

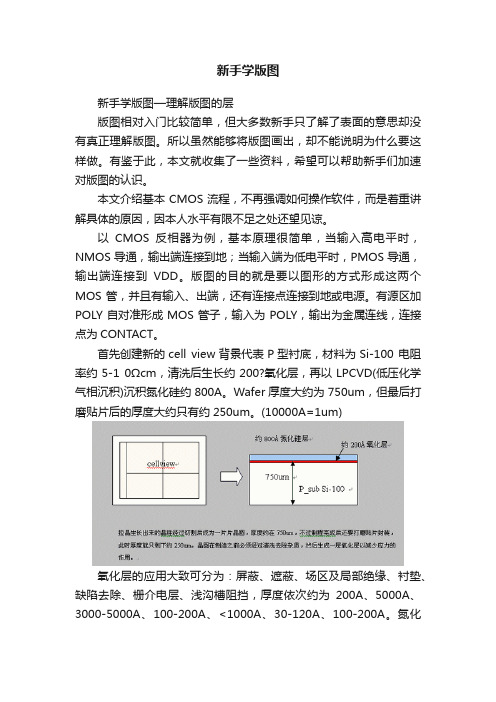

首先创建新的cell view背景代表P型衬底,材料为Si-100 电阻率约5-1 0Ωcm,清洗后生长约200?氧化层,再以LPCVD(低压化学气相沉积)沉积氮化硅约800A。

Wafer厚度大约为750um,但最后打磨贴片后的厚度大约只有约250um。

(10000A=1um)氧化层的应用大致可分为:屏蔽、遮蔽、场区及局部绝缘、衬垫、缺陷去除、栅介电层、浅沟槽阻挡,厚度依次约为200A、5000A、3000-5000A、100-200A、<1000A、30-120A、100-200A。

氮化物一般较为致密,所以可以用来隔离、阻挡,以及CMP的停止层。

涂布光阻、曝光、显影,以氮化物等离子体干法刻蚀去除氮化硅,剥离光阻(以下将省略一些层的去除过程)。

版图Active层将定位出有源区,非有源区将通过LOCOS(硅的局部氧化)生长场氧化层,厚度大约3000-10000A。

不过因该过程存在鸟嘴效应及表面平坦度问题,90年代后已经由STI(淺沟槽绝缘)所取代。

版图P-well层定位P-well区域,在这一区域离子植入B+/225KeV/3x10^1 3cm^-2。

版图技巧总结

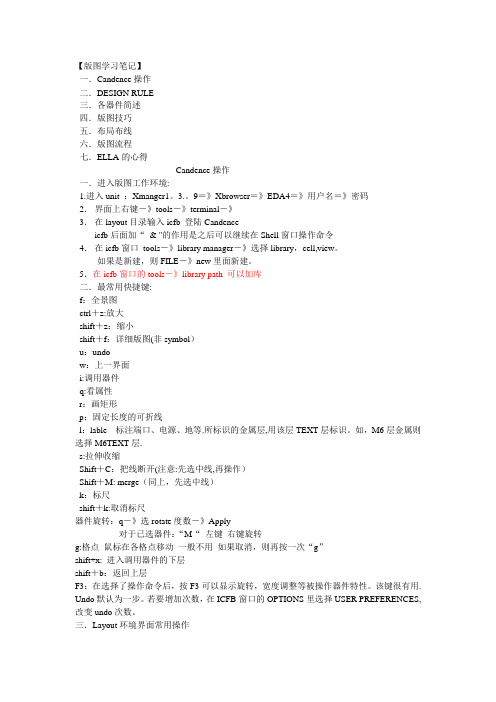

【版图学习笔记】一.Candence操作二.DESIGN RULE三.各器件简述四.版图技巧五.布局布线六.版图流程七.ELLA的心得Candence操作一.进入版图工作环境:1.进入unit :Xmanger1。

3.。

9=》Xbrowser=》EDA4=》用户名=》密码2.界面上右键-》tools-》terminal-》3.在layout目录输入icfb 登陆Candenceicfb后面加“& "的作用是之后可以继续在Shell窗口操作命令4.在icfb窗口tools-》library manager-》选择library,cell,view。

如果是新建,则FILE-》new里面新建。

5.在icfb窗口的tools-》library path 可以加库二.最常用快捷键:f:全景图ctrl+z:放大shift+z:缩小shift+f:详细版图(非symbol)u:undow:上一界面i:调用器件q:看属性r:画矩形p:固定长度的可折线l:lable 标注端口、电源、地等.所标识的金属层,用该层TEXT层标识。

如,M6层金属则选择M6TEXT层.s:拉伸收缩Shift+C:把线断开(注意:先选中线,再操作)Shift+M: merge(同上,先选中线)k:标尺shift+k:取消标尺器件旋转:q-》选rotate度数-》Apply对于已选器件:“M“左键右键旋转g:格点鼠标在各格点移动一般不用如果取消,则再按一次“g”shift+x: 进入调用器件的下层shift+b:返回上层F3:在选择了操作命令后,按F3可以显示旋转,宽度调整等被操作器件特性。

该键很有用. Undo默认为一步。

若要增加次数,在ICFB窗口的OPTIONS里选择USER PREFERENCES,改变undo次数。

三.Layout环境界面常用操作左边的窗口为“LSW”窗口.A V:all view NV:no view AS:all select NS:none select(在连线时,可以先选NV,所有层次都看不见,再选中需要连线的层次,则版图上只显示该层,方便连线。

版图设计培训资料

5) virtuoso编辑器 --版图层次显示(LSW)

技术中心内部资料

26

第二部分:版图设计基础

3. 版图编辑器

6) virtuoso编辑器 --版图编辑菜单

技术中心内部资料

27

第二部分:版图设计基础

3. 版图编辑器

7) virtuoso编辑器 --显示窗口

技术中心内部资料

28

7) virtuoso编辑器--CDL输出

技术中心内部资料

37

第二部分:版图设计基础

5. 了解工艺厂商

GLOBALFOUNDRIES

HHG —华虹宏力

--中芯国际 CSMC – 华润上华 FMIC—深圳方正 TSMC -- 台积电 UMC -- 台联电 Winbond -- 华邦 先锋 比亚迪 新进 厦门集顺 无锡和舰

3. 版图编础

3. 版图编辑器

cell

3) virtuoso编辑器-- 建立

CIW窗口

技术中心内部资料

24

第二部分:版图设计基础

3. 版图编辑器

4) virtuoso编辑器--工作区和层次显示器

LSW

技术中心内部资料

工作区域

25

第二部分:版图设计基础

2.2互连

1) 典型工艺

CMOS N阱 1P4M工艺剖面图

连线与孔之间的连接

技术中心内部资料 21

第二部分:版图设计基础

3. 版图编辑器

建立LIBRARY

1) virtuoso编辑器

CIW窗口

技术中心内部资料

22

第二部分:版图设计基础

2) virtuoso编辑器--Library manager

新手学版图—理解版图的层

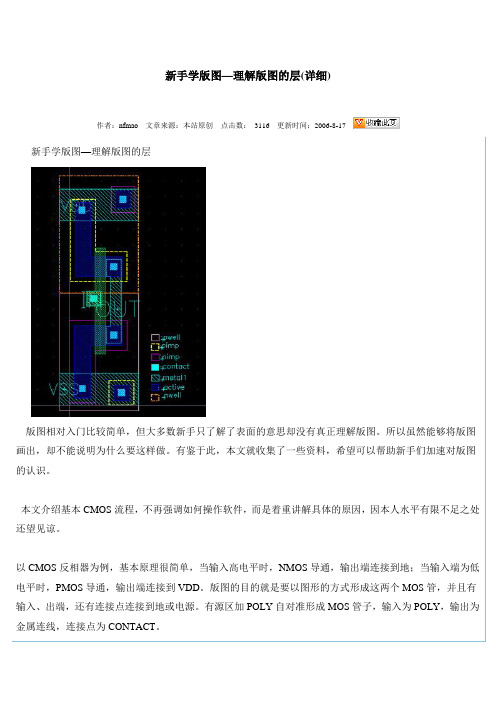

新手学版图—理解版图的层(详细)作者:nfmao 文章来源:本站原创 点击数: 3116 更新时间:2006-8-17新手学版图—理解版图的层版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS 流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS 反相器为例,基本原理很简单,当输入高电平时,NMOS 导通,输出端连接到地;当输入端为低电平时,PMOS 导通,输出端连接到VDD 。

版图的目的就是要以图形的方式形成这两个MOS 管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POLY 自对准形成MOS 管子,输入为POLY ,输出为金属连线,连接点为CONTACT 。

阻,光照射的区域可溶化,以此定位出开孔区域。

孔内金属是以MOCVD(金属有机化学气相沉积CVD)形式沉积金属W(钨),再以CMP方式打磨多余的金属。

濺射第一层金属,并以版图metal1层,刻画出金属连线。

覆盖CMP(介电层),以同样的方式开孔(版图via 1层),刻画第二层金属(版图metal2层)。

如果是完整的项目还要使用版图pass层开出PAD的位置,并进行钝化处理以PECVD(介质等离子体增强化学气相沉积)沉积氮化硅,以达到保护芯片的目的。

现在各层的作用已经有了说明,接下来将利用实际的作用来举例说明,层与层之间的关系。

1,版图P-well层,N-wel l层在衬底形成各自的阱区,它们之间的关系应该不能相互重叠。

2,因为器件形成在阱中,所以器件的图形必须被阱所覆盖,要么在P-well中,要么在N-well中。

3,P-well与P-well,N-well与N-well是否可以相连,取决于特性是否一致,比如相同的电位。

cxx版图学习初级(个人经验)

CXX版图设计学习目录1写在前面的话,一些感受、声明和注意事项2开始—画最简单的单元反相器3工艺层的相关知识1写在前面的话本人也是刚开始学习版图设计,但觉得版图的一些学习资料繁杂,难度深浅不一,对于一个新手来说很难通过这些学习资料自学成才,通过这一个多星期的学习,我将以自己独特的方式来组织这些学习资料,从而使得一个毫无基础的新手可以快速入门。

再次声明,这篇材料是各种版图资料的重新组合。

以后有什么想说的还会继续补充。

学习这种实践性很强的技术,只看书显然是不够的,必须要在软件上实际操作,通过不断的熟悉软件和设计规则来快速成为一名版图设计工程师。

本人的学习计划是实践+理论+实践+理论……2开始—画最简单的单元反相器Virtuoso Editing 的使用简介全文将用一个贯穿始终的例子来说明如何绘制版图。

这个例子绘制的是一个最简单的非门的版图。

§2-1 建立版图文件使用library manager。

首先,建立一个新的库myLib,关于建立库的步骤,在前文介绍cdsSpice 时已经说得很清楚了,就不再赘述。

与前面有些不同的地方是:由于我们要建立的是一个版图文件,因此我们在technology file 选项中必须选择compile a new tech file,或是attach to an exsiting tech file。

这里由于我们要新建一个tech file,因此选择前者。

这时会弹出load tech file的对话框,如图2-1-1 所示。

在ASCII Technology File 中填入csmc1o0.tf即可。

接着就可以建立名为inv的cell 了。

为了完备起见,读者可以先建立inv的schematic view和symbol view(具体步骤前面已经介绍,其中pmos 长6u,宽为0.6u。

nmos 长为3u,宽为0.6u。

model 仍然选择hj3p 和hj3n)。

地图基础知识

地图基础知识版图国家版图是指一个国家行使主权的疆域。

“版图”这个概念的产生,在中国可以追溯到夏代。

《周礼·夏官·司土》中的“掌群臣之版”,就是指主管各地的户籍名册(中国古代将名册或户籍记载于木片上进行管理,这种木片称之为“版”或“板”)。

周代实行分封制,由各诸侯国拥戴中央王朝,各诸侯国就将所管辖的疆域和各疆域内生活的人群开始进行分级管理。

《周礼·天官·司会》中,记载了“都”、“鄙”、“赞”、“里”等行政单位的范围和人员,相当于后世的行政区划图,这就是中国“版图”这一概念的开始。

从春秋战国直到秦汉,都有属国必须献版图的制度。

献版图就是献江山,“版图”一词以后就延伸为国家的疆域。

因此,正确表示和规范使用国家版图,自古以来就是十分严肃的事情。

地图按照一定的数学法则,运用符号系统、以图形或数字的形式表示具有空间分布特性的自然与社会现象的载体。

地图要素构成地图内容的基本要素,包括数学要素、地理要素和整饰要素(亦称辅助要素),所以又通称地图“三要素”。

地图分类分别以地图的内容、比例尺、制图区域范围、用途、介质表达形式和使用方法等作标志,将地图区分(或划分)为各种类型或类别。

按内容分为普通地图和专题地图。

普通地图反映地表基本要素的一般特征的地图。

它以相对均衡的详细程度表示制图区域各种自然地理要素和社会经济要素的基本特征、分布规律及其相互联系。

它的首要任务在于正确地反映地域分布规律和如实地表达区域地理特征。

因此,普通地图全面反映水系、地貌、土质、植被、居民地、交通线、境界及其他标志,而不是突出表示其中某一种要素。

他们在地图上表示的详细程度、精度、完备性、概括性和表示方法,在很大程度上取决于地图的比例尺。

一般地讲,地图比例尺愈大,表示的内容愈详细,随着地图比例尺的缩小,内容的概括程度也就相应地增大。

普通地图专题地图着重反映自然或社会现象中的某一种或几种专业要素,即集中表现某种主题内容的地图。

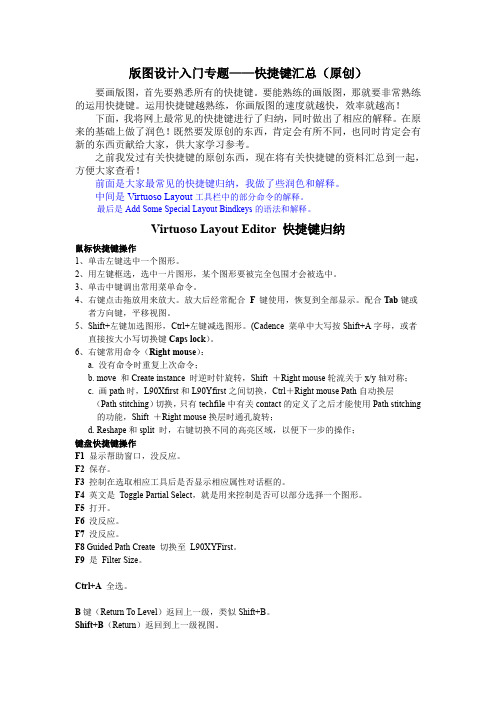

版图设计入门专题——快捷键汇总 原创

版图设计入门专题——快捷键汇总(原创)要画版图,首先要熟悉所有的快捷键。

要能熟练的画版图,那就要非常熟练的运用快捷键。

运用快捷键越熟练,你画版图的速度就越快,效率就越高!下面,我将网上最常见的快捷键进行了归纳,同时做出了相应的解释。

在原来的基础上做了润色!既然要发原创的东西,肯定会有所不同,也同时肯定会有新的东西贡献给大家,供大家学习参考。

之前我发过有关快捷键的原创东西,现在将有关快捷键的资料汇总到一起,方便大家查看!前面是大家最常见的快捷键归纳,我做了些润色和解释。

中间是Virtuoso Layout工具栏中的部分命令的解释。

最后是Add Some Special Layout Bindkeys的语法和解释。

Virtuoso Layout Editor快捷键归纳鼠标快捷键操作1、单击左键选中一个图形。

2、用左键框选,选中一片图形,某个图形要被完全包围才会被选中。

3、单击中键调出常用菜单命令。

4、右键点击拖放用来放大。

放大后经常配合F键使用,恢复到全部显示。

配合Tab键或者方向键,平移视图。

5、Shift+左键加选图形,Ctrl+左键减选图形。

(Cadence菜单中大写按Shift+A字母,或者直接按大小写切换键Caps lock)。

6、右键常用命令(Right mouse):a.没有命令时重复上次命令;b.move和Create instance时逆时针旋转,Shift+Right mouse轮流关于x/y轴对称;c.画path时,L90Xfirst和L90Yfirst之间切换,Ctrl+Right mouse Path自动换层(Path stitching)切换,只有techfile中有关contact的定义了之后才能使用Path stitching 的功能,Shift+Right mouse换层时通孔旋转;d.Reshape和split时,右键切换不同的高亮区域,以便下一步的操作;键盘快捷键操作F1显示帮助窗口,没反应。

地球版图和地理工具的使用技巧

地球版图和地理工具的使用技巧地球版图是一种用来展示地球表面的平面图,它可以帮助我们更好地了解地球的地理特征和地理位置。

而地理工具则是我们在使用地球版图时常常会用到的辅助工具。

在本文中,我将分享一些关于地球版图和地理工具的使用技巧,希望能对大家有所帮助。

一、地球版图的基本结构地球版图通常由经纬线、地理特征和地名等要素构成。

其中,经线是指连接地球南北两极的虚构线,而纬线则是连接地球东西两极的虚构线。

这些线条的交汇点被称为格点,通过格点我们可以确定一个地点的具体位置。

在使用地球版图时,我们可以根据经纬线的刻度来估算地点的经纬度,从而确定其位置。

二、地球版图的使用技巧1. 缩放功能:地球版图通常具有缩放功能,可以通过放大或缩小来调整地图的大小。

当我们需要查看特定地区的详细信息时,可以将地图放大;而当我们需要查看整个地球的概览时,可以将地图缩小。

这样可以更好地满足我们的需求。

2. 搜索功能:地球版图通常具有搜索功能,可以通过输入地名或地点的名称来快速定位。

这对于我们在查找特定地点时非常方便。

只需在搜索框中输入关键词,地球版图就会自动定位到相应的位置,并显示相关信息。

3. 测量工具:地球版图通常配备了测量工具,可以帮助我们测量距离、面积和方向等。

当我们需要计算两个地点之间的距离时,可以使用测量工具来准确测量。

这对于旅行规划或地理研究非常有用。

三、地理工具的使用技巧1. GPS导航仪:GPS导航仪是一种常用的地理工具,它利用卫星信号来确定地理位置,并提供导航指引。

在使用GPS导航仪时,我们可以输入目的地的坐标或地址,它会为我们规划最佳路线,并提供语音导航。

这对于驾车或步行导航非常有帮助。

2. 地图软件:地图软件是我们在手机或电脑上常用的地理工具,它可以提供实时的地图信息和导航功能。

通过地图软件,我们可以随时查看地图、搜索地点、规划路线等。

同时,地图软件还可以提供交通状况、公共交通线路和周边设施等信息,让我们更好地了解目的地。

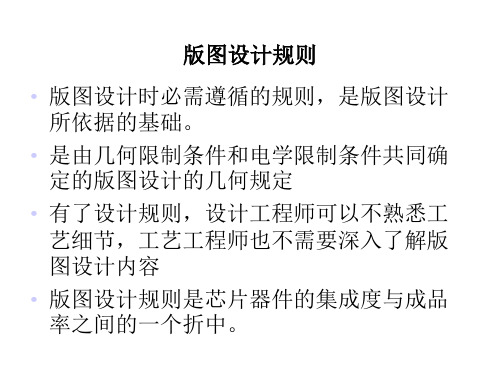

版图设计基础

• 交叠规则

• 两层之间交叠的最小尺寸。交叠规则定义 的两层为不同的层。

• 两层交叠,并且一层要伸出另一层的最小 尺寸

• 两层交叠,两层之间的最小尺寸

设计规则举例 • N阱层相关的设计规则及其示意图

• P+、N+有源区层相关的设计规则及其示意图

• Poly层相关的设计规则及其示意图

• Contact层相关的设计规则及其示意图

• Metal层相关的设计规则及其示意图

• Pad层相关的设计规则及其示意图

二、几何设计规则 -举例及问题讨论

当给定电路原理图设计其版图时,必须根据 所用的工艺设计规则,时刻注意版图同一层上 以及不同层间的图形大小及相对位置关系。然 而对于版图设计初学者来说,第一次设计就能 全面考虑各种设计规则是不可能的。为此,需 要借助版图设计工具的在线设计规则检查 (DRC)功能来及时发现存在的问题。

为了工艺上按比例缩小或版图编辑的需要, 合并接触采用图4.9(a)所示的分离式接触结 构,而不采用图4.9(b)的合并长孔结构。

版图的验证

• 版图设计完成后,还需要进行一系列的检 查和验证。

• 版图的验证包括:设计规则检查(DRC)、 电学规则检查(ERC)、版图参数提取以 及电路图与版图一致性检查(LVS)

• CIF格式 用文本命令来表示掩膜分层和版图图形,通过对 基本图形的描述、图形定义描述、附加图样调用 功能,可以实现对版图的层次性描述。采用字符 格式,可读性较强

EDIF格式 是电路的一种二进制描述,带有电路的单元符号 (symbol)信息,也是纯文本,主要用于电路数 据交换。EDIF文件可读性强

版图_基础篇

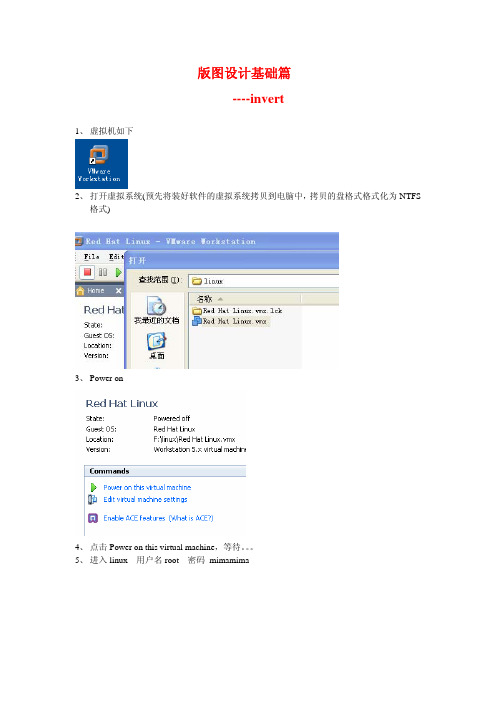

版图设计基础篇----invert1、虚拟机如下2、打开虚拟系统(预先将装好软件的虚拟系统拷贝到电脑中,拷贝的盘格式格式化为NTFS格式)3、Power on4、点击Power on this virtual machine,等待。

5、进入linux 用户名root 密码 mimamima6、显示桌面7、打开终端,右键选择open terminal8、Ls查看目录9、进入PDK文件夹 cd chrt1810、打开cadence icfb11、新建(打开(osc中有我做的例子))原理图12、File new library13、Name 选择attach to an existing techfile14、选择chrt18rf15、选择cellview16、选择刚新建的library,自命名cell name17、按i添加元件,或者选择add instance18、按browse选择选择library19、我们一般选择chrtbase和chrt18rf里的元器件,依次往右选,如上选择了chrtbase中MOS管,型号nmos-1p8,最后一栏选symbol,然后回到virtuoso schematic editing,点击左键即选中了该元件如下图20、选中器件按字母Q可以修改器件的属性,多MOS管而言一般是W,L,fingers,同样的方法选择其他器件修改属性。

21、save连线;左侧这几个功能经常用到22、 C 复制,p 添加pin(输入输出接口如下)23、输入四个pin name以空格隔开,direction 选择inputoutput,点击hide在virtuososchematic editing原理图中合适位置依次点击鼠标左键放置pin,然后连线如下图。

Save 至无错。

24、生成cellview供仿真调用,如下选择cellview,ok,ok,关闭生成的cellview和原理图invert25、可如下修改user preferences26、修改成10次,这个画错了,可以按u回到上一步,可回10步27、再新建一个原理图用来做前仿(原理图级仿真)28、这回可以在我们自己建的库里调出刚才画的反向器invert,方法同其他器件的添加,只是库选择mmlinvert,可按R再电击invert旋转器件。

新手学版图—认识保护环

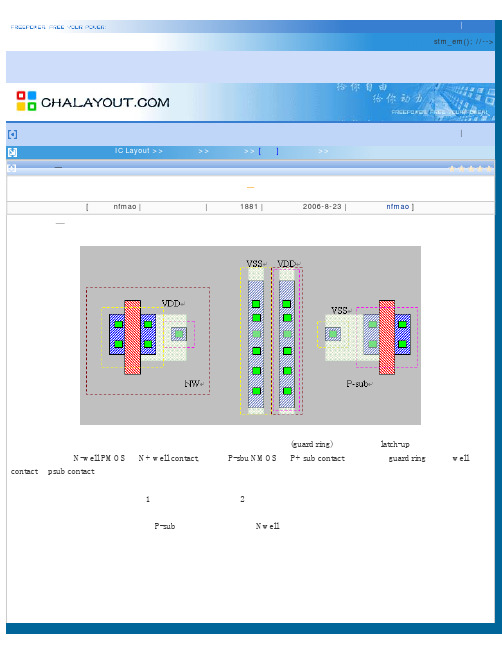

网站论坛| 旧讨论区stm_em(); //-->最新公告:当前没有任何公告!网站论坛| 加入收藏您现在的位置:纯粹的版图IC Layout >> 文章专栏 >> 物理版图 >> [专题]新手学版图 >> 正文新手学版图—认识保护环热新手学版图—认识保护环[ 作者:nfmao | 转贴自:本站原创 | 点击数:1881 | 更新时间:2006-8-23 | 文章录入:nfmao ]新手学版图—认识保护环上次我们讲到了版图各层的具体作用,本篇要介绍的是如何放置保护环(guard ring) 来正确防护latch-up。

上图是典型的版图结构,左边是N-well PMOS 加 N+ well contact, 右边是P-sbu NMOS 加 P+ sub contact,中间就是guard ring,当然well contact 、psub contact 也是保护的一部分,只不过没有画成环状而已,不能忽略。

保护环的基本概念主要分成两种:1,多数载流子保护环;2,少数载流子保护环。

多数与少数是相对的,比如:电子在P-sub中为少数载流子到了Nwell中就是多数载流子了。

那么保护环到底发挥着什么作用呢?画出上图的剖面图来更用助于我们理解。

将中间的保护环暂时拿掉,分析其中的寄生情况。

为了不让情况变得复杂,我们只描述主要的寄生情况。

其中Nwell中的P + 、Nwell、P-sub组成纵向的PNP,Nwell中的P+为发射极。

另外P-sub中的N+、P-sub、Nwell组成横向的NPN,P-sub中的N +为发射极。

简单理解就是MOS的源/漏极作为了寄生三极管的发射极。

(注意源漏是存在差异的)少数载流子保护环是掺杂不同类型杂质,形成反偏结提前收集引起闩锁的注入少数载流子。

多数载流子保护环是掺杂相同类型杂质,减小多数载流子电流产生的降压。

以剖面图为例,P-sub中的N+区的电子注入经P-sub扩散,大多数电子到达Nwell-Psub结,并在电压的作用下加速漂移到Nwell中,电子进入Nwell在被最后收集的时候,便会形成压降,导致寄生PNPN结构发生latchup。

版图设计基础new

硅芯片上的电子世界--电容

• 电容:一对电极中间夹一层电介质的三明治结构; • 硅芯片上的薄膜电容:

几十微米

上电极:金属或多晶硅 氧化硅电介质 下电极:金属或多晶硅 硅片

• 集成电路中的集成电容

• 金属-金属(多层金属工艺,MIM) • 金属-多晶硅 • 多晶硅-多晶硅(双层多晶硅工艺,PIP)

方块电阻: R=ρL/S=ρL/dW=(ρ/d)L/W R = ρ/d R=R L/W 方块电阻与半导体的掺杂水平和掺杂区的结深有关 对于集成电路来说,方块电阻是基本单位,量纲是Ω/ 只要知道材料的方块电阻,就可以根据所需要的电阻值计算 出电阻的方块数,即电阻条的长度和宽度比 栅极多晶:2-3 Ω/ ;金属:20-100m Ω/ 多晶:20-30 Ω/ ;扩散区:2-200 Ω/

接触孔层和通孔层

• 接触孔包括有源区接触孔(Active Contact)和多晶硅接 触孔(poly contact) • 有源区接触孔用来连接第一层金属和N+或P+区域,在版 图设计中有源区接触孔的形状通常是正方形。 • 应该尽可能多地打接触孔,这是因为接触孔是由金属形成, 存在一定的阻值,假设每个接触孔的阻值是R,多个接触 孔相当于多个并联的电阻

版图设计(物理层设计)

• 版图设计的目标:实现电路正确物理连接,将设计好的 电路映射到硅片上进行生产。芯片面积最小,性能优化 (连线总延迟最小) 集成电路设计的最终目标

• 版图设计的重要性:

电路功能和性能的物理实现;

布局、布线方案决定着芯片正常工作、面积、速度; • 经验很重要。 版图设计包括: 基本元器件版图设计; 布局和布线; 版图检验与分析。

绘图层

• • • • • • • • • • N阱层(N Well) 有源区层(Active) 多晶硅栅层(Poly) P选择层(P Select) N选择层(N Select) 接触孔层(Contact) 通孔层(Via) 金属层(Metal) 文字标注层(Text) 焊盘层(Pad)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

新手学版图--几种电阻的画法刚好Module 部门要画test key 测试新制程对器件的影响,其中就有一部分是画不同类型的电阻。

这些电阻有:poly电阻,nwell电阻,pplus电阻,nplus电阻。

上图即为这几种电阻的画法,除poly 电阻外,其他三种电阻的画法是值得推敲的。

电阻三端分别定义为force ,sense 和sub。

我们来分析这三种电阻。

nwell 电阻:问题1:为什么force ,sense 端要加thin oxide 和nplus?问题2:为什么要用nplus 而不用pplus?Pplus 电阻:问题1:为什么要画在nwell 中?问题2:为什么 sub 要接高电位?问题3:为什么电阻中间要用thin oxide 连接?Nplus 电阻:问题1:可不可以画在nwell 中?其实以上问题的重点1是要理解thin oxide 的作用,以及nwell , p+/N+ plus 在制造过程中所处的步骤。

thin oxide 可以理解为去除FOX。

nwell 在制造的前端就形成了,FOX不会对此造成影响。

而P+/N+ plus 会受FOX的影响,如果F OX阻挡的话,wafer 上就不会形成相应的P型或N型。

重点2即是否会出现不正确的导通。

回答完这些问题之后,我们可以联想到加guard ring时的一些情况。

就p-sub /n well CMOS 版图而言,少数载流子guard ring 为nwell + nplus + thin oxide + VDD, 多数载流子guard ring 为 pplus + thin oxide + VSS。

讨论当两种guard ring thin oxide 不连续时的不同影响。

新手学版图—理解版图的层版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS反相器为例,基本原理很简单,当输入高电平时,NMOS导通,输出端连接到地;当输入端为低电平时,PMOS导通,输出端连接到VDD。

版图的目的就是要以图形的方式形成这两个MOS管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POLY自对准形成MOS管子,输入为POLY,输出为金属连线,连接点为CONTACT。

首先创建新的cell view背景代表P型衬底,材料为Si-100 电阻率约5-10Ωcm,清洗后生长约200Å氧化层,再以LPCVD(低压化学气相沉积)沉积氮化硅约800 A。

Wafer厚度大约为750um,但最后打磨贴片后的厚度大约只有约250um。

(10 000A=1um)1、氧化层的应用大致可分为:屏蔽、遮蔽、场区及局部绝缘、衬垫、缺陷去除、栅介电层、浅沟槽阻挡,厚度依次约为200A、5000A、3000-5000A、100-200A、<1000A、30-120A、100-200A。

2、氮化物一般较为致密,所以可以用来隔离、阻挡,以及CMP的停止层。

3、涂布光阻、曝光、显影,以氮化物等离子体干法刻蚀去除氮化硅,剥离光阻(以下将省略一些层的去除过程)。

版图Active层将定位出有源区,非有源区将通过LOCOS(硅的局部氧化)生长场氧化层,厚度大约3000-10000A。

不过因该过程存在鸟嘴效应及表面平坦度问题,90年代后已经由STI(淺沟槽绝缘)所取代。

版图P-well层定位P-well区域,在这一区域离子植入B+/225KeV/3x10^13cm^-2。

用版图N-well层定位N-well区域,离子植入P+/600KeV/2x10^13cm^-2。

以P/250/2x10^12 + P/1200/3x10^13 + 950C,30min,为例最后深度大约2um,方块电阻790ohms。

传统工艺制成的阱区深度约4um左右。

阱区形成后还可能进行阈值调整处理,这一步不需要版图层的参与。

版图Poly层定位poly及gate,不过在形成channel(沟道)之前,必须生长出一层优质的氧化层,这一层的厚度约30-120A,可能实际测量出来只有十几埃。

在这一层上以LPCVD沉积多晶硅约0.5um,并对poly掺杂P/30/5x10^15。

因为多晶硅各向异性所以采用RIE(反应离子刻蚀)方法进行刻蚀。

自对准形成源、漏极,被poly层挡住与active层重叠的下面将会是MOS的沟道,剩下的active 区域将形成源、漏极。

为了抑制热电子或热载流子效应要通过LD D(轻掺杂漏极)首先进行轻掺杂,然后在栅上形成侧墙后再以低能量、高电流来形成源漏区,这样会形成一个梯度。

版图P-imp层决定形成P+型,离子植入B /10/2x10^15,版图N-imp层决定形成N+型,离子植入As/30/3x10^15。

通常该区域的深度在2um左右。

此时器件已经基本形成,之后要为连接作好准备。

在表面濺射一层金属层(比如T i),在与硅接触的表面反应形成金属硅化物(silicide),在外表面形成TiN。

如果栅、源、漏极都有silicide 俗称为salicide,如果只形成在多晶硅上称为polycide。

表面平坦化处理时,可以通过加热掺杂的BPSG(硼磷硅玻璃)软化流动,或以C MP(化学机械研磨)以达到表面平坦化。

版图contact层定位连接孔,contact光掩膜通常采用Dark形式,即图形区域透光,背景不透光,配合正光阻,光照射的区域可溶化,以此定位出开孔区域。

孔内金属是以MOCVD(金属有机化学气相沉积CVD)形式沉积金属W(钨),再以C MP方式打磨多余的金属。

濺射第一层金属,并以版图metal1层,刻画出金属连线。

覆盖CMP(介电层),以同样的方式开孔(版图via1层),刻画第二层金属(版图metal2层)。

如果是完整的项目还要使用版图pass层开出PAD的位置,并进行钝化处理以P ECVD(介质等离子体增强化学气相沉积)沉积氮化硅,以达到保护芯片的目的。

现在各层的作用已经有了说明,接下来将利用实际的作用来举例说明,层与层之间的关系。

1,版图P-well层,N-wel l层在衬底形成各自的阱区,它们之间的关系应该不能相互重叠。

2,因为器件形成在阱中,所以器件的图形必须被阱所覆盖,要么在P-well中,要么在N-well中。

3,P-well与P-well,N-well与N-well是否可以相连,取决于特性是否一致,比如相同的电位。

4,P-imp,N-imp层要比相对的active 大。

否则未覆盖的区域将没有离子植入。

5,因为自对准工艺,在形成channel的地方,poly要横跨过active层。

没有c hannel的地方避免接触。

6,contact层必须与metal层或poly层要有接触(在需要连接的地方)。

传统的“钉头”形式需要金属覆盖住contact。

新手学版图—理解版图的层版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS反相器为例,基本原理很简单,当输入高电平时,NMOS导通,输出端连接到地;当输入端为低电平时,PMOS导通,输出端连接到VDD。

版图的目的就是要以图形的方式形成这两个MOS管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POLY自对准形成MOS管子,输入为POLY,输出为金属连线,连接点为CONTACT。

首先创建新的cell view背景代表P型衬底,材料为Si-100 电阻率约5-10Ωcm,清洗后生长约200Å氧化层,再以LPCVD(低压化学气相沉积)沉积氮化硅约800 A。

Wafer厚度大约为750um,但最后打磨贴片后的厚度大约只有约250um。

涂布光阻、曝光、显影,以氮化物等离子体干法刻蚀去除氮化硅,剥离光阻(以下将省略一些层的去除过程)。

版图Active层将定位出有源区,非有源区将通过LOCOS(硅的局部氧化)生长场氧化层,厚度大约3000-10000A。

不过因该过程存在鸟嘴效应及表面平坦度问题,90年代后已经由STI(淺沟槽绝缘)所取代。

版图P-well层定位P-well区域,在这一区域离子植入B+/225KeV/3x10^13cm^-2。

用版图N-well层定位N-well区域,离子植入P+/600KeV/2x10^13cm^-2。

以P/250/2x10^12 + P/1200/3x10^13 + 950C,30min,为例最后深度大约2um,方块电阻790ohms。

传统工艺制成的阱区深度约4um左右。

阱区形成后还可能进行阈值调整处理,这一步不需要版图层的参与。

版图Poly层定位poly及gate,不过在形成channel(沟道)之前,必须生长出一层优质的氧化层,这一层的厚度约30-120A,可能实际测量出来只有十几埃。

在这一层上以LPCVD沉积多晶硅约0.5um,并对poly掺杂P/30/5x10^15。

因为多晶硅各向异性所以采用RIE(反应离子刻蚀)方法进行刻蚀。

自对准形成源、漏极,被poly层挡住与active层重叠的下面将会是MOS的沟道,剩下的active 区域将形成源、漏极。

为了抑制热电子或热载流子效应要通过LD D(轻掺杂漏极)首先进行轻掺杂,然后在栅上形成侧墙后再以低能量、高电流来形成源漏区,这样会形成一个梯度。

版图P-imp层决定形成P+型,离子植入B /10/2x10^15,版图N-imp层决定形成N+型,离子植入As/30/3x10^15。

通常该区域的深度在2um左右。

此时器件已经基本形成,之后要为连接作好准备。

在表面濺射一层金属层(比如T i),在与硅接触的表面反应形成金属硅化物(silicide),在外表面形成TiN。

如果栅、源、漏极都有silicide 俗称为salicide,如果只形成在多晶硅上称为polycide。

表面平坦化处理时,可以通过加热掺杂的BPSG(硼磷硅玻璃)软化流动,或以C MP(化学机械研磨)以达到表面平坦化。

版图contact层定位连接孔,contact光掩膜通常采用Dark形式,即图形区域透光,背景不透光,配合正光阻,光照射的区域可溶化,以此定位出开孔区域。

孔内金属是以MOCVD(金属有机化学气相沉积CVD)形式沉积金属W(钨),再以C MP方式打磨多余的金属。