NXPLPC111x芯片中文手册―11带SSP的SPI01

NXP i.MX RT系列产品外部存储器烧写说明说明书

by:NXP Semiconductors1简介i.mx rt 系列产品是NXP 生产的业界第一款跨界处理器,这篇文档将介绍如何将一个可执行文件烧写进外部存储器。

为了烧写程序进flash,并且从flash 启动和调试,首先需要新型的Dap-link 固件和SDK 文件。

这篇文档说明了怎样去编译,调试,和配置FLEXSPI NOR Flash。

有关HyperFlash,和MfgTool 资料,可以参考How to Enable Boot from Octal SPI Flash and SD Card (文档AN12107)和How to Enable Boot from QSPI Flash (文档AN12108)。

该文档所使用的案例基于MIMXRT1050 SDK (版本:2.3.1),开发环境是IAR Embedded Workbench 8.22.1。

使用的硬件平台是IMXRT1050-EVKB。

2MIMXRT1050 EVK 设置在这块EVK 上有两块板载flash:Hyper Flash 和QSPI NOR Flash。

其中的默认flash 是Hyper Flash。

如果需要使能板载的QSPI NOR Flash,EVK 需要做出一些修改。

2.1EVK 设置1.首先需要移除板载的Hyper Flash,否则它会影响QSPI NOR Flash 的读写时序。

目录1简介.................................................12MIMXRT1050 EVK 设置..................12.1EVK 设置......................................12.2EVKB 设置...................................33XIP 启动流程...................................34更新OpenSDA 固件........................75例子.................................................75.1为XIP 启动工程添加或者移除启动头文件.........................................75.2将可执行文件烧录进板载Hyper Flash..........................................105.3将可执行文件烧录进板载QSPI NOR Flash.................................105.4烧录可执行文件进入一个新的QSPI NOR Flash.................................125.5使用MCUXpresso IDE 烧录可执行文件进一个新的QSPI NOR Flash ...................................................145.6修改启动头文件使其支持NOR flash XIP 启动 (156)历史版本 (20)AN12183怎样在FLEXSPI NOR Flash 模式下使能调试Rev. 1 — 10/2019Application Note图 1.移除 Hyper Flash2. 图 2 中的 R153-R158 位置焊接阻值为 0Ω 的电阻。

lpc1111.lpc1112.lpc1113.lpc1114

HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body 7 x 7 x 0.85 mm

capabilities (second SPI on LQFP48 and PLCC44 packages only). I2C-bus interface supporting full I2C-bus specification and Fast-mode Plus with a

data rate of 1 Mbit/s with multiple address recognition and monitor mode. Other peripherals:

HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body 7 x 7 x 0.85 mm

HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body 7 x 7 x 0.85 mm

instruction set and memory addressing together with reduced code size compared to

existing 8/16-bit architectures.

LPC1114的IO配置部分的中文手册

表111. LPC111x 引脚配置引脚配置--图8–10引脚描述表8–114引脚配置--图8–10引脚描述表8–114引脚配置图8–8-图8–10引脚描述表8–112表8–114图8–10表8–112表8–113表8–1143. LPC111x 引脚描述表 112. LPC1113/14 引脚描述表 (LQFP48 封装)RESET — 外部复位输入:此引脚上的低电平会使设备复位,I/O 端口和外设复位成初始的默认状态,并使处理器从0地址开始执行。

I/O PIO0_0 — 通用数字输入/输出引脚。

PIO0_1/CLKOUT/ CT32B0_MAT2PIO0_2/SSEL0/ CT16B0_CAP04[1]I/O PIO0_1 —通用数字输入/输出引脚。

复位时低电平启动在线系统编程命令处 理程序。

O CLKOUT — 时钟输出脚。

OCT32B0_MAT2 —32位定时器0匹配输出2。

10[1]I/O PIO0_2 —通用数字输入/输出引脚。

O SSEL0 —SPI0从机选择。

ICT16B0_CAP0 —16位定时器0捕获输入0。

PIO0_314[1] I/OPIO0_3 —通用数字输入/输出引脚。

.I/O SCK0 —SPI0串行时钟。

PIO0_7/CTS 23[1] I/O PIO0_7 —通用数字输入/输出引脚(大电流输出驱动器)。

I CTS —UART清除发送。

PIO0_8/MISO0/CT16B0_MAT0PIO0_9/MOSI0/CT16B0_MAT1 SWCLK/PIO0_10/ SCK0/CT16B0_MAT2TDI/PIO0_11/AD0/CT32B0_MAT3 TMS/PIO1_0/AD1/CT32B1_CAP0 TDO/PIO1_1/AD2/CT32B1_MAT0TRST/PIO1_2/AD3/CT32B1_MAT1 27[1] I/O PIO0_8 —通用数字输入/输出引脚。

NXP LPC111x芯片中文手册—11 带SSP的SPI01

h u t.e d u.c n1.如何阅读本章所有LPC111x系列中的SPI模块均相同。

第二个SPI模块,SPI1,只存在于LQFP48和PLCC44封装上,在HVQFN33封装上则没有。

注释:两个SPI模块都包含全部的SSP特征集,所有相关寄存器都使用SSP前缀命名。

2.特性•兼容Motorola SPI、4线TI SSI和美国国家半导体公司的Microwire总线。

•同步串行通信。

•支持主机和从机操作。

•收发均有8帧FIFO。

•每帧有4-16位数据。

3.基本描述SPI/SSP是一个同步串行端口(SSP)控制器,可控制SPI、4线SSI和Microwire总线。

它可以与总线上的多个主机和从机相互作用。

在数据传输过程中,总线上只能有一个主机与一个从机进行通信。

原则上数据传输是全双工的,4~16位帧的数据由主机发送到从机或由从机发送到主机。

但实际上,大多数情况下只有一个方向上的数据流包含有意义的数据。

LPC111x系列处理器有两个SPI/同步串行端口控制器。

u p.wu p .wh ut.ed u.c n4.引脚描述表161622.SPI引脚描述SCK0/1I/O SCK CLK SK串行时钟。

SCK/CLK/SK是用来同步数据传输的时钟信号。

它由主机驱动,从机接收。

当使用SPI接口时,时钟可编程为高电平有效或低电平有效,否则总是高电平有效。

SCK仅在数据传输过程中切换。

在其它时间里,SPI/SSP接口保持无效状态或不驱动它(使其处于高阻态)。

SSEL0/1I/O SSEL FS CS帧同步/从机选择。

当SPI/SSP接口是总线主机时,它在串行数据启动前驱动该信号为有效状态。

在数据发送出去之后又将该信号恢复为无效状态。

该信号的有效状态根据所选的总线和模式可以是高或低。

当SPI/SSP接口作为总线从机时,该信号根据使用的协议来判断主机数据的存在。

当只有一个总线主机和一个总线从机时,来至主机的帧同步信号或从机选择信号直接与从机相应的输入相连。

LPC111x 产品数据手册

LPC1111/12/13/14 32-位 ARM Cortex-M0 微控制器

4. 订购信息

表1 订购信息 器件编号 LPC1111FHN33/101 LPC1111FHN33/102 LPC1111FHN33/201 LPC1111FHN33/202 LPC1112FHN33/101 LPC1112FHN33/102 LPC1112FHN33/201 LPC1112FHN33/202 LPC1113FHN33/201 LPC1113FHN33/202 LPC1113FHN33/301 LPC1113FHN33/302 LPC1114FHN33/201 LPC1114FHN33/202 LPC1114FHN33/301 LPC1114FHN33/302 LPC1113FBD48/301 LPC1113FBD48/302 LPC1114FBD48/301 LPC1114FBD48/302 LPC1114FA44/301[1] LPC1114FA44/302[1] [1] 名称 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 LQFP48 LQFP48 LQFP48 LQFP48 PLCC44 PLCC44 封装信息 描述 HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm LQFP48:塑料薄型QFP;48 条引线;裸片尺寸:7×7 ×1.4mm LQFP48:塑料薄型QFP;48 条引线;裸片尺寸:7×7 ×1.4mm LQFP48:塑料薄型QFP;48 条引线;裸片尺寸:7×7 ×1.4mm LQFP48:塑料薄型QFP;48 条引线;裸片尺寸:7×7 ×1.4mm PLCC44:带引线的塑料芯片载体;44 条引线 PLCC44:带引线的塑料芯片载体;44 条引线 版本 n/a n/a n/a n/a n/a n/a n/a n/a n/a n/a n/a n/a n/a n/a n/a n/a sot313-2 sot313-2 sot313-2 sot313-2 sot187-2 sot187-2

深圳颢天成 LPC11CxxDemo-V1 开发板说明书

LPC11CxxDemo-V1开发板用户手册V1.0深圳颢天成科技有限公司1 概述1.1简介LPC11CxxDemo-V1深圳市颢天成科技有限公司推出的一款基于NXP公司LPC11Cxx 系列处理器(Cortex-M0内核)的全功能评估板。

该板功能接口丰富,是一个应用开发好平台,也是学习者的首选。

配合JLINK、ULINK调试工具一起使用,更方便开发调试,所有的例程都是MDK下的完整工程,从而为自己的应用开发节省了时间,提高了效率。

1.2 硬件资源列表●LPC11Cxx(32位RISC性能处理器)32位ARM Cortex-M0结构优化●4个LED发光管,1个电源发光管●1个mini型USB插座,支持全速USB 2.0●1个RESET按键,1个ISP按键,1个WAKEUP按键,1个普通按键●1个UART支持RS-232●SSP接口●I2C接口●8通道10位ADC模块●1个JTAG/SWD调试接口●供电方式:USB供电1.3 软件资源列表例程名称 测试功能描述Blinky LED灯闪烁GPIO GPIO口边沿中断触发SSP SSP同步串行通讯SysTiick 通过系统滴答延时实现LED灯闪烁Timer32 通过32位定时器延时实现LED灯闪烁UART UART串口发送接收字符WDT 看门狗定时器应用实例I2C I2C主模式测试1.4 产品清单核对:LPC11CxxDemo-V1开发板1块128*64的LCD屏1块交叉串口线1条USB A-B线1根LPC11Cxx Demo-V1光盘一张1.5 使用入门1.5.1 电源LPC11CxxDemo-V1评估板采用USB供电方式,通过主板上的USB Device端口供电,供电正常时,评估板上的电源指示灯亮。

1.5.2 连接PC端推荐使用KEIL集成开发环境,通过JTAG连接仿真器到评估板,即可进行应用程序的调试和开发。

1.5.3 硬件原理:参加原理图1.5.4 镜像文件:编译好的可直接下载运行HEX文件1.6 出厂设置和硬件测试1)跳线J5 OFF不连接,不使用ISP下载2)串口1在一些例程中作为实验板与PC机的交互接口。

NXP芯片手册1

LPC1114教程原创

设置成数字 IO 就可以使用了。让然在使用别的复用功能时也一样首先需要设置

IO 配置寄存器将管脚设置在你需要的复用功能上。

下面就该了解一下通用 GPIO 的寄存器了,在通用的 GPIO 寄存器中分两部分,

一部分是数字功能,一部分是中断功能(这一节暂且不讨论),数字功能主要由

2 个寄存器构成,一个是方向寄存器 DIR 一个是数据寄存器 DATA,方向寄存器

九、LED 指示灯 在我们的开发板上有 3 个普通 LED 灯,是通过 IO 口直接控制的,采用的是灌电 流的方式驱动的。电路原理图如图所示:

பைடு நூலகம்

十、按键电路 开发板上有 3 个普通按键,通过这 3 个普通的按键可以做按键实验,熟悉按键的 读取方式。连接管脚如图所示:

十一、SD 卡接口 本开发板支持大容量的 SD 卡读写,这样我的再多的数据都可以通过 SD 卡保存 了,一些图片等信息也可以通过存储在SD卡中保存。SD卡通过 SPI 总线操作。 接口原理图如下:

口,这样你就可以在你的电脑上看见一个虚拟的移动存储器了,把里面的固件删 除,复制上你的新固件(程序),整个下载过程就完成了,怎么样简单吧!如果 还不明白那就看看 ZLG 或者 NXP 关于 USB 下载的文档哈! 六、一直都有的 24c02 24c02 是一种 IIC 协议的 EEPROM 存储芯片,芯片本身很便宜,在开发板上的低 位却不低,几乎所有的开发板都有它的踪迹,这是由于 2 个原因,一是通过一个 IIC 总线的器件可以学习 IIC 协议和内置 IIC 控制器的学习,二是在 MCU 运行的 过程中有很多数据是需要 EEPROM 保存的。基于这两个原因这个小芯片一直存 在于各个开发板就不奇怪了。下面是 24c02 部分的原理图。

DS-LPC11U14使用手册

鼎尚LPC11U14开发板使用手册版本 V1.5(2012/11)苏州鼎尚信息技术有限公司版权所有Copyright© 2012 苏州鼎尚信息技术有限公司Copyright© 2012 Suzhou Dingsung Information Technology Co.,Ltd. All Rights Reserved目录一、概述 (3)二、芯片特性 (3)三、开发板简介 (5)I、使用板载仿真器下载或调试程序 (6)1、板载仿真器介绍 (6)2、确定使用的Keil版本 (6)3、安装CoLinkEx调试软件 (6)4、使用USB连接线连接仿真器与电脑 (7)5、设置“Project/Options/Debug/Coocox Debugger”对话框 (7)6、设置“Project/Options/Utilities/Coocox Debugger”对话框 (8)7、在Keil工程中下载程序 (9)8、在Keil环境中仿真程序 (10)II、使用Flash Magic下载程序到开发板 (12)四、使用例程说明 (13)●1-1-led-blinky (13)●1-2-led-systick (17)●1-3-led-key (19)●2-2-uart-shell (22)●2-3-uart-rs485 (25)●3-1-key-wakeup (27)●4-1-usb-hid (27)●4-2-usb-msc (29)●4-3-usb-cdc (31)●4-4-usb-audio (32)●5-1-IIc (35)●6-1-ssp (35)一、概述苏州鼎尚信息技术有限公司出品的LPC11U14开发板采用NXP ARM Cortex-M0为核心的LPC11U14芯片。

LPC11U14芯片性能卓越、简单易用、功耗低、能显著降低8/16位应用的代码长度,它的价值和易用性比现有的8位/16位微控制器更胜一筹。

LPC1114

00 P = 1

01 P = 2

10 P = 4

11

P=8

-

保留. 不要将1写到这些保留位中。

0x00 0x0

4.4 系统 PLL状态寄存器

User manual

Rev. 00.10 — 11 January 2010

© NXP B.V. 2010. All rights reserved.

10 of 326

此LPC111X 数据手册之中文翻译,由武汉理工大学UP团队友情提供,仅供学习交流之用,欢迎指正,共同修改完善。

NXP Semiconductors

0

复位SPI0外设。

1

SPI0 复位失效。

1

I2C_RST_N

I2C复位控制

0x1

0

复位I2C 外设。

1

I2C 复位失效。

UM10398_0

User manual

Rev. 00.10 — 11 January 2010

© NXP B.V. 2010. All rights reserved.

13 of 326

-

0x0DC

保留

R/W

0x0E0

CLKOUT时钟源选择

R/W

0x0E4

CLKOUT时钟源更新允许

R/W

0x0E8

CLKOUT时钟分频器

-

0x0EC - 0x0FC 保留

R

0x100

POR捕获PIO状态0

R

0x104

POR捕获PIO状态1

0x000 0x000 0x000 0x000 0x001 0x85F 0x000 0x000 0x000 0x000 0x000 0x000 0x000 0x000 0x000 依赖用户

NXP mcu

TinyM0核心板电路为LPC111x芯片的最小系统,硬件支持2.54mm间距的 标准排针。用户可以将TinyM0核心板配套自行设计的底板进行产品开发。 ● 支持多款芯片

和16位竞争产品的2至4倍。

Cortex-M0内核

● 32位ARM RISC处理器,16位Thumb指令集; ● 功耗与面积高度优化,设计专用于低成本、低功耗场合; ● 24位SysTick定时器; ● 32位硬件乘法器; ● 中断现场自动保存,有处理决定性、固定延迟的中断能力; ● 系统接口支持小端或字节不变的大端数据访问; ● SWD串行线调试。

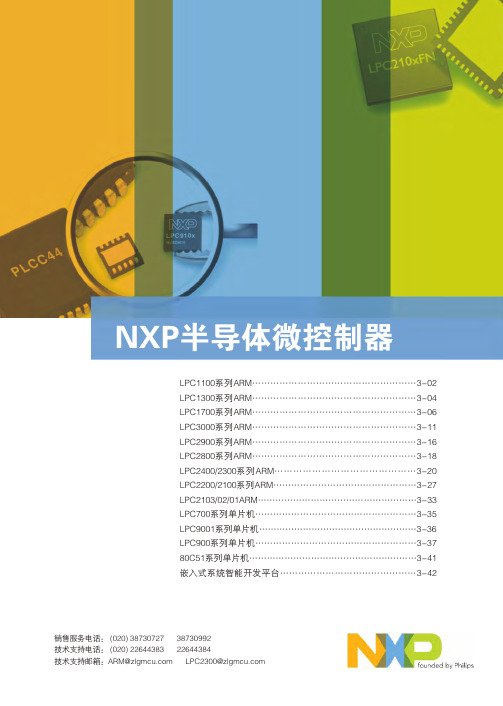

LPC1300选型表:

器件型号 LPC1343 LPC1342 LPC1313 LPC1311

Flash (KB) 32 16 32 8

SRAM(KB) 8 4 8 2

USB 2.0 Device Device

-

I2C(Fast+) 1 1 1 1

ADC 8ch/10bit 8ch/10bit 8ch/10bit 8ch/10bit

置的新型开漏工作模式

LPC1100

◎ 四个通用计数器/计数器 ◎ 可编程的看门狗定时器(WDT),带锁死功能 ◎ 系统计时器 ◎ 各外设自带时钟分频器,有利于降低功耗

芯片特色:

Cortex-M0处理器性能 ● Cortex-M0微控制器可以轻松超越高端8位和16位器件的

性能水平; ● 内核额定性能为0.9DMIPS/MHz,相当于与其最接近的8位

NXP LPC111x芯片中文手册―11 带SSP的SPI01

up .w hd 1. 如何阅读本章所有 LPC111x 系列中的 SPI 模块均相同。

第二个 SPI 模块, SPI1,只存在于LQFP48和 PLCC44封装上,在 HVQFN33封装上则没有。

注释:两个 SPI 模块都包含全部的 SSP 特征集,所有相关寄存器都使用 SSP 前缀命名。

2. 特性• 兼容 Motorola SPI 、 4线 TI SSI 和美国国家半导体公司的 Microwire 总线。

• 同步串行通信。

• 支持主机和从机操作。

• 收发均有 8帧 FIFO 。

•每帧有 4-16位数据。

3. 基本描述SPI/SSP是一个同步串行端口 (SSP控制器,可控制 SPI 、 4线 SSI 和 Microwire 总线。

它可以与总线上的多个主机和从机相互作用。

在数据传输过程中,总线上只能有一个主机与一个从机进行通信。

原则上数据传输是全双工的, 4~16位帧的数据由主机发送到从机或由从机发送到主机。

但实际上,大多数情况下只有一个方向上的数据流包含有意义的数据。

LPC111x 系列处理器有两个 SPI/同步串行端口控制器。

u d u UM10398Semiconductors LPC1100开发,尽在第 11章 :LPC111x 带有 SSP 的 SPI0/1 4. 引脚描述表 161622. SPI 引脚描述SCK0/1I/OSCK CLK SK 串行时钟。

SCK/CLK/SK是用来同步数据传输的时钟信号。

它由主机驱动,从机接收。

当使用 SPI 接口时,时钟可编程为高电平有效或低电平有效,否则总是高电平有效。

SCK 仅在数据传输过程中切换。

在其它时间里, SPI/SSP接口保持无效状态或不驱动它(使其处于高阻态。

SSEL0/1I/OSSEL FS CS 帧同步 /从机选择。

当 SPI/SSP接口是总线主机时,它在串行数据启动前驱动该信号为有效状态。

在数据发送出去之后又将该信号恢复为无效状态。

南京日新 NXP单片机 LPC2101 2102 2103 说明书

NXP单片机 LPC2101/2102/2103用户使用手册供应商:江苏省南京市地址:南京市江宁区胜利路19号联系人:李先生PHILIPS单片16/32位微控制器-LPC2101/2102/21031.概述 (3)2.特性 (3)2.1主要特性 (3)3.订购信息 (4)3.1订购选项 (4)4.结构框图 (5)5.管脚信息 (6)5.1管脚排列 (6)5.2管脚描述 (7)6.功能描述 (10)6.1结构概述 (10)6.2片内FLASH程序存储器 (10)6.3片内静态RAM (11)6.4存储器映射 (11)6.5中断控制器 (12)6.5.1 中断源 (12)6.6管脚连接模块 (12)6.7快速通用并行I/O口 (12)6.7.1 特性 (13)6.8 10位A/D转换器 (13)6.8.1 特性 (13)6.9 UART (13)6.9.1 特性 (13)6.10 I2C串行I/O控制器 (14)6.10.1 特性 (14)6.11 SPI串行I/O控制器 (14)6.11.1 特性 (14)6.12 SSP串行I/O控制器 (14)6.12.1 特性 (15)6.13通用32位定时器/外部事件计数器 (15)6.13.1 特性 (15)6.14通用16位定时器/外部事件计数器 (15)6.14.1 特性 (16)6.15看门狗定时器 (16)6.15.1 特性 (16)6.16实时时钟 (16)6.16.1 特性 (17)6.17系统控制 (17)6.17.1 晶振 (17)6.17.2 PLL (17)6.17.3 复位和唤醒定时器 (17)6.17.4 代码安全保护 (18)6.17.5 外部中断输入 (18)6.17.6 存储器映射控制 (18)6.17.7 功率控制 (18)6.17.8 APB总线 (18)6.18仿真和调试 (18)6.18.1 Embedded ICE (19)6.18.2 RealMonitor (19)7. 极限参数 (19)8. 静态特性 (20)9.动态特性 (24)10.表面封装 (25)11.缩写词 (26)12.修订记录 (26)1.概述LPC2101/2102/2103基于一个支持实时仿真的ARM7TDMI-S CPU,并带有8kB和32kB 嵌入的高速Flash存储器。

LPC11C1x_C_CANDriver

13.4.1 调用C_CAN API ........................................................................................................1 13.4.2 CAN初始化 ................................................................................................................2 13.4.3 CAN中断处理程序 ....................................................................................................3 13.4.4 CAN Rx报文对象配置...............................................................................................3 13.4.5 CAN接收 ....................................................................................................................3 13.4.6 CAN发送 ....................................................................................................................4 13.4.7 CANopen配置.............................................................................................................4 13.4.8 CANopen处理程序.....................................................................................................6 13.4.9 CAN/CANopen回调函数 ...........................................................................................6 13.4.10 CAN报文接收的回调 ................................................................................................7 13.4.11 CAN报文发送回调 ....................................................................................................7 13.4.12 CAN错误回调 ............................................................................................................7 13.4.13 CANopen SDO加速的读回调....................................................................................8 13.4.14 CANopen SDO加速的写回调....................................................................................8 13.4.15 CANopen SDO分段的读回调....................................................................................9 13.4.16 CANopen SDO分段的写回调..................................................................................10 13.4.17 CANopen fall-back SDO处理程序回调...................................................................11

LPC111x中文版用户手册

20101102

LPC111x/LPC11C1x 用户手册

• 增加了 LPC111x/102/202/302 (LPC1100L 系列 ) ( 表 1,表 280)。 • 更新了 PLL 输出频率 (< 100 MHz),见 3.10 节 “ 系统 PLL 功能描述 ”。 • 更新了对深度睡眠模式和深度掉电模式的描述,见 3.8 节 “ 电源管理 ”。 • 增加了第五章 “LPC111x/LPC11Cxx 功耗配置 ” 。 • WDT 更改为 24 位定时器,见 17 章 “LPC111x/LPC11Cxx 看门狗定时器 (WDT)”。 • 21.6.2 章节的 “ 调试连接 ”。 • SYSTCKCAL 寄存器的地址改为 0x4004 8154 ( 表 6 和表 33)。 • 添加了比较 flash 映像的注解 ( 20.10 章节的 “flash 映像的注解 ”)。 • 在 20.5 部分 -“UART ISP 命令 ” 中,ISP 的波特率被严格限制 (230400 bps 除外)。 • Flash 写操作的干扰影响 (20.5.7 节的 “ 复制 RAM 到 flash<Flash address> <RAM address> <no of

版权所有 2012恩智浦有限公司 未经许可,禁止转载

NXP Semiconductors

UM10398

LPC111x/LPC11Cxx User manual

修改记录 版本 5 更新:

4 更新: 3 更新:

2 更新:

1

日期

描述

20110621

LPC111x/LPC11C1x/LPC11C2x 用户手册

片上 C_CAN 驱动器和闪存的系统编程工具通过 C_CAN 连接在 LPC11Cxx 里,此外 LPC11C2x 还包含一个一个片上 CAN 收发器。

LPC1114的IO配置部分的中文手册

表111. LPC111x 引脚配置引脚配置--图8–10引脚描述表8–114引脚配置--图8–10引脚描述表8–114引脚配置图8–8-图8–10引脚描述表8–112表8–114图8–10表8–112表8–113表8–1143. LPC111x 引脚描述表 112. LPC1113/14 引脚描述表 (LQFP48 封装)RESET — 外部复位输入:此引脚上的低电平会使设备复位,I/O 端口和外设复位成初始的默认状态,并使处理器从0地址开始执行。

I/O PIO0_0 — 通用数字输入/输出引脚。

PIO0_1/CLKOUT/ CT32B0_MAT2PIO0_2/SSEL0/ CT16B0_CAP04[1]I/O PIO0_1 —通用数字输入/输出引脚。

复位时低电平启动在线系统编程命令处 理程序。

O CLKOUT — 时钟输出脚。

OCT32B0_MAT2 —32位定时器0匹配输出2。

10[1]I/O PIO0_2 —通用数字输入/输出引脚。

O SSEL0 —SPI0从机选择。

ICT16B0_CAP0 —16位定时器0捕获输入0。

PIO0_314[1] I/OPIO0_3 —通用数字输入/输出引脚。

.I/O SCK0 —SPI0串行时钟。

PIO0_7/CTS 23[1] I/O PIO0_7 —通用数字输入/输出引脚(大电流输出驱动器)。

I CTS —UART清除发送。

PIO0_8/MISO0/CT16B0_MAT0PIO0_9/MOSI0/CT16B0_MAT1 SWCLK/PIO0_10/ SCK0/CT16B0_MAT2TDI/PIO0_11/AD0/CT32B0_MAT3 TMS/PIO1_0/AD1/CT32B1_CAP0 TDO/PIO1_1/AD2/CT32B1_MAT0TRST/PIO1_2/AD3/CT32B1_MAT1 27[1] I/O PIO0_8 —通用数字输入/输出引脚。

LPC1114-LPC11U14和LPC1343对比学习(七)SSP

LPC1114/LPC11U14和LPC1343对比学习(七)SSPLPC1114 和LPC11U14 有两路SSP 总线,而LPC1343 只有一路SSP 总线,其他没有太大的区别,不过LPC11U14 的SSP1 总线都有两路管脚可以设置,进一步增加了芯片的灵活性。

三种芯片的SSP 总线初始化基本一致:但是需要注意,LPC1114 和LPC1343 的SSP0 总线,再设置好时钟后,还必须选择时钟的输出引脚,LPC_IOCON->SCK_LOC = SSP0_SCK_SELECT;而LPC1114 的SSP1 总线和LPC11U14 的两路SSP 总线则不需要这样设置。

对于LPC1114 的SSP1 总线可以理解,因为没有管脚映射。

但是LPC11U14 却有管脚映射功能,如果没有此寄存器,如果多个管脚都设置成同一的功能,真不知道会出现什么样的效果。

就是能正常工作,感觉程序没有以前那样严谨了,不知道NXP 为什么会这样设计对于SSP 总线,需要知道主从设置的主要区别,在主模式下器件的片选管脚可以随意设定而不一定要总线的NSS 管脚,而且就算使用此管脚也要设置成普通GPIO 端口,通过程序控制器件片选。

但是在从模式下从机管脚必须使用总线的NSS。

在使用SSP 总线来控制SD 卡时,SD 卡的初始化必须要尽量降低SSP 总线速度,一般在400K 以下比较安全,如果不想降低SSP 总线速度,那就必须在初始化函数中添加延时来降低速度,保证SD 卡初始化成功。

之后就可以加快SSP 总线速度,提高SD 卡读写速度。

tips:感谢大家的阅读,本文由我司收集整编。

仅供参阅!。

通用异步收发器(UART)

保留

0x01 0x00 0x00 0x00 0x60 0x00 0x00

0x10 0x80

-

RS-485/EIA-485控制。包含配置RS-485/EIA-485模式各个方面 的控制。

RS-485/EIA-485地址匹配。包含RS-485/EIA-485模式下的地 址匹配值。

0x00 0x00

U0RS485DLY 读/写 0x054 RS-485/EIA-485直接控制延迟。

1 允许自动波特率结束中断。

9 ABTOIntEn

允许自动波特率超时中断。

0

0 禁止自动波特率超时中断。

1 允许自动波特率超时中断。

31:10 -

保留, 用户软件不要向保留位写入1从保留位读出的值未被 NA 定义。

UM10398_0

User manual

Rev. 00.10 — 11 January 2010

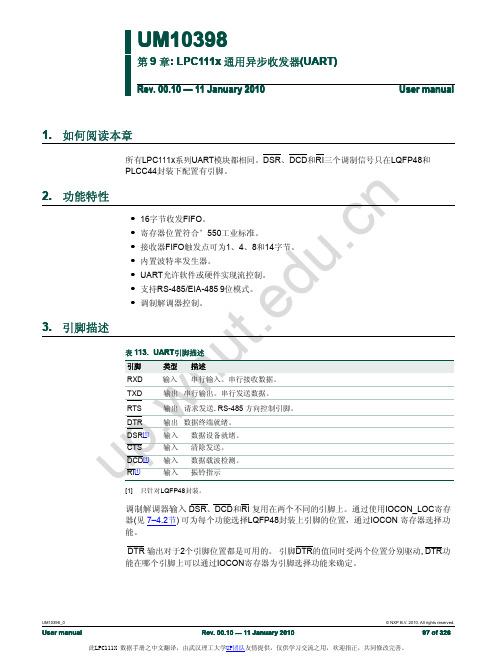

引脚描述

• 16字节收发FIFO。 • 寄存器位置符合’550工业标准。 • 接收器FIFO触发点可为1、4、8和14字节。 • 内置波特率发生器。 • UART允许软件或硬件实现流控制。 • 支持RS-485/EIA-485 9位模式。 • 调制解调器控制。

表 113. UART引脚描述

引脚

类型 描述

UM10398_0

User manual

Rev. 00.10 — 11 January 2010

© NXP B.V. 2010. All rights reserved.

98 of 326

此LPC111X 数据手册之中文翻译,由武汉理工大学UP团队友情提供,仅供学习交流之用,欢迎指正,共同修改完善。

© NXP B.V. 2010. All rights reserved.

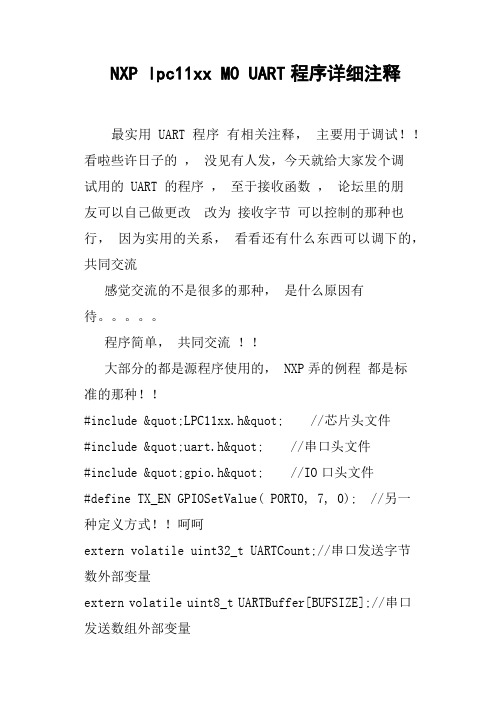

NXPlpc11xxM0UART程序详细注释

NXP lpc11xx M0 UART程序详细注释最实用UART 程序有相关注释,主要用于调试!!看啦些许日子的,没见有人发,今天就给大家发个调试用的 UART 的程序,至于接收函数,论坛里的朋友可以自己做更改改为接收字节可以控制的那种也行,因为实用的关系,看看还有什么东西可以调下的,共同交流感觉交流的不是很多的那种,是什么原因有待。

程序简单,共同交流!!大部分的都是源程序使用的, NXP弄的例程都是标准的那种!!#include "LPC11xx.h" //芯片头文件#include "uart.h" //串口头文件#include "gpio.h" //IO口头文件#define TX_EN GPIOSetValue( PORT0, 7, 0); //另一种定义方式!!呵呵extern volatile uint32_t UARTCount;//串口发送字节数外部变量extern volatile uint8_t UARTBuffer[BUFSIZE];//串口发送数组外部变量uint8_t aa[10]="2010.5.9AM"; //定义需要发送的数组该下日期uint8_t bb[1]; //定义接收数组int main (void){UARTInit(115200); //初始化串口波特率UARTCount=1; //这里是一个测试程序bb[0]=0x00; //接收数组清零GPIOSetDir(PORT0, 7, 1 ); //1为输出TX_EN; //指示灯的使用UARTSend((uint8_t *) aa,10); //串口发送函数while (1){if ( UARTCount != 0 ) //用于测试{LPC_UART->;IER = IER_THRE | IER_RLS;bb[0]=UARTRec(); //串口接收函数UARTSend((uint8_t *) bb,1);LPC_UART->;IER = IER_THRE | IER_RLS | IER_RBR; }}}这里是接收函数,可以自己放置位置uint8_t UARTRec(){uint8_t BufferPtr;while((LPC_UART->;LSR & 0x01) == 0);BufferPtr = LPC_UART->;RBR;return BufferPtr;}。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

up .w hd 1. 如何阅读本章所有 LPC111x 系列中的 SPI 模块均相同。

第二个 SPI 模块, SPI1,只存在于LQFP48和 PLCC44封装上,在 HVQFN33封装上则没有。

注释:两个 SPI 模块都包含全部的 SSP 特征集,所有相关寄存器都使用 SSP 前缀命名。

2. 特性? 兼容 Motorola SPI 、 4线 TI SSI 和美国国家半导体公司的 Microwire 总线。

? 同步串行通信。

? 支持主机和从机操作。

? 收发均有 8帧 FIFO 。

?每帧有 4-16位数据。

3. 基本描述SPI/SSP是一个同步串行端口 (SSP控制器,可控制 SPI 、 4线 SSI 和 Microwire 总线。

它可以与总线上的多个主机和从机相互作用。

在数据传输过程中,总线上只能有一个主机与一个从机进行通信。

原则上数据传输是全双工的, 4~16位帧的数据由主机发送到从机或由从机发送到主机。

但实际上,大多数情况下只有一个方向上的数据流包含有意义的数据。

LPC111x 系列处理器有两个 SPI/同步串行端口控制器。

u d u UM10398Semiconductors LPC1100开发,尽在第 11章 :LPC111x 带有 SSP 的 SPI0/1 4. 引脚描述表 161622. SPI 引脚描述SCK0/1I/OSCK CLK SK 串行时钟。

SCK/CLK/SK是用来同步数据传输的时钟信号。

它由主机驱动,从机接收。

当使用 SPI 接口时,时钟可编程为高电平有效或低电平有效,否则总是高电平有效。

SCK 仅在数据传输过程中切换。

在其它时间里, SPI/SSP接口保持无效状态或不驱动它(使其处于高阻态。

SSEL0/1I/OSSEL FS CS 帧同步 /从机选择。

当 SPI/SSP接口是总线主机时,它在串行数据启动前驱动该信号为有效状态。

在数据发送出去之后又将该信号恢复为无效状态。

该信号的有效状态根据所选的总线和模式可以是高或低。

当SPI/SSP接口作为总线从机时,该信号根据使用的协议来判断主机数据的存在。

当只有一个总线主机和一个总线从机时,来至主机的帧同步信号或从机选择信号直接与从机相应的输入相连。

当总线上接有多个从机时,需要管理好这些从机的帧选择 /从机选择输入,以免一次传输有多个从机响应。

MISO0/1I/OMISO DR(M DX(S MOSI0/1I/OMOSI DX(M DR(S SI(MSO(SSO(MSI(S主机输入从机输出。

MISO 信号线从从机传送串行数据传送到主机。

当SPI/SSP作为从机,串行数据从该信号输出。

当 SPI/SSP作为主机,从该信号得到串行数据时钟。

当 SPI/SSP作为从机但未被FS/SSEL选定,它不会驱动该信号 (保持高阻态。

主机输出从机输入。

MOSI 信号线从主机传送串行数据到从机。

当 SPI/SSP作为主机,串行数据从该信号输出。

当 SPI/SSP作为从机,从该信号得到串行数据时钟。

注释:SCK0功能在三个不同的引脚上复用 (在 HVQFN 封装上有两个引脚。

通过设置 IOCON_LOC寄存器 (见 7–4.2小节选择一个引脚作为 SCK0功能,另外在IOCON 寄存器中设置功能。

SCK1引脚没有复用。

UM10398SemiconductorsLPC1100开发,尽在第 11章 :LPC111x 带有 SSP 的 SPI0/15. 时钟和功耗管理SPI 模块由 AHBCLKCTRL 寄存器 (见表 3–19 控制。

用于 SPI 时钟分频器和预分频器的 SPI 外设时钟,由 SSP0/1CLKDIV寄存器 (见 3–4.15小节控制。

可以通过设置 SSP0/1CLKDIV寄存器 (见 3–4.15小节来禁止 SPI0/1_PCLK时钟。

SPI 模块可以通过设置 AHBCLKCTRL 寄存器禁止 (表 3–19 以节省功耗。

6. 寄存器描述SPI 控制器寄存器地址如表 11–163和表 11–164所示。

注释:使用 SSP 前缀的寄存器名称,表示 SPI 控制器完全兼容 SSP 功能。

[1]复位值仅指已使用位中的数据,不包括保留位的内容。

表 164. 寄存器概览:SPI1(基址 0x 404000580080000 控制寄存器 0。

选择串行时钟频率,总线类型和数据长度。

SSP0CR1R/W0x004控制寄存器 1。

选择主机 /从机和其他模式。

0SSP0DR R/W0x008数据寄存器。

写满将发送 FIFO ,读空将接收FIFO 。

0SSP0SR RO 0x00C 状态寄存器。

-SSP0CPSR R/W0x010时钟预分频寄存器。

0SSP0IMSC R/W0x014中断屏蔽设置和清零寄存器。

0SSP0RIS R/W0x018原始中断状态寄存器。

-SSP0MIS R/W0x01C 屏蔽中断状态寄存器。

0SSP0ICRR/W0x020SSPICR 中断清零寄存器。

NA控制寄存器 0。

选择串行时钟频率,总线类型和数据长度。

SSP1CR1R/W0x004控制寄存器 1。

选择主机 /从机和其他模式。

0SSP1DRR/W0x008数据寄存器。

写满将发送 FIFO ,读空将接收 FIFO 。

0SSP1SR RO0x00C 状态寄存器。

-SSP1CPSR R/W0x010时钟预分频寄存器。

0SSP1IMSC R/W0x014中断屏蔽设置和清零寄存器。

0SSP1RIS R/W0x018原始中断状态寄存器。

-SSP1MIS R/W0x01C 屏蔽中断状态寄存器。

0SSP1ICRR/W0x020SSPICR 中断清零寄存器。

NAUM10398SemiconductorsLPC1100开发,尽在第 11章 :LPC111x 带有 SSP 的 SPI0/1[1]复位值仅指已使用位中的数据,不包括保留位的内容。

6.1SPI/SSP控制寄存器 0该寄存器控制 SPI/SSP控制器的基本操作。

表 165:SPI/SSP控制 0(SSP0CR0-address 0x40040000, SSP1CR0-address 3:0 DSS数据长度选择。

该字段控制着每帧传输的位数目。

不支持且不使用值 0000-0010。

000000114-位传输 1005-位传输 1016-位传输 1107-位传输 1118-位传输 0009-位传输 00110-位传输 01011-位传输 01112-位传输 10013-位传输 10114-位传输11015-位传输 11116-位传输 FRF帧格式 0000SPI TIMicrowire1不支持且不应使用这个组合。

CPOL时钟输出极性。

该位只用于 SPI 模式。

0SPI 控制器使总线时钟在两帧传输之间保持低电平。

SPI 控制器使总线时钟在两帧传输之间保持高电平。

CPHA时钟输出相位。

该位只用于 SPI 模式。

SPI 控制器在帧传输的第一个时钟跳变沿捕获串行数据,也就是说,传输远离时钟线的帧间状态。

SPI 控制器在帧传输的第二个时钟跳变沿捕获串行数据,也就是说,传输紧邻时钟线的帧间状态。

5:8SCR串行时钟频率。

SCR 之值为总线上每传输一个数据位所对应的预分频时钟数减 1。

假设 CPSDVSR 为预分频器的分频值, APB 时钟 PCLK 为预分频器的时钟,则位频率为 PCLK /(CPSDVSR×[SCR+1]。

0x00uUM10398SemiconductorsLPC1100开发,尽在第 11章 :LPC111x 带有 SSP 的 SPI0/16.2SPI/SSP0控制寄存器 1该寄存器控制着 SPI/SSP控制器的工作方式的某些方面。

表 166:SPI/SSP控制寄存器 1(SSP0(SSP0CC R1–地址 0x 404000400000044, SS SSPP 1CR1–地址 6.3SPI/SSP数据寄存器软件可将要发送的数据写入该寄存器,或从该寄存器读出接收到的数据。

表 167:SPI/SSP数据寄存器 (S SP SP00DR –地址 0x40x400040008, SSP1SSP1DD R –地址回环模式 0正常操作模式串行输入脚同时也是串行输出脚(MOSI 或 MISO ,而不是仅作为串行输入脚(MISO 或 MOSI 分别起作用。

SSE允许 SPI 。

0禁止 SPI 控制器。

SPI 控制器可与串行总线上的其它器件相互通信。

在设置该位之前,软件应将合适的控制信息写入其它 SPI/SSP寄存器和中断控制器寄存器。

MS主机 /从机模式。

该位只能在 SSE 位为 0时写入。

SPI 控制器作为总线主机,驱动 SCLK 、 MOSI 和 SSEL 线并接收 MISO 线。

SPI 控制器作为总线从机,驱动 MISO 线并接收 SCLK 、 MOSI 和 SSEL 线。

SOD从机输出禁止。

该位只与从机模式有关(MS=1。

如果该位为 1,将阻塞 SSI 控制器驱动发送数据线(MISO 。

07:4-保留,用户软件不要向保留位写入 1。

从保留位读出的值未定义。

NA要发送的帧数据写入该寄存器。

如果 Tx FIFO 以前为空,且总线上的 SPI 控制器不忙,则立刻开始发送数据。

否则,写入该寄存器的数据要等到所有数据发送(或接收完后才能发送。

如果数据长度小于 16位,软件必须对数据进行右对齐后再写入该寄存器。

读:当状态寄存器的 RNE 位为 1时,指示 Rx FIFO 不为空,软件可读取该寄存器。

软件读取该寄存器时, SSP 控制器将返回 Rx FIFO 中最早收到的一帧数据。

如果数据长度小于 16位,该字段的数据必须进行右对齐,高位补零。

0x0000up .wd u. cn 6.4SPI/SSP状态寄存器该只读寄存器反映了 SSP 控制器的当前状态。

表 168:SPI/SSP状态寄存器 (S(SSS P 0SR –地址 0x40x40004000000C, SSP1SR –地址 0TFE 发送 FIFO 空。

发送 FIFO 为空时该位为 1,反之为011TNF 发送 FIFO 未满。

Tx FIFO 满时该位为 0,反之为 1。

12RNE 接收 FIFO 非空。

接收 FIFO 为空时该位为 0,反之为 1。

03RFF 接收 FIFO 满。

接收 FIFO 满时该位为 1,反之为 0。

04BSY 忙。

SPI 控制器空闲时该位为 0, 当前正在0发送 /接收一帧数据和 /或 Tx FIFO 非空时该位为 1。

7:5-保留。

用户软件不要向保留位写入 1。

从保留位读出的值 NA未定义。

6.5SPI/SSP时钟预分频寄存器SPI_PCLK到 SPI 预分频器时钟的分频系数,由该寄存器控制。