多核Cache替换策略实验

利用多维分级Cache替换策略减少对PCM内存写回量

利用多维分级Cache替换策略减少对PCM内存写回量阮深沉;王海霞;汪东升【期刊名称】《计算机工程与科学》【年(卷),期】2016(038)008【摘要】寻找新型存储材料代替DRAM内存是当前的一个研究热点.相变存储PCM因其具有低功耗、高存储密度和非易失性的优点受到广泛的关注,然而PCM 的可擦写次数有限,要用作内存必须考虑如何减少对其的写操作.针对该问题,一种有效的解决方法是优化Cache替换策略,减少Cache中脏块被替换出的数量.现有研究主要通过在插入和访问命中时给脏块设定较高的保护优先级来达到给脏块额外保护的目的,但是在降级过程中不再对脏块与干净块进行区分,这导致Cache可能在存在大量干净块的情况下仍然先替换脏块.提出一种新型的Cache替换策略MAC,它通过一个多维分级结构在脏块与干净块之间设置了不可逾越的界限,使得脏块能得到更有力的保护.模拟实验表明,相对IRU替换策略,MAC以较低的硬件开销代价平均减少约25.12%的内存写,同时对程序运行性能几乎没有影响.【总页数】6页(P1568-1573)【作者】阮深沉;王海霞;汪东升【作者单位】清华大学信息技术与科学国家实验室,北京100084;清华大学信息技术与科学国家实验室,北京100084;清华大学信息技术与科学国家实验室,北京100084【正文语种】中文【中图分类】TP333【相关文献】1.利用必要性减少计算量 [J], 殷畅;李正;2.DM642上利用DMA和CACHE优化内存存取实例 [J], 常传文;茅文深3.在VB利用内存映射文件读取大数据量原始遥感影像图 [J], 杨群4.利用NOAA气象卫星资料制作锡林郭勒草原产草量分级图 [J], 丛子杰5.利用金凯德分级系统进行英语课外读物分级的量性研究 [J], 李林福;因版权原因,仅展示原文概要,查看原文内容请购买。

Cache替换策略与写操作策略

Cache的替换策略

例: 访问顺序号:1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

访问主存块地址:1 2 4 1 3 7 0 1 2 5 4 6 4 7 2

0

10 2 31

42 5 63

块 1 1 1 1 1 1 1 1 1 1 41 4 4 4 4

分

配

4 4 4 4 04 0 0 50 5 5 5 5 5

• 常见的写操作策略有两种: 1、全写法、写直达法(Write Through) 2、回写法、写回法(Write B法、写直达法(Write Through):命中时,不仅写Cache, 也同时写入主存。使主存与Cache相关块内容始终保持一致。

优点:主存与Cache始终同步。 缺点:当CPU向主存写操作时, Cache无高速缓冲功能,降低了

Cache的写操作策略

2、回写法、写回法(Write Back):命中需要将信息 写入主存时,暂时只写入 Cache,并不写入主存, Cache中的这个块作一个标记,只有当该块内容需要从 Cache中替换出来时,再一次性写入主存。

优点:减少对主存的写操作次数, 工作速度较快. 缺点:存在Cache与主存数据不一致的隐患.

Cache的功效。

Cache的写操作策略

2、回写法、写回法(Write Back):Cache命中需要将信息写入主存 时,暂时只写入 Cache,并不写入主存,Cache中的这个块作一个 标记,只有当该块内容需要从Cache中替换出来时,再一次性写入 主存。

优点:减少对主存的写操作次数, 工作速度较快。 缺点:存在Cache与主存数据不一致的隐患。

情

2 2 2 2 72 7 7 7 7 7 67 6 6 26

cache性能分析实验报告

计算机系统结构实验报告名称: Cache性能分析学院:信息工程姓名:学号:S121055专业:计算机系统结构年级:实验目的1.加深对Cache的基本概念、基本组织结构以及基本工作原理的理解;2.了解Cache的容量、相联度、块大小对Cache性能的影响;3.掌握降低Cache失效率的各种方法,以及这些方法对Cache性能提高的好处;4.理解Cache失效的产生原因以及Cache的三种失效;5.理解LRU与随机法的基本思想,及它们对Cache性能的影响;实验平台Vmware 虚拟机,redhat 9.0 linux 操作系统,SimpleScalar模拟器实验步骤1.运行SimpleScalar模拟器;2.在基本配置情况下运行程序(请指明所选的测试程序),统计Cache总失效次数、三种不同种类的失效次数;3.改变Cache容量(*2,*4,*8,*64),运行程序(指明所选的测试程序),统计各种失效的次数,并分析Cache容量对Cache性能的影响;4.改变Cache的相联度(1路,2路,4路,8路,64路),运行程序(指明所选的测试程序),统计各种失效的次数,并分析相联度对Cache性能的影响;5.改变Cache块大小(*2,*4,*8,*64),运行程序(指明所选的测试程序),统计各种失效的次数,并分析Cache块大小对Cache性能的影响;6.分别采用LRU与随机法,在不同的Cache容量、不同的相联度下,运行程序(指明所选的测试程序)统计Cache总失效次数,计算失效率。

分析不同的替换算法对Cache性能的影响。

预备知识1. SimpleScalar模拟器的相关知识。

详见相关的文档。

2. 复习和掌握教材中相应的内容(1)可以从三个方面改进Cache的性能:降低失效率、减少失效开销、减少Cache命中时间。

(2)按照产生失效的原因不同,可以把Cache失效分为三类:①强制性失效(Compulsory miss)当第一次访问一个块时,该块不在Cache中,需从下一级存储器中调入Cache,这就是强制性失效。

多核处理器片上Cache访问行为分析与优化机制研究

国防科学技术大学博士学位论文多核处理器片上Cache访问行为分析与优化机制研究姓名:***申请学位级别:博士专业:电子科学与技术指导教师:***2011-05摘要多核处理器(Chip Multi-Processors,CMP)相比单核处理器具有功耗低、复杂度小、可扩展性好和性价比高等优势,已成为工业界和学术界的主流微处理器体系结构。

近来在服务器和数据中心等领域,服务聚合(Server Consolidation)和虚拟计算(Virtual Computing)成为趋势,使多样化的多道程序负载成为CMP平台上的主要负载形式。

多核处理器多采用相对简单的处理器核,设计复杂性和性能瓶颈主要集中在存储系统上。

随着半导体制造工艺进入纳米时代,多核处理器平台上的层次Cache系统面临着片外访问延迟大、片外访问带宽有限、负载多样化、片上互连线延迟不断增长和应用间负面相互干扰等挑战。

片上层次Cache系统特别是非一级Cache(Non-First Level Cache)已成为当前多核处理器平台上的重要课题之一。

Cache系统的有效性和多核处理器的系统性能与Cache上承受的Cache访问行为密切相关。

分析Cache系统上的Cache访问行为特性对于研究多核处理器Cache系统的优化、管理机制有重要意义。

本文针对多核处理器中片上非一级Cache的访问行为分析方法和优化机制展开研究,重点关注多道程序负载,兼顾多线程负载。

本文主要取得以下研究成果:1.提出一种在片上非一级Cache中在线识别应用Cache行为类型的方法OABI。

该方法基于理论分析和对SPEC CPU2006测试程序集中应用的Cache访问行为特征的统计,根据应用的失效率随Cache容量的变化趋势和基准失效数将应用Cache行为分为五类,并引入相应的硬件支持实现了对应用Cache行为类型的在线识别。

该方法可用于指导CMP片上非一级Cache的资源管理和优化。

多核cpu cache替换算法

多核cpu cache替换算法多核CPU Cache替换算法是指在多核处理器中,当缓存容量已满时,如何选择和替换缓存中的数据,以便为新数据腾出空间。

以下是几种常见的多核CPU Cache替换算法:1. 随机替换算法(Random Replacement):随机选择一个缓存块进行替换。

优点是实现简单,但缺点是可能会导致缓存命中率下降。

2. 先进先出算法(FIFO Replacement):将最早进入缓存的块进行替换。

优点是实现简单,但缺点是可能会导致缓存命中率下降,尤其是当缓存已经存在热点数据时。

3. 最近最少使用算法(LRU Replacement):将最近最少使用的块进行替换。

优点是可以提高缓存命中率,但缺点是需要额外的存储空间来记录每个缓存块的访问时间。

4. 基于时间的替换算法(Time-Based Replacement):将最长时间未被访问的块进行替换。

优点是可以提高缓存命中率,但缺点是需要额外的存储空间来记录每个缓存块的访问时间。

5. 基于频率的替换算法(Frequency-Based Replacement):将最不经常使用的块进行替换。

优点是可以提高缓存命中率,但缺点是需要额外的存储空间来记录每个缓存块的访问频率。

6. 基于大小置换算法(Size-Based Replacement):将最小/最大的块进行替换。

优点是可以提高缓存命中率,但缺点是需要额外的存储空间来记录每个缓存块的大小。

7. 基于局部性替换算法(Spatial/Temporal Replacement):将与当前访问模式最不匹配的块进行替换。

优点是可以提高缓存命中率,但缺点是需要额外的存储空间来记录每个缓存块的访问模式。

8. 基于关联性替换算法(Associative Replacement):将与当前访问最不相关的块进行替换。

优点是可以提高缓存命中率,但缺点是需要额外的存储空间来记录每个缓存块的相关性。

以上这些多核CPU Cache替换算法都有各自的优缺点,选择哪种算法取决于具体的系统和应用场景。

计算机组成原理实验报告-Cache模拟器的实现

计算机组成原理实验报告-Cache模拟器的实现实验内容:1、启动CacheSim。

2、根据课本上的相关知识,进一步熟悉Cache的概念和工作机制。

3、依次输入以下参数:Cache容量、块容量、映射方式、替换策略和写策略。

Cache容量块容量映射方式替换策略写策略256KB 8 Byte 直接映射------ -------64KB 32 Byte 4路组相联 LRU -------64KB 32 Byte 4路组相联随机--------8KB 64 Byte 全相联 LRU ---------4、读取cache-traces.zip中的trace文件。

5、运行程序,观察cache的访问次数、读/写次数、平均命中率、读/写命中率。

思考:1、Cache的命中率与其容量大小有何关系?2、Cache块大小对不命中率有何影响?3、替换算法和相联度大小对不命中率有何影响?实验步骤与预习:实验步骤:1、启动CacheSim。

2、根据课本上的相关知识,进一步熟悉Cache的概念和工作机制。

3、依次输入以下参数:Cache容量、块容量、映射方式、替换策略和写策略。

4、读取cache-traces.zip中的trace文件。

5、运行程序,观察cache的访问次数、读/写次数、平均命中率、读/写命中率。

预习:Cache:高速缓冲存储器高速缓冲器是存在于主存与CPU之间的一级存储器,由静态存储芯片(SRAM)组成,容量比较小但速度比主存高得多,接近于CPU的速度。

Cache的功能是用来存放那些近期需要运行的指令与数据。

目的是提高CPU对存储器的访问速度。

工作机制:主要由三大部分组成:Cache存储器:存放由主存调入的指令与数据块。

地址转换部件:建立目录表以实现主存地址到缓存地址的转换。

替换部件:在缓存已满时按照一定的策略进行数据块替换,并修改地址转换部件。

实验结果:一般而言,cache用量越大,其cpu命中率越高,当然容量也没必要太大,当cache 容量达到一定的值时,命中率不因容量的增大而有明显的提高。

高级Cache替换策略研究

3. VWay Cache

全相连cache有2个好处:最小化miss冲突和可以使用全局的替换策略。miss的冲突程度 与cache的组相连程度成反比。全局的替换策略允许全相连cache选择最佳的替换块,而这仅 限于替换算法的智能。但是,对全相连cache的访问是线性扫描,需要大量的tag比较,导致 访问延时和性能下降。

1.2 算法描述

如果A算法的miss率大于B算法的miss率,并且如果当前B miss并且被选择移除的 块在adapt.cahe中时,adpat.cahe就移除与B中相同的那个块。否则的话,adapt.cache 移除任意不在B中的一块。当B算法的miss率大于A算法的miss率时,和上面的操作相 同。

传统的LRU替换策略将新的访问插入在MRU的位置上,使得其有被命中的机会。LIP策 略是将预取的Cache line放置在LRU位置,以避免由不精确的预取所产生的污染。但是由于 LIP没有年龄机制,LIP策略会导致部分不再被引用的line处于non-LRU的位置上,并且不会 变更给定应用程序的工作集的sets

首先,我们用 … 表示对地址 … 依次进行N次循环访问。假定有这样一个模型:

用 … 紧接着 … 访问一个全相连的cache。cache的空间为K(K<T)。假定BIP中的

参数 很小,并且两个访问序列的重复次数

并且N K⁄ 。下表比较了各种策略的hit

情况

我们看到,在循环引用模型中,由于工作集大于cache的大小,从而导致LRU的完全miss, LIP策略可以保证较好的hit,但是对于全新的访问序列由于其不能将替换插入到MRU位置, 所以导致新的完全miss。BIP由于可以部分得插入到MRU中,所以对于新的访问序列仍能有 较高的hit率。

多核处理器中多级缓存替换策略的设计

摘要高速缓存是高性能处理器中提高访存速度的重要技术,其对处理器性能的影响至关重要。

本论文主要针对基于包容式高速缓存结构的多核处理器中,多核共享的最下级缓存不清楚其上层缓存的使用情况而导致下级缓存将上级的常用数据无效掉的问题,提出一种感应上级的最近最少使用(LRU, Least Recently Used)替换策略,将上级高速缓存(Cache)的局部性信息发送给下级Cache,下级Cache在数据替换的时候,结合上级Cache和本级Cache综合的局部性信息进行替换,避免上述错误的无效掉上级Cache常用数据的情况。

从而提高处理器执行效率和整体性能。

在上述理论基础上,以GEM5处理器模拟器为设计与测试平台,修改缓存模型中最外层高速缓存(LLC, Last Level Cache)的替换策略的代码。

具体方法主要为,在共享的LLC上加入upperAccess 标志位,以upperAccess标志位的状态为上级Cache数据使用情况的判断依据,在LLC需要做出替换决定时优化LLC高速缓存行(Cacheline)的替换顺序,尽量避免上层缓存的常用数据被替换掉,从而完成感应上级的LRU替换策略的加入,并以此减少二级缓存(L2 Cache)和更上级Cache出现包含式受害者(Inlusuve Victim)现象的次数。

在加入感应上级的LRU替换策略的模拟器模型中运行SPEC CPU2006测试集进行验证。

以L2和L3 Cache的每千条指令的未命中数据(MPKI, Miss per Kilo Instruction)和每周期指令数(IPC, Instruc-tions per cycle)数据为切入点,对比优化前后的缓存替换策略对系统整体性能的影响。

对比多个测试项目的结果,优化后单核测试下的IPC平均提升1.35%,L2 Cache 的MPKI平均降低1.5%。

优化后多核测试的IPC数据平均提升3.83%,L3 cache的MPKI平均降低5.0%。

多核系统中共享Cache的冒泡替换算法

多核系统中共享Cache的冒泡替换算法林晓敏;桂婷;乔福明;胡同森【期刊名称】《微电子学与计算机》【年(卷),期】2011(28)4【摘要】在多核环境下,对共享L2 Cache的优化显得尤为重要,因为当被访问的数据块不在L2 Cache中时(发生L2缺失),CPU需要花费几百个周期访问主存的代价是相当大的.在设计Cache时,替换算法是考虑的一个重要因素,替换算法的好坏直接影响Cache的性能和计算机的整体性能.虽然LRU替换算法已经被广泛应用在片上Cache中,但是也存在着一些不足:当Cache容量小于程序工作集时,容易产生冲突缺失;且LRU替换算法不考虑数据块被访问的频率.文中把冒泡替换算法应用到多核共享Cache中,同时考虑数据块被访问的频率和最近访问的信息.通过分析实验数据,与LRU替换算法相比,采用冒泡替换算法可以使MPKI(Misses per Kilo instructions)和L2 Cache命中率均有所改善.【总页数】4页(P118-121)【关键词】替换算法;Cache;LRU;冒泡替换;多核【作者】林晓敏;桂婷;乔福明;胡同森【作者单位】浙江工业大学计算机科学技术学院;浙江工业大学之江学院【正文语种】中文【中图分类】TP302【相关文献】1.一种基于频率的多核共享Cache替换算法 [J], 方娟;李成艳;王帅;姚治成2.集群VOD系统中磁盘Cache替换算法研究 [J], 刘志明;彭宇行3.多核并行计算中Cache伪共享的研究 [J], 赵富4.PLRU替换算法在嵌入式系统cache中的实现 [J], 李洪;毛志刚5.多核系统中共享cache的动态划分 [J], 杨磊;时磊;张铁军;王东辉因版权原因,仅展示原文概要,查看原文内容请购买。

多级cache之间的替换(缓存)策略

多级cache之间的替换(缓存)策略下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!多级缓存之间的替换策略在计算机体系结构中,缓存是一种常见的性能优化技术,它通过存储最常访问的数据来加速数据访问速度。

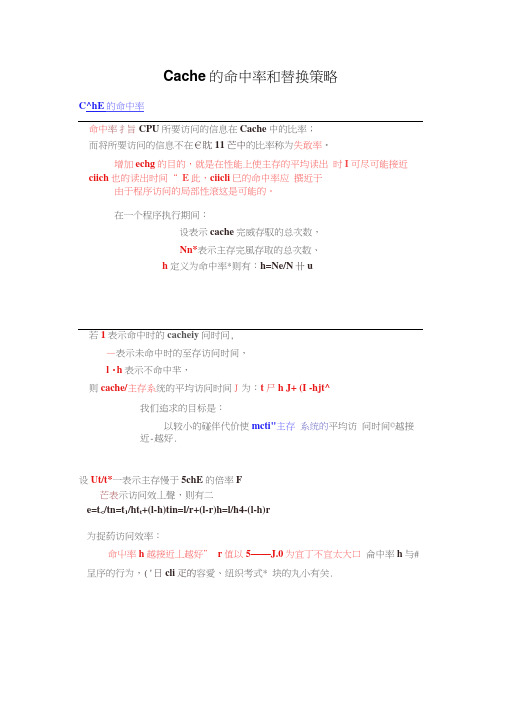

Cache的命中率和替换策略

Cache的命中率和替换策略C^hE的命中率命中率扌旨CPU所要访问的信息在Cache中的比率;而将所要访问的信息不在€眈11芒中的比率称为失敢率•增加echg的目的,就是在性能上使主存的平均读出时I可尽可能接近ciich也的读出时间“ E此,ciicli巳的命中率应撰近于由于程序访问的局部性滾这是可能的。

在一个程序执行期间:设表示cache完威存馭的总次数,Nn*表示主存完風存取的总次数、h定义为命中率*则有:h=Ne/N卄u若1表示命中时的cacheiy问时问,—表示未命中时的至存访问时间,l・h表示不命中芈,则cache/主存系统的平均访问时间J为:t尸h J+ (I -hjt^我们追求的目标是:以较小的碰伴代价使mcti"主存系统的平均访问时间©越接近-越好.设Ut/t*一表示主存慢于5chE的倍率F芒表示访问效丄聲,则有二e=t</tn=t1/ht t+(l-h)tin=l/r+(l-r)h=l/h4-(l-h)r为捉葯访问效率:命屮率h越接近丄越好” r值以5——J.0为宜丁不宜太大口侖中率h与#呈序的行为,('日cli疋的容愛、纽织考式* 块的丸小有关.例:CPU执行一』殳程序时,cache完成存取的次数为丄900矢,主存完戚存取的次数为丄00次,已Bracht吞取周期为50ns, 主存存取周期为250ns, 求cache/主存系统的效率和平均访问时间。

解:h=N c/(N v+N in)=1900/(1900+100)=0.95r=t m/t c=250ns/50ns=5e=_l/(r+( 1 -r)h)=l/(5+( 1 -5) x 0.95)=83.3% t a=t c/e=50ns/0.833=60ns 例:已知Cache存储周期为40ns,主存存倚周期为200ns, Cache / 主存系统平均访问时间为50ns,求Cache的命中卑是多少?解:因为ta=htc+(l-h)tm所以h=(ta-tm)/(tc-tm)=(50-200)/(40-200)=15/丄6替换策略当一个新的主存块要调入到cache,而允许存放此块的行位置都被其它主存块占满时,就要产生替换,因为cache工作原理要求它应尽量保存最新的数据。

计算机组成原理Cache替换策略

练习1:

对于一个容量为3个块的全相联Cache,假定访问的地址块号序列为 1, 2,3,4,1,2,3,4,分别用FIFO算法和LRU算法,写出其队列变化情况, 并得出结论。

练习2

对于一个全相联Cache,假定访问的地址块号序列为 1,2,3,4,1, 2,5,1,2,3,4,5,在先进先出替换方式下,分别写出分配给程序的 主存页面是3页和4页的情况下,其队列的变化情况,并得出结论。

时间t 1 2 3 4 5 6 7 8 9 10 11 12 页地址流 2 3 2 1 5 2 4 5 3 2 5 2

先进先出 FIFO

ห้องสมุดไป่ตู้命中3次

近期最少使用 LRU

命中5次

2 2 2 2* 5 5 5* 5* 3 3 3 3* 2 2 2 1 1 1* 4 4

调调命调替替 替命 进进中进换换 换中

3 3 3 3* 2* 2* 5 5 4 4 4* 2

替 命 替替 换 中 换换

2 2 2 2 2* 2 2 2* 3 3 3* 3*

3 3 3* 5 5 5* 5 5 5* 5

5

1 1 1* 4 4 4* 2 2 2

调 调进 命 调进 替 命中 替 命 替 替换 命 命

进

中

换 中换中 换

中中

注意:

对于一个容量为3个块的全相联cache假定访问的地址块号序列为12341234分别用fifo算法和lru算法写出其队列变化情况并得出结练习2对于一个全相联cache假定访问的地址块号序列123412512345在先进先出替换方式下分别写出分配给程序的主存页面是3页和4页的情况下其队列的变化情况并得出结论

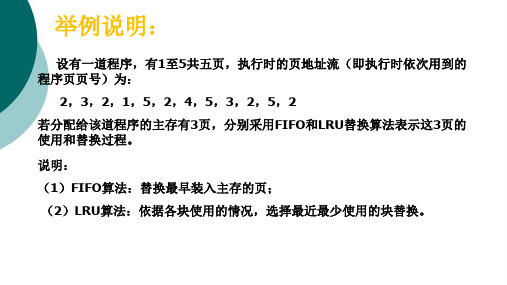

举例说明:

设有一道程序,有1至5共五页,执行时的页地址流(即执行时依次用到的 程序页页号)为:

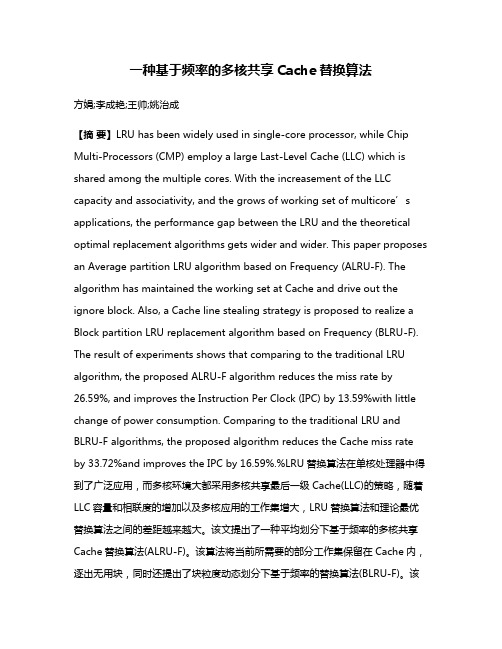

一种基于频率的多核共享Cache替换算法

一种基于频率的多核共享Cache替换算法方娟;李成艳;王帅;姚治成【摘要】LRU has been widely used in single-core processor, while Chip Multi-Processors (CMP) employ a large Last-Level Cache (LLC) which is shared among the multiple cores. With the increasement of the LLC capacity and associativity, and the grows of working set of multicore’s applications, the performance gap between the LRU and the theoretical optimal replacement algorithms gets wider and wider. This paper proposes an Average partition LRU algorithm based on Frequency (ALRU-F). The algorithm has maintained the working set at Cache and drive out the ignore block. Also, a Cache line stealing strategy is proposed to realize a Block partition LRU replacement algorithm based on Frequency (BLRU-F). The result of experiments shows that comparing to the traditional LRU algorithm, the proposed ALRU-F algorithm reduces the miss rate by26.59%, and improves the Instruction Per Clock (IPC) by 13.59%with little change of power consumption. Comparing to the traditional LRU and BLRU-F algorithms, the proposed algorithm reduces the Cache miss rate by 33.72%and improves the IPC by 16.59%.%LRU替换算法在单核处理器中得到了广泛应用,而多核环境大都采用多核共享最后一级Cache(LLC)的策略,随着LLC容量和相联度的增加以及多核应用的工作集增大,LRU替换算法和理论最优替换算法之间的差距越来越大。

cache硬件设计实验总结

cache硬件设计实验总结Cache硬件设计实验总结Cache是计算机系统中的一种高速缓存,用于存储最近被访问的数据,以提高计算机系统的性能。

在计算机系统中,CPU访问内存的速度比访问Cache的速度慢得多,因此,Cache的设计对于计算机系统的性能至关重要。

本文将对Cache硬件设计实验进行总结。

实验目的本次实验的目的是设计一个Cache硬件,实现Cache的读写操作,并测试Cache的性能。

具体实验要求如下:1. 设计一个Cache硬件,包括Cache的大小、块大小、组数、替换策略等参数的设置。

2. 实现Cache的读写操作,包括Cache的读取、写入和替换等操作。

3. 测试Cache的性能,包括Cache的命中率、访问时间等指标。

实验过程1. Cache硬件设计在本次实验中,我们设计了一个4KB大小的Cache,块大小为16B,共有256组。

采用的替换策略是LRU(Least Recently Used,最近最少使用)。

具体的Cache硬件设计如下:(1)Cache的地址结构Cache的地址结构包括标记位、组索引和块内偏移量。

在本次实验中,我们采用了直接映射的Cache结构,因此组索引的位数为8位,块内偏移量的位数为4位。

标记位的位数为16-8-4=4位。

(2)Cache的数据结构Cache的数据结构包括标记位、有效位、块内数据和LRU计数器。

标记位用于存储主存地址的高位,有效位用于表示Cache中的数据是否有效,块内数据用于存储主存地址对应的数据,LRU计数器用于记录Cache中每个块的使用情况。

2. Cache的读写操作Cache的读写操作包括Cache的读取、写入和替换等操作。

具体的操作流程如下:(1)Cache的读取操作当CPU需要读取主存中的数据时,首先会查询Cache中是否存在该数据。

如果存在,则直接从Cache中读取数据;如果不存在,则从主存中读取数据,并将数据存储到Cache中。

cache实验报告

cache实验报告《cache实验报告》在计算机科学领域中,cache(缓存)是一种用于存储临时数据的高速存储器,用于加快数据访问速度。

在本次实验中,我们对cache进行了一系列的实验,以探究其对计算机系统性能的影响。

首先,我们设计了一个简单的计算机系统模型,包括CPU、内存和cache。

我们使用了不同大小和结构的cache,并对其进行了性能测试。

通过比较不同cache结构下的数据访问速度和命中率,我们发现了cache大小和关联度对性能的影响。

较大的cache和更高的关联度可以显著提高数据访问速度和命中率,从而提升整个系统的性能。

接着,我们对cache的替换策略进行了实验。

我们比较了最常见的替换策略,如LRU(最近最少使用)、FIFO(先进先出)和随机替换。

通过实验结果,我们发现不同的替换策略会对cache的性能产生显著影响。

在某些情况下,合适的替换策略可以提高cache的命中率,从而提高系统的整体性能。

最后,我们对cache的一致性和一致性维护进行了实验。

我们测试了不同的一致性协议,如MESI(修改、独占、共享、无效)协议和MOESI(修改、独占、共享、无效、所有者)协议。

通过实验,我们发现一致性协议的选择对cache的性能和系统的稳定性有着重要影响。

合适的一致性协议可以有效减少数据访问的冲突和错误,提高系统的可靠性和性能。

综上所述,本次实验对cache进行了全面的性能测试和分析,探究了cache对计算机系统性能的影响。

通过实验结果,我们得出了一些重要结论,为优化计算机系统性能提供了重要的参考和指导。

希望本次实验结果能够对相关领域的研究和应用产生积极的影响。

多核Cache替换策略实验

实验三:多核Cache替换算法研究实验报告一、实验背景1.实验要求设计新的多核cache替换算法使用CRC模拟器及老师提供traces对算法进行测试分析实验结果。

2.实验环境简介CRC(CacheReplacementCompetition)是一个模拟Cache替换的环境,运行于linux32位或64位操作系统系下,通过对其中replacement_state.cpp和replacement_state.h两个文件进行编写完成不同Cache替换算法的测试。

3.实验过程a)配置CRC模拟器环境b)在CRC目录下新建一个trace目录,包括单核及多核c)研究并实现算法DIP-SDd)测试单核、多核(四核为佳),其中单核参数UL3:1024:64:16,4核参数UL3:4096:64:16e)根据CPI及LLCMisses分析实验结果二、本组算法思想多核处理器通常包含多级Cache,L1Cache与核耦合紧密,多为各处理器核私有;最后一级Cache(LLC)及更高层次Cache则多为大容量Cache,组织方式比较多样,是访存能否在片上命中的最后一道屏障,因此Cache资源管理的研究多集中在LLC上。

1.传统LRU算法传统的LRU替换策略在片上Cache中被广泛使用,对于高局部性工作集有很好的性能,但是LRU替换策略仅仅考虑数据块的最近访问的信息,却不关心数据块被访问的频率,当Cache容量小于程序的工作集时,Cache也会表现出抖动现象(即发生冲突缺失:被替换出Cache的数据块被不断的换进换出Cache),会导致计算机性能下降。

这是因为替换前后的数据有一定的相关性,LRU的替换原则是将新数据放到MRU上。

这样一来,可能被替换出去的数据可能马上就又会被用到,而很多没有被替换的LRU位置上的数据实际上并不可能总是被用到,所以cache的访问需要再次访问内存。

2.本次实验实现的算法本次实验共完成了Bubble、LIP、BIP及DIP-SD这几种算法,下面将分别阐述这几种算法的思想。

片上多核处理器二级Cache结构及资源管理技术研究

片上多核处理器二级Cache结构及资源管理技术研究处理器与内存之间访问速度差距日益增大,有效组织和利用片上Cache资源以减少片外存储访问对于提升处理器性能至关重要。

随着多核处理器的普及和半导体工艺的进步,芯片将集成更多的核,给二级Cache结构设计带来更大的压力和挑战。

当前主流多核处理器采用基于LRU替换策略的共享或者私有二级Cache结构设计。

然而,单一的共享或者私有Cache结构设计不能有效权衡容量与访问延迟。

共享Cache结构能够有效利用资源,但是全局线延迟导致较慢的访问速度;私有Cache结构通过数据复制获得较快访问速度,但是容量限制导致较多的访问失效。

此外,受组相联度、应用等因素的影响,LRU替换策略与理论最优替换策略之间的性能差距日趋增大。

针对上述问题,本文深入研究了多核处理器中二级Cache资源的组织与管理机制,提出一种基于全局替换策略的可变相联度混合Cache结构模型,研究基于存储访问需求变化的动态容量划分与组均衡管理机制,并提供低功耗与可扩展优化。

论文的创新点如下:1.提出面向CMP的可变相联度混合Cache结构CMP-VH。

CMP-VH将二级Cache划分成一种优化的私有/共享结构,Tag私有,数据部分私有部分共享。

CMP-VH基于数据块的重用信息进行全局替换,并支持核间容量划分以适应不同应用存储访问需求的变化。

使用Simics模拟器搭建8核片上多处理器平台,对SPLASH并行程序负载的模拟实验结果表明,在相同总容量前提下,CMP-VH结构下的平均二级Cache失效率与传统共享Cache结构接近,比传统私有Cache结构降低约23.37%。

2.提出基于数据项动态分配的容量划分技术VH-PAD。

VH-PAD根据各个核的容量需求进行资源分配,包含初始化、重划分和回退三个阶段。

初始化阶段赋予每个核相同数目资源;重划分阶段基于当前划分容量的饱和程度评估容量需求以指导容量划分;回退阶段基于当前占用容量判断是否撤销重划分阶段操作。

P2010多核处理器面向低功耗的共享Cache划分方案

Hale Waihona Puke 多核处理器面向低功耗的共享 Cache 划分方案 A L ow Pow er Orient ed M echanism for Shared Cache Part itioning on CM P s

熊 伟 , 殷建平 , 所 光 , 赵志恒 XIONG Wei, YIN Jian ping, SUO Guang, ZHAO Zhi heng ( 国防科学技术大学计算机学院 , 湖南 长沙 410073) ( School of Computer Science, National University of Defense Technology, Changsha 410073, China)

1

引言

IBM 最多 32 线程 Pow er7 系 列芯 片、 Intel 公司 的 16 线 程 N ehalem 和 AM D 公司的 6 核 O pter on 。 但是 , 随着片上集成的核的数目增多 , 处 理器对存储系 统的访问随之 加剧。 为满 足系 统的 访存 需求 , 片 上 Cache 特别是最后一级 Cache( 目 前主流 为 L2 级 ) 的容 量不断 增 大 , 其功耗所占系统总功耗的比重也越来越大。目前 , 多数 多核处理器最后一 级 Cache 采用 的是共 享方 式 , 因此研 究 如何减少多核共享 Cache 的能耗具有很实际的意义。 而在 实际应用 中 , 大容 量 Cache 并不 是 时 时 都能 得 到 充 分 利

图1

共享 Cache 划分框架

Cache 的 T ag 和 L RU 信息的 阵列。在 L 2 Cache 相联 度为 A 的系统 中 , 它还 包含了 A + 1 个硬 件计 数器 C 1 , C2 , , C A , M issCounter , 这 些 计 数 器 用 于记 录 不 同 栈 距 离 位 置 Cache 列的命中次数。 M RM 的工作过程为 : 当其监控 到所 在核的 L2 访问端口 失效地址时 , 首先在自身的 T A G 阵列 中查找 , 看是否 命中 , 若未 命中 , 则 计 数器 M iss Counter 加 1; 若命中 , 则命中 T ag 对 应的 L RU 值所 索引 的计 数器 加 1 。因此 , M R M 可以得到不同栈 距离的 Cache 列的命 中次 数。根据 L RU 栈距离特性 [ 9] , 栈距离为 n 的位置的失效率 为:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验三:多核Cache替换算法研究实验报告一、实验背景1.实验要求设计新的多核cache替换算法使用CRC模拟器及老师提供traces对算法进行测试分析实验结果。

2.实验环境简介CRC(CacheReplacementCompetition)是一个模拟Cache替换的环境,运行于linux32位或64位操作系统系下,通过对其中replacement_state.cpp和replacement_state.h两个文件进行编写完成不同Cache替换算法的测试。

3.实验过程a)配置CRC模拟器环境b)在CRC目录下新建一个trace目录,包括单核及多核c)研究并实现算法DIP-SDd)测试单核、多核(四核为佳),其中单核参数UL3:1024:64:16,4核参数UL3:4096:64:16e)根据CPI及LLCMisses分析实验结果二、本组算法思想多核处理器通常包含多级Cache,L1Cache与核耦合紧密,多为各处理器核私有;最后一级Cache(LLC)及更高层次Cache则多为大容量Cache,组织方式比较多样,是访存能否在片上命中的最后一道屏障,因此Cache资源管理的研究多集中在LLC上。

1.传统LRU算法传统的LRU替换策略在片上Cache中被广泛使用,对于高局部性工作集有很好的性能,但是LRU替换策略仅仅考虑数据块的最近访问的信息,却不关心数据块被访问的频率,当Cache容量小于程序的工作集时,Cache也会表现出抖动现象(即发生冲突缺失:被替换出Cache的数据块被不断的换进换出Cache),会导致计算机性能下降。

这是因为替换前后的数据有一定的相关性,LRU的替换原则是将新数据放到MRU上。

这样一来,可能被替换出去的数据可能马上就又会被用到,而很多没有被替换的LRU位置上的数据实际上并不可能总是被用到,所以cache的访问需要再次访问内存。

2.本次实验实现的算法本次实验共完成了Bubble、LIP、BIP及DIP-SD这几种算法,下面将分别阐述这几种算法的思想。

2.1.Bubble(冒泡替换算法)[1]冒泡替换算法将数据块被访问的频率和访问的最近信息考虑在内。

冒泡替包括插入策略、推进策略和替换策略。

为每个Cache组(set)设置一个队列,把这个队列称之为冒泡队列。

插入策略是指一个将要被调入Cache的数据块放在冒泡队列的底部,因为它仅仅被访问一次,且小于所有其它的数据块被访问的次数。

推进策略是指当一个数据块命中时,命中的数据块就和其上方相邻的数据块交换其位置;如果命中的数据块已经是队列的最顶端了,则保持其位置不变。

推进策略移动经常被访问的数据块到冒泡队列的顶端,移动不经常被访问的数据块到冒泡队列的底部。

因为最近被访问的数据块,逐步向冒泡队列的顶端推进(逐渐远离冒泡队列的底部),所以同时考虑到了数据块被访问频率和最近访问信息。

替换策略是指被访问的数据块不在Cache中时,被替换出Cache的数据块有两种选取方法:选取冒泡队列顶端的数据块作为驱出块;选取冒泡队列的底部数据块作为驱出块。

为每个Cache组(set)设置一个组命中标签H,初始化为0,当H值为1时,被替换的数据块从冒泡队列的底部选取;当H值为0时,被替换的数据块从冒泡队列的顶端选取,并且其余的数据块依次向冒泡队列顶端推进一个位置。

2.2.LIP(LRUInsertionPolicy)LRU策略对于高局部性工作集有很好的性能,但是对于那些内存使用密集并且超过可用cache的工作集来说则性能非常低下。

LRUInsertionPolicy(LIP)策略则将新的访问位置放在LRU位置。

只有当它们存在LRU位置中被引用时,才将它们提升到MRU位置中。

这样,数据先被放到LRU位置上,处理器开始访问,由于LRU上的数据正式处理器需要的数据,所以马上会被放到MRU位置上,如此一来,无形中扩大了可用cache的大小。

当数据并未被访问到的时候,继续向存储器要数据,但是这个时候并不是全部将需要的数据给替换,而是LRU位置上的一部分数据会保存在cache中,可以提高cache的命中率。

2.3.BIP(BimodalInsertionPolicy)由于LIP没有年龄机制,LIP策略会导致部分不再被引用的line处于non-LRU的位置上,并且不会变更给定应用程序的工作集sets。

在这样的情况下,我们提供一种新的策略,BimodalInsertionPolicy(BIP),它在一个很低的概率下,将部分新的访问集放入MRU位置。

BIP策略包含一个参数ε,控制新进来的数据被替换到MRU位置上的比例。

我们可以看到,在传统的LRU策略中ε=1,而在LIP中ε=0。

2.4.DIP-SD(DynamicInsertionPolicyviaSetDueling)[2]DIP动态的评估两种策略的miss情况,从中选择更好的策略。

数据集分为三个部分:划分给LRU策略数据集、划分给BIP策略数据集、划分给正常策略。

当未命中LRU数据集时则PSEL加1,当未命中BIP数据集时减1。

当MSB(PSEL)最高位为1时则选择LRU 策略来作为下一次正常数据集中Cache替换策略;否则选择BIP策略作为下一次Cache替换策略。

数据集设定策略采用论文[2]中设定的方法,如下所示:按照Set个数将数据集进行分类:假设共有N个set,每种策略包括K个set,将set划分为N/K个相等区域。

为每个数据集提供2个bit的数据位以区分每个数据集的类型:分配给LRU策略、分配给BIP策略数、分配给正常使用。

同时,对每个set进行log2N位的二进制编码,如N=64,则第10个set编码号为001010,如果编码后高(log2N)/2位于低(log2N)/2位相同,则将数据划分给LRU策略数据集;若互补,则划分给BIP策略数据集;其余则为正常数据集。

3.研究但未实现的算法-RRIP(Re-ReferenceInsertionPolicy)[3]RRIP预测数据块的下一次访问间隔,尽量把访问时间间隔较小的数据块留在cache中,从而提高cache的命中率。

具体算法描述如下:将LRU替换算法中LRU端作为RRPtail,MRU端作为RRPhead,如下图:(1)VictimSelectionPolicy:选择PPRV值最大的块换出cache。

即从RRPhead开始扫描,找到RRPV=3的块将其换出;若没有,则将所有的RRPV值加1。

(2)InsertionPolicy:插入新的数据块,并将它的RRPV值设为1或者2。

这样做可以使得新的数据块在cache中存在的时间不至于太长也不太短,这就类似于将新的数据块插入到链的中间部分。

(3)UpdatePolicy:当cache命中时,将命中块的RRPV值设为0。

RRIP替换策略可以在混合模式下,在cache中保存一部分被访问过的数据块,提高cache的命中率,能够将新插入但无后续访问的块尽早被替换.。

三、算法设计及实现由于LIP算法及BIP算法实现与LRU算法实现非常类似且较为简单,因此这里的算法设计重点讲解Bubble算法及DIP-SD算法的设计。

具体实现代码请详见【附录】中源代码。

Bubble算法及DIP-SD算法均主要参考他人论文,但在具体实现中有所改动,主要包括:Bubble算法中插入策略与替换策略所完成的功能有所重复,因此在实现时以替换策略的实现为主,且由于使用到具体的查询次数,因此在cache块的初始化中将其访问次数进行了初始化设置;DIP-SD算法中有关2bit标志位用来识别set所属区域类型,由于在具体实现时发现不使用标志位也可判断该set所属的类型,因此在实现时未设置标志位。

3.1Bubble算法设计DIP算法设计四、实验结果分析1.单核实验结果及分析(发现在32位CRC中执行较慢,后面测试时候移植到64位服务器上测试,加快了进度)179LRU179RANDOM179BIP179LIP179DIP-SD179BUBBLE(注:bubble算法无论在32位还是64位CRC上都没运行起来,遇到“段错误”,至今未能解决)181LRU181RANDOM181BIP181LIP181DIP-SD从上图可以看出,LIP算法则在缺页及CPI中均明显优于LRU算法。

4核实验结果及分析mix_LRUmix_RANDOMmix_BIPmix_LIPmix_DIP-SD从上图可以看出,LIP算法则在缺页及CPI中均明显优于LRU算法。

实验遇到问题:移植到64位服务器时候make产生错误,找不到/usr/lib64解决方案:是因为ubuntu并没有该路径,所以要修改原CRC的makefile,将其中/usr/lib64/的路径改为:/usr/lib/x86_64-linux-gnu实验遇到问题:制作mix_ls_cat.mix解决方案:cat > traces/mix_ls_cat.mixhome/muye/CRC/traces/ls.out.trace.gzhome/muye /CRC/traces/cat.out.trace.gzhome/muye /CRC/traces/ls.out.trace.gzhome/muye /traces/cat.out.trace.gzCTRL-D这里用了179、181、179、181。

实验所用主要命令:../bin/etrace.64 -threads 1 -t ../traces/181.out.trace.gz -o 179BUBBLE.stats -cache UL3:1024:64:16 -LLCrepl 1../bin/etrace.64 -threads 4 -mix ../traces/mix_ls_cat.mix -cache UL3:4096:64:16 -autorewind 1 -icount 1 -o mix_ls_cat.stats -LLCrepl 1五、组员分工【参考文献】1.《多核系统中共享Cache的冒泡替换算法》林晓敏,桂婷,乔福明,胡同森《微电子学与计算机》28卷第4期2.《AdaptiveInsertionPoliciesforHigh-PerformanceCaching》MoinuddinQureshi,Aamer Jaleel,YalePatt,SimonSteelyJr.,J oelEmer.ISCA’073.《HighPerformanceCacheReplacementUsingRe-ReferenceIntervalPrediction(RRIP)》Aamer Jaleeletal.ISCA2010。