S3C2410简介

s3c2410简介

B Host 2个端口的usb host 遵从OHCI Rev 1.0 和USB规范1.1版兼容 B Device 1个端口的USB Device 可带5个节点的USB Device 和USB规范1.1版兼容

6.SD Host 接口 和SD存储卡1.0版协议兼容 和SDIO存储卡1.0版协议兼容 带64个字节的FIFO存储器支持Tx/Rx 基于DMA或基于中断的操作 和多媒体卡2.11版协议兼容

字符型指针(int *)问。

S3C2410实例

1.和诸多元器件组合在一起供平时学习、实 验、开发等使用。 2.宏分布数字化工业测控系统 3.数码汽车音响和汽车综合信息监测系统 4.煤矿远程数字化测控安全系统 5.视频监控系统

s3c2410引脚介绍

S3C2410共有272引脚,采 用FBGA封装,主要分为 总线控制信号、各类元器 件接口信号以及电源时钟 控制信号。引脚分布底视 图如图所示。各引脚名称 如书中表所示。

s3c2410特殊功能寄存器

寄存器的状态决定硬件如何工作,为了使硬件工作于某 种状态,可以通过修改寄存器的值来实现。 例如:S3C2410X处理器的工作频率可达203MHz,但决不是只 能工作于该频率。可以通过修改内部寄存器的值,使处理器 工作在不同的频率下,通常所说的超频就是通过修改CPU的 时钟相关的寄存器的值来实现的。 在S3C2410的地址空间0x48000000~0x60000000之间, 存有大量的SFR(Special Function Registers,特殊功能 寄存器)用于实现对内部外围模块的控制。

三星ARM2410简介

1.S3C2410 概述 2.S3C2410主要特性 3.s3c2410引脚介绍 4.s3c2410特殊功能寄存器 5.S3C2410实例

s3c2410s3c2440处理器介绍

鲁东大学 LUDONG UNIVERSITY

S3C2410A结构框图

S3c2440处理 器结构框图

❖ S3C2410A在片上,S3通C过24A1M0ABA简总介线集成了以下资源:

AHB总线-各类控制器

✓支持STN和TFT的LCD控制器 ✓ NAND Flash 控制器 ✓存储管理器(片选逻辑和SDRAM控制器) ✓时钟及电源管理器

APB总线-设备与接口 ✓ 3通道UART、 ✓ 4通道DMA、 ✓ 4通道PWM定时器、 ✓ I/O口、 ✓ RTC、

: 1M bps

CTS/RTS

Key

Debug

GPS

BT

Matrix

SRAM/ROM /NOR Flash /OneNAND/OneDRAM

1Gbit X 6banks (x8/x16/x32)

UART0 SMC

UART1

NAND

NAND Flash IF

SDRAM/mDDR

1Gbit X 2banks (x16/x32)

PMIC

Main Charger

Li-Ion

USB Charger

Control

Data

5V DC

5V USB

TV-out

TV

TFT/CSTN LCDC + SPI(GPIO) + TSADC RGB I/F

Main TFT LCD & TSP

1/2/4/8/16 bpp Up to QVGA

SD/SDIO IIS I/F

✓ I2C总线接口、 ✓ I2S总线接口、 ✓ USB主设备、USB从设备 ✓ SD主卡和MMC(Multi Media Card,多媒体卡)卡接口 ✓2通道的SPI接口)

第三部分ARM芯片S3C2410简介及硬件系统结构设计

AHB

AHB主要用于高性能模块(如CPU、DMA和DSP等)之间的连接。 APB APB主要用于低带宽的周边外设之间的连接,例如UART等

6

总线和总线桥

CPU

低速设备

高速总线

桥

低速总线

存储器

高速设备

数据

低速设备

7

S3C2410A的内部结构

8

S3C2410A片上资源

ARM920T核、工作频率203MHz; 16KB 数据Cache, 16KB 指令Cache,MMU,外部存储器控制器; LCD控制器(支持黑白、灰度、Color STN、TFT屏),触摸屏接口; NAND FLASH控制器,SD/MMC接口支持,4个DMA通道; 3通道UART、1个多主I2C总线控制器、1个IIS总线控制器; 4通道PWM定时器及一个内部定时器; 117个通用I/O口; 24个外部中断源;

S3C2410及硬件系统结构设计

1

ARM简介

ARM简介

将技术授权给 其它芯片厂商

...

形成各具特色 的ARM芯片

2

本节提要

1 S3C2410A概述 2 3 4 最小系统

基于ARM芯片的系统设计方法

ARM芯片的裸机开发

3

S3C2410A处理器简介

16/32位ARM920T处理器S3C2410A,三星公司生产 采用了高级微控制器总线(Advanced Microcontroller Bus Architectuer,AMBA)的总线结 构,提供了丰富的片上资源 独立的16KB 指令和16KB 数据哈佛结构的缓存,每个 缓存均为8 个字长度 为手持设备和一般类型应用提供了低价格、低功耗、高 性能小型微控制器的解决方案。

5 ARM9 S3C2410处理器及实验系统概述

�

CPU S3C2410X:16-/32-bit RISC 微处理器,通过200P SODIMM

插槽和主板相联既可以采用S3C2410X的核心板,也可采用 S3C2440(400MHz)核心板 BOOT ROM:支持三种启动方式 – SST 2M-byte – Intel StrataFlash 16M-byte(可选) – SAMSUNG NAND flash 64M-byte/128M-byte (直接smart media card 启动) SDRAM:64M-byte (32M-byte×2) TFT/STN 液晶和触摸屏接口 :SHARP 3.5″真彩TFT液晶屏 3个通道的异步串口,其中一个可以切换为红外(IrDA)接口 两个通道的USB接口,其中一个可以切换为HOST或DEVICE设备

显示部分: 显示部分: LCD SHARP LQ043T3DX02 4.3寸真彩 寸真彩

TFT液晶屏 480 X 272:1个 液晶屏 : 个 VGA接口:支持 接口: 接口 支持640 X 480分辨率 见 分辨率 注释4, 】 【注释 ,6】 LED 8 X 8点阵 点阵 8段数码管:4个 段数码管: 个 注释3】 段数码管 见【注释 】 AIDIO部分: 部分: 部分 AC97耳机接口:1个 耳机接口: 个 耳机接口 麦克风: 1个 见【注释 】 注释5】 麦克风: 个

SUPERIO接口,通过华邦SUPERIO芯片W83977EF扩展了如下资源:

S3C2410简介

1.16 SPI 接口

������ ������ ������ 兼容2 通道SPI 协议2.11 版 发送和接收具有2×8 位的移位寄存器 可以基于DMA 或中断模式工作

1.17 看门狗定时器

16 位看门狗定时器 在定时器溢出时发生中断请求或系统复位

1.18 USB 控制器

USB 主设备 2 个 USB 主设备接口 遵从OHCI Rev.1.0 标准 兼容USB ver1.1 标准 USB 从设备 1 个USB 从设备接口 具备5 个Endpoint 兼容USB ver1.1 标准

1.10 DMA 控制器

������ 4 通道的DMA 控制器; ������ 支持存储器到存储器,IO 到存储器, 存储器到IO 和IO 到IO 的传输 ������ 采用猝发传输模式加快传输速率。

1.11 A/D 转换和触摸屏接口

������ ������ 8 通道多路复用ADC 最大500KSPS/10 位精度

ldr r0, =|Load$$EXCEPTION_EXEC$$Base| ;source data ldr r1, =|Image$$EXCEPTION_EXEC$$Base| ;place exception talbe at 0x0 ldr r2, =|Image$$EXCEPTION_EXEC$$Length|

1.6 具有脉冲带宽调制功能的定时器

4 通道16 位具有PWM 功能的定时器,1 通 道16 位内部定时器,可基于DMA 或中断工 作 可编程的占空比周期,频率和极性 能产生死区 支持外部时钟源

1.7 RTC(实时时钟)

������ 全面的时钟特性:秒、分、时、日期, 星期,月和年; ������ 32.768KHz 工作 ������ 具有报警中断 ������ 具有节拍中断

s3c2410中文手册

s3c2410中文手册简介S3C2410 是一种嵌入式处理器,由韩国三星电子公司设计和制造。

它是一款高度集成的 ARM 架构芯片,广泛应用于各种移动设备中,如智能手机、平板电脑、PDA 等。

本手册将详细介绍 S3C2410 芯片的特性、功能和使用方法,帮助开发人员更好地理解和应用该芯片。

芯片特性S3C2410 芯片具有以下主要特性:1.ARM920T 内核: S3C2410 芯片采用了 ARM920T 内核,它是一种高性能、低功耗的 32 位 RISC 处理器。

ARM920T 内核支持 ARMv4T 指令集,并具有强大的计算和处理能力。

2.高度集成的外设: S3C2410 芯片内集成了许多常用的外围设备,包括 UART、SPI、I2C、PWM 等。

这些外设可满足各种应用需求,简化了系统设计和连接。

3.多种接口: S3C2410 芯片提供了丰富的接口,如LCD 控制器、触摸屏控制器、SDIO 控制器等。

这些接口允许连接各种外部设备,如显示屏、输入设备、存储卡等,实现更丰富的功能。

4.低功耗设计: S3C2410 芯片采用先进的低功耗设计技术,具有很低的静态功耗和动态功耗。

这使得它非常适合于移动设备,延长了电池寿命。

芯片功能GPIOS3C2410 芯片提供了多个 GPIO 管脚,用来实现输入和输出功能。

GPIO 管脚可以通过软件配置为输入模式或输出模式,并可以设置电平状态。

开发人员可以利用GPIO 实现各种功能,如控制 LED 灯、读取按键状态等。

UARTS3C2410 芯片内集成了多个 UART 模块,用于串口通信。

每个 UART 模块都提供了数据传输和接收的功能,并支持多种通信协议,如 RS232、RS485 等。

开发人员可以使用 UART 实现与外部设备的串口通信。

LCD 控制器S3C2410 芯片具有强大的 LCD 控制器,支持多种显示模式和分辨率。

LCD 控制器可以控制显示屏的像素点,实现图形显示和文字显示功能。

S3C2410处理器特点

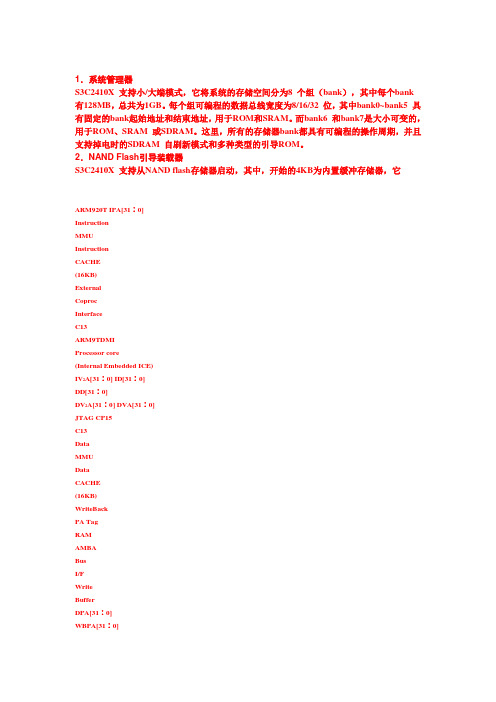

1.系统管理器S3C2410X 支持小/大端模式,它将系统的存储空间分为8 个组(bank),其中每个bank 有128MB,总共为1GB。

每个组可编程的数据总线宽度为8/16/32 位,其中bank0~bank5 具有固定的bank起始地址和结束地址,用于ROM和SRAM。

而bank6 和bank7是大小可变的,用于ROM、SRAM 或SDRAM。

这里,所有的存储器bank都具有可编程的操作周期,并且支持掉电时的SDRAM 自刷新模式和多种类型的引导ROM。

2.NAND Flash引导装载器S3C2410X 支持从NAND flash存储器启动,其中,开始的4KB为内置缓冲存储器,它ARM920T IPA[31∶0]InstructionMMUInstructionCACHE(16KB)ExternalCoprocInterfaceC13ARM9TDMIProcessor core(Internal Embedded ICE)IV2A[31∶0] ID[31∶0]DD[31∶0]DV2A[31∶0] DVA[31∶0]JTAG CP15C13DataMMUDataCACHE(16KB)WriteBackPA TagRAMAMBABusI/FWriteBufferDPA[31∶0]WBPA[31∶0]LCDCONT.LCDDMAUSB Host CONTExtMasterNAND CONT.NAND Flash BootLoaderClock Generator(MPLL) Bridge & DMA(4Ch)BUS CONT.Arbitor/DecodeInterrupt CONT.PowerManagementMemory CONT.SRAM/NOR/SDRAMUART 0,1,2USB DevfceSDI/MMCWatchdogTimerBUS CONT.Arbitor/DecodeSPI 0,1I2CI2SGPIORTCADCTimer/PWM0~3,4(Internal)APBBUSAHBBUS图4.11 S3C2410X系统结构图在启动时将被转载(装在or 转载)到SDRAM 中并执行引导,之后该4KB 可以用作其他《嵌入式Linux应用程序开发详解》——第4章、嵌入式系统基础用途。

ARM微处理器 S3C2410的简介

ARM微处理器 S3C2410的简介1.1 ARM微处理器的介绍1)ARM微处理器的工作状态和工作模式从编程的角度看,ARM微处理器的工作状态有两种,可在两种状态之间切换:第一种为ARM状态,此时处理器执行32位的字对齐的ARM指令;第二种为Thumb状态,此时处理器执行16位的、半字对齐的Thumb指令。

2)ARM微处理器支持7种运行模式,分别为:用户模式(USR):ARM处理器正常程序执行的模式。

快速中断模式( FIQ ):用于高速数据传输或通道处理用于快速中断服务程序。

当处理器的快速中断请求引脚有效,且CPSR(6位)中F位为0时(开中断),会产生FIQ异常。

外部中断模式( IRQ ):用于通用的中断处理,当处理器的外部中断请求引脚有效,且CPSR(7位)中I位为0时(开中断),会产生IRQ异常。

系统的外设可通过该异常请求中服务。

特权模式或管理员模式(SVE):操作系统使用的保护。

执行软件中断SWI 指令和复位指令时,就进入管理模式,在对操作系统运行时工作在该模式下。

1.2 S3C2410微处理器1.2.1 概述S3C2410是韩国三星公司的一款基于ARM920T内核的16/32位RISC嵌入式微处理器,主要面向手持设备以及高性价比,低功耗的应用。

运行的频率可以达到203MHz。

ARM920T核由ARM9TDMI,存储管理单元(MMU)和高速缓存三部分组成。

其中MMU可以管理虚拟内存,高速缓存由独立的16KB地址和16KB数据高速Cache 组成。

ARM920T有两个协处理器:CP14和CP15。

CP14用于调试控制,CP15用于存储系统控制以及测试控制。

ARM920T体系结构框图图2-1 ARM920T体系结构框图1.2.2 S3C2410微处理器的结构S3C2410内部结构原理内部原理框图如下:图2-2S3C2410内部结构原理ARM 微处理器中共定义了37个编程可见寄存器,每个寄存器的长度均为32位。

ARM9 S3C2410开发板简介

Page 1 of 13S3C2410开发板数据手册强烈推荐这款2410开发板 超值提供ARM9 2410开发板+全新三星原装3.5三星TFT 带驱动板和触摸 1400元 LCD 单卖 550元 全新三星原装3.5三星TFT 带驱动板和触摸 GPRS 模块单卖 400元LCD 简介:生产商: SamSung 型 号: L TV350 成 色: 全新原装特 性: 26万色TFT 、分辨率320*240、带触摸屏、LED 背光 接 口: RGB/CPU 总线可选, 直接接S3C2410 附 件: 电压驱动板,2.0mm 双排插引出接口ARM9 2410硬件平台综述ARM9 2410平台由核心板(Core-Board)和底板(Bottom-Board)以及3.5寸LCD(带触摸)组成。

如下图所示:板子背面示意图:● ARM2410 的主要特点1、Core-Board(核心板)CPU: Samsung的S3C2410x处理器,工作频率达203MHz;FLASH ROM: 64MB Nand Flash,可选配为各种容量8位的NANDFLASH;NOR FLASH(SST39VF1601)提供2MBNor Flash;SDRAM : 64M (Samsung K4S561632H-Tc75) 2片4Banks×4Mbits ×16bits SDRAMPC100/PC133兼容;RTC 实时时钟: 外接32.768KHz的晶振,带有备份电池,可保持时钟NAND FLASH --NOR FLASH 启动选择开关两个I/O 口连接两个LED,方便用户调试自己的程序2、Bottom-Board (底板)LCD 接口: 支持各种TFT LCD(50PIN2.0排针)触摸屏接口:可接四线电阻式触摸屏;串口:两个RS232串口;1路TTL电平接口GPRS/GSM接口: SIMCOM公司GSM/GPRS模块USB Device接口: 1个DEVICE接口(USB 1.1协议)SPI 接口IIC总线接口ADC模数转换接口: 4路10位AD两个USB HOST: 1个USB Host A型接口(USB1.1协议),1个USBHost B型接口(USB1.1协议);SD/MMC 接口: 支持SD卡、同时兼容MMC卡;JTAG接口:标准ARM 20针JTAG&&Wiggle&&ICE 接口;IIS :采用UDA1341TS IIS 接口(立体声输出,MIC 输入),外部中断接口: 8路外部中断输入网卡:提供10M Ethernet芯片CS8900A,采用集成隔离变压器的RJ45接口,并带有Page 2 of 13Page 3 of 13ACT 、 LINK 指示灯蜂鸣器: 带驱动电路。

基于S3C2410的系统硬件设计

基于S3C2410的系统硬件设计引言:S3C2410是一款高度集成的32位微处理器。

它集成了一个强大的ARM9核心,以及包括SDRAM控制器、NOR Flash Boot ROM、LCD控制器、UART、USB主机和设备端口、SD卡接口等外设。

基于S3C2410的系统硬件设计需要考虑系统芯片的功能特点和外设接口的设计要求,以确保系统能够稳定、高效地运行。

主要部分:1.微处理器核心:S3C2410集成了ARM920T核心,具有16KB指令缓存和16KB数据缓存。

在硬件设计中,需要正确连接CPU核心的引脚,并为其提供足够的电源和地引脚。

此外,还需要提供适当的复位电路和时钟电路,以保证CPU能够正常工作。

2. 外部存储器:S3C2410具有片内存储器控制器,支持SDRAM和NOR Flash存储器。

在硬件设计中,需要根据系统的存储需求选择适当的存储器,并正确连接到芯片的存储器接口。

同时,需要提供相应的存储器芯片供电和地引脚。

3.LCD控制器:S3C2410内部集成了一款多功能LCD控制器,支持多种显示模式和分辨率。

在硬件设计中,需要根据系统的显示需求选择适当的LCD屏幕,并将其连接到芯片的LCD接口。

同时,还需要提供相应的LCD背光供电和地引脚。

4.UART和USB接口:S3C2410内部集成了多个UART和USB接口,用于与外部设备进行通信。

在硬件设计中,需要根据系统的通信需求选择适当的接口,并将其连接到芯片的相应引脚。

同时,还需要提供相应的电源和地引脚。

5.外部中断和定时器:S3C2410具有多个外部中断和定时器,可用于处理外部事件和计时。

在硬件设计中,需要根据系统的需求选择适当的中断和定时器,并将其连接到芯片的相应引脚。

同时,还需要提供相应的电源和地引脚。

6.SD卡接口:S3C2410内部集成了一个SD卡接口,可用于存储和读取数据。

在硬件设计中,需要将SD卡接口连接到芯片的相应引脚,并提供相应的电源和地引脚。

嵌入式ARM-S3C2410

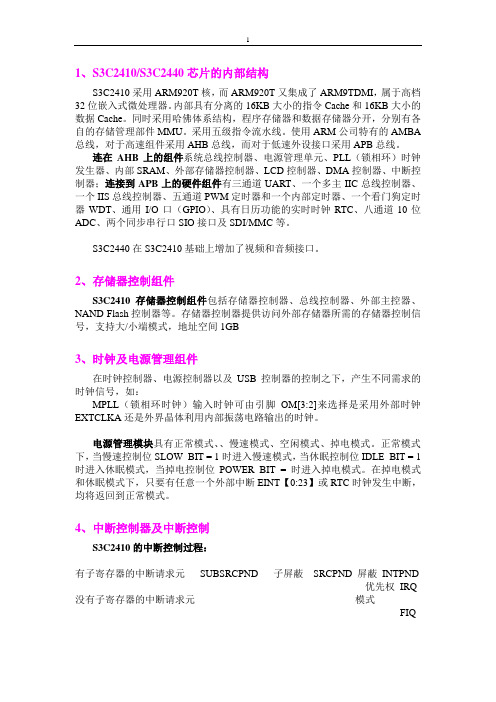

1、S3C2410/S3C2440芯片的内部结构S3C2410采用ARM920T核,而ARM920T又集成了ARM9TDMI,属于高档32位嵌入式微处理器。

内部具有分离的16KB大小的指令Cache和16KB大小的数据Cache。

同时采用哈佛体系结构,程序存储器和数据存储器分开,分别有各自的存储管理部件MMU。

采用五级指令流水线。

使用ARM公司特有的AMBA 总线,对于高速组件采用AHB总线,而对于低速外设接口采用APB总线。

连在AHB上的组件系统总线控制器、电源管理单元、PLL(锁相环)时钟发生器、内部SRAM、外部存储器控制器、LCD控制器、DMA控制器、中断控制器;连接到APB上的硬件组件有三通道UART、一个多主IIC总线控制器、一个IIS总线控制器、五通道PWM定时器和一个内部定时器、一个看门狗定时器WDT、通用I/O口(GPIO)、具有日历功能的实时时钟RTC、八通道10位ADC、两个同步串行口SIO接口及SDI/MMC等。

S3C2440在S3C2410基础上增加了视频和音频接口。

2、存储器控制组件S3C2410存储器控制组件包括存储器控制器、总线控制器、外部主控器、NAND Flash控制器等。

存储器控制器提供访问外部存储器所需的存储器控制信号,支持大/小端模式,地址空间1GB3、时钟及电源管理组件在时钟控制器、电源控制器以及USB控制器的控制之下,产生不同需求的时钟信号,如:MPLL(锁相环时钟)输入时钟可由引脚OM[3:2]来选择是采用外部时钟EXTCLKA还是外界晶体利用内部振荡电路输出的时钟。

电源管理模块具有正常模式、、慢速模式、空闲模式、掉电模式。

正常模式下,当慢速控制位SLOW_BIT = 1时进入慢速模式,当休眠控制位IDLE_BIT = 1时进入休眠模式,当掉电控制位POWER_BIT = 时进入掉电模式。

在掉电模式和休眠模式下,只要有任意一个外部中断EINT【0:23】或RTC时钟发生中断,均将返回到正常模式。

S3C2410——SD卡(个人总结版)

0

4095

数据

0

CRC

1

帧起始标记

帧结束标记

16比特CRC校验

SDI模式——帧

宽带数据帧(Data0-Data3同时传输数据)

DAT3 DAT2

0 0 0 0

4095 4094 4093 4092

数据 数据 数据 数据

3 2 1 0

CRC CRC CRC CRC

1 1 1 1

DAT1

DAT0

SDI模式——时序

S3C2410——SD卡

SD卡简介

SD卡(Secure Digital Memory Card)中文翻译

为安全数码卡,是一种基于半导体快闪记忆器的新一代

记忆设备,它被广泛地于便携式装置上使用,例如数码

相机、个人数码助理(PDA)和多媒体播放器等。SD卡由

日本松下、东芝及美国SanDisk公司于1999年8月共同

开发研制。大小犹如一张邮票的SD记忆卡,重量只有2

克,但却拥有高记忆容量、快速数据传输率、极大的移

动灵活性以及很好的安全性。

DATA0-3:数据引脚(双向) CMD:命令引脚(双向) 总线 接口

0 1

2

3

4

5

6

7 8

VDD:3.3V电压

CLK:时钟 3、4号引脚:地线

寄

存

控制器 器 组

FLASH

(Card Specific Data)专用数据寄存器,保存SD卡的 配置信息,包括卡的容量、数据访问时间、最大传输率、 最大读数据长度、最大读写电流、擦除保护和写保护等 信息。

CSD 128

SCR 64

OCR 32

(SD Configuration Reigister)SD卡配置寄存器,包 括SD版本号、SD加密支持和数据总线宽度等信息。

S3C2410数据资料之USB

图 9-37 OUT_CSR1_REG 和 OUT_CSR2_REG 的定义类同 OUT_CSR1_REG 等(见图 9-38,9-39)

图 9-38

图 9-39 EPn_FIFO :FIFI 资料寄存器(见图 9-40)

图 9-40 MAXP_REG :最大资料包长度配置寄存器(见图 9-41)

图

三、S3C2410 USB 内部控制寄存器简介: FUNC_ADDR_REG :USB 设备地址寄存器(见图 9-26) FUNCTION_ADDR :CPU 将由 USB 主机分配的器件地址写入该字段 ADDR_UPDATE :当 CPU 写入新的地址后,置该位来更新 FUNCTION_ADDR 字段中的值

图 9-31 FRAME_NUM_REG:帧计数器(低位资料)(见图 9-32)

图 9-32 FRAME_NUM_REG:帧计数器(高位资料)(见图 9-33)

图 9-33 INDEX_REG:索引寄存器(见图 9-34) INDEX:指向 USB 控制器内的某个 Endpoint

图 9-34 EP0_CSR : Endpoint0 控制状态寄存器(图 9-35) OUT_PKT_RDY :当有效 OUT 通讯包由 USB 控制器写入 FIFO 后,该位被置 1 IN_PKT_RDY :当有效 IN 通讯包由 USB 控制器写入 FIFO 后,该位被置 1 SENT_STALL :如果因为总线冲突而导致控制传输中断,该位将被 USB 控制器置 1 DATA_END :当资料发送完之后,由 CPU 置该位 SETUP_END :当控制传输完成之后,由 CPU 置该位 SEND_STALL :如果收到无效的信令包, CPU 应该在清除 OUT_PKT_RDY 的同时置该位 SERVICED_OUT_PKT_RDY:CPU 通过置该位来清除 OUT_PKT_RDY 状态 SERVICED_SETUP_END:CPU 通过置该位来清除 SETUP_END 状态位

基于S3C2410的RTC模块应用设计

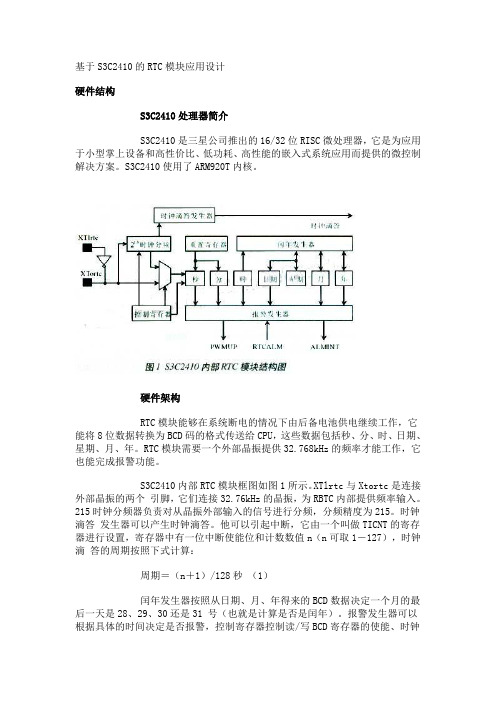

基于S3C2410的RTC模块应用设计硬件结构S3C2410处理器简介S3C2410是三星公司推出的16/32位RISC微处理器,它是为应用于小型掌上设备和高性价比、低功耗、高性能的嵌入式系统应用而提供的微控制解决方案。

S3C2410使用了ARM920T内核。

硬件架构RTC模块能够在系统断电的情况下由后备电池供电继续工作,它能将8位数据转换为BCD码的格式传送给CPU,这些数据包括秒、分、时、日期、星期、月、年。

RTC模块需要一个外部晶振提供32.768kHz的频率才能工作,它也能完成报警功能。

S3C2410内部RTC模块框图如图1所示。

XTlrtc与Xtortc是连接外部晶振的两个引脚,它们连接32.76kHz的晶振,为RBTC内部提供频率输入。

215时钟分频器负责对从晶振外部输入的信号进行分频,分频精度为215。

时钟滴答发生器可以产生时钟滴答。

他可以引起中断,它由一个叫做TICNT的寄存器进行设置,寄存器中有一位中断使能位和计数数值n(n可取1-127),时钟滴答的周期按照下式计算:周期=(n+1)/128秒(1)闰年发生器按照从日期、月、年得来的BCD数据决定一个月的最后一天是28、29、30还是31 号(也就是计算是否是闰年)。

报警发生器可以根据具体的时间决定是否报警,控制寄存器控制读/写BCD寄存器的使能、时钟复位、时钟选择等,重置寄存器可以选择“秒”对“分”进位的边界,提供三个可选边界:30、40或者50秒。

RTC最重要的功能就是显示时间。

在掉电模式下,RTC依然能够正常工作,此时,RTC模块通过外部的电池工作。

电池一般选用能够提供1.8V电压的银芯电池,电池与专用于RTC电源的引脚RTCVDD连接,RTC时间显示功能是通过读/写寄存器实现的,要显示秒、分、时、日期、月、年,CPU必须读取存于BCDSEC,BCDMIN,BCDHOUR,BCDDAY,BCDDATE,BCDMON与 BCDYEAR寄存器中的值,时间的设置也是通过以上的寄存器实现的,即以上寄存器是可读可写的。

第五章-基于S3C2410的系统硬件设计-规范文件-

15、看门狗定时器

■ 看门狗为16位定时器 ■ 当看门狗发生超时的时候,它可以发出中断请求

或者进行系统复位

16、I I C 总线接口

■ 8位串行数据双向传输 ■ 标准模式传送速度100Kbit/秒,快速模式传送

速度400Kbit/秒;

17、I I S 总线接口

■ 1通道基于DMA操作的IIS总线音频接口; ■ 串行数据传输,每通道8位或16位; ■ 传送和接收各有64字节的FIFO; ■ 支持IIS格式和MSB-justified数据格式;

5、时钟和电源管理

■ 片上MPLL和UPLL,UPLL产生时钟给 USB HOST和USB Device,MPLL产生时 钟给CPU,最高频率高达266MHz

■ 片上每个功能模块的时钟输入都可以通过 软件设置来使能或禁止

5、时钟和电源管理

■ 电源模式包括正常模式、慢模式、IDLE模式、关 机模式

NAND Flash 控制器流程 图

the S3C2410Xis equippedwithaninternalSRAMbuffercalled ‘Steppingstone’. Whenbooting, the first4 KBytes ofthe NANDflashmemory willbe loaded intoSteppingstoneand the boot code loaded intoSteppingstonewillbe executed.

5.1.3 Nand Flash控制器

2、NAND Flash 介绍

Samsung、TOSHIBA和Fujistu 支持NAND技 术Flash存储器。

这种结构的闪速存储器适合于纯数据和文件存 储,主要作为Smart Media卡、Compact Flash卡、 PCMCIA ATA卡、固态盘的存储介质,并正成为闪 速磁盘技术的核心。

基于S3C2410的系统硬件设计

基于S3C2410的系统硬件设计概述:S3C2410是一款由三星公司设计的嵌入式系统芯片,采用ARM9架构,主频为200MHz。

在嵌入式系统中,它被广泛应用于各种控制和通信设备。

在本文中,我们将介绍基于S3C2410的系统的硬件设计。

硬件设计:1.处理器:S3C2410芯片是嵌入式系统的核心,它具有强大的计算和控制能力。

在系统设计中,需要考虑处理器的供电和散热问题,以确保其稳定运行。

2.存储器:S3C2410芯片具有32KB的指令缓存和16KB的数据缓存,但通常还需要外部存储器来扩展系统的存储容量。

可以选择使用FLASH存储器作为程序和数据的存储介质。

3.外设接口:S3C2410芯片支持多种外设接口,包括UART、SPI、I2C、USB等。

在硬件设计中,需要根据应用需求选择合适的外设接口,并设计相应的接口电路。

4.显示屏:S3C2410芯片具有LCD控制器,可以驱动液晶显示屏。

在设计中,需要选择合适的显示屏,并设计相应的电路来连接S3C2410芯片和显示屏。

5.输入设备:系统通常需要一些输入设备,如按键、触摸屏等。

在硬件设计中,需要为这些输入设备设计相应的电路,并与S3C2410芯片进行连接。

6.时钟电路:S3C2410芯片需要外部时钟源来提供时钟信号。

在设计中,需要选择合适的时钟电路,并确保时钟信号的稳定性和准确性。

7.电源管理:S3C2410芯片需要稳定的供电电源。

在硬件设计中,需要设计相应的电源管理电路,以确保系统的正常运行。

8.其他外部接口:根据具体应用需求,可能还需要设计一些其他外设接口,如以太网接口、音频接口等。

总结:基于S3C2410的系统硬件设计需要考虑处理器、存储器、外设接口、显示屏、输入设备、时钟电路、电源管理等方面。

在设计过程中,需要充分考虑应用需求,选择合适的硬件组件,并设计相应的电路来连接这些组件。

通过合理的硬件设计,可以确保系统的稳定运行,并满足用户的需求。

S3C2410的RTC实时时钟

#define rBCDSEC (*(volatile unsigned char *)0x57000070)

#define rBCDMIN (*(volatile unsigned char *)0x57000074)

#define rBCDHOUR (*(volatile unsigned char *)0x57000078)

BCDMIN 0x57000074 (R/W) 分时钟当前值 不定

BCDHOUR 0x57000078 (R/W) 时时钟当前值 不定

BCDDAY 0x5700007C BCDDATE 0x57000080 BCDMON 0x57000084

(R/W) (R/W) (R/W)

日时钟当前值 不定 星期当前值 不定 月时钟当前值 不定

#define rBCDYEAR (*(volatile unsigned char *)0x57000088)

精选版课件ppt

4

6、RTC 编程实例

(1)实时时钟初始化函数 void Rtc_Init(void) /********************************************* Function name: Rtc_Init Description : 实时时钟初始化程序 *********************************************/

RTC实时时钟

1、S3C2410的RTC实时时钟

在一个嵌入式系统中,通常采用RTC来提供可靠的 系统时间,包括时、分、秒和年、月、日、星期等,而 且要求在系统处于关机状态下它也能够正常工作(通常 采用后备电池供电)。

它的外围也不需要太多的辅助电路,典型的就是只 需要一个高精度的32.768KHz晶体和电阻电容等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2.7.3 存储器控制器(续1)

— 可通过软件选择大小端 — 地址空间:每个Bank 128Mbytes (总共 1GB) —除 bank0 (16/32-bit) 外,所有的Bank都可以通过编程选择总线宽度 = (8/16/32-bit) — 共 8 个banks

前6个Bank用于控制 ROM, SRAM, etc.

通过提供一系列完整的系统外围设备,S3C2410A大大减少了

整个系统的成本,消除了为系统配置额外器件的需要。

S3C2410X和S3C2410A的区别

(1) A/D 9位升到10位; (2) MMC 的接口频率从10M 升到 20M。 其他功能一样!管脚兼容,封装一样。

S3C2410A可以替代S3C2410X。 S3C2410X01已经停产。

OM [1:0] = 00 OM [1:0] = 01 从Nand Flash 启动; 从16位宽的ROM启动;

OM [1:0] = 10

OM [1:0] = 11

从32位宽的ROM启动;

TEST模式。

2.7.3 存储器控制器

FLASH ROM属于真正的单电压芯片,在使用上很类似 EPROM,因此,有些书籍上便把FLASH ROM作为EPROM的一 种。事实上,二者还是有差别的。 FLASH ROM在擦除时,也要执行专用的刷新程序,但是在 删除资料时,并非以Byte为基本单位,而是以Sector(又称Block)为 最小单位,Sector的大小随厂商的不同而有所不同;只有在写入时 ,才以Byte为最小单位写入; FLASH ROM芯片的读和写操作都是在单电压下进行,不需 跳线,只利用专用程序即可方便地修改其内容。 DRAM,动态随机存取存储器,需要不断的刷新(ms级),才 能保存数据。而且是行列地址复用的,许多都有页模式。

NAND Flash与NOR Flash是有很大不同的。 NOR Flash带有SRAM接口,有足够的地址引脚来寻址,可以 很容易地存取其内部的每一个字节。

NAND Flash用复杂的I/O口来串行地存取数据,各个产品或

厂商的方法各不相同。8个引脚用来传送控制、地址和数据信息。

所 有 Flash 器 件 都 受 位 交 换 现 象 的 困 扰 , 此 问 题 更 多 见 于

I2S

GPIO RTC

LCD DMA LCD Cont.

4 Channel DMA Controller

Memory Cont.

ADC

S3C2410A的272 脚FBGA 封装

2.7.2 S3C2410A 的启动

S3C2410A支持从NAND Flash启动,NAND Flash具 有容量大,比NOR Flash价格低等特点。系统采用NAND Flash与SDRAM组合,可以获得非常高的性价比。 S3C4120X具有三种启动方式,可通过OM [1:0]管脚 (OM0为管脚U14, OM1为管脚U15)进行选择。

2.7.5 时钟和电源管理

时钟和电源由3部分组成:时钟控制、USB控制和 电源控制。

(3) 电源控制 S3C2410A通过4种电源管理模式有效地控制了功耗:

NORMAL模式

SLOW模式 ID 输入/输出口

S3C2410A 有117多功能I/O口,它们分别是:

NAND Flash。必须采用错误检测/错误更正(EDC/ECC)算法确保 可靠性。

2.7.5 时钟和电源管理

时钟和电源由3部分组成:时钟控制、USB控制和 电源控制。

(1) 时钟控制 S3C2410A能够产生3种时钟信号,分别是: FCLK应用于CPU的时钟, HCLK用于AHB Bus各种外围设备, PCLK 用于APB Bus各种接口设备。 其中FCLK 应用的就是MPLL的频率,不用设置。 (2) USB控制 主要对USB的时钟参数进行配置。

0x4800000c

0x48000010 0x48000014 0x48000018 0x4800001c 0x48000020

R/W

R/W R/W R/W R/W R/W

BANK2 控制

BANK3 控制 BANK4 控制 BANK5 控制 BANK6 控制 BANK7 控制

0x0700

0x0700 0x0700 0x0700 0x18008 0x18008

2.7.3 存储器控制器

SRAM,静态的随机存取存储器,加电情况下,不需要刷 新,数据不会丢失,而且,一般不是行列地址复用的。需要更 大的硅片面积,成本较高。它的存取时间比DRAM要短得多, 经常用于Cache。 SDRAM,同步的DRAM,即数据读写需要时钟来同步。 因而能够工作在较高的时钟频率下。数据从存储元(memory cell) 被流水化地取出,最后突发式(burst)输出到总线。 DRAM和SDRAM由于实现工艺问题,容量较SRAM大。 但是读写速度不如SRAM。

2.7.1 内部结构

UARTS

Power Management

USB Devices

SDI/MMC Watchdog Timer

Clock Cont.

Interrupt Cont.

ARM920T Core 200MHz

JTAG

BUS Cont.

Bridge SPI I2C

AHB

Bus Cont. Arbiter/Decoder USB HostCONT. NandFlash Cont.

(1)总线宽度和等待控制寄存器BWSCON

寄存器 BWSCON 地址 0x48000000 读/写 R/W 功能 总线宽度和等待控制 复位后的值 0x000000

bank0的数据总线(nGCS0)必须首先设置成16 位或32 位的。因为 bank0 通常作为引导ROM 区(映射到地址0x0000-0000),在复位时,系 统将检测OM[1:0]上的逻辑电平,并据此来决定bank0 的总线宽度。 BWSCON寄存器描述了bank1~bank7数据总线宽度和等待控制。总 线宽度可以是8位、16位和32位。每个bank_n(n=1~7)用该寄存器的4位 来描述,分别是UB/LB(即高8位和低8位)、是否需要总线访问等待周 期、数据总线宽度的是多少(占用了2位)。 如果对每个bank使能WAIT功能,当对某个bank区进行访问时, nOE的低电平有效时间就会在nWAIT引脚的控制下延长。从tacc-1时 刻开始检测nWAIT的状态。在采样到nWAIT为高电平后的下一个时钟 ,nOE将恢复高电平。nWAIT对nWE信号的作用与对nOE信号相同。

2.7.6 输入/输出口

(2) 输入/输出口数据寄存器(GPADAT-GPHDAT) 如果管脚被置成输出方式则可以向相应的位写数据;如果

管脚被置成输入方式则可以从相应的位读数据。

2.7.4 NAND Flash控制器

当前,NOR flash存储器的价格比较昂贵,而SDRAM和 NAND flash存储器的价格相对来说比较合适,这样就激发了 一些用户产生希望从NAND flash启动和引导系统,而在 SDRAM上执行主程序代码的想法。 S3C2410A恰好满足这一要求,它可以实现从NAND flash上 执行引导程序。 S3C2410A具备一个内部SRAM缓冲器--“Steppingstone”。 当系统启动时,NAND flash存储器的前面4KByte字节将被自 动载入到Steppingstone中,然后系统自动执行这些载入的引 导代码。

★ 1个LCD控制器(支持STN和TFT带有触摸屏的液晶显示器); ★ SDRAM控制器; ★ 3个通道的UART; ★ 4个通道的DMA;

2.7 S3C2410 ARM微处理器简介

★ 4个具有PWM功能的计时器和1个内部时钟;

★ 8通道的10位ADC;

★ 触摸屏接口; ★ I2C总线接口; ★ 1个USB主机接口,1个USB设备接口; ★ 2个SPI接口; ★ SD接口和MMC卡接口; ★ 117位通用I/O口和24位外部中断源。

嵌入式系统的原理及应用

2.7 S3C2410 ARM微处理器简介

Samsung 公司推出的16/32位RISC处理器S3C2410A, 为手持设备和一般类型应用提供了低价格、低功耗、高性 能小型微控制器的解决方案。采用272 脚FBGA 封装,内含 一个ARM920T 内核。为了降低系统成本,S3C2410A 提供 了以下丰富的片内外围:

2.7 S3C2410 ARM微处理器简介

S3C2410A采用了ARM920T内核,0.18um工艺的CMOS标准 宏单元和存储器单元。它的低功耗、精简和出色的全静态设计特 别适用于对成本和功耗敏感的应用。同样它还采用了一种叫做 AMBA新型总线结构。 S3C2410A显著特性是CPU核心。 ARM920T实现了MMU,AMBA BUS和Harvard高速缓冲体 系结构。这一结构具有独立的16kB指令Cache和16kB数据Cache, 每个都是由8字长的行(line)构成。

2.7.3 存储器控制器(续1)

存储器控制是通过相关的寄存器来实施的。

寄存器分为控制寄存器和状态寄存器。可以给控制寄

存器赋值以得到所需要的状态,而状态寄存器会根据情况自

行产生变化。不要试图控制状态寄存器。

存储器控制器是由若干寄存器组成。了解这些寄存器 ,就可以阅读或编写Bootloader程序了。

写NAND flash命令到NFCMD寄存器;

写NAND flash地址到NFADDR寄存器; 在读写数据时,通过NFSTAT寄存器来获得NAND flash 的状态信息。应该在读操作前或写入之后检查R/nB信号 (准备好/忙信号); 通过NFDATA读写数据。

NAND Flash与NOR Flash

— Port A (GPA): 23-输出口 — Port B (GPB): 11-输入/输出口 — Port C (GPC): 16-输入/输出口 — Port D (GPD): 16-输入/输出口 — Port E (GPE): 16-输入/输出口